**Optimum Performance Controls of

Multiport Converter for Transport

Electrification Applications**

by

**Wei Juin Choy**

Thesis submitted to The University of Nottingham for

the degree of Doctor of Philosophy, January 2024

# Contents

|                                                               |          |

|---------------------------------------------------------------|----------|

| List of Acronyms.....                                         | iv-vi    |

| List of Figures.....                                          | vii-x    |

| List of Tables.....                                           | xi       |

| Abstract.....                                                 | xii-xiii |

| Acknowledgements.....                                         | xiv-xv   |

| Chapter 1: Introduction.....                                  | 1        |

| 1.1 Motivation for Carbon Reduction.....                      | 2        |

| 1.2 Strategy for Vehicle Electrification.....                 | 3        |

| 1.3 Industrial Association and Research Background.....       | 6        |

| 1.4 Thesis Outline.....                                       | 7        |

| Chapter 2: Review of Converter Technology.....                | 8        |

| 2.1 Electric Drives and Propulsion Inverters.....             | 12       |

| 2.1.1 High Voltage Trends and Silicon Carbide Technology..... | 12       |

| 2.1.2 Module Packaging Trends.....                            | 14       |

| 2.2 DCDC Converters.....                                      | 18       |

| 2.2.1 Challenges Facing the State of the Art.....             | 19       |

| 2.2.2 Cost Optimisation via Hardware.....                     | 20       |

|                                                                       |     |

|-----------------------------------------------------------------------|-----|

| 2.2.3 Cost Optimisation via Software.....                             | 26  |

| Chapter 3: Proposal of Multiport Converter Design.....                | 28  |

| 3.1 Inverter and PMSM.....                                            | 31  |

| 3.2 Isolated Buck Converter (dcA).....                                | 36  |

| 3.3 Interleaved Buck/Boost Converter (dcB).....                       | 39  |

| Chapter 4: Simultaneous System Characterisation and Optimisation..... | 44  |

| 4.1 Optimisation Methodology.....                                     | 44  |

| 4.1.1 Multiple Objective Optimisation Problem Technique.....          | 44  |

| 4.1.2 MOOP Application Example.....                                   | 47  |

| 4.2 Loss estimation.....                                              | 49  |

| 4.2.1 Conduction Losses.....                                          | 51  |

| 4.2.2 Switching Losses.....                                           | 54  |

| 4.2.3 Magnetic Losses.....                                            | 56  |

| 4.2.4 Performance Simulation Sweep.....                               | 65  |

| 4.3 Optimisations.....                                                | 74  |

| 4.3.1 Phase Deactivation.....                                         | 74  |

| 4.3.2 Phase Displacement.....                                         | 78  |

| 4.4 Discussion and Conclusions.....                                   | 79  |

| 4.4.1 MOOP Analysis.....                                              | 95  |

| 4.4.2 Optimisation Summary.....                                       | 103 |

| Chapter 5: Hardware Prototyping and Validation.....                   | 105 |

| 5.1 Power Module Profile Test Setup.....                              | 106 |

|                                             |     |

|---------------------------------------------|-----|

| 5.1.1 Conduction Losses Validation.....     | 108 |

| 5.1.2 Switching Losses Validation.....      | 112 |

| 5.2 Multiport Converter Test Setup.....     | 117 |

| 5.2.1 Engine RESTART.....                   | 122 |

| 5.2.2 Engine RUN.....                       | 125 |

| Chapter 6: Conclusions.....                 | 132 |

| 6.1 Summary of Achievements.....            | 132 |

| 6.2 Proposals for Future Scope of Work..... | 135 |

| Appendix A.....                             | 136 |

| Appendix B.....                             | 137 |

| Appendix C.....                             | 140 |

| Appendix D.....                             | 147 |

| Bibliography.....                           | 148 |

## List of Acronyms

|       |                                     |

|-------|-------------------------------------|

| 2D    | 2 Dimension                         |

| 3D    | 3 Dimension                         |

| AC    | Alternating Current                 |

| ACB   | Active Current Balancing            |

| AGD   | Active Gate Driver                  |

| Al    | Aluminum Electrolyte                |

| BOPP  | Biaxial Oriented PolyPropylene      |

| CAGR  | Compounded Annual Growth Rate       |

| CFFC  | Compensating Fringing Field Concept |

| COP26 | Climate Change Conference 2026      |

| CSR   | Current Source Rectifier            |

| D.O.E | Department Of Energy                |

| DAB   | Dual Active Bridge                  |

| DBC   | Direct Bonded Copper                |

| DC    | Direct Current                      |

| dcA   | Isolated Buck Converter             |

| dcB   | Interleaved Buck/Boost Converter    |

| DCDC  | DC to DC                            |

| DCM   | Discontinuous Conduction Mode       |

| DPT   | Double-Pulse Test                   |

|       |                                         |

|-------|-----------------------------------------|

| DS    | Drain-Source                            |

| DSC   | Double Sided Cooling                    |

| EMC   | Electro Magnetic Compliance             |

| EMI   | Electro Magnetic Interference           |

| ES    | Energy Storage                          |

| ESR   | Equivalent Series Resistance            |

| EV    | Electric Vehicle                        |

| FE    | Finite Element                          |

| FEA   | Finite Element Analysis                 |

| FFT   | Fast Fourier Transform                  |

| FW    | Field Weakening                         |

| GHG   | Greenhouse gas                          |

| HV    | High Voltage                            |

| ICE   | Internal Combustion Engine              |

| inv   | Inverter                                |

| IPMSM | Interior Permanent Magnet Machine       |

| KPI   | Key Performance Index                   |

| LPTN  | Lumped Parameter Network                |

| MLCC  | Multi-Layer Ceramic Capacitor           |

| MOOP  | Multiple Objective Optimisation Problem |

| MPC   | Model Predictive Control                |

| MPPF  | Metalized Polymer Films                 |

| MTPA  | Maximum Torque Per Ampere               |

| NBfL  | New Bus for London                      |

| NEV   | New Energy Vehicle                      |

|        |                                      |

|--------|--------------------------------------|

| NVH    | Noise Vibration Harshness            |

| PCB    | Printed Circuit Board                |

| PD     | Phase Displacement                   |

| PI     | Proportional Integral                |

| PMSM   | Permanent Magnet Synchronous Machine |

| PS-PWM | Phase Shifted Pulse Width Modulation |

| PWM    | Pulse Width Modulation               |

| RC     | Resistor-Capacitor                   |

| RMS    | Root Mean Square                     |

| RPM    | Revolutions Per Minute               |

| Si     | Silicon                              |

| SiC    | Silicon Carbide                      |

| SW     | Switching                            |

| TAB    | Tripple Active Bridge                |

| TH     | Targeted Harmonic                    |

| THD    | Total Harmonic Distortion            |

| UK     | United Kingdom                       |

| US     | United States of America             |

| VJT    | Virtual Junction Temperature         |

| VSI    | Voltage Source Inverter              |

# List of Figures

|                                                                                                                                                                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1: Electric car registrations and sales share in selected countries/regions, 2016-2021[1].....                                                                                                                                                              | 1  |

| Figure 1.2. Greenhouse gas emissions from transport in the EU, by transport mode and scenario as published by the European Environment Agency[3].....                                                                                                                | 2  |

| Figure 1.3 Inverter cost breakdown for a potential pathway to meet 2025 targets through the application of advanced integrated power modules; proposed DC link voltage range of 525-775V (650V nominal) and maximum current of 600A to achieve 100kW rating [7]..... | 5  |

| Figure 1.4. 2016 Wrightbus Routemaster Hybrid Bus (pictured) [14] .....                                                                                                                                                                                              | 6  |

| Figure 2.1: Vehicle component topology depicting multiple bus architecture supported by the proposed multiport converter governed by a unified controller operating the MOOP enhanced strategy to control power flow. ....                                           | 11 |

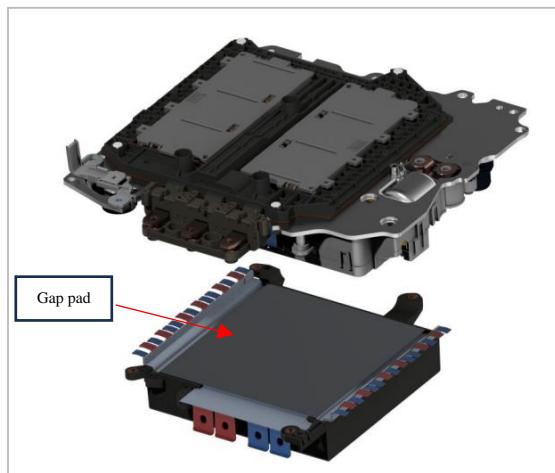

| Figure 2.2. Parallel Bosch power stage and capacitor module with a gap pad to provide thermal separation [25]. .....                                                                                                                                                 | 13 |

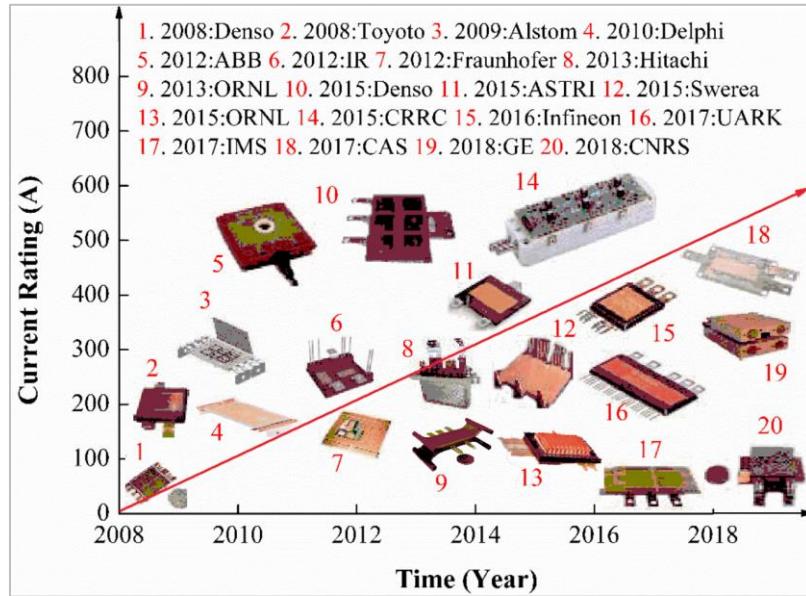

| Figure 2.3. DSC Power Modules from institutes and companies [32] .....                                                                                                                                                                                               | 15 |

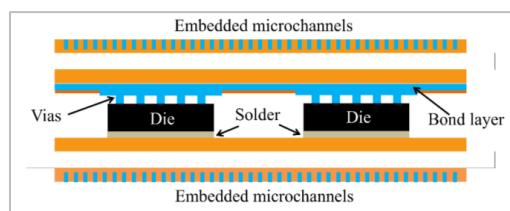

| Figure 2.4. Power Module Structure [32]. .....                                                                                                                                                                                                                       | 15 |

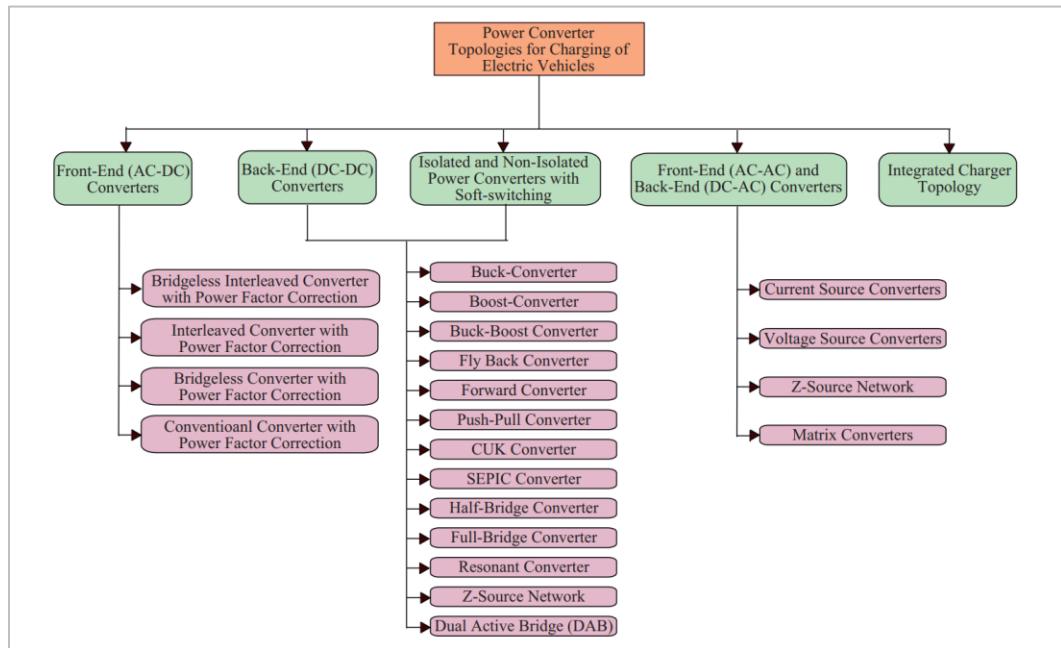

| Figure 2.5. DCDC converter topologies [34].....                                                                                                                                                                                                                      | 18 |

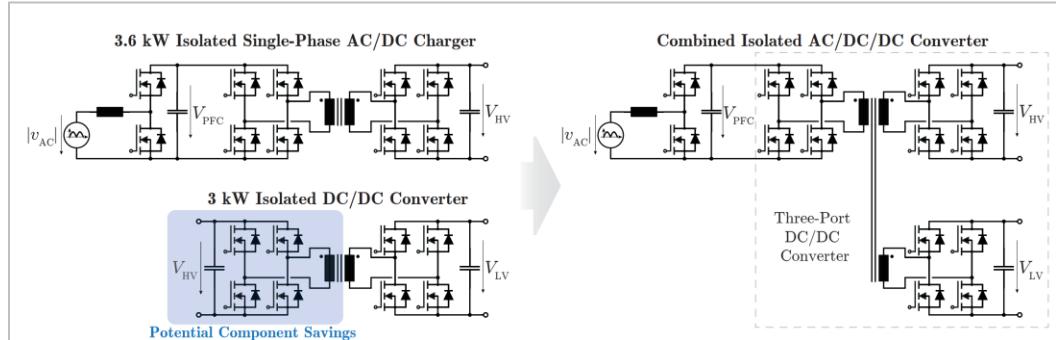

| Figure 2.6: Potential component saving achieved through integrated converter design [38].....                                                                                                                                                                        | 19 |

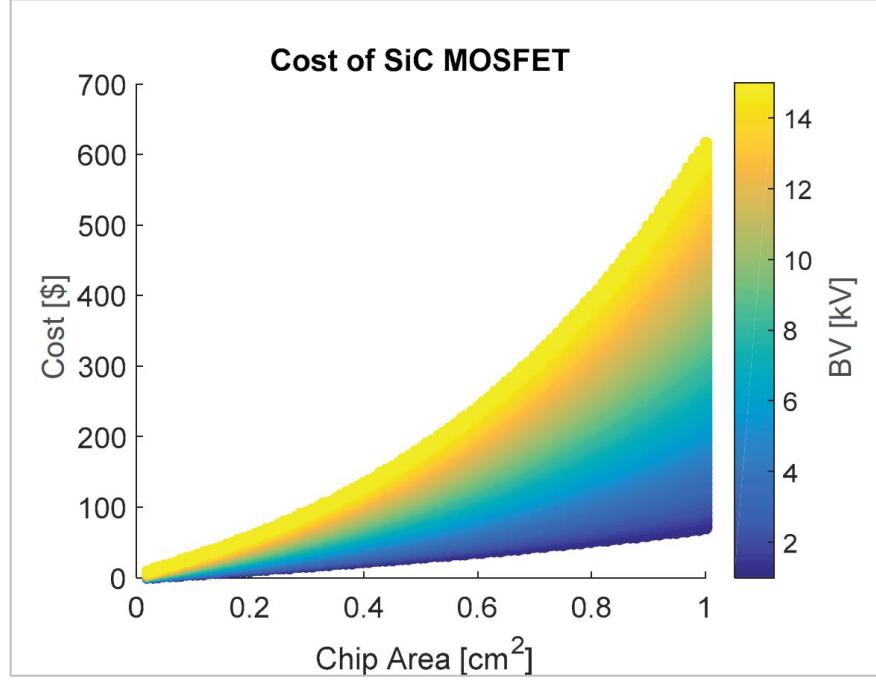

| Figure 2.7. SiC MOSFET cost vs active chip area at different voltage levels. ....                                                                                                                                                                                    | 21 |

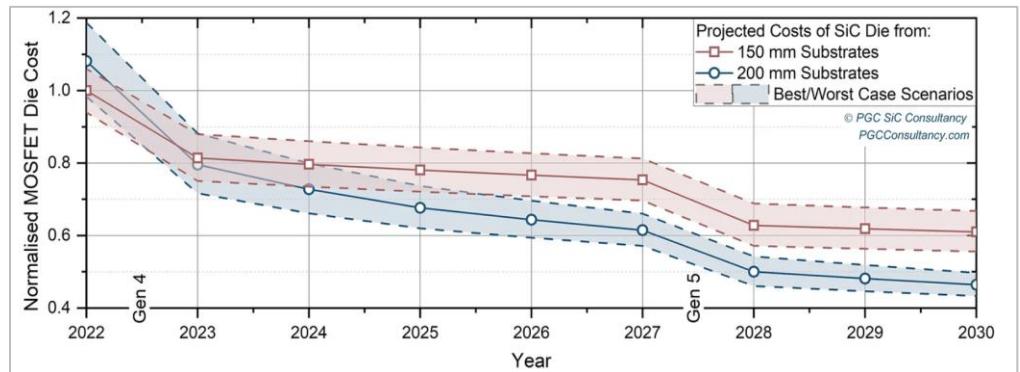

| Figure 2.8: PGC Consultancy SiC cost forecast model based on a best-in-class 2021 1200V/100A device [42].....                                                                                                                                                        | 21 |

|                                                                                                                                                                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

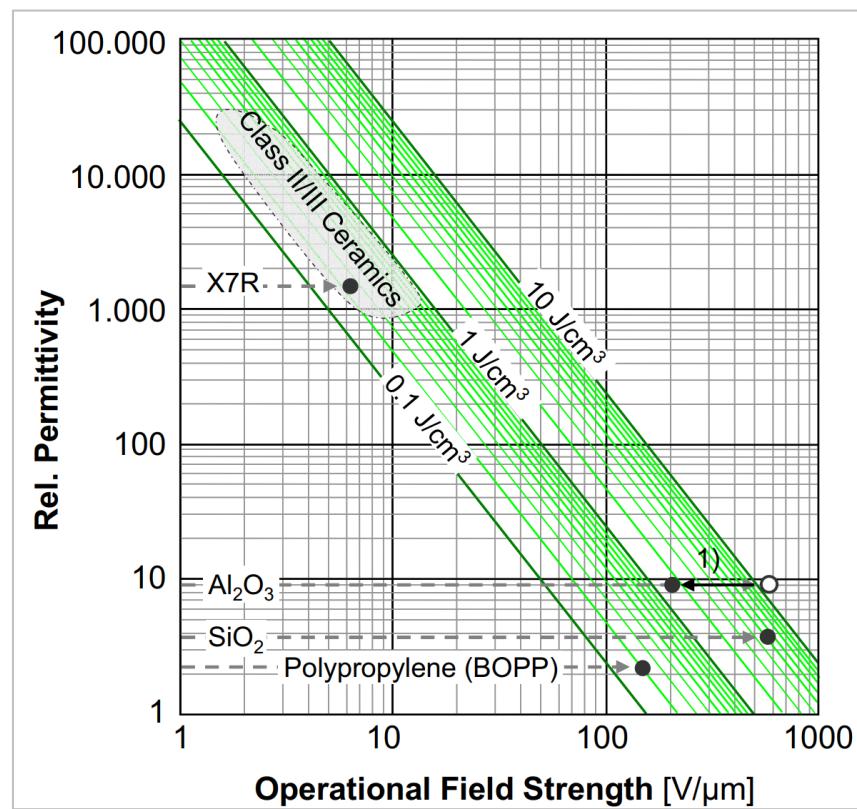

| Figure 2.9: Energy storage capacity of various dielectric materials compared [47].                                                                                                                                                                                                    | 23 |

| Figure 2.10: Statistical results of unit cost of standard film capacitors and Aluminium electrolytic capacitors [48].                                                                                                                                                                 | 24 |

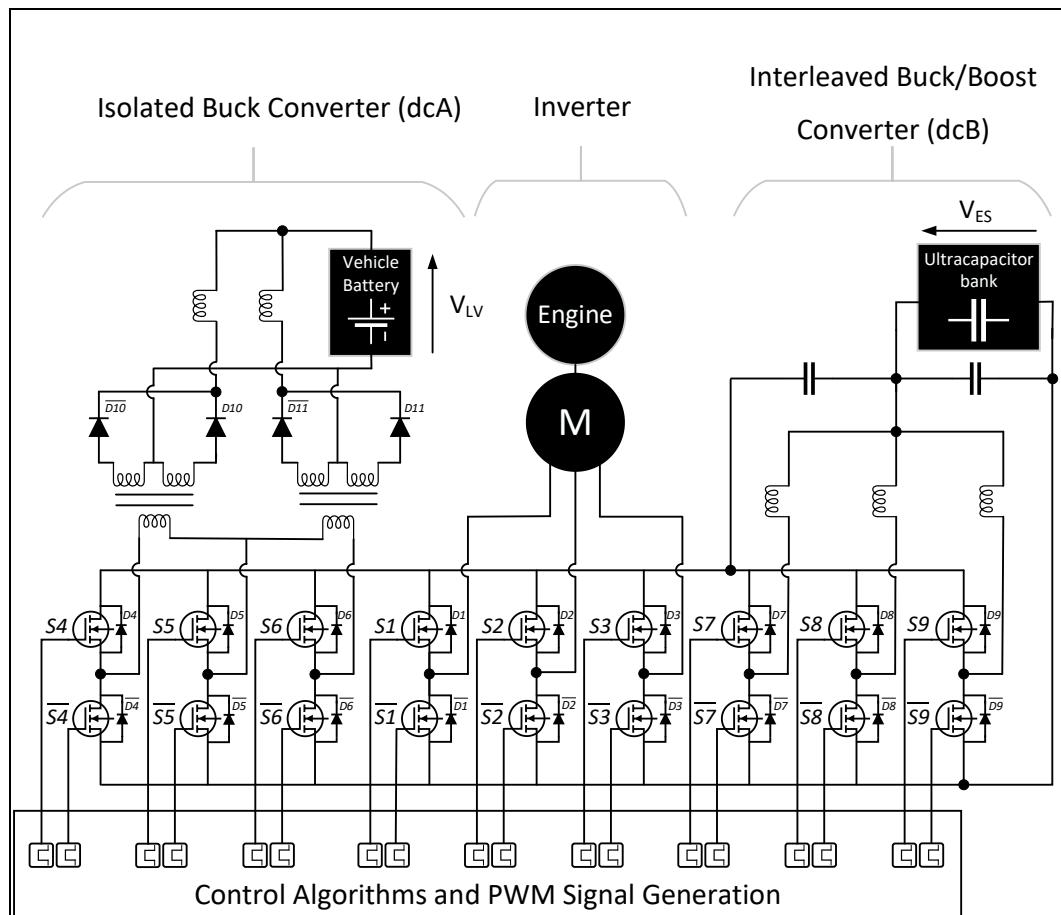

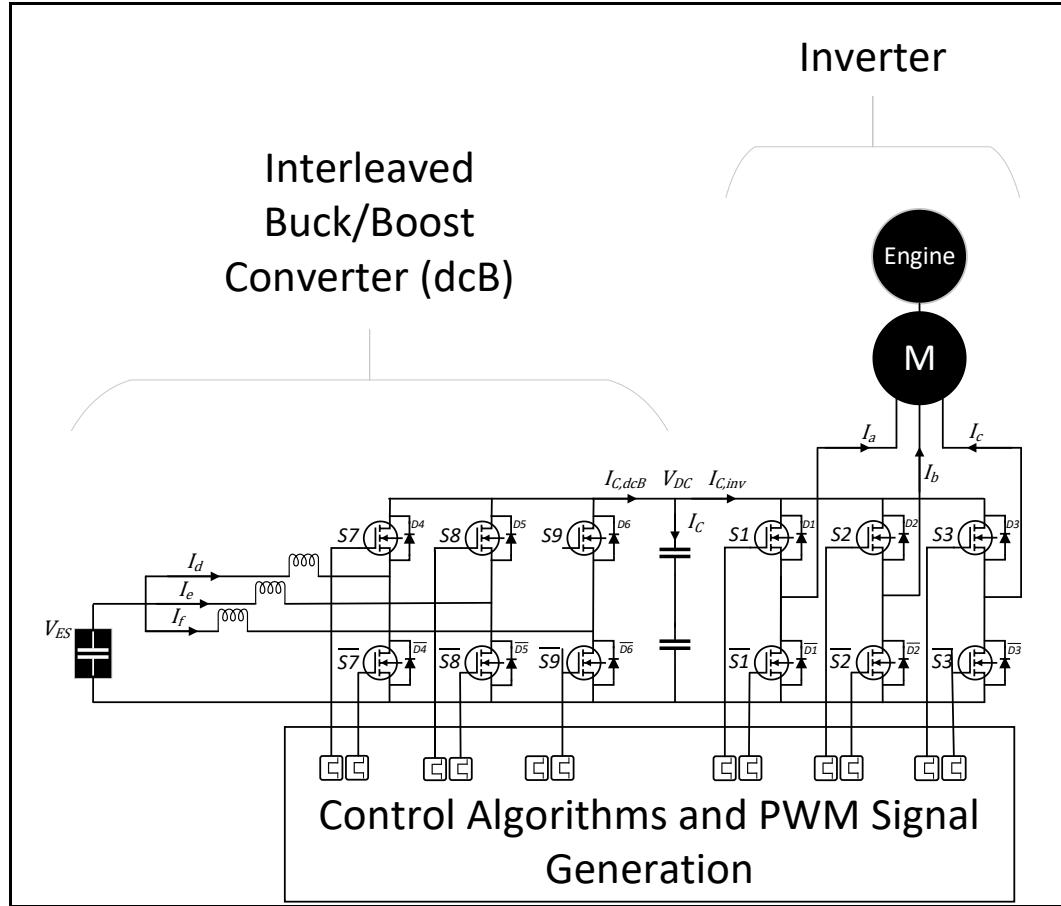

| Figure 3.1: Multiport converter topology consisting of an Inverter, Inv, an isolated buck converter, dcA and a non-isolated interleaved buck/boost converter, dcB.                                                                                                                    | 28 |

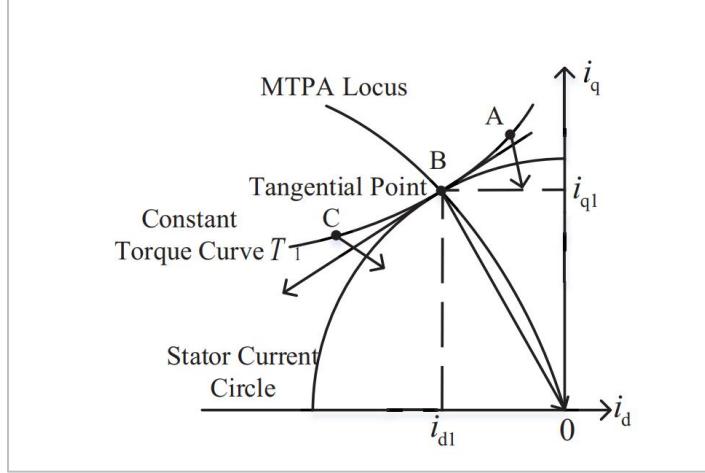

| Figure 3.2: Maximum Torque Per Ampere MTPA with reference to the dq frame [63].                                                                                                                                                                                                       | 32 |

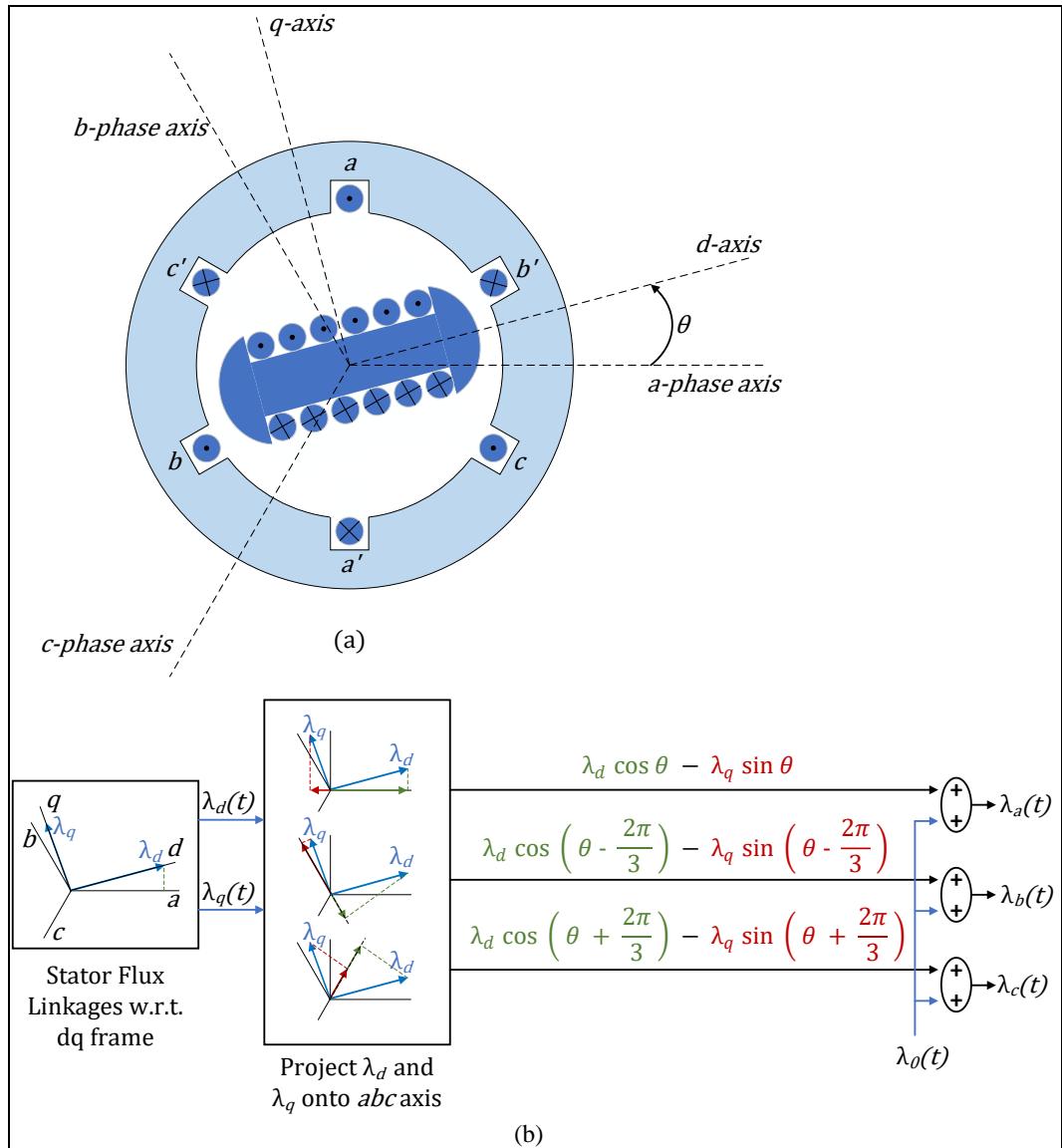

| Figure 3.3: Illustration of Park transformation. (a) Three phase synchronous machine with magnetic axes labelled. (b) Park's derivation of the inverse transformation.                                                                                                                | 34 |

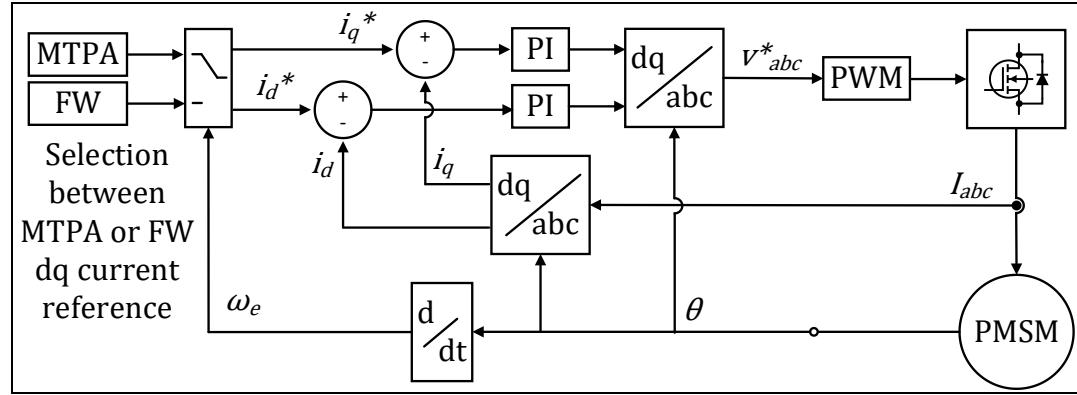

| Figure 3.4: Inverter control algorithm structure.                                                                                                                                                                                                                                     | 35 |

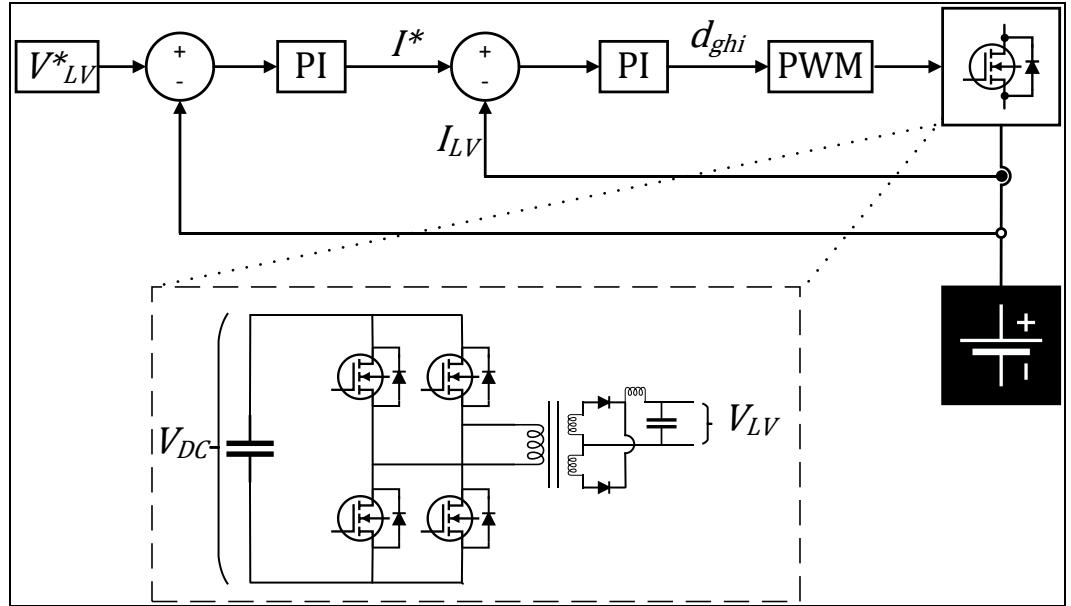

| Figure 3.5: Isolated Buck Converter control algorithm structure.                                                                                                                                                                                                                      | 36 |

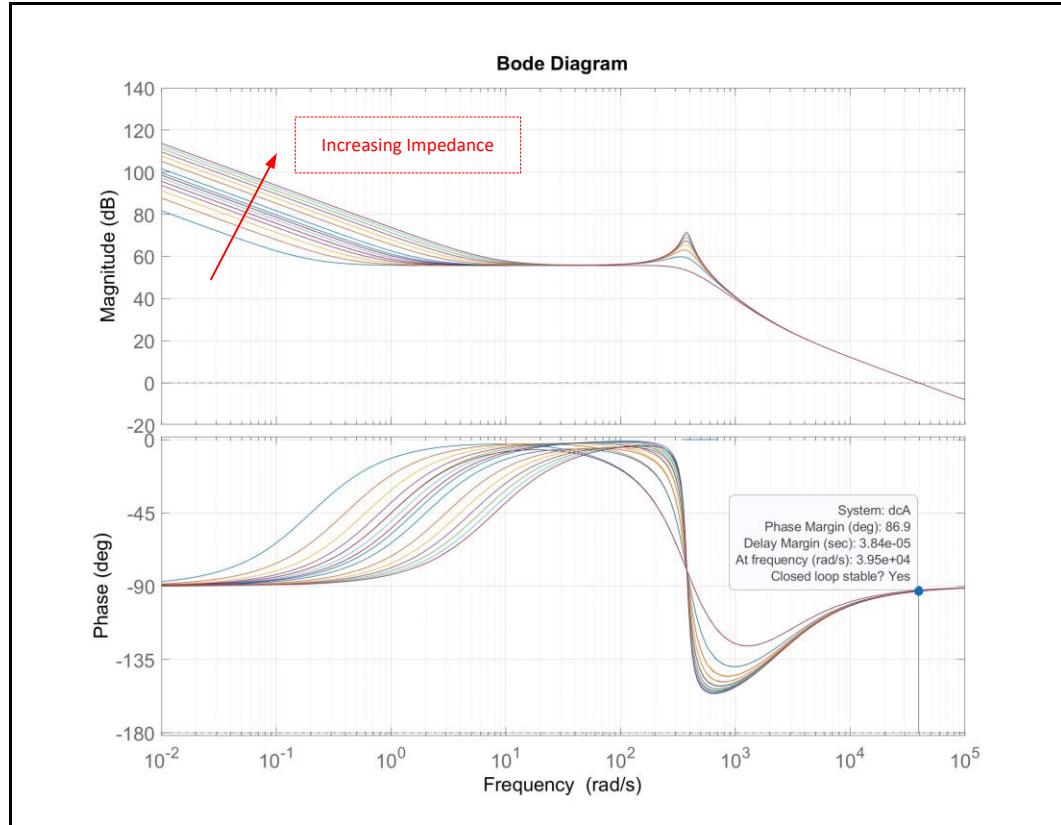

| Figure 3.6: Isolated Buck Converter (dcA) frequency response as $R_{dcA\_ESR}$ is varied.                                                                                                                                                                                             | 38 |

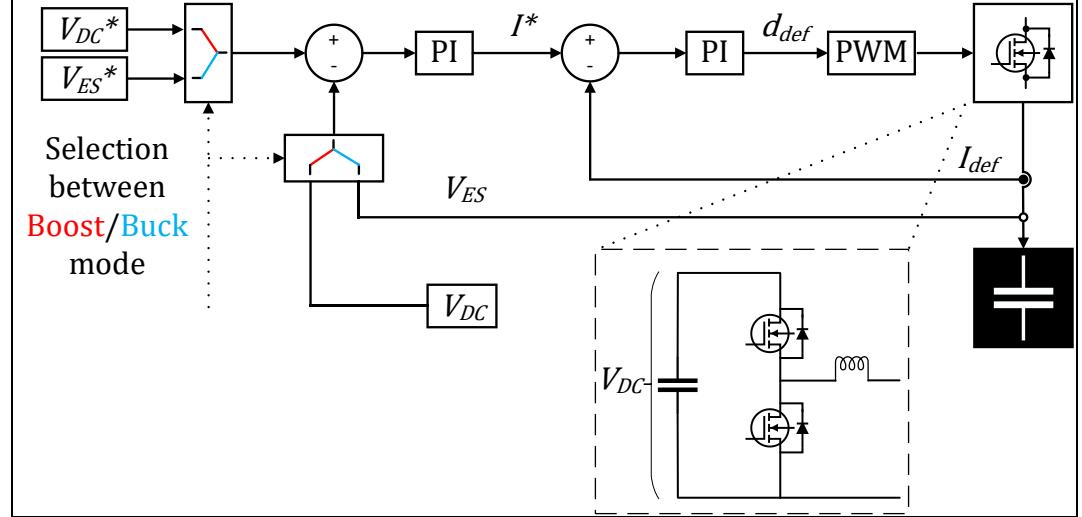

| Figure 3.7: Interleaved Buck/Boost Converter (dcB) control algorithm structure in Boost (red) and Buck (blue) mode.                                                                                                                                                                   | 40 |

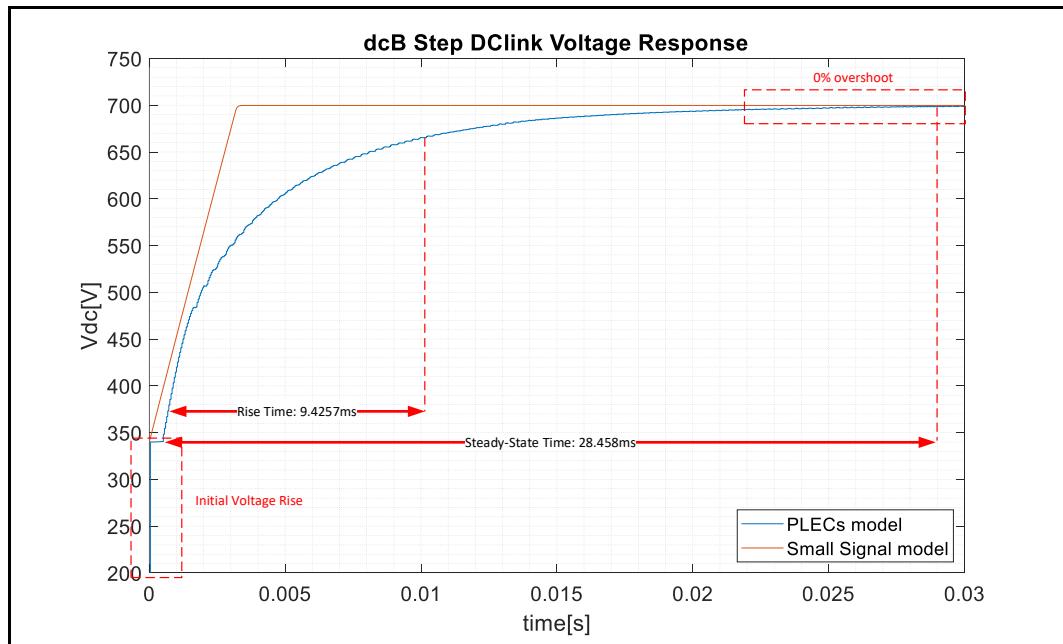

| Figure 3.8: Interleaved Buck/Boost DC Converter (dcB) step response with optimized gains                                                                                                                                                                                              | 42 |

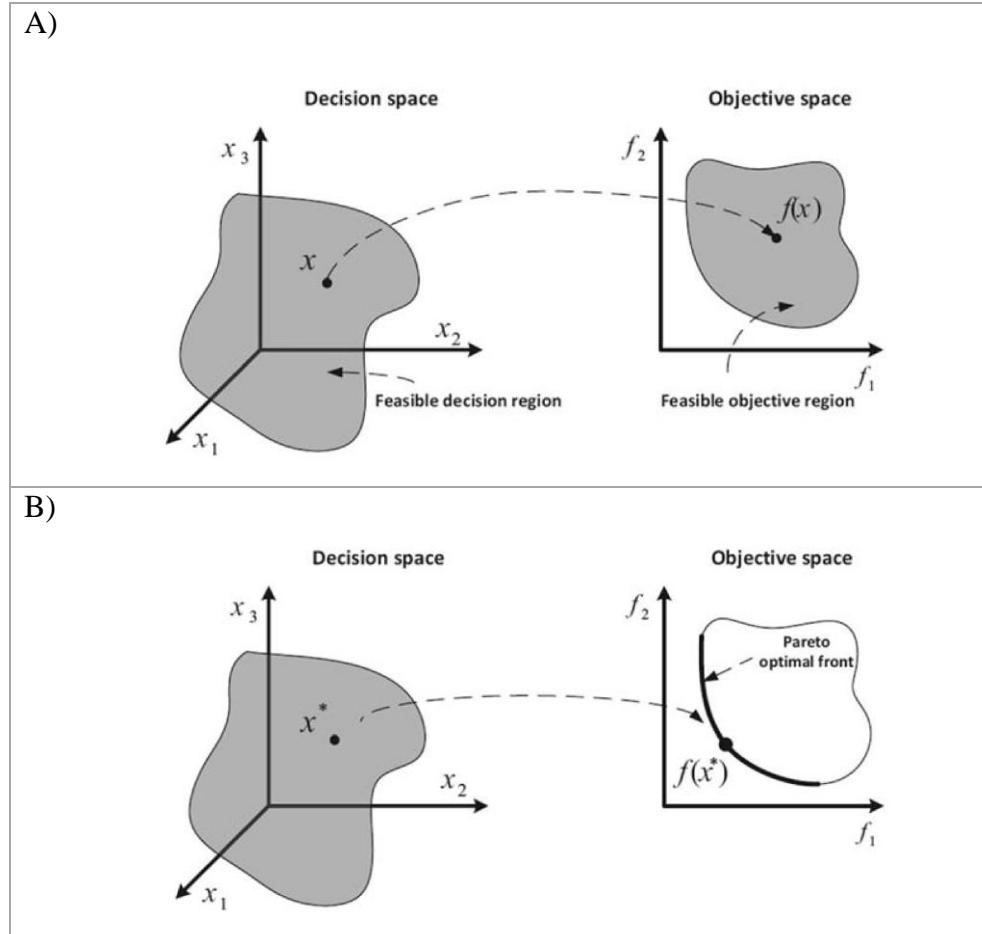

| Figure 4.1: Pictorial representation of the objective functions within the solution space and objective function space (A). Definition of the Pareto optimal front (B) [76].                                                                                                          | 46 |

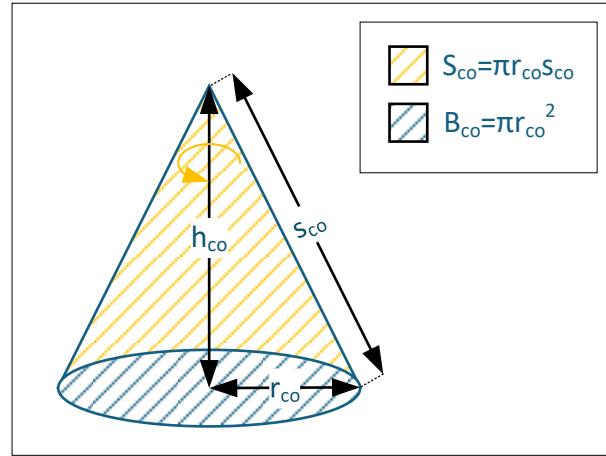

| Figure 4.2. Example MOOP application on a right circular cone.                                                                                                                                                                                                                        | 47 |

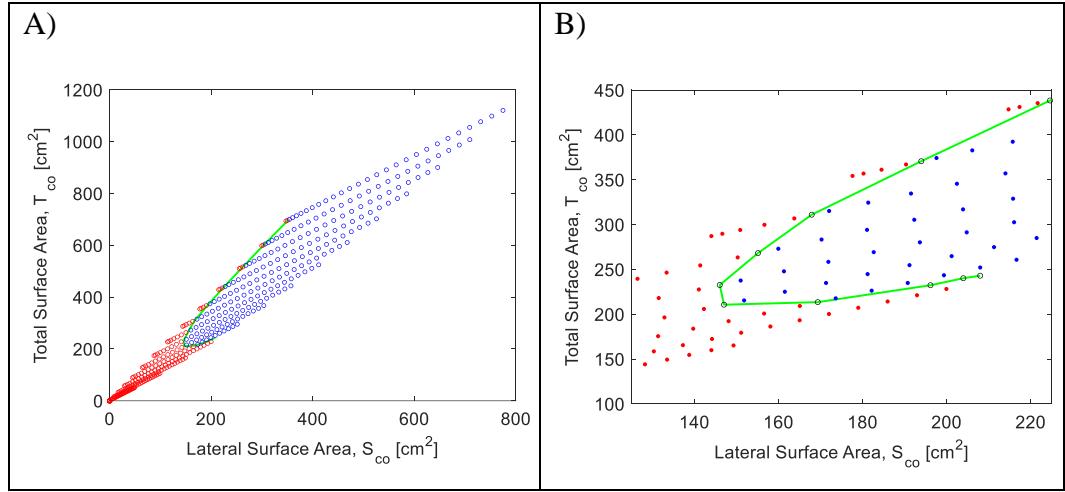

| Figure 4.3. (A) MOOP Objective space encompassing the lateral and total surface area of a cone. Blue circles indicate the feasible region. Red circles denote vectors not satisfying the minimum volume constraint in Table 4 (B) Zoom on (A) illustrating the Pareto Front in green. | 48 |

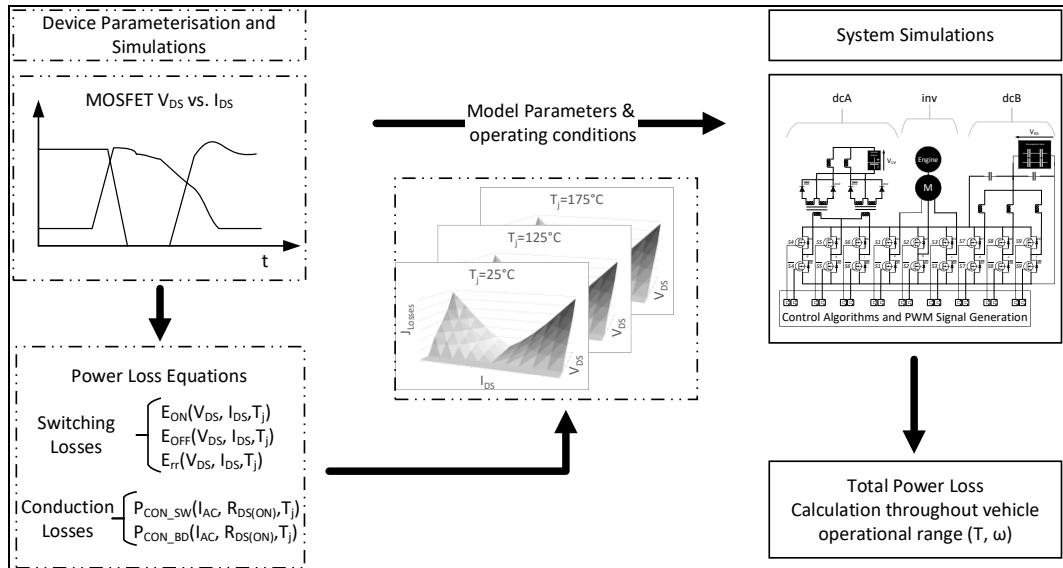

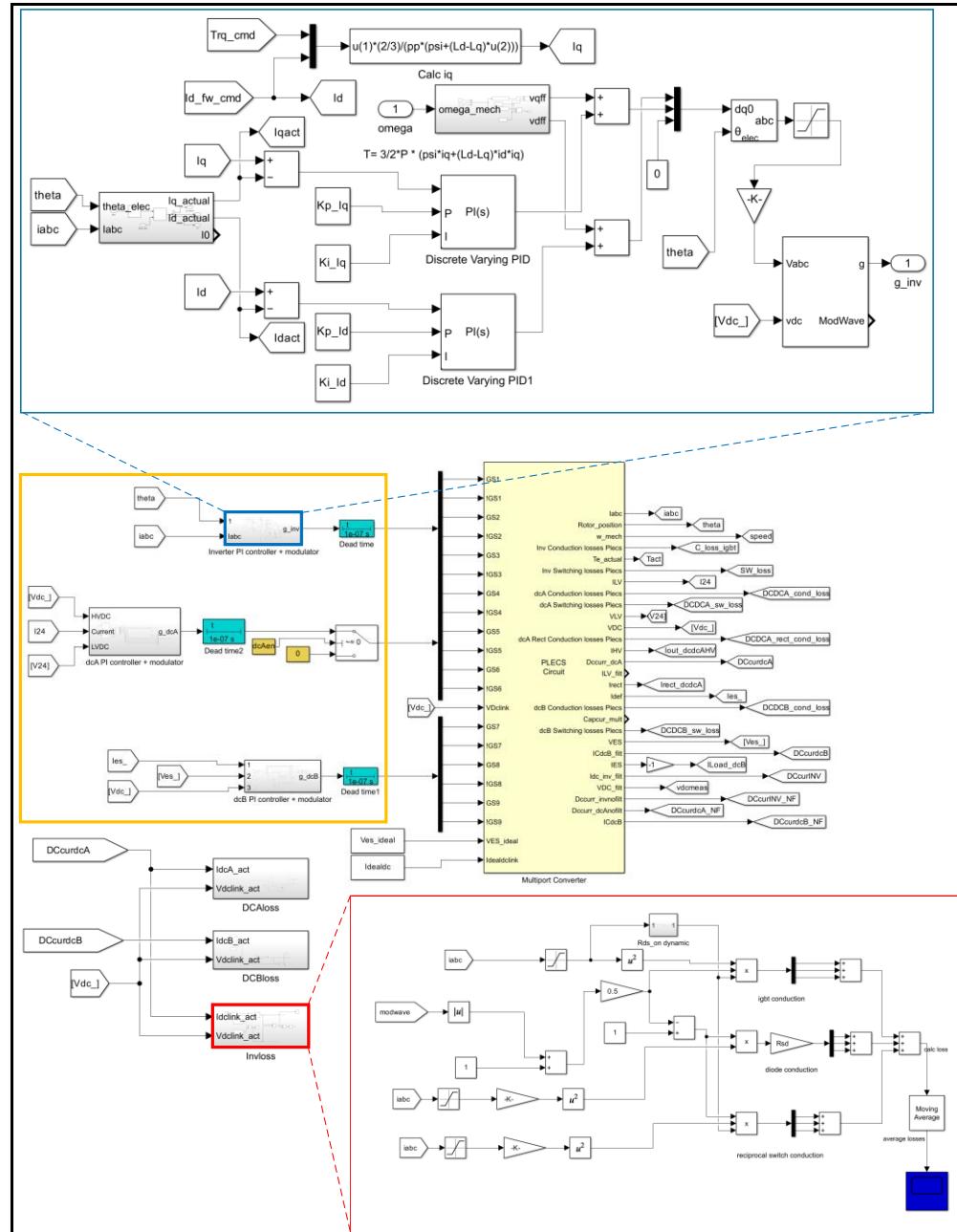

| Figure 4.4: Multiport converter semiconductor loss calculation in MATLAB/SIMULINK.                                                                                                                                                                                                    | 49 |

|                                                                                                                                                                                                   |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

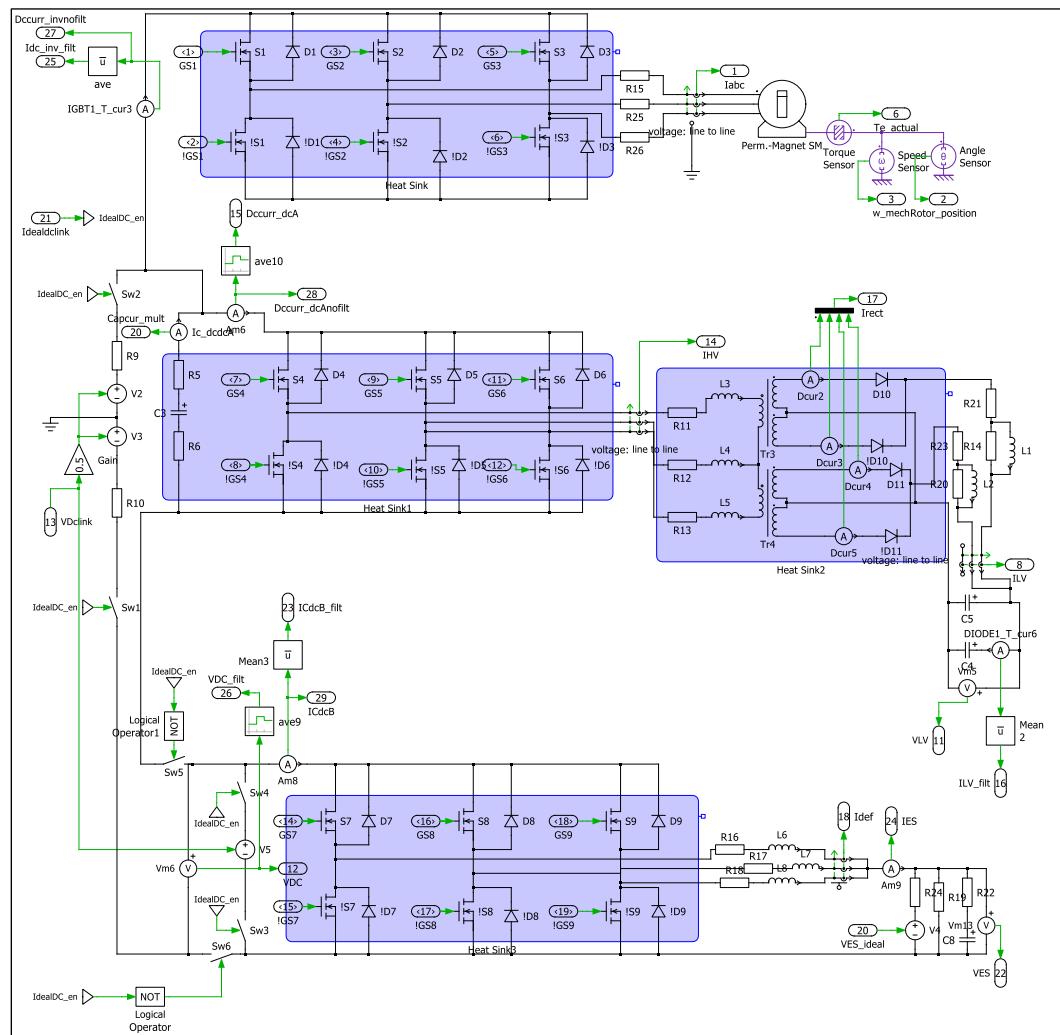

| Figure 4.5. Component-level PLECs model implementation of the Multiport converter.....                                                                                                            | 50 |

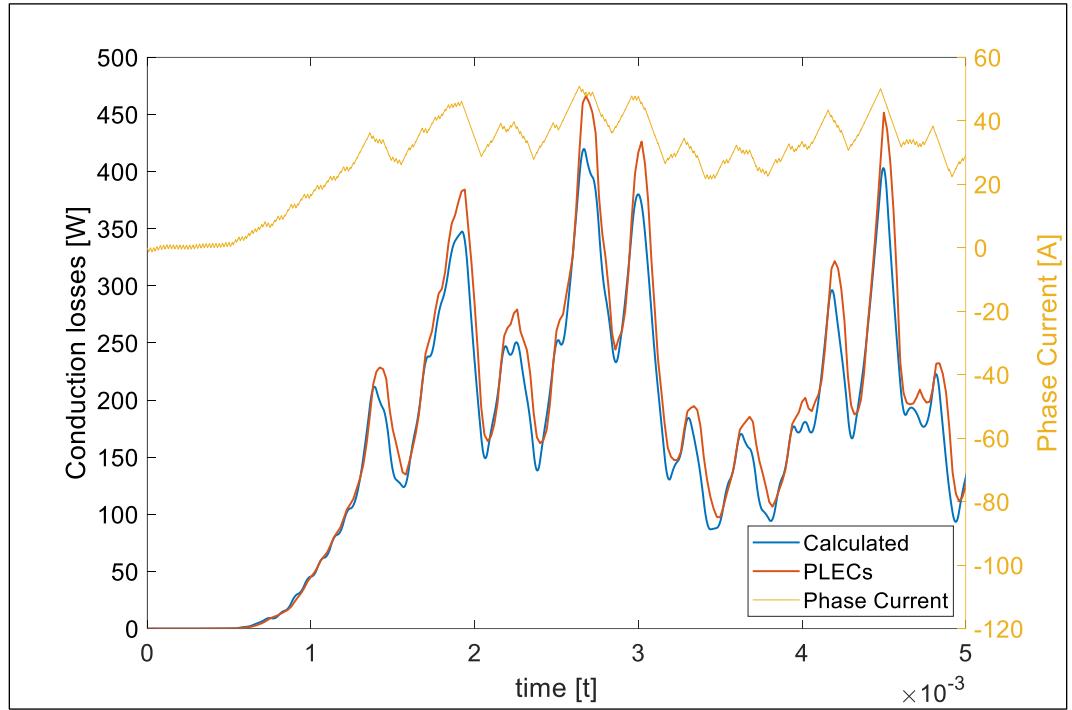

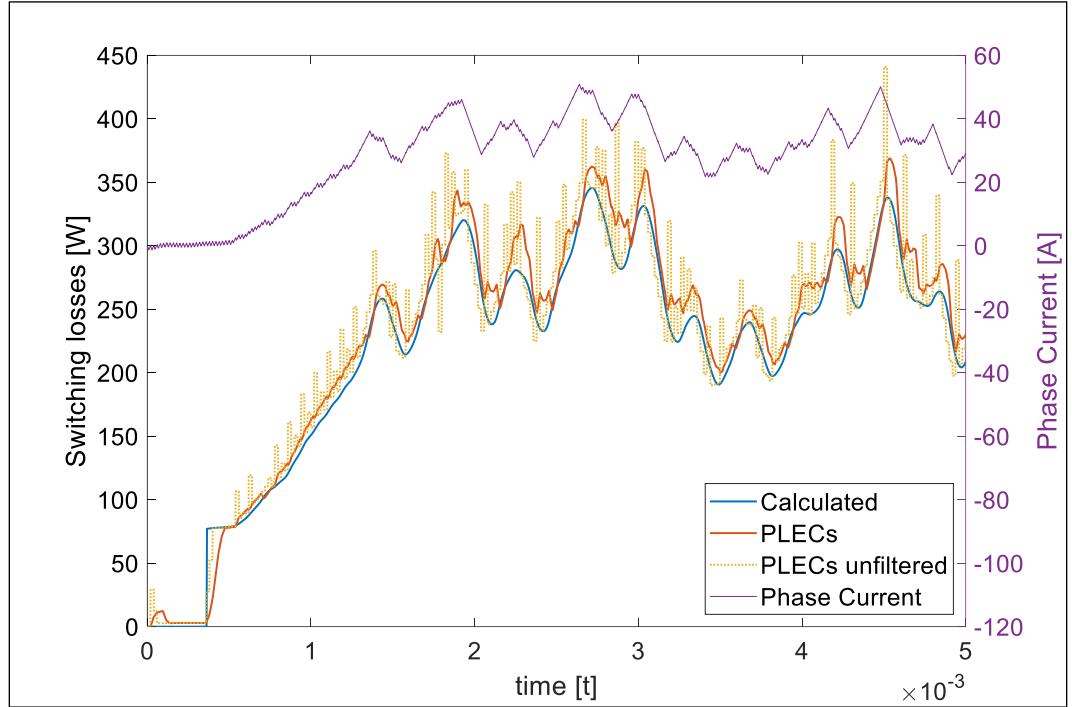

| Figure 4.6. Comparison of conduction losses within dcB during Multiport converter Boost operation. Calculation method in blue, PLECs results in red, and converter phase current in yellow. ....  | 53 |

| Figure 4.7. Comparison of switching losses within dcB during Multiport converter Boost operation. Calculation method in blue, PLECs results in red (with filter) and yellow (without filter)..... | 55 |

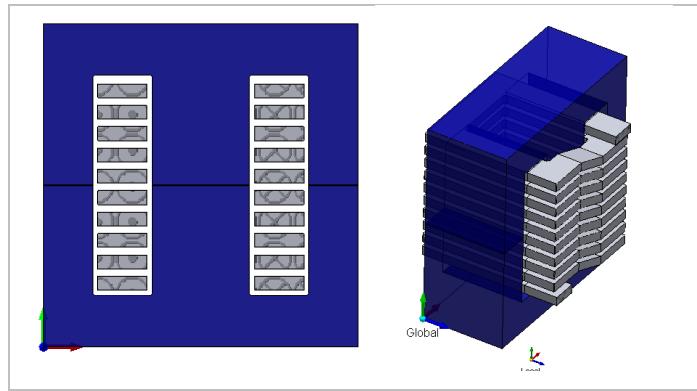

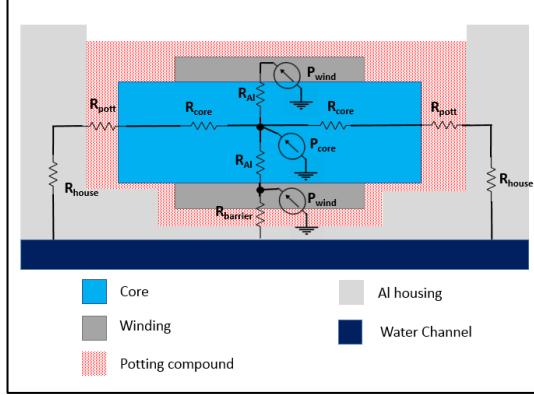

| Figure 4.8: 2D and 3D FE Model of dcB inductor. ....                                                                                                                                              | 58 |

| Figure 4.9: 2D and 3D FEA flux densities of dcB inductor. ....                                                                                                                                    | 58 |

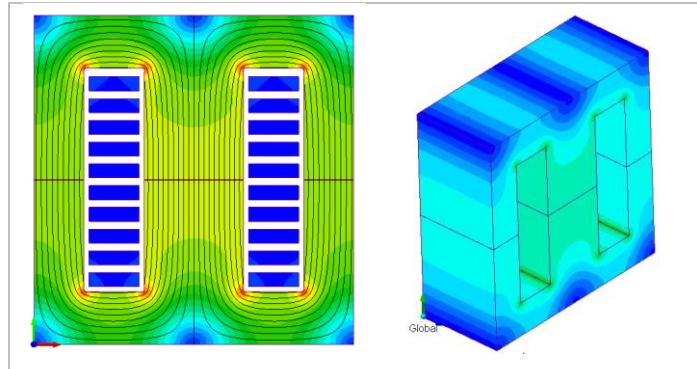

| Figure 4.10: Comparison of results from Analytical, 2DFEA and 3DFEA for calculation of main inductance (A), DC winding loss (B), AC winding loss (C) and Core Loss (D) .....                      | 59 |

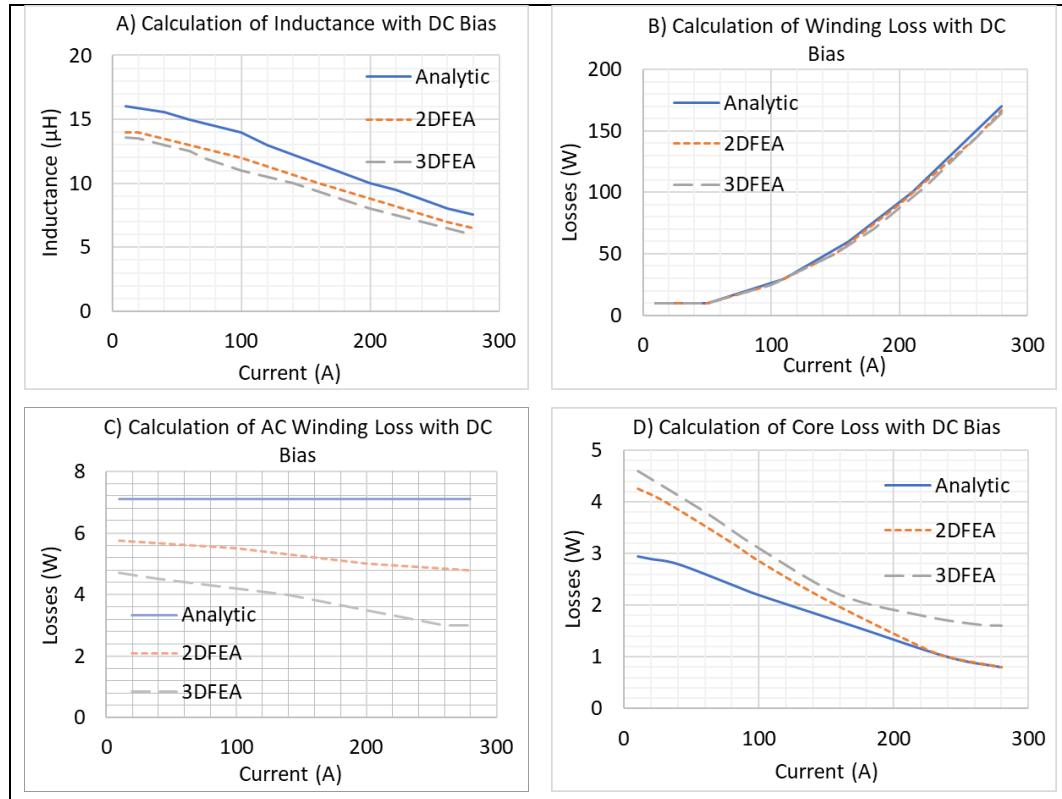

| Figure 4.11: Simplified lumped parameter network. ....                                                                                                                                            | 61 |

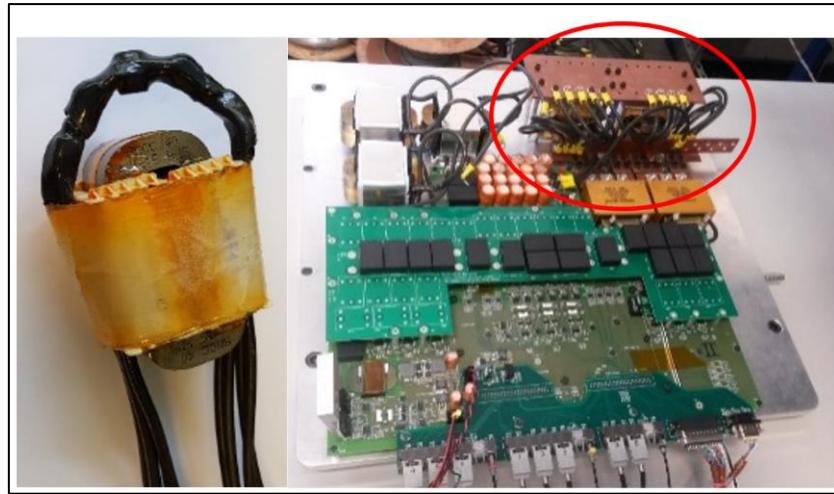

| Figure 4.12. Inductor Design 1 separate (left), tested within functional prototype multiport converter (right). ....                                                                              | 62 |

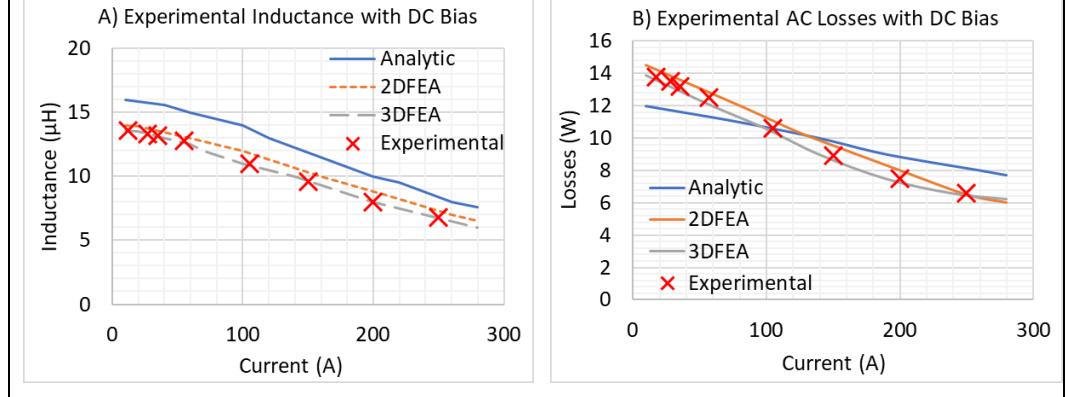

| Figure 4.13: Experimentally measured inductance of Design 2 and AC losses as current is increased.....                                                                                            | 63 |

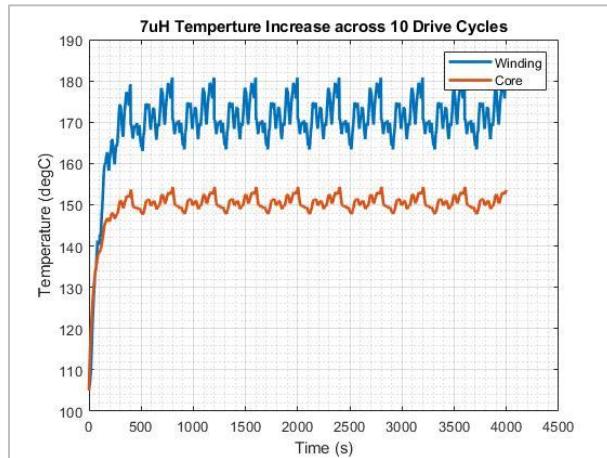

| Figure 4.14: Simulation of dcB Inductor temperature across 10 drive cycles.....                                                                                                                   | 64 |

| Figure 4.15. Loss calculation model of multiport converter. Refer to Figure 4.5 for PLECs circuit of Multiport Converter. ....                                                                    | 65 |

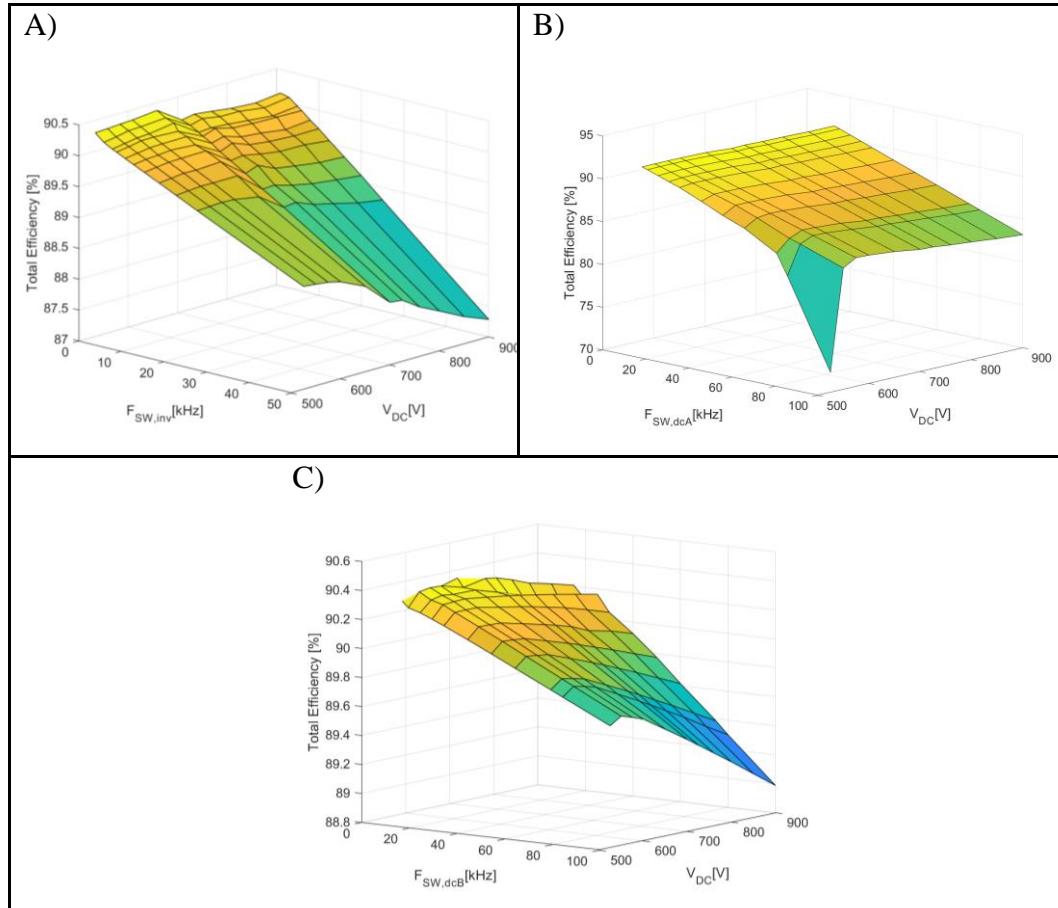

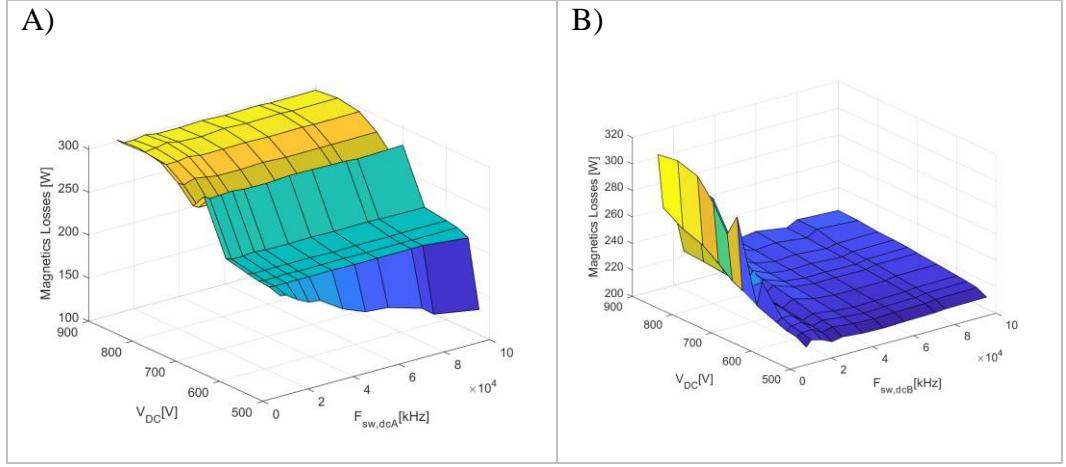

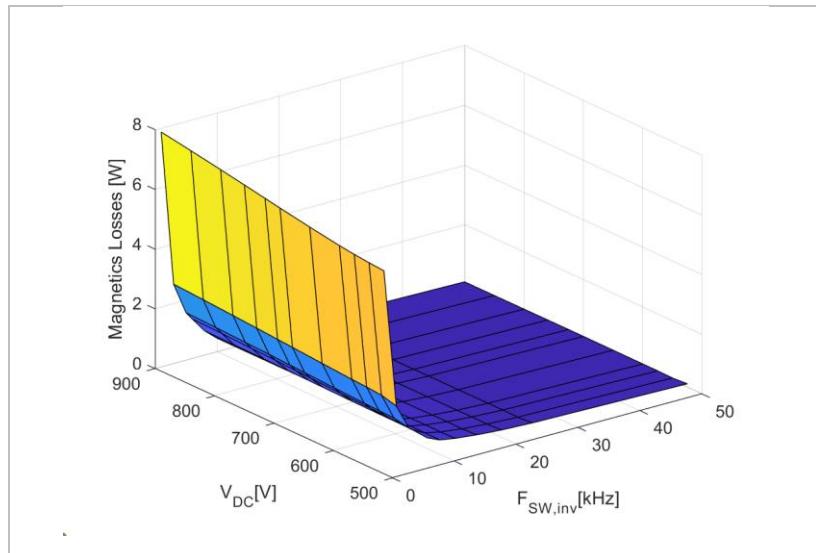

| Figure 4.16: Total multiport converter efficiency when DC link voltage and (A) Inverter, (B) dcA and (C) dcB switching frequency is varied. ....                                                  | 69 |

| Figure 4.17: Magnetic component losses as DC link voltage and switching frequency is varied in (A) dcA and (B) dcB. ....                                                                          | 70 |

| Figure 4.18: THD [%] content on inverter phase current as DC link voltage and inverter switching frequency is varied. ....                                                                        | 71 |

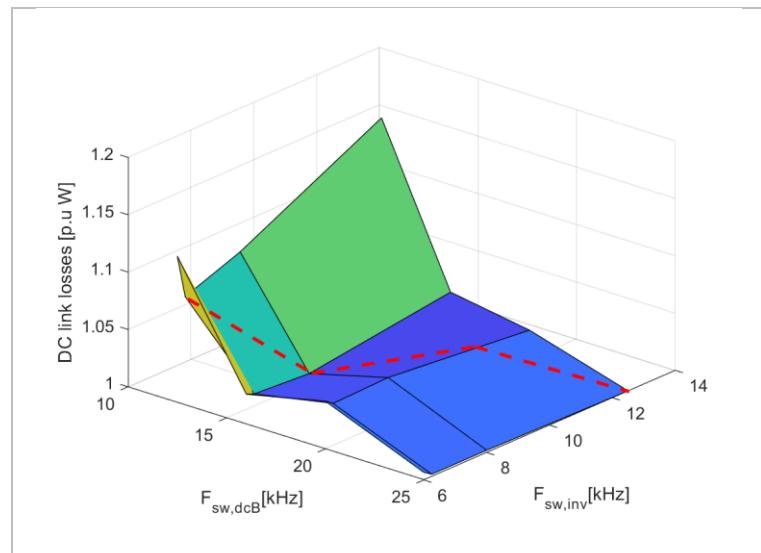

| Figure 4.19: Per Unit (p.u.) DC link capacitor losses- calculated on base value: 70.77W as $F_{SW,inv}$ and $F_{SW,dcB}$ are varied. ....                                                         | 72 |

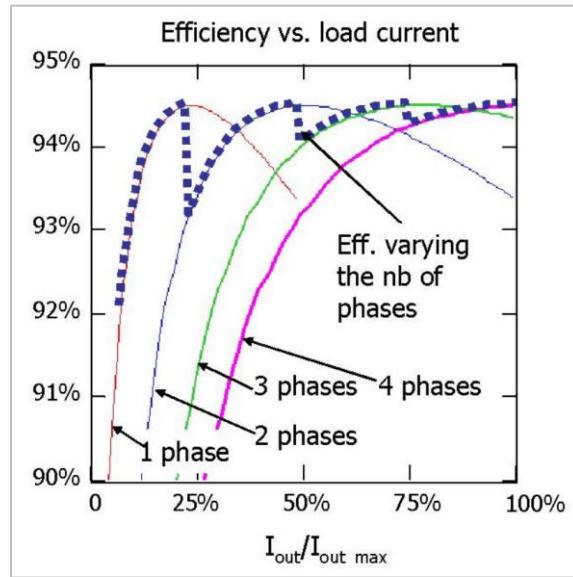

| Figure 4.20: Multiphase converter efficiency for variation in the number of active phases [97]. ....                                                                                              | 75 |

|                                                                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

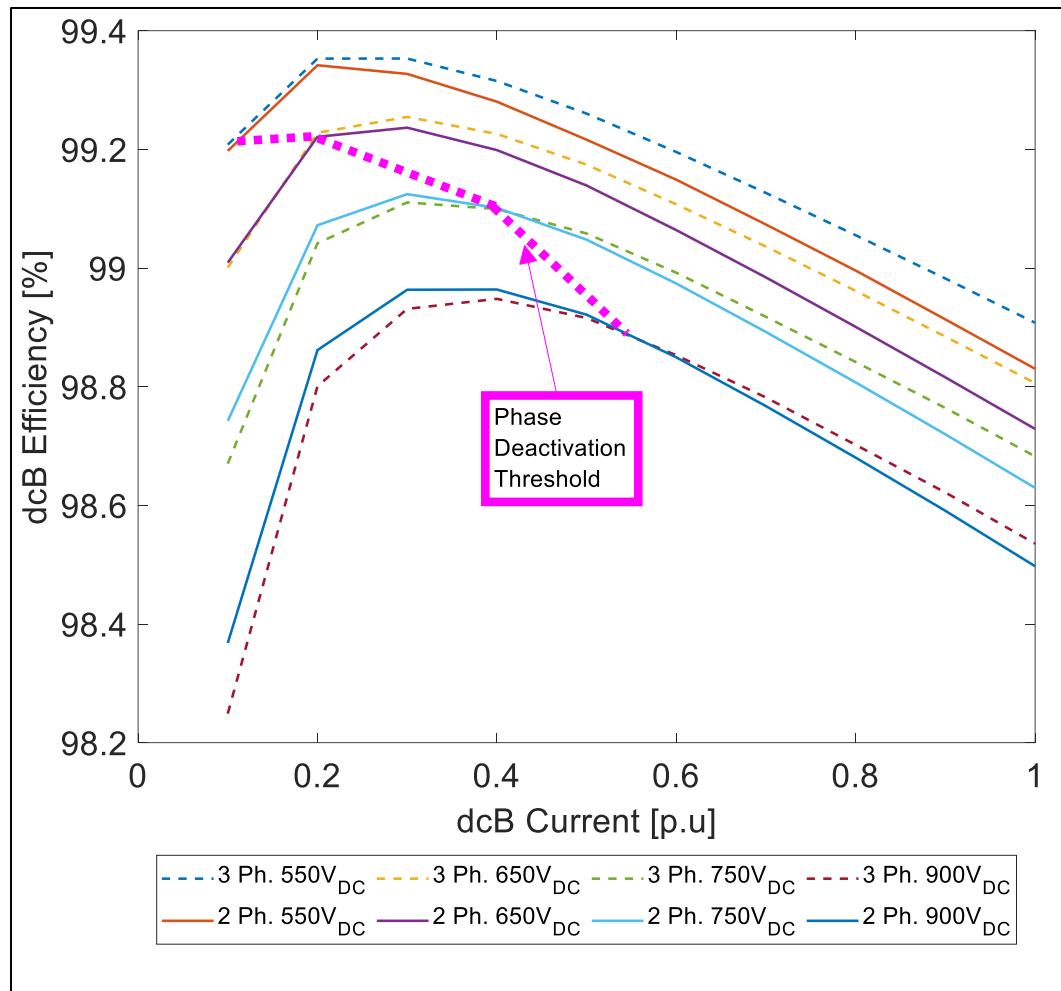

| Figure 4.21: dcB efficiency as current is increased in 3-Phase and 2-Phase operation for various DC link voltages giving the threshold to enable/disable Phase Deactivation. .... | 77  |

| Figure 4.22: Simplified multiport converter composed of a three-cell boost converter (dcB in boost mode) and two-level VSI (inv in motoring mode). ....                           | 80  |

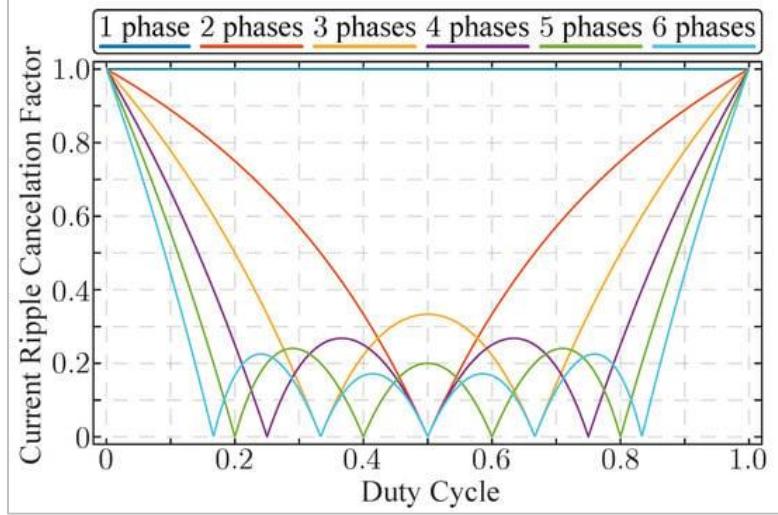

| Figure 4.23: Capacitor current ripple cancellation factor as a function of duty cycle for a different number of active phases [69].....                                           | 81  |

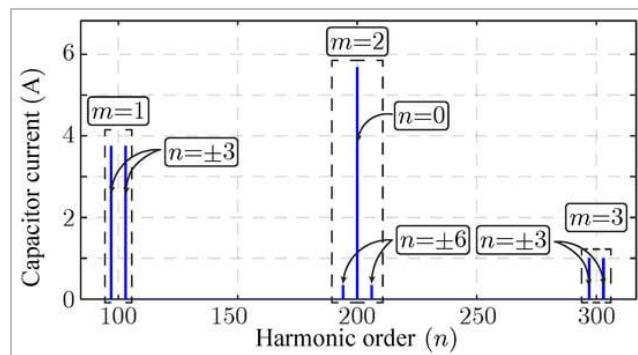

| Figure 4.24: Capacitor current harmonic spectrum decomposition [110]. ....                                                                                                        | 85  |

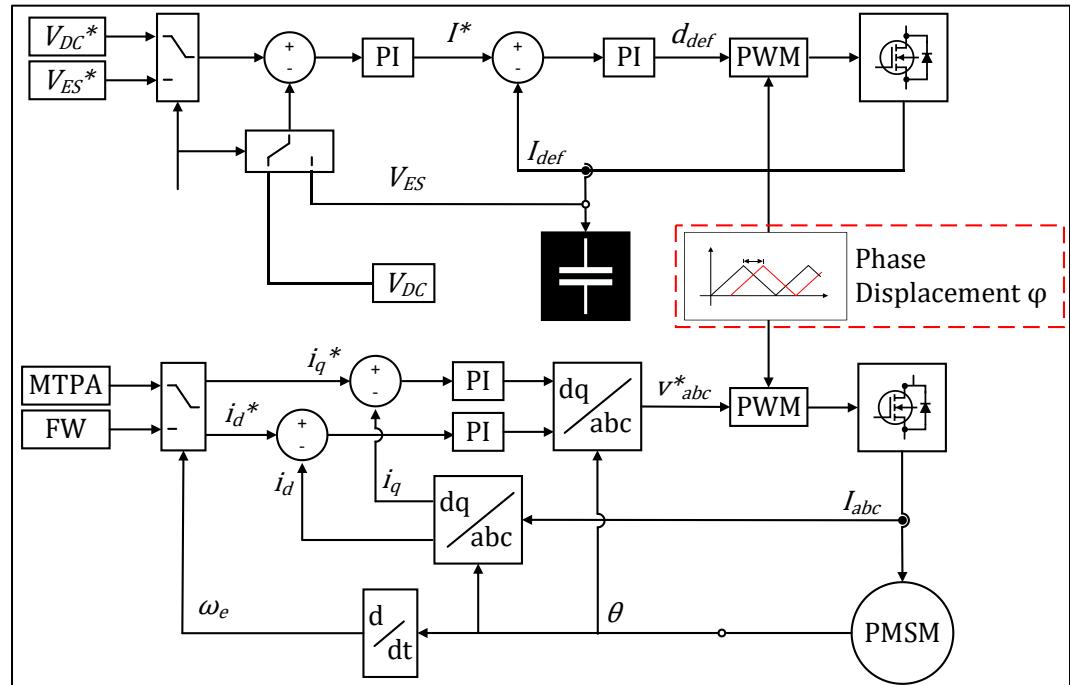

| Figure 4.25: Phase Displacement implementation within Boost converter and inverter controller structure.....                                                                      | 87  |

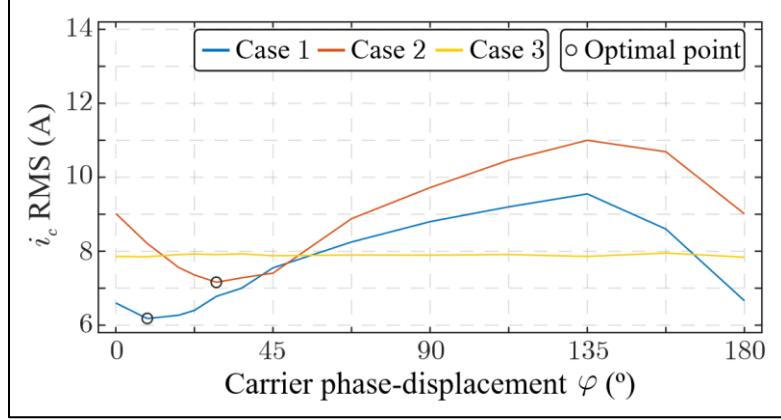

| Figure 4.26: Evaluation of the effective current in the DC link capacitor of a 3-cell interleaved converter[110]. ....                                                            | 89  |

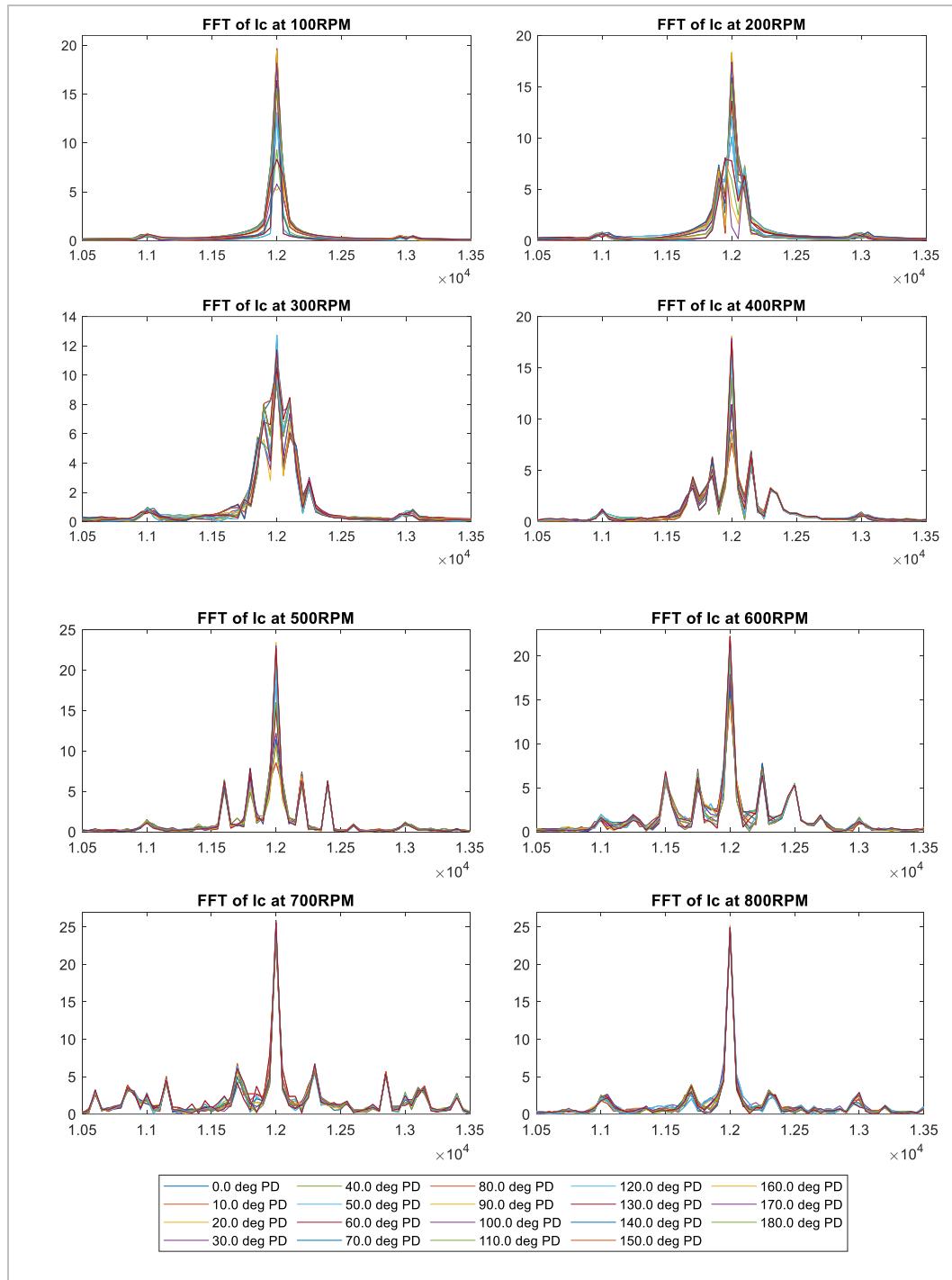

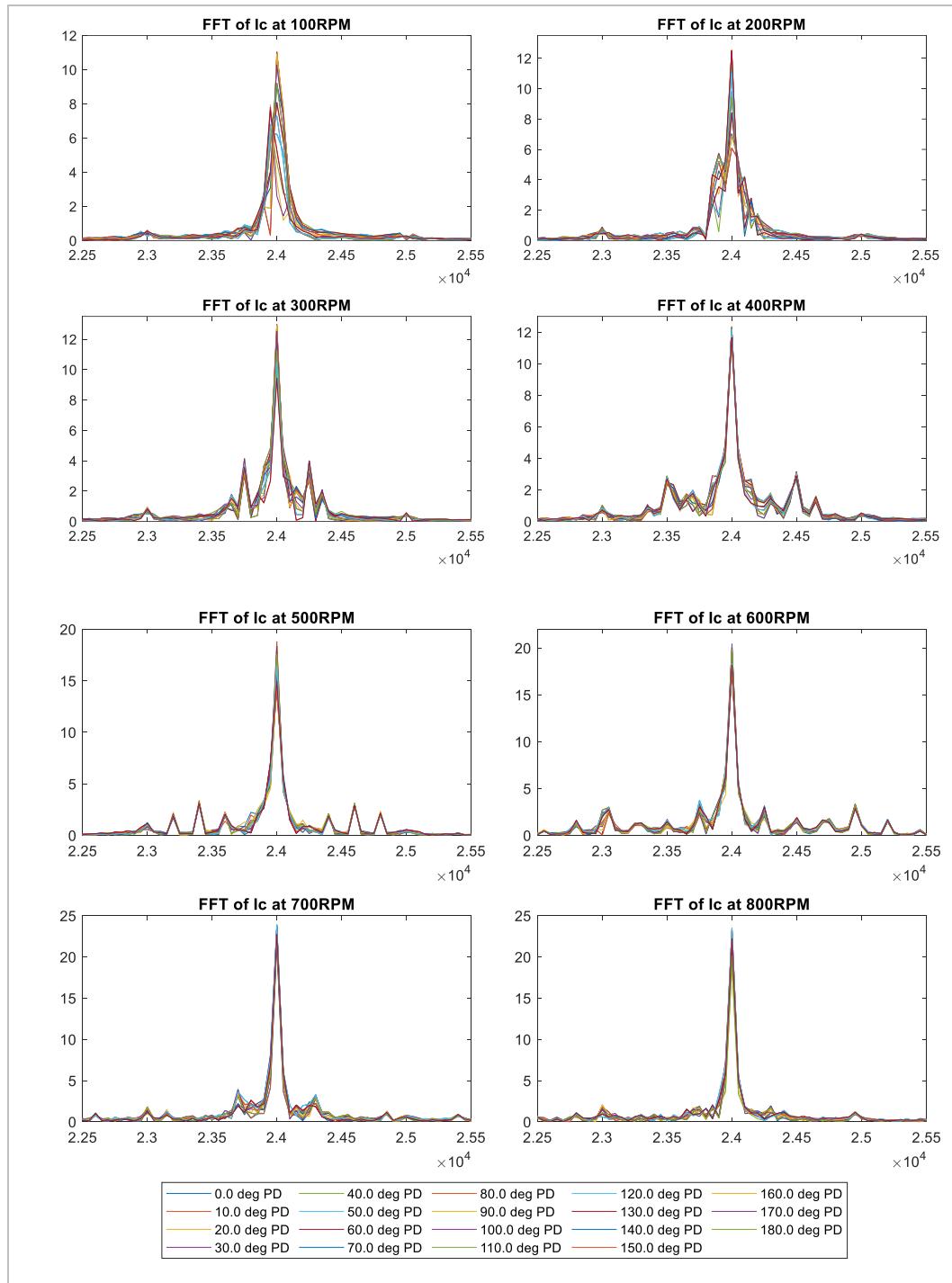

| Figure 4.27: Resultant capacitor current spectrum at 12kHz (Case A) for Phase Displacement angles ranging from 0-180 degrees at PMSM speed ranging from 100-800RPM.....           | 91  |

| Figure 4.28: Resultant capacitor current spectrum at 24kHz (Case B) for Phase Displacement angles ranging from 0-180 degrees at PMSM speed ranging from 100-800RPM.....           | 92  |

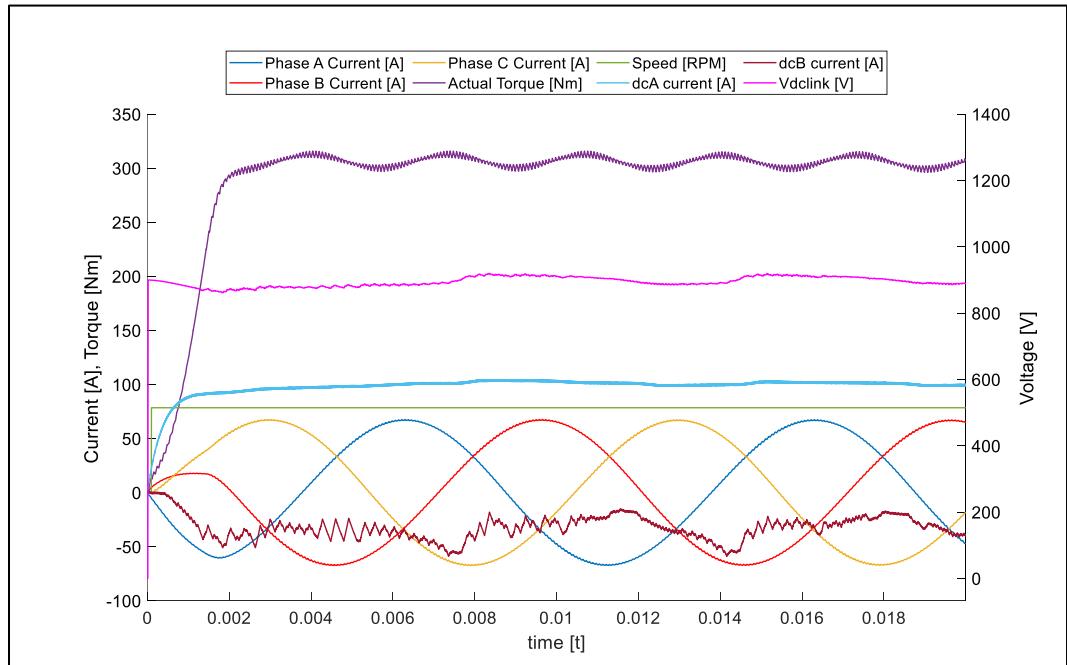

| Figure 4.29. Simulink simulation of single operational point (750RPM and 300Nm) including all elements of design space. ....                                                      | 95  |

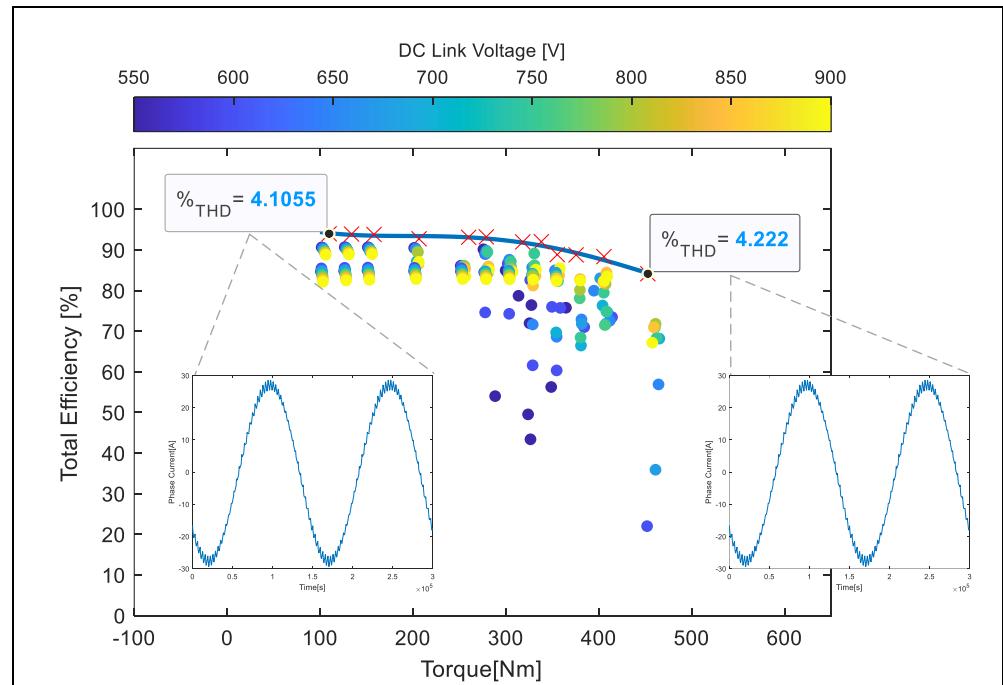

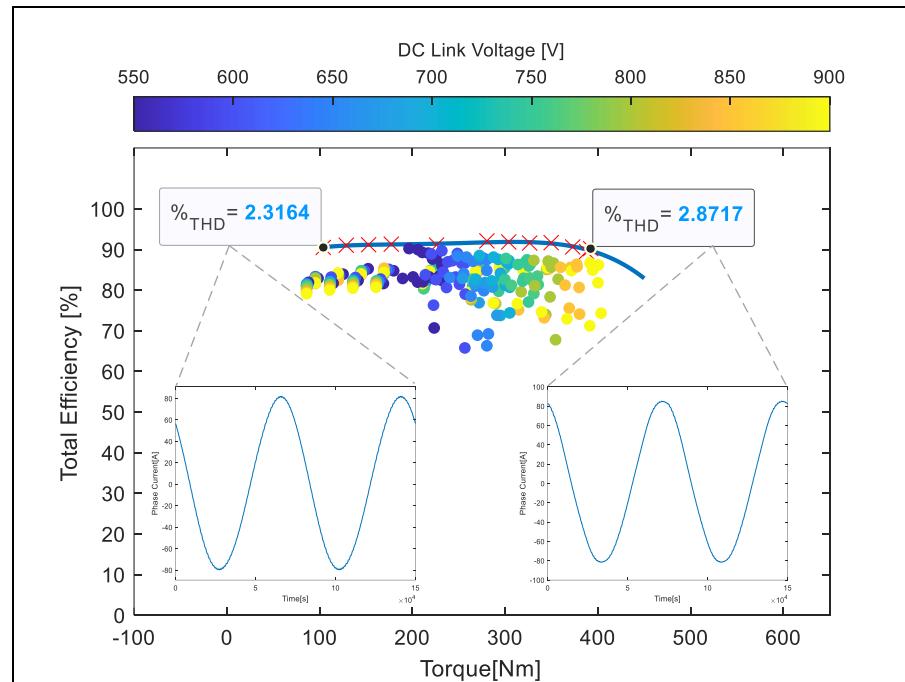

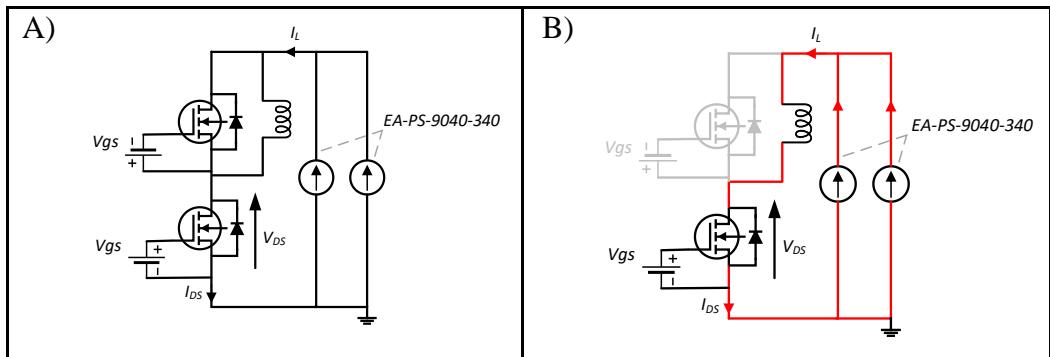

| Figure 4.30. CASE I: Pareto Front of multiport converter operation for varying values of requested driver torque at 500RPM.....                                                   | 99  |

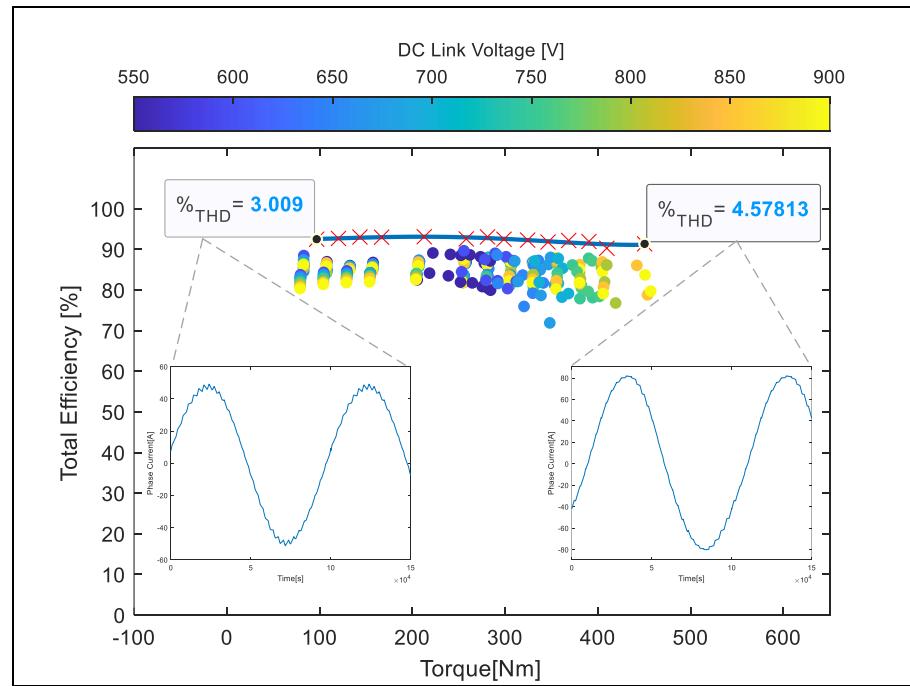

| Figure 4.31. CASE II: Pareto Front of multiport converter operation for varying values of requested driver torque at 750RPM.....                                                  | 100 |

| Figure 4.32. CASE III: Pareto Front of multiport converter operation with and without optimizations for varying values of requested driver torque at 1000RPM.....                 | 101 |

| Figure 4.33. CASE IV: Pareto Front of multiport converter operation for varying values of requested driver torque at 1500RPM.....                                                 | 102 |

|                                                                                                                                                                                                                                                                                                                                                                                              |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

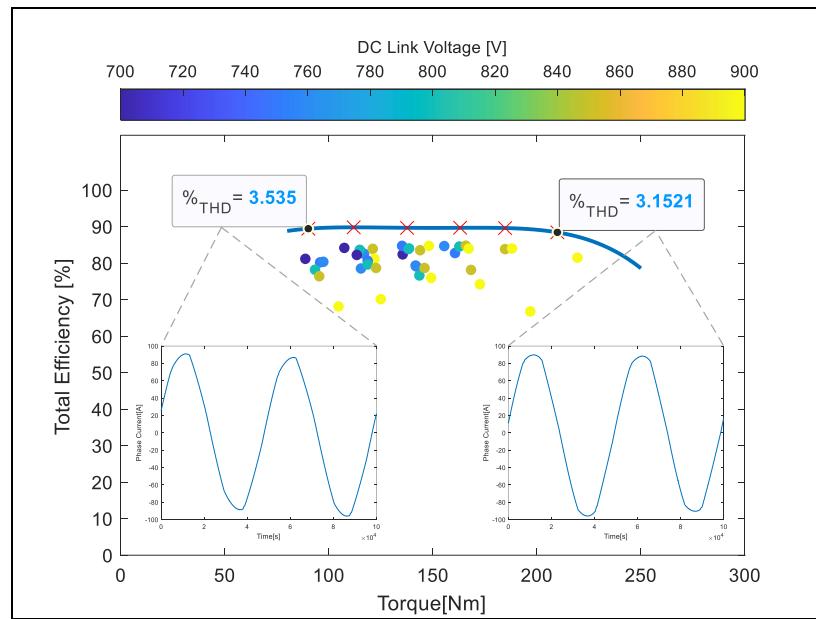

| Figure 5.1. A) EA-PS 9040-340 Power Supply, B) instrumented power module test rig, C) thermocouple temperature measurement and D) Thermal imaging capture techniques.....                                                                                                                                                                                                                    | 106 |

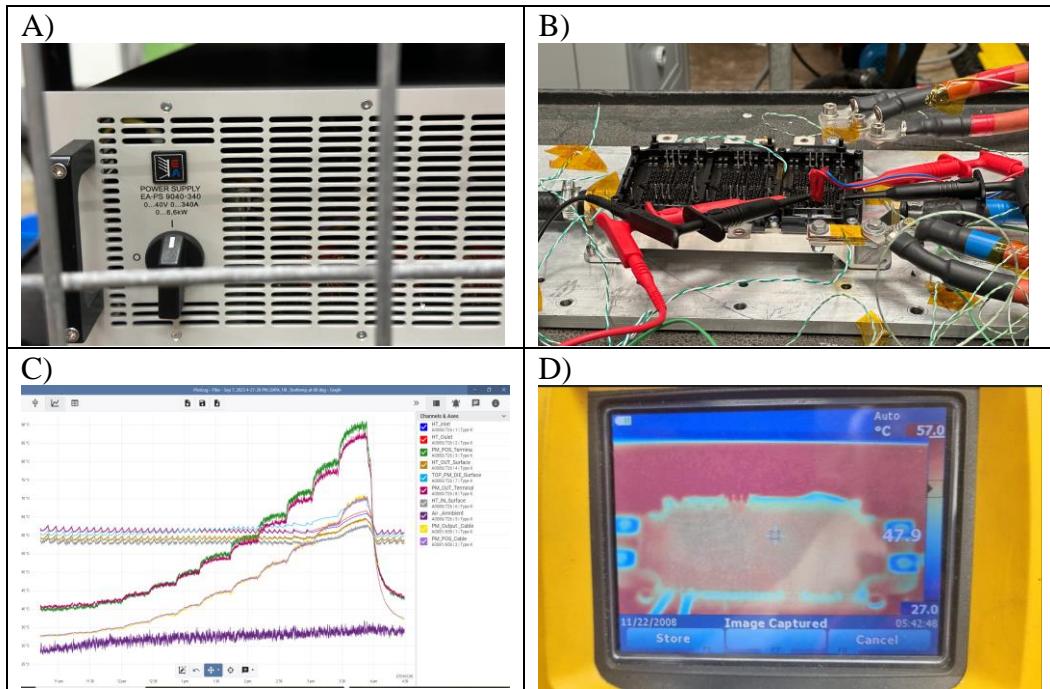

| Figure 5.2. Schematic with power loss measurement points (A). Current flow direction during test operation. ....                                                                                                                                                                                                                                                                             | 106 |

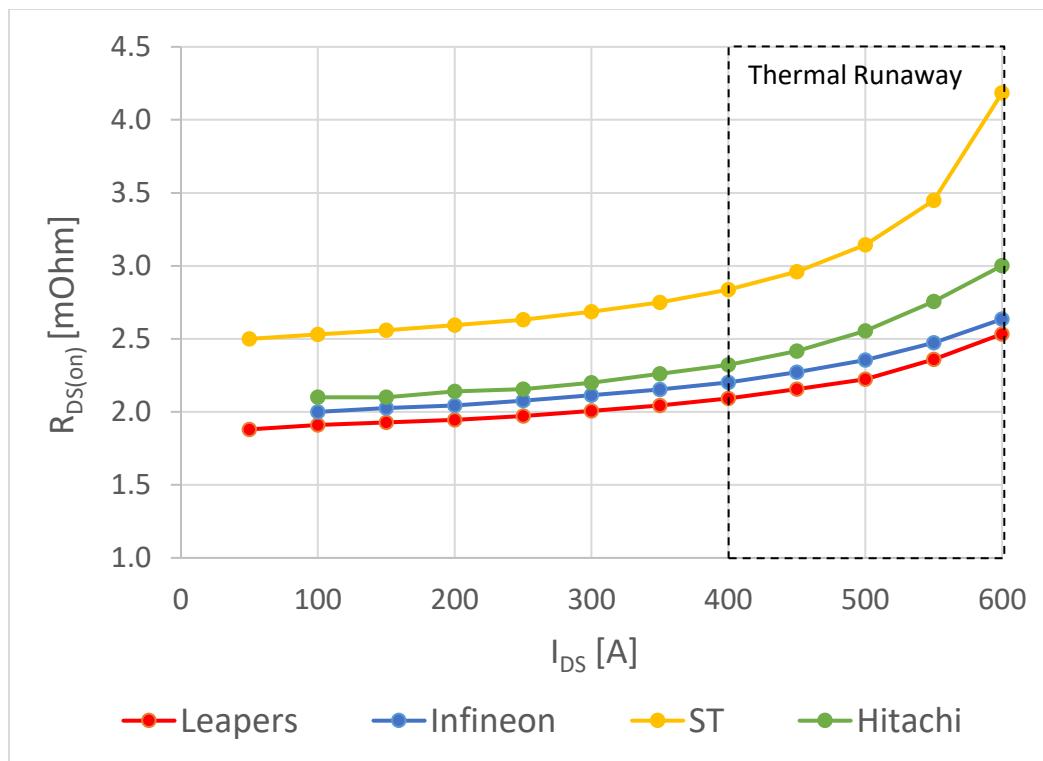

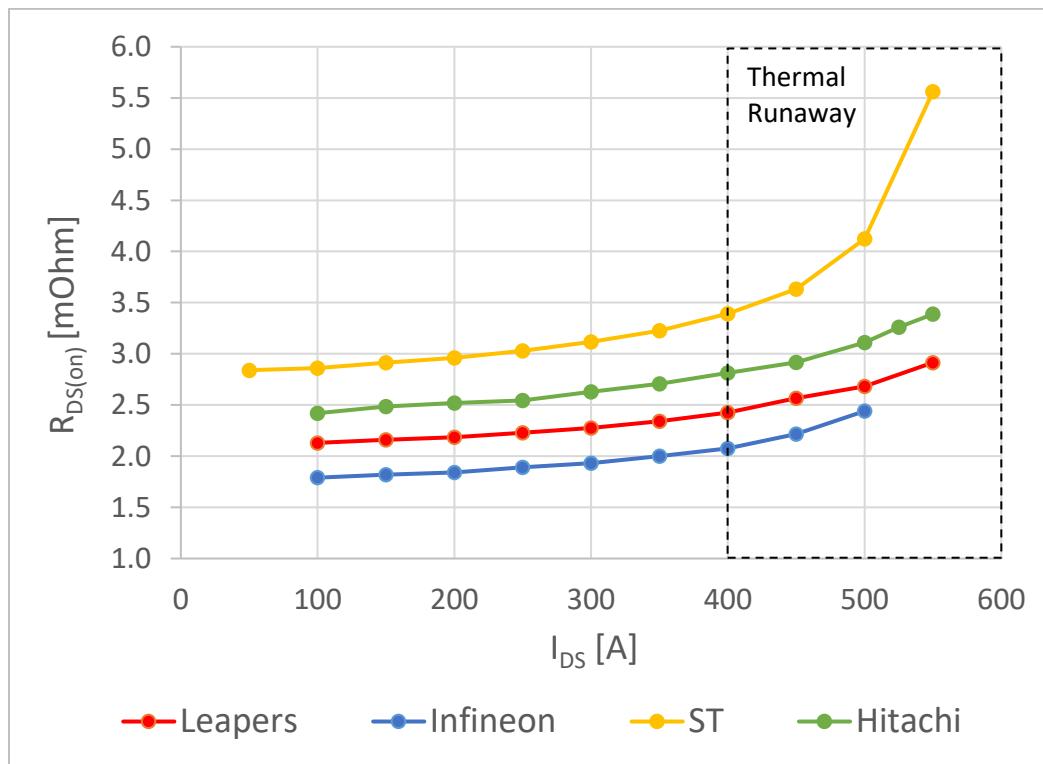

| Figure 5.3. Experimentally derived $R_{DS(on)}$ profile vs $I_{DS}$ characteristic at 25°C. ....                                                                                                                                                                                                                                                                                             | 109 |

| Figure 5.4. Experimentally derived $R_{DS(on)}$ profile $I_{DS}$ characteristic at 65°C ....                                                                                                                                                                                                                                                                                                 | 109 |

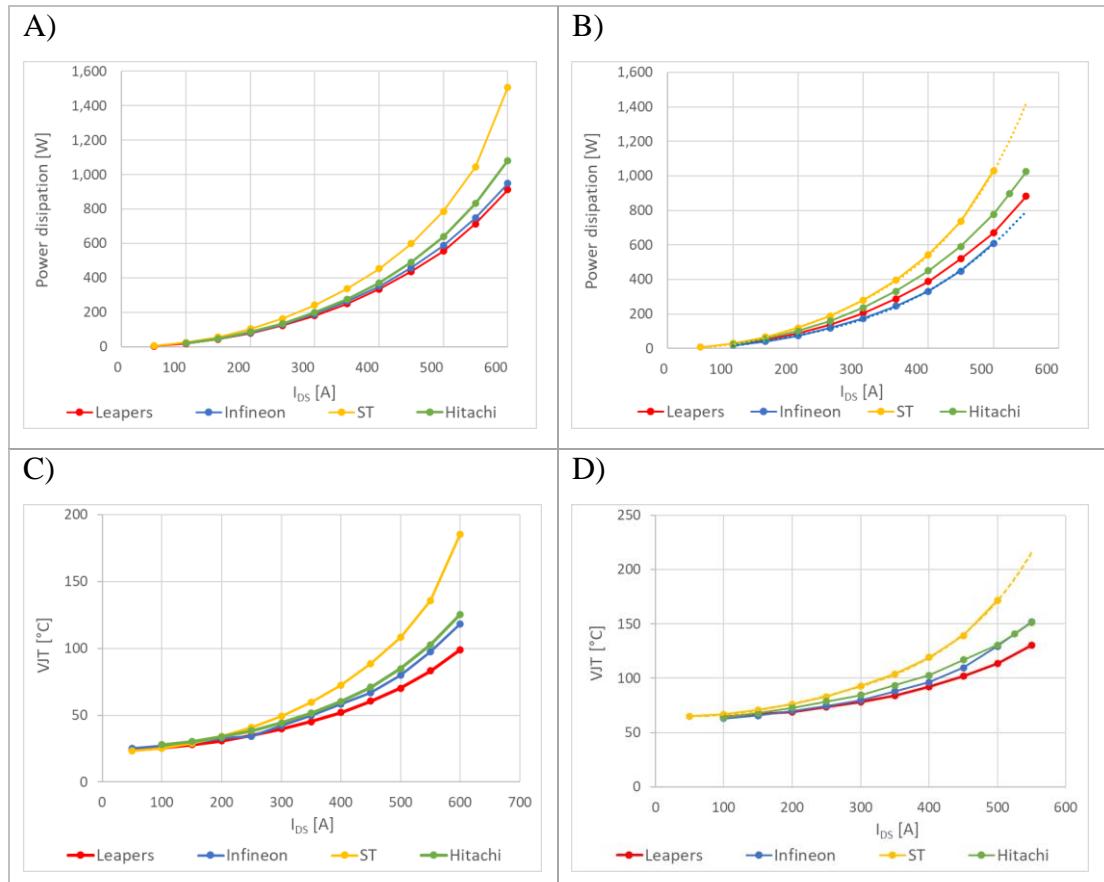

| Figure 5.5. Power dissipation and Virtual Junction Temperature (VJT) of power modules as $I_{DS}$ current is increased for 25°C (A and C respectively) and 65°C (B and D respectively) coolant temperature. ....                                                                                                                                                                             | 111 |

| Figure 5.6. DPT hardware setup. ....                                                                                                                                                                                                                                                                                                                                                         | 113 |

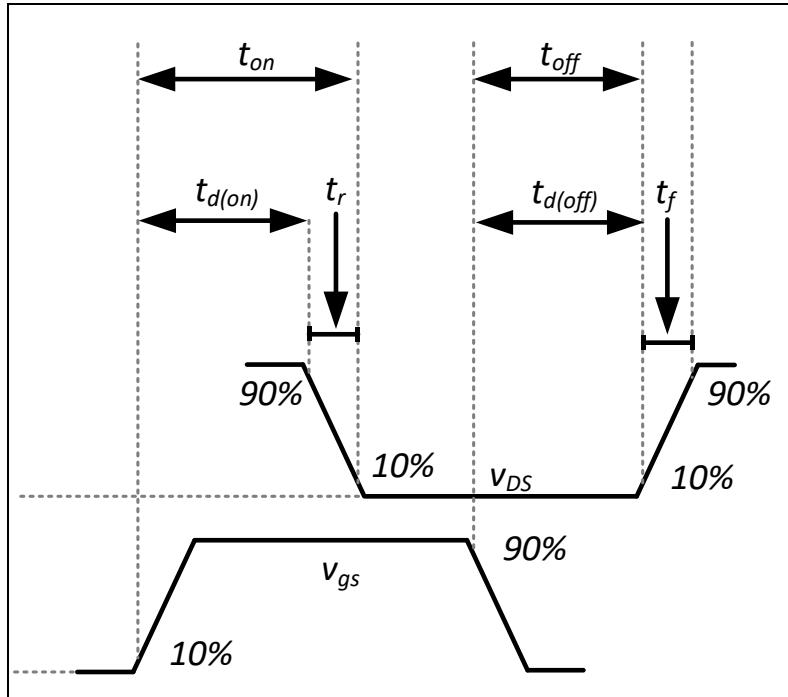

| Figure 5.7. Industry standard to measure turn-on and turn-off parameters [132]. ....                                                                                                                                                                                                                                                                                                         | 114 |

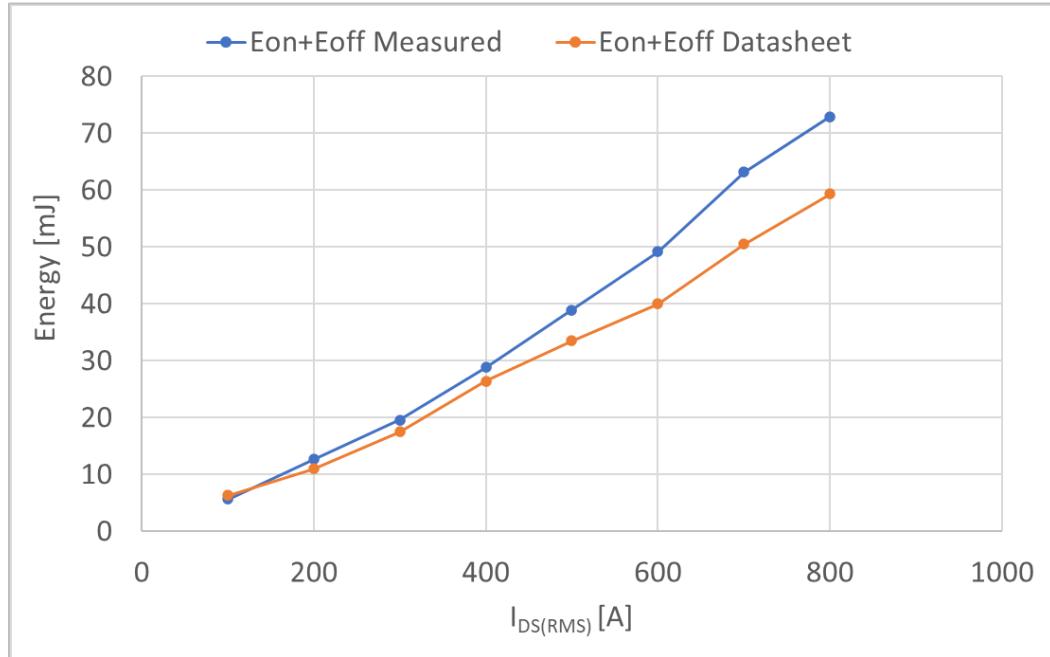

| Figure 5.8. Datasheet vs. measured Leapers SiC DFS02FB12HDW1 HYBRIDPACK sum switching energy emissions at $V_{DC} = 600V$ , $T_J = 25^{\circ}C$ .....                                                                                                                                                                                                                                        | 115 |

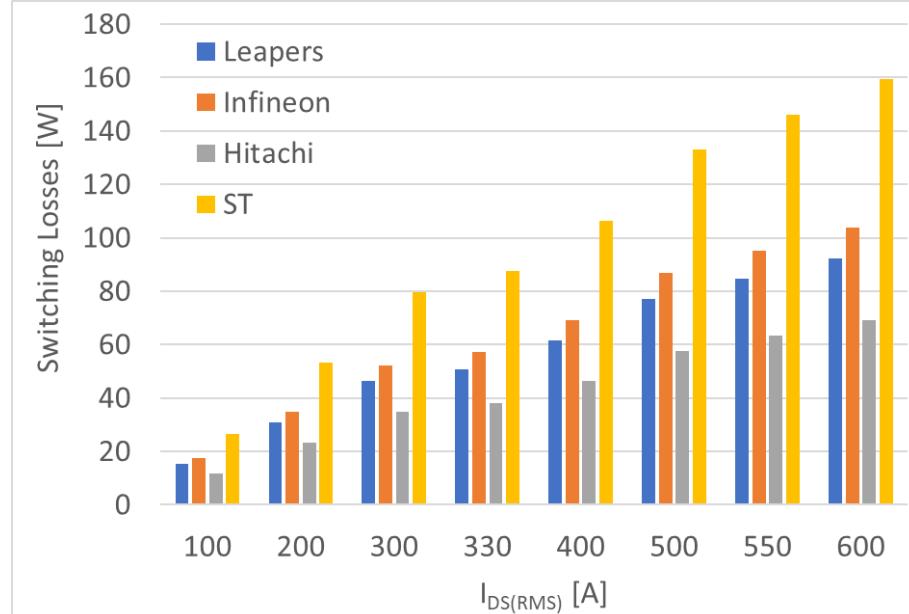

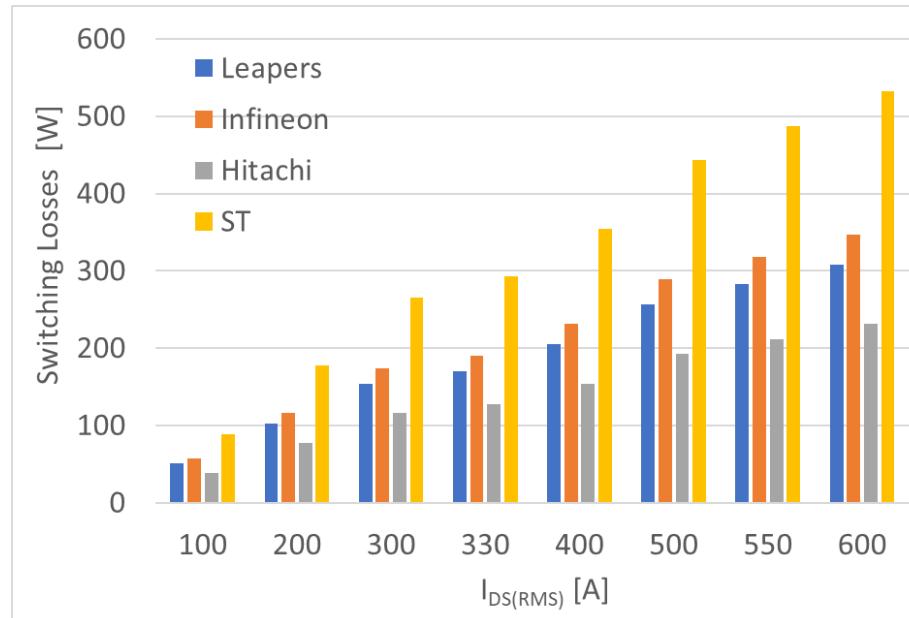

| Figure 5.9. Tabulated switching losses for $V_{DC} = 700V$ , $F_{sw} = 3kHz$ for $I_{DS}$ range : 100-600A .....                                                                                                                                                                                                                                                                             | 116 |

| Figure 5.10. Tabulated switching losses for $V_{DC} = 700V$ , $F_{sw} = 10kHz$ for $I_{DS}$ range : 100-600A .....                                                                                                                                                                                                                                                                           | 116 |

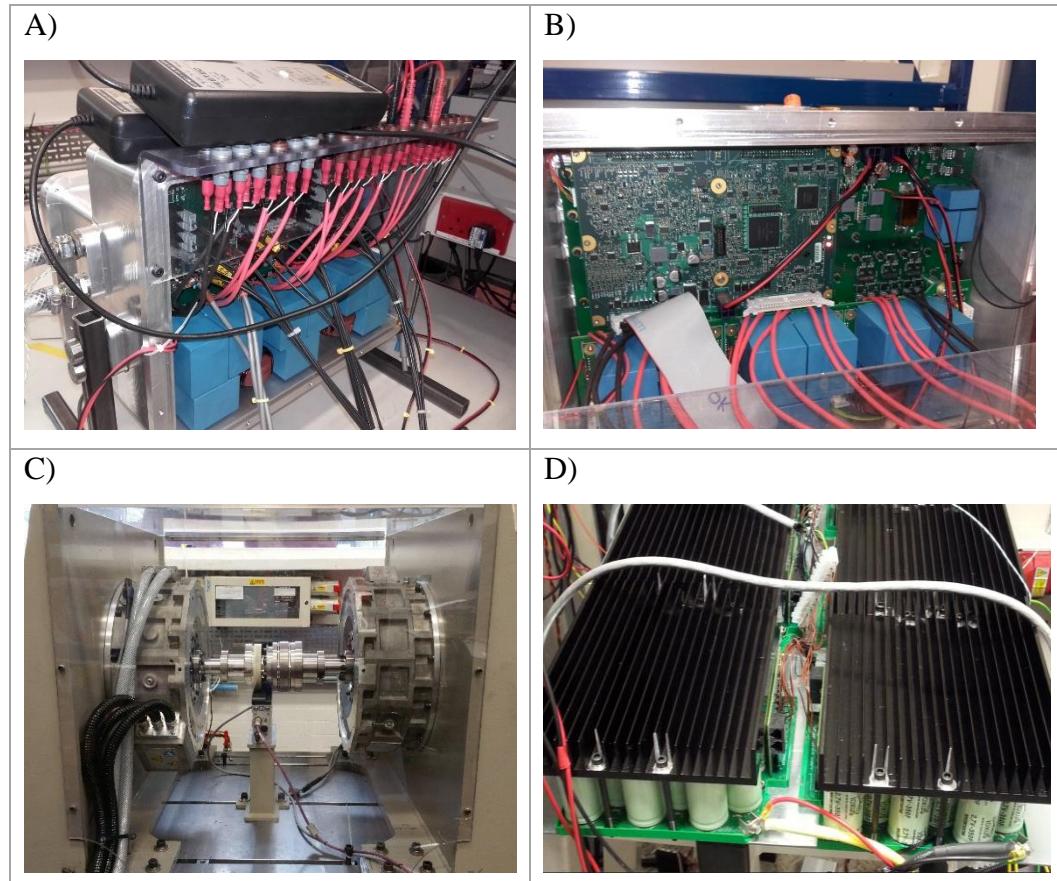

| Figure 5.11. A) Multiport converter (D.U.T), B) Test instrumentation connections and converter controller, C) Back-to-back PMSM test bed and D) ultracapacitor bank during validation tests. ....                                                                                                                                                                                            | 118 |

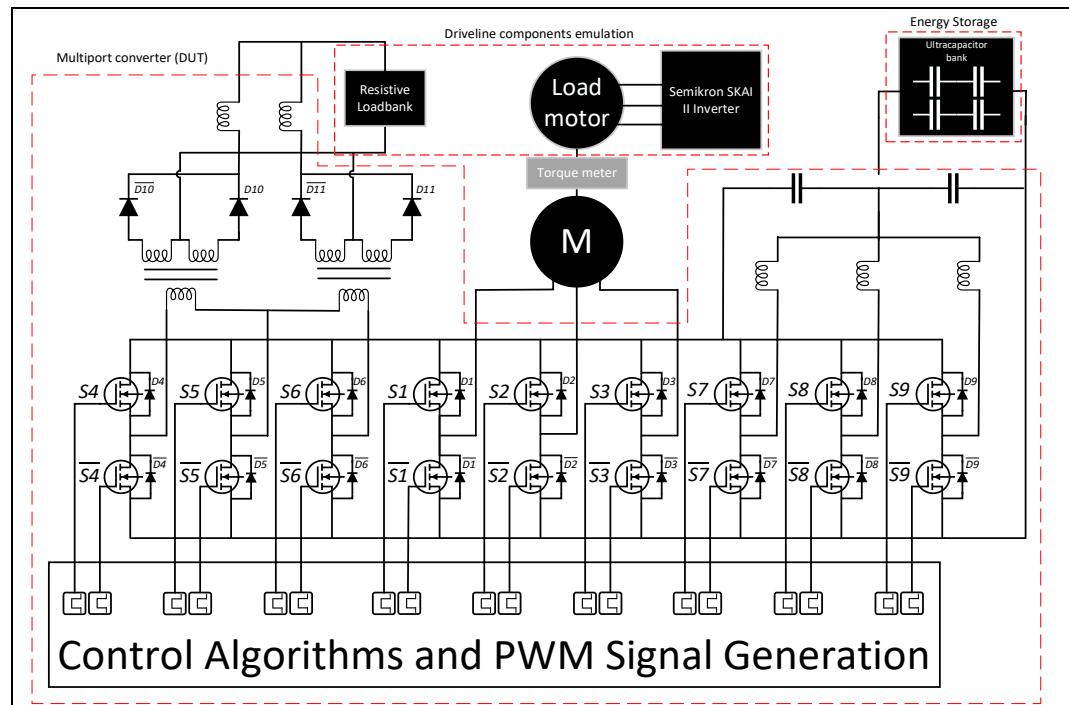

| Figure 5.12. Multiport converter test setup.....                                                                                                                                                                                                                                                                                                                                             | 119 |

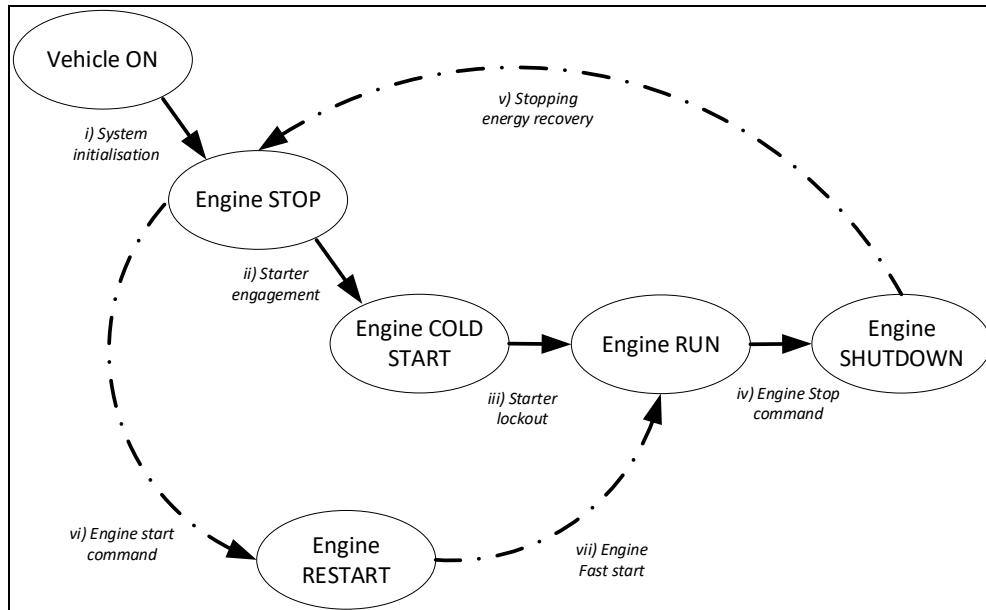

| Figure 5.13. Hybrid drivetrain mode transitions.....                                                                                                                                                                                                                                                                                                                                         | 120 |

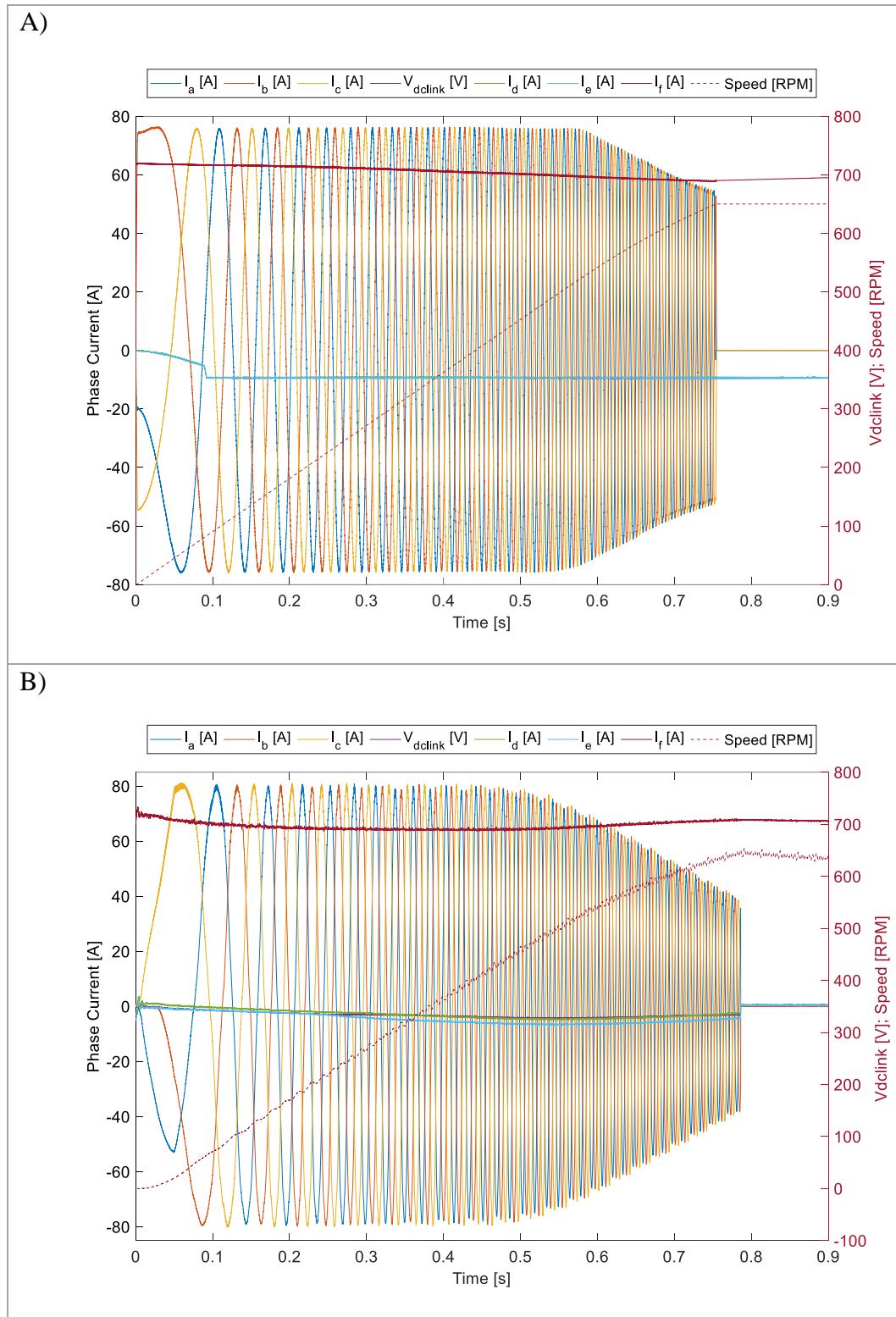

| Figure 5.14. Speed, voltage and current profile of multiport electric drive during Engine Restart (Inverter-Motoring, dcB- Boost). (A) Simulated Results: Inverter current, $I_{abc}$ , DC link voltage, machine speed and dcB current, $I_{def}$ in motoring mode. (B) Experimental Results: Inverter current, $I_{abc}$ , DC link voltage, machine speed and dcB current, $I_{def}$ . .... | 123 |

|                                                                                                                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

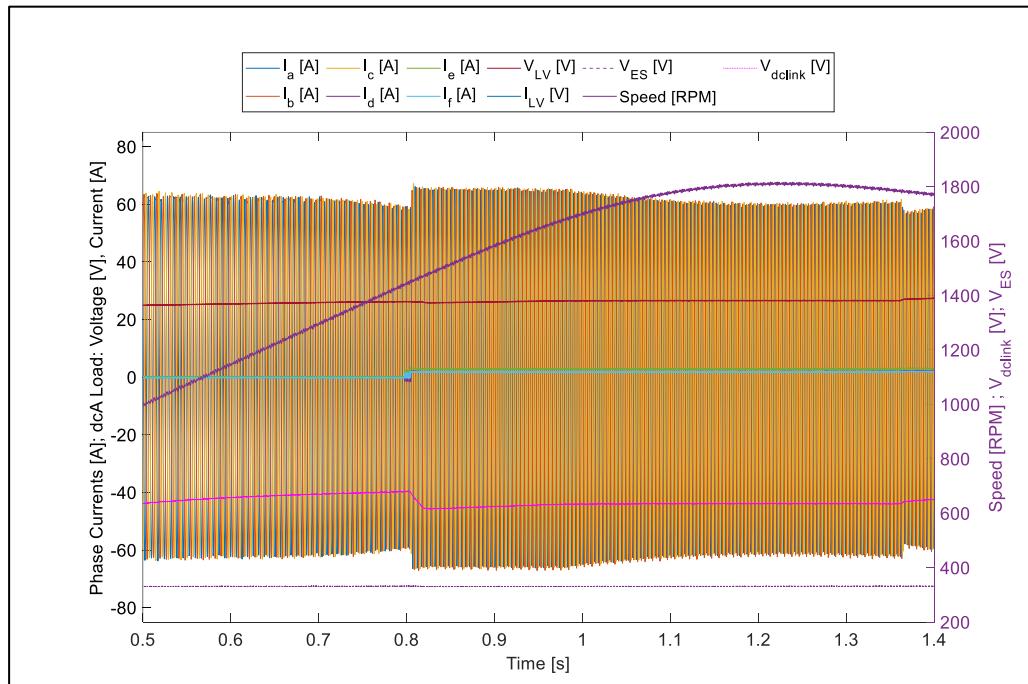

| Figure 5.15. Experimentally measured phase currents of Inverter in regeneration mode, phase currents of dcB in Buck mode and output current of dcA in Buck mode. .... | 125 |

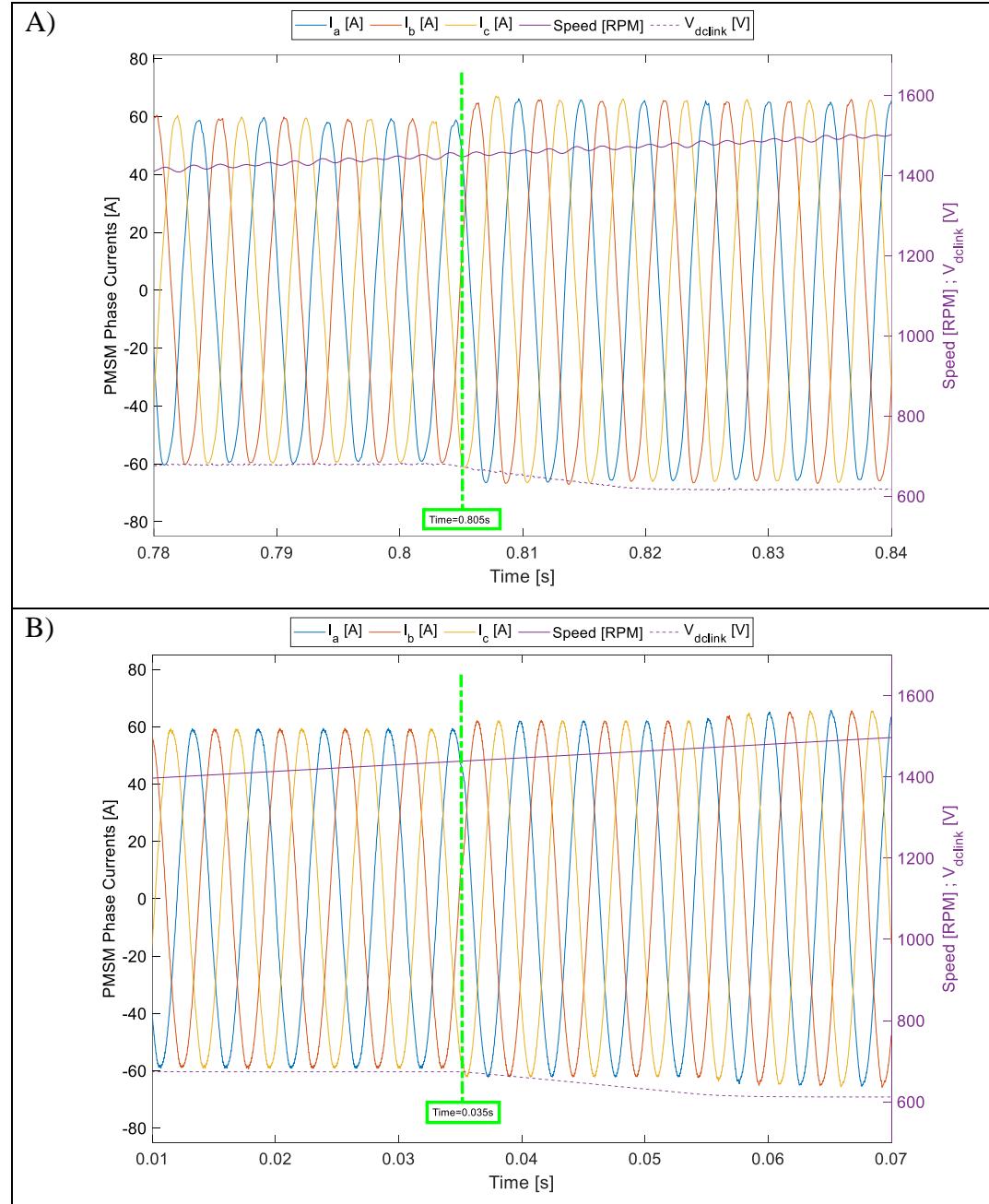

| Figure 5.16. Experimental (A) and Simulated (B) inverter phase currents as DC link voltage and speed are varied during PMSM acceleration event. ....                  | 126 |

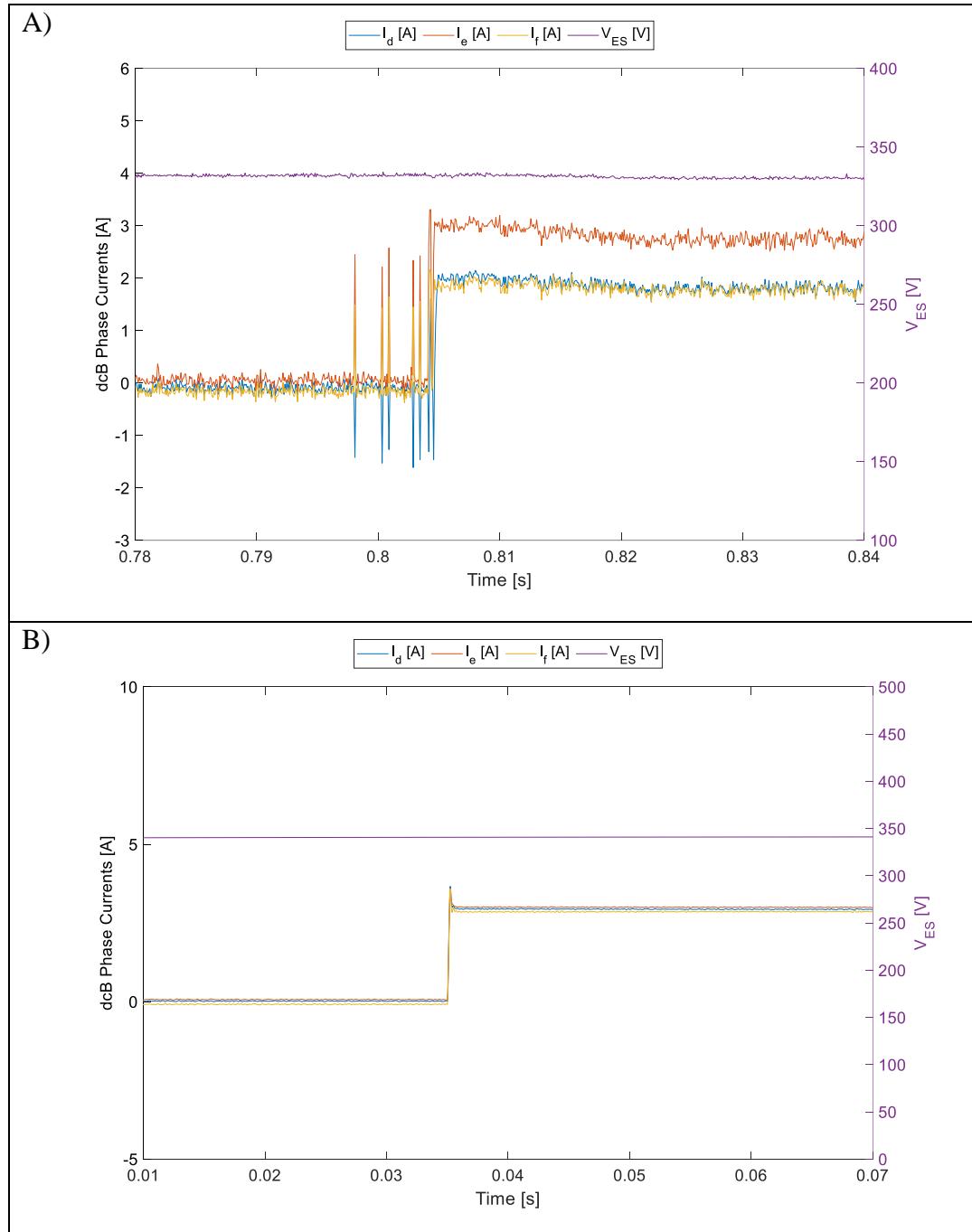

| Figure 5.17. Experimental (A) and Simulated (B) dcB phase currents as DC link voltage and speed are varied during PMSM acceleration event. ....                       | 128 |

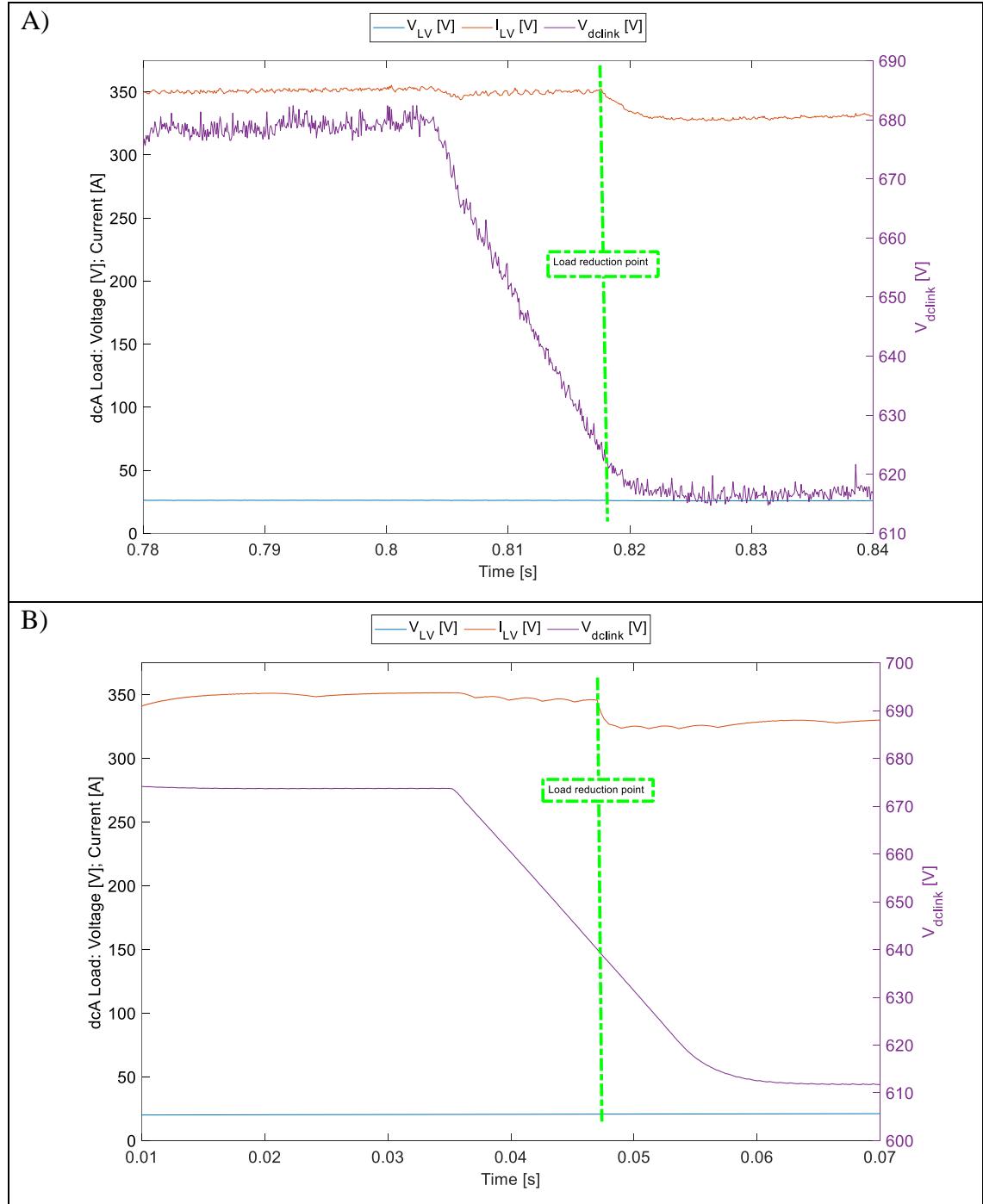

| Figure 5.18. Experimental (A) and Simulated (B) dcA load current as DC link voltage and speed are varied during PMSM acceleration event. ....                         | 130 |

| Figure 5.19. A full-scale production-ready Multiport converter mounted in the engine compartment of the test vehicle for vehicle performance baseline testing. ....   | 131 |

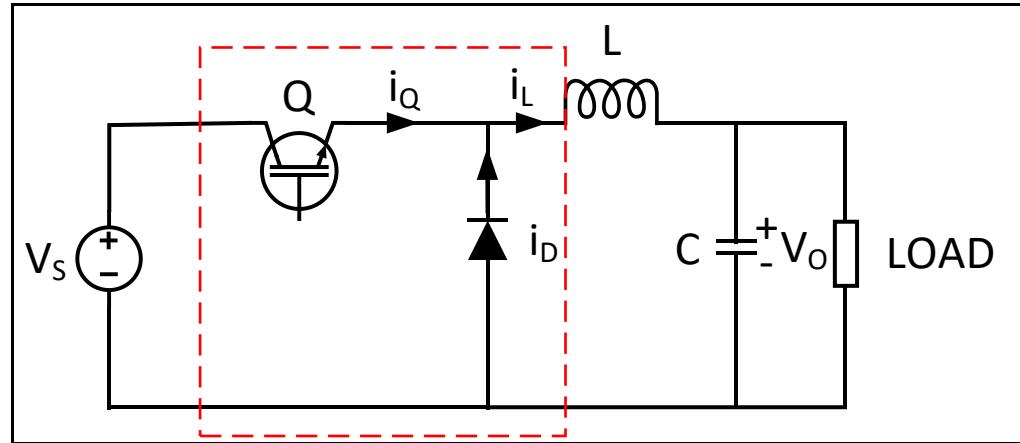

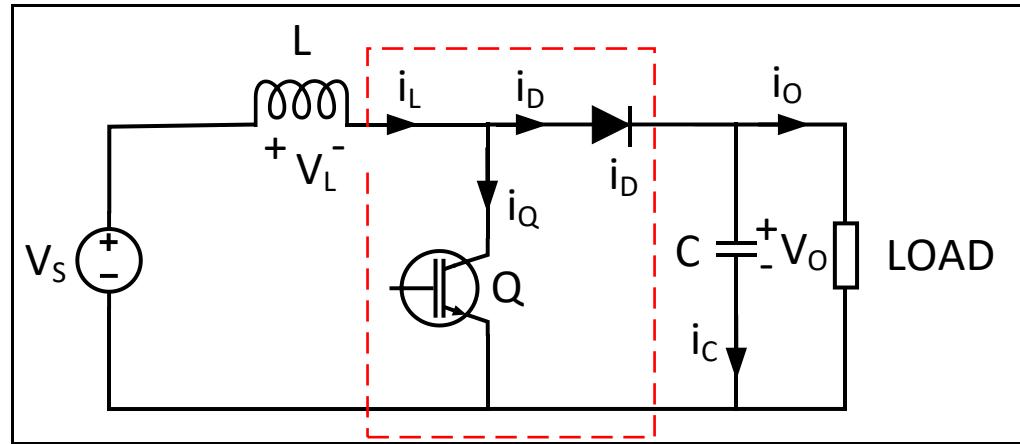

| Figure C.1. Buck converter equivalent circuit. Switch circuit marked by red box. ....                                                                                 | 140 |

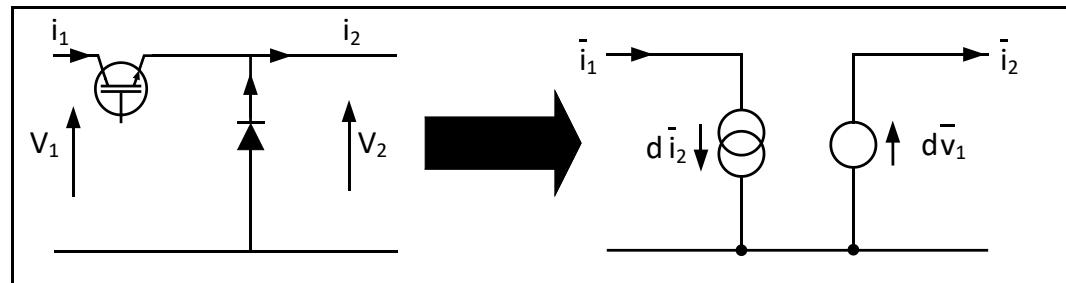

| Figure C.2. Extracted switch model (left) and equivalent averaged switch circuit with controlled sources (right). ....                                                | 140 |

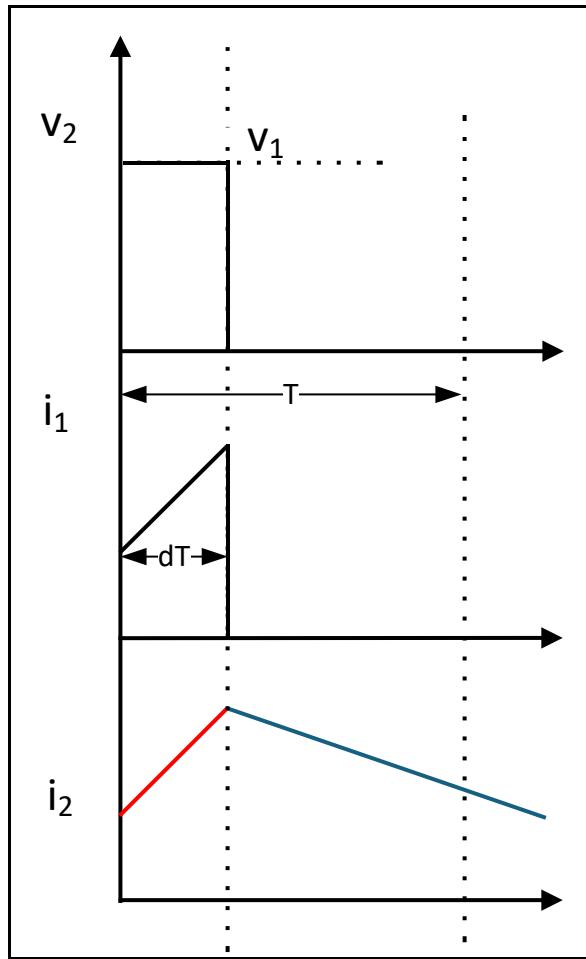

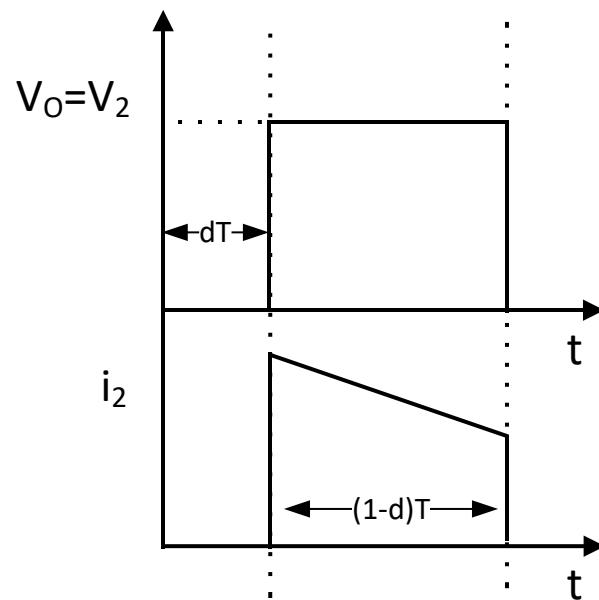

| Figure C.3. Buck converter current and voltage waveform during one switching period, T. ....                                                                          | 141 |

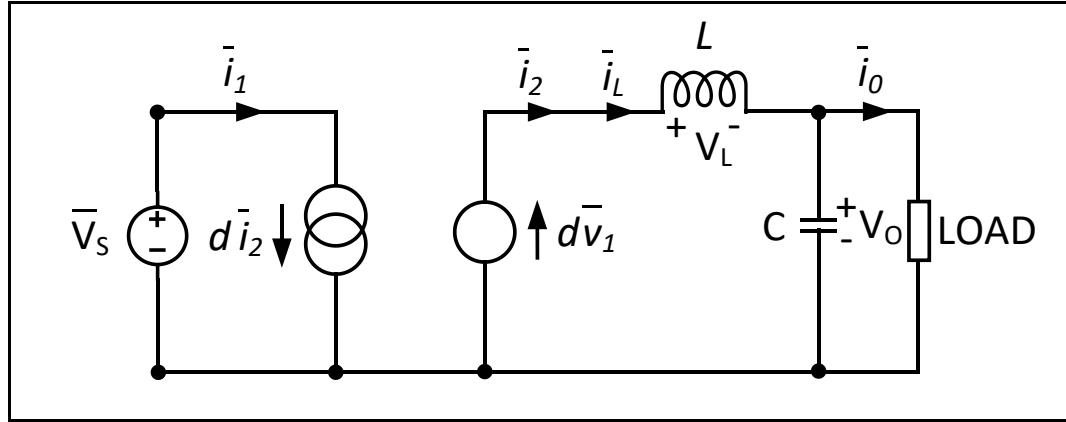

| Figure C.4. Buck Converter average model. ....                                                                                                                        | 142 |

| Figure C.5. Buck converter AC perturbation model. ....                                                                                                                | 143 |

| Figure C.6. Boost converter equivalent circuit. Switch circuit marked by the red box. ....                                                                            | 144 |

| Figure C.7. Boost converter current and voltage waveform during one switching period, T. ....                                                                         | 144 |

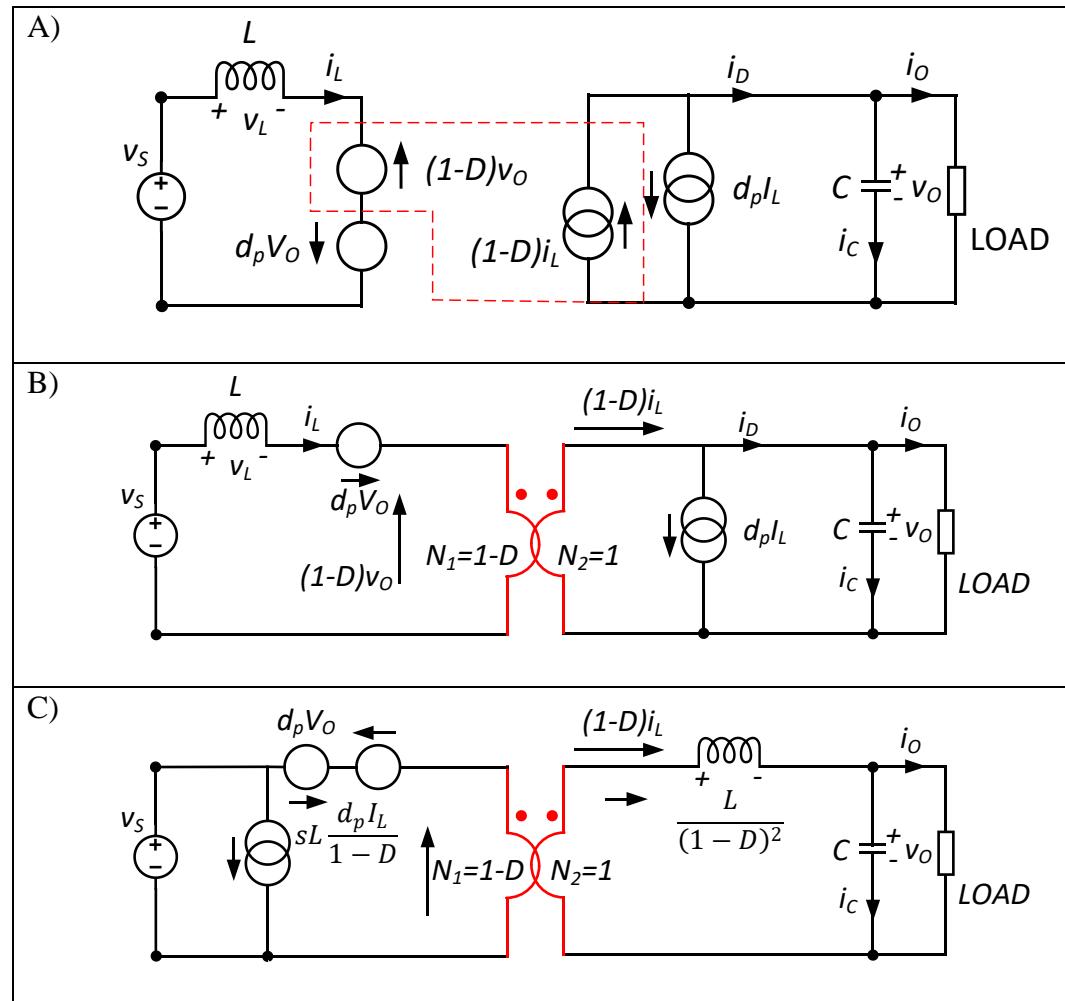

| Figure C.8. Boost converter AC equivalent models: Initial perturbation model (A), introduction of the coupling relations (B) and final average model (C). ....        | 145 |

## List of Tables

|    |                                                                                             |     |

|----|---------------------------------------------------------------------------------------------|-----|

| 1  | Functionality of converter components.....                                                  | 10  |

| 2  | Comparison of DSC Power Module Packaging Technologies....                                   | 16  |

| 3  | Inverter and PMSM Parameters.....                                                           | 31  |

| 4  | MOOP Parameters.....                                                                        | 47  |

| 5  | Thermal Network Parameters.....                                                             | 61  |

| 6  | Max/Min values for Simulation Sweep.....                                                    | 68  |

| 7  | Evaluated States to validate effectiveness<br>of Phase Displacement optimization [109]..... | 88  |

| 8  | Evaluated Operational Points for Phase Displacement.....                                    | 90  |

| 9  | Case A Results: Optimum Phase Displacement Angle for<br>Minimum Capacitor Current.....      | 94  |

| 10 | Case B Results: Optimum Phase Displacement Angle for<br>Minimum Capacitor Current.....      | 94  |

| 11 | MOOP Parameters.....                                                                        | 97  |

| 12 | Conduction Loss Test Parameters.....                                                        | 108 |

| 13 | Switching Loss Test Parameters.....                                                         | 113 |

| 14 | Driveline Mode Description.....                                                             | 120 |

## Abstract

Environmental concerns and energy efficiency have been driving the transportation innovation in the past decades. In this framework, hybrid city transport has been receiving the attention of the industry. The challenges for this application, are the required high-power density, lower maintenance cost and the high-temperature environment due to the integration with the internal combustion engine.

The main goal of the thesis is to propose, demonstrate and verify a combination of control techniques to maximise the performance of the multiport converter in all phases of on-vehicle operation.

In the first part of this work, a multiport converter is proposed to realise the requirements of the automotive industry to achieve greater performance in driveline electrification. The platform suggests the combination of previously discrete power electronics converter modules into one physical package commonising parts such as the microcontroller, DC link, heatsink and busbars. Therefore, for completeness, the current state-of-the-art of converter technology is presented along with challenges and their mitigation within the industry.

The central part of the thesis focuses on the optimisation framework of the converter. Multi-objective Optimisation (MOO) techniques are used to define and describe the optimisation goals. A comprehensive simulation model is built and verified both at component (power module and inductor) and system level (complete multiport converter) satisfying the mandatory requirement for clear objectives and toolset for validation of the optimisation control techniques proposed. Three distinct strategies are investigated including Phase Deactivation,

Phase Displacement and the utilisation of the optimum parameter set derived from the MOO study.

In the latter part of the work the performance and optimisation gains are evaluated through a combination of simulation and experimental data. The results show a distinct improvement comparing against conventional, non-optimised operation, demonstrating strong applicability of the techniques derived in the development of a high efficiency and high energy density automotive multiport converter.

## Acknowledgements

*This work is dedicated to the memory of Dr. Alessandro Costababer, my supervisor originally assigned, who sadly passed away during the PhD. His immense knowledge, dedication and sound guidance laid the foundations for this work.*

The last eight years spent pursuing a part-time PhD with the University of Nottingham UK, alongside a full-time job, have not been easy. However, when I reflect on my academic journey, through all the unknowns and difficulties along the way, I realise that these challenges have taught me so many skills and values which I will now take to my career and treasure for the rest of my life.

The PhD was made possible by the joint funding by Cummins Inc. and the University of Nottingham. Therefore, I would first like to thank Dr. Neil Brown, Brad Palmer and Krzysztof Paciura from Cummins Inc. and Professor Chris Gerada, Dr. Michael Galea and Dr. Gaurang Vakil from the University of Nottingham, as without their efforts the work wouldn't have even commenced.

Words cannot express my gratitude to my supervisor, Professor Giampaolo Buticchi who generously provided invaluable guidance and feedback no matter the time of day nor geographical location. His acute attention to detail and consistent mentorship was crucial towards the completion of the PhD.

Many thanks to researchers from the university, Dr. Andrew Trentin and Dr. Marco Degano for sharing their knowledge and support during the 6-month test activities on the machine test rig. Likewise, I wish to thank Dr. Adam Walker for support with electromagnetic design analysis and simulation work. Also, thanks to Dr. Daniel Fallows for valuable advice on the research activities.

Lastly, I would be remiss in not mentioning my family, especially my wife, parents, and brother. Their patient understanding and unwavering belief in

me has kept my spirits high throughout this process. I would also like to thank my dog, Pippin for all the entertainment and emotional support. My PhD journey wouldn't have been possible without all of you.

# Chapter 1

## Introduction

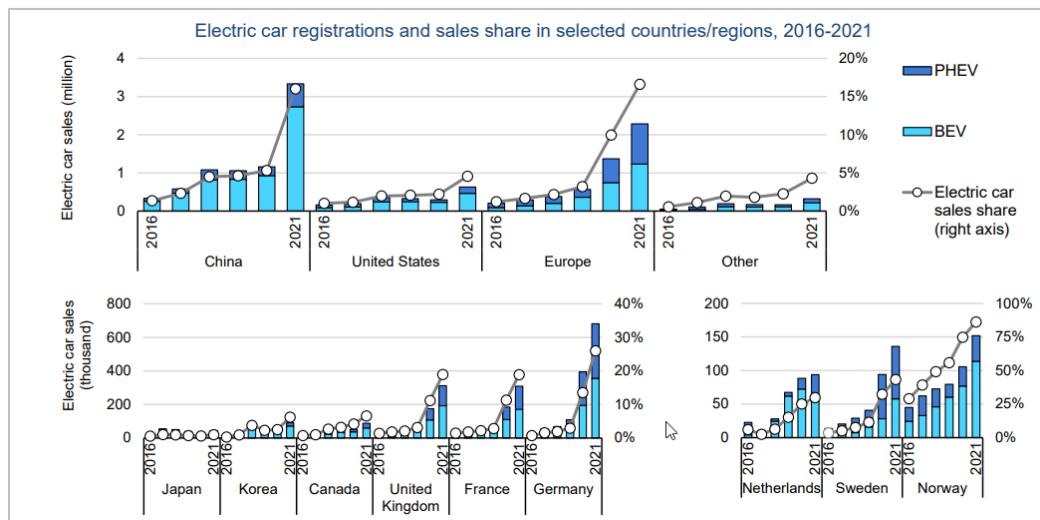

The electric transport sector is continuing to grow and assume increasing market share. Despite the proliferation of a global health pandemic, collective electric vehicle sales worldwide doubled in 2021 from the previous year to a new record of 6.6 million and continued growing strongly through 2022 particularly in China, Europe, and the United States as illustrated in Figure 1.1.

Figure 1.1: Electric car registrations and sales share in selected countries/regions, 2016-2021[1]

According to the International Energy Agency, the robust growth is driven by two key factors[2]: i) ever increasing support for transition to electric mobility, in the form of financial support for environmental regulatory measures such as policies set by the UN Climate Change conference (COP26) and China New Energy Vehicle (NEV) and ii) technological enablers such as electrical drive design architecture and developments in battery chemistry and manufacturing techniques;

both important factors in narrowing the cost gap between electric vehicles (EV) and their conventional Internal Combustion Engine (ICE) counterparts[1].

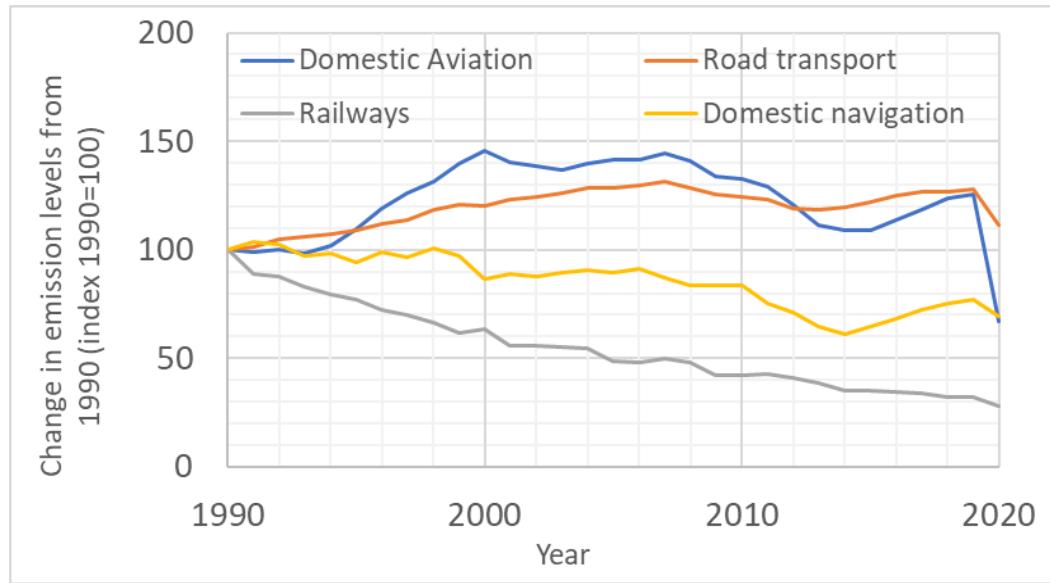

Figure 1.2. Greenhouse gas emissions from transport in the EU, by transport mode and scenario as published by the European Environment Agency[3].

## 1.1 Motivation for Carbon Reduction

Greenhouse gas (GHG) emissions within the road transport sector have been the highest in Europe since the 1990s compared to other modes of transport – such as aviation, maritime and rail according to data published by the European Environment Agency. This trend continued to rise, as shown in Figure 1.2, increasing by nearly 20% through the turn of the millennium before a drop in 2020 when the Covid-19 pandemic reduced travel significantly. While emissions from all other methods of transport plateaued and saw a significant reduction a decade prior, the road transport sector emissions remained high, accounting for 40.3% of all EU transport GHG in 2020. In order to address this issue, the European Commission, as part of the European Green Deal in 2023, is proposing a roadmap to reduce CO<sub>2</sub> emissions from the heavy-duty road transport sector – trucks, city busses and long-distance busses which are responsible for over 6% of total EU GHG emissions and more than 25% of road transport GHG emissions in general. The proposed phased implementation

determines targets of 45%, 65% and 90% emissions reductions from 2030, 2035 and 2040 respectively. Due to the use case of the specific application scenario where they can be charged overnight and travel well defined and predictable routes, city busses in particular are targeted to transition to zero-emission by 2030 to further stimulate the adoption of electrification [4].

## 1.2 Strategy for Vehicle Electrification

Given its passenger carrying capability, one major point of growth in public road transport is driven by electrified busses, whereby the International Energy Agency claims that in 2018, there were approximately 460 000 electrified busses in operation around the world, up 100 000 from the year before [2]. In order to understand if the purchase and operation of these busses are to be commercially and financially viable, a lifecycle cost analysis has to be performed for the various applications of electrification technology within a bus. A study by Lajunen [5] showed, having compared 4 bus duty cycles including those from Finland and California that the cost over the lifetime, 12 years, of an electrified bus favoured hybrid variants over its conventional and fully electric counterparts due to lower cost. In order to reduce the cost impact of EVs, the United Kingdom (UK) government is providing funding support of more than 294 million pounds to local transport authorities which is aimed to subsidise the initial purchase, maintenance and infrastructure cost of 4000 zero emission busses from 2021 to 2023 [6].

The US Drive partnership, made up of the United States Department of Energy (D.O.E), Ford, General Motors and multiple other energy and utility companies published a roadmap along with trends affecting electrification of drivetrains to identify key challenges and propose solutions to resolve them. Among some of the trends seen is in the adoption of electrified skateboard chassis by major manufacturers that includes both electric traction drive and energy storage, in place of conventional drive train setups. This provides greater vehicle design freedom, the ability to achieve modularity and ease of scalability. Secondly, vehicle performance requirements are driving the demand for higher power drivetrains as customers

require faster acceleration and larger, more versatile vehicles. Based on these trends, US Drive proposes a technical target for 2025, based on 3 key matrices [7]:

- 1) Cost difference between an electrified vehicle and a comparable Internal Combustion Engine (ICE) vehicle should be no greater than 3 years of fuel savings.

- 2) Increase in power density of 8x to meet packaging constraints within Hybrid vehicles which include other DCDC converters and onboard chargers.

- 3) Twice the reliability of traditional automotive life - 300,000 miles, to enhance the longevity of the vehicle.

Electrified Vehicle manufacturers must ensure that achieving one of these matrices does not come at the cost of another. For example, as part of the US Department of Energy's (DoE) efforts to achieve energy security, the Clean Cities program was launched. It encountered concerns from the consumer regarding idle reduction, whereby, turning the vehicle on and off would result in premature wear and consequently failure of the starter motor and battery. Therefore, it is clear that the challenge faced with automotive electrification is in balancing performance and safety requirements against implementation cost, packaged within a design that optimises for power density and thermal performance [8].

The objective to achieve the electrification strategies places a growing electrical power requirement on vehicles, as referenced in [9], for the following reasons: the need for new and improved vehicle architectures, power conversion on demand, the use of precise electronics control and fast, high power motion onboard the vehicle. These requirements further the advent of driveline electrification in the automotive space with the integrated power electronic converters as the heart of the system since they offer improved power density with simplified integration for vehicle manufacturers [10]. Due to cost concerns, many electric vehicle functions in the past were realised actively avoiding power electronic components [9]. However, since the early 2000s until now, major strides in the development of power electronic converters pertaining to density, reliability, thermal performance and control algorithms have been achieved placing them as a viable solution to many of the

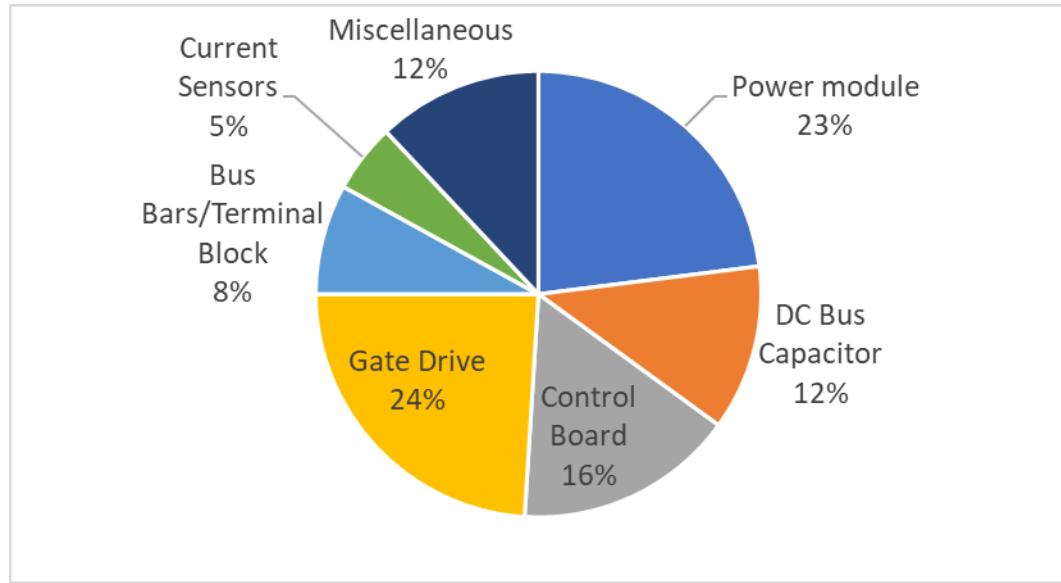

challenges faced with on-vehicle power requirements in all aspects of vehicle design-powertrain, safety management, body and convenience [11]. This growth is set to increase with the electrification of vehicle drivetrains in the coming years as the demand for fully electric vehicles increases. US Drive proposes a 2020 cost target of \$3.3/kW and 13.4kW/l and a 2025 cost target of \$2.7/kW and 100kW/l in [7] through a combination of component and multiphysics integration. Figure 1.3 illustrates a cost breakdown of an inverter as a proposed target to meet the 2025 cost target. With this increase comes further development in the power electronic converter space and the objective of reaching even higher power densities and efficiency [12].

Figure 1.3 Inverter cost breakdown for a potential pathway to meet 2025 targets through the application of advanced integrated power modules; proposed DC link voltage range of 525-775V (650V nominal) and maximum current of 600A to achieve 100kW rating [7].

### 1.3 Industrial Association and Research Background

Given the current transition of the public transport sector to electrified drivelines, the research effort was conducted with close links to Cummins Inc., the Tier-1 engine supplier of the 2016 Wrightbus Routemaster double-decker hybrid bus () to Transport for London, TfL [13]. Known also as the New Bus for London, NBfL, the drivetrain tuning and design would be optimised for routes in London, United Kingdom [14].

Figure 1.4. 2016 Wrightbus Routemaster Hybrid Bus (pictured) [14].

The goal of the research was to improve operational efficiency and manufacturability while reducing emissions, taking the parallel hybrid system consisting of a Cummins 4.5L Euro 5 diesel engine coupled to a Siemens electric drive [15] as a baseline. To this end, the engine would be upgraded to meet Euro 6 specifications, with maximum electrification to crank driven accessories, such as the alternator, cooling and lubrication pumps. Torque production by the engine would be supplemented by a Cummins electric motor which could also leverage regenerative energy as the vehicle is braking. Considering these objectives, the

research would iterate on the design and capabilities of the NBfL, by taking it as a technological and cost baseline to propose a fully optimised solution.

## 1.4 Thesis Outline

This thesis focuses on two topics. The first is the proposal of a multiport converter topology to meet the requirements of a London bus application and the second is to present the design and validation work of advanced control strategies to enhance the performance envelope, taking advantage of the integrated construction of the converter.

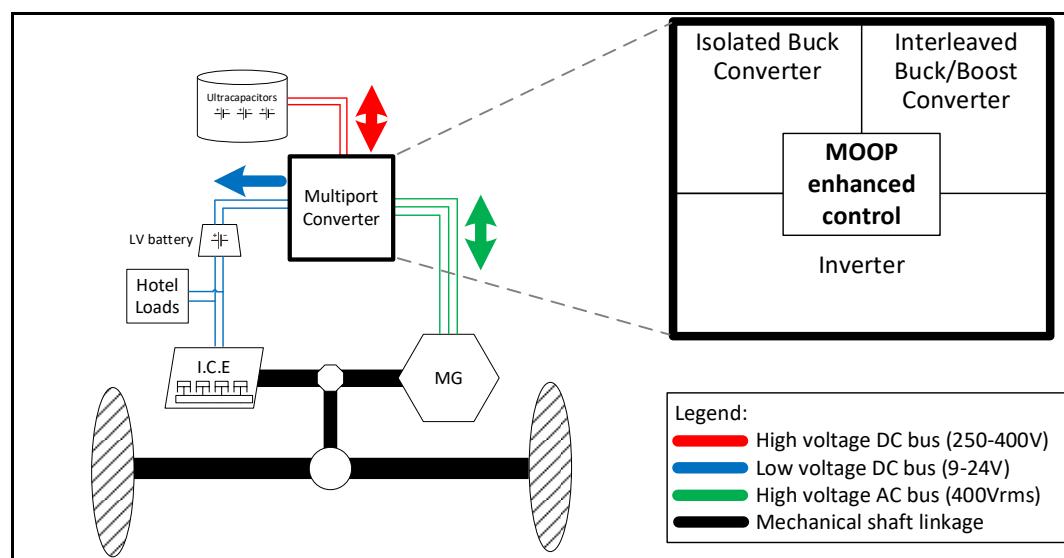

The stringent requirements of the London bus cycle provide strong justification and a requirements framework for vehicle manufacturers to meet. Baseline studies of pre-existing converter technologies must be carried out to initially understand key enablers and identify developmental gaps. Next, a novel concept of an automotive multiport converter design is presented for evaluation. The Multiport converter is the amalgamation of 3 separate converter units- an inverter capable of bidirectional power flow to a PMSM (Permanent Magnet Synchronous Machine) and two DCDC converters for management of a shared DC bus and on-vehicle power conditioning. Each converter unit is validated and optimised individually to meet their specific functional requirements before adaptations are performed to physically integrate the multiport converter.

The second topic builds upon the baseline by studying the multiport converter performance attributes during simultaneous operation. To cope with the complexity of selecting an optimal control strategy for the inverter with trade-offs between conflicting performance objectives, the Multiple Objective Optimisation Problem (MOOP) solving technique based on a well-known economics theory, the Pareto Optimum, is applied. Advance control methodologies are developed to achieve the desired optimum operational point.

While studies on the advantages introduced by various multiport converter topologies [16] as well as efforts to improve general efficiency in hybrid vehicle topologies [17], [18] are well documented in literature, a fully multi objective optimisation of a hybrid vehicle solution- including energy storage power conditioning and management incorporated with the traction and low voltage bus, the complete hybrid vehicle electrical network, has not been presented before. Herein lies the novelty of this work whereby the optimum combination of singular converter units from conventional hybrid system architectures [19] into a multiport converter and collectively optimised according to specific operational requirements of the vehicle.

Design justifications as well as the results of simulation and experimental work carried out are presented, firstly to prove the effectiveness of the methods employed, and also so that the ideas presented may be further built on and deployed across a wider scope of electric drive applications. Concepts proposed within this thesis have been peer-reviewed as part of publications for which a list has been included in Appendix A.

In all, the thesis aims to:

- Propose the concept of a multiport converter through integration of standalone converters as a viable topology for hybrid buses.

- Demonstrate the utilisation of MOOP solving techniques within the specific context of automotive drive optimisation.

- Investigate and prove the effectiveness of advanced control techniques that improve individual components and collective performance and efficiency of the integrated design of the multiport converter.

To this end the thesis is outlined as below:

- Chapter 1 presents a general introduction to the current state of vehicle electrification and current motivations and strategies of governmental bodies behind global efforts.

- Chapter 2 gives a review of the state of the art of inverters and DCDC converters including the challenges faced by the respective technology implementations and mitigation actions taken to counteract them to bring them to market.

- In Chapter 3, a specific multiport converter design is proposed to satisfy the application requirements of a hybrid passenger bus. The multiport converter is separated into individual converter module for detailed analysis. Design methodology of each converter module is presented.

- The concept of simultaneous optimisation is presented in Chapter 4. MOOP is introduced to clarify the optimisation objectives. Key loss components identified are analysed within a simulation model and results of simulation sweeps are discussed. Advanced control strategies targeting the loss components are simulated and results presented. The optimal parameter set represented as a Pareto Front for multiple driving scenarios is presented along with performance gains obtained.

- Chapter 5 presents the experimental test rigs, used to validate design methodologies presented in the thesis.

- Finally, Chapter 6 presents general conclusions, considerations of limitations faced in this work and proposal for further work to be done.

## Chapter 2

### Review of Converter Technology

Legislation and proposed roadmaps by governmental and consumer entities drive requirements surrounding the design of automotive power electronics converters. It is clear that majority electric drivetrain manufacturers implement electrification technologies in 3 main areas: propulsion, hotel load supply and charging; where the propulsion converter space is dominated by the 3 phase, 2 level DC-AC inverter due to simplicity of control and low cost [20], while hotel load supply and onboard charging functionality is typically provided by DC-DC converters.

Taking the NBfL, as a baseline for further electrification [21], the need for power conditioning within between the drivetrain and hotel loads becomes apparent. This is driven by the requirements to supplement torque production by the 480Nm, Cummins B4.5 diesel engine [22] in propulsion mode, supply hotel loads (such as the cabin lighting and blown-air heating system), charge on-board energy storage devices (24V vehicle battery and ultracapacitor bank) during regenerative modes and finally to stop and restart the I.C.E when the vehicle is stationary. The functionality required is summarised in Table 1.

Table 1

FUNCTIONALITY OF CONVERTER COMPONENTS

|                       | <b>Functionality required</b>      | <b>Power flow direction</b> | <b>AC/DC</b> | <b>Voltage</b>              | <b>Selected component</b>           |

|-----------------------|------------------------------------|-----------------------------|--------------|-----------------------------|-------------------------------------|

| <b>Drivetrain</b>     | Propulsion and Regenerative Torque | Bidirectional               | AC           | 275-400V                    | Inverter                            |

| <b>Energy Storage</b> | Charge and Discharge               | Bidirectional               | DC           | 250-400V                    | Bidirectional interleaved converter |

| <b>Hotel Loads</b>    | Supply                             | Unidirectional              | DC           | 24V (Galvanically Isolated) | Unidirectional isolated converter   |

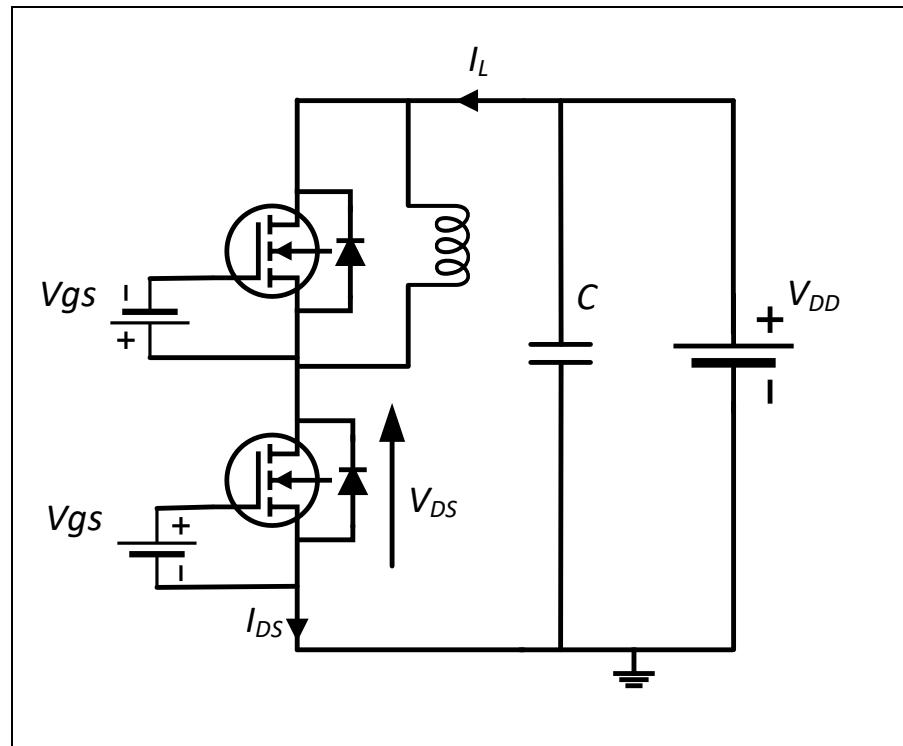

AC driven drivetrain components such as the MG-inverter operate on a voltage bus approximately 30 times that of the DC driven hotel load components, making power conditioning and control between each node critical to system functionality. Differences in power flow direction, type and values are depicted as a simplified block diagram in Figure 2.1 showing the variety in type of electrical power needed to support vehicle functionality. The multiport converter co-locates all of this functionality within a comprehensive, single package, enabling optimisation through MOOP.

Figure 2.1: Vehicle component topology depicting multiple bus architecture supported by the proposed multiport converter governed by a unified controller operating the MOOP enhanced strategy to control power flow.

In this chapter, the multiport converter is analysed and presented according to functionality- propulsion inverters and DCDC converters to account for the differences in the state-of-the-art of technology between the two converter types, the trends and challenges faced and optimisation opportunities in hardware and software.

## 2.1 Electric drives and Propulsion Inverters

The traction inverter forms the central propulsion component within an electric drivetrain. As it is responsible for converting the DC power supplied by the vehicle energy storage into AC power in the electrical machine, the inverter is subject to great pressure for improvement, simultaneously requiring high power density, switching frequency, efficiency and high temperature operation capability over a wide load range.

### 2.1.1 High Voltage Trends and Silicon Carbide Technology

Recent trends show a shift towards 800V Electric Vehicle, EV powertrain architectures [20] as the increased voltage level allows for a reduction in weight and size of onboard power cables [23]. The increase in main voltage bus places the requirement for the blocking voltage of power modules to therefore increase, to at least 1200V to provide adequate margin. Silicon technology (Si) based switching devices have been under development for years and therefore has led to it being the dominant selection for power converter design. However, the development of better power modules in terms of current handling, efficiency and higher temperature has seen a reduction in pace as the material properties begin to reach a limit, restricting further progression, causing a subsequent migration to Silicon Carbide (SiC) technology, particularly in the recent decade [24].

The push for industrialisation of SiC technology by automotive applications [25] has led to the proliferation of challenges to established designs to allow for highly performant, compact, robust, and cost-effective solutions. As higher and higher voltages are favoured, at the greater switching frequencies enabled by SiC technology, the uniformity of current distribution becomes paramount to avoid lifetime degradation of the module, particularly at operation points close to peak ratings of the module. Therefore, it is important to design for mirror-symmetric cell layout of the commutation circuit formed with the DC link capacitor. Where perfect symmetry may be difficult to achieve due to hardware tolerances, approaches that utilise negative feedback from Kelvin sources of each chip connected via resistors on the gate-driver board [26]. The mechanism enables modules to compensate chip-

parameter deviations during the  $di/dt$  phase, subsequently bringing the modules to the same switching speed. This balances the currents and therefore the switching losses, avoiding critical overcurrent within the modules.

While dynamic control measures such as active compensation, Active Current Balancing (ACB) [27] and dead-time elimination schemes [28] and advanced baseplate such as pin-fin technology [29] may be utilised to allow high peak-power densities, high continuous power density of the inverter module relies on the thermal performance of the AC and DC interfaces, EMC filter, busbars and DC link capacitors. The DC link capacitor loss distribution can be expressed as:

$$P_{C,loss} = R_{ESR} I_C^2 \quad (2.1)$$

where,  $P_{C,loss}$  represents the losses in the elements of the capacitor,  $R_{ESR}$  is the equivalent series resistance (ESR) and  $I_C$  represents the RMS value of current. To optimise for the lowest  $P_{C,loss}$ , equation (2.1) clearly shows that both  $R_{ESR}$  and  $I_C$  must be reduced.  $R_{ESR}$  may be reduced through component selection and design, for example, a parallel configuration of film capacitors which is deliberately designed to avoid heat influx from its physical interfaces using a gap pad pictured in Figure 2.2 [25].

Figure 2.2. Parallel Bosch power stage and capacitor module with a gap pad to provide thermal separation [25].

Although  $I_C$  would be determined by the inverter operating point, sophisticated techniques which rely on phase shifting [30] the PWM pulses of one converter with respect to the other in a multi-converter setup may be used to lower the amplitude of capacitor ripple current which will in turn reduce  $I_C$  and therefore achieve loss reduction.

### 2.1.2 Module Packaging Trends

An early approach of a “sandwich” or Double Sided Cooling (DSC) structure automotive inverter power module is presented in [31] where designers target four main performance matrices – high temperature operation, reduction in thermal cycling, utilisation of silicon carbide and manufacturability. It is shown that by using the sandwich structure of connecting two Direct Bonded Copper (DBC) substrates, one on top of the device and one at the bottom, heat can be extracted by both sides. Furthermore, specific positioning of the substrates and dies has been performed such that uni-axial compressive force is applied to the dies during operation, increasing resistance to fatigue of the interconnects due to thermal cycling and therefore increasing the lifetime and reliability of the module.

Using similar key performance indicators (KPI), a review of a wide array of power modules developed by research institutes and industrial companies is presented in Figure 2.3, showing a clear increase in current handling capability from 2008 to present and a lower thermal resistance in DSC when compared

Figure 2.3. DSC Power Modules from institutes and companies [32]

to the single sided cooling counterpart. Each power module is then studied at a structural level as illustrated in by Figure 2.4, to identify the pros and cons of each packaging approach.

Figure 2.4. Power Module Structure [32].

Various packaging approaches and technologies are analysed according to their suitability for various different applications and tabulated in Table 2 for comparison.

Table 2

COMPARISON OF DSC POWER MODULE

PACKAGING TECHNOLOGIES [32]

| R&D Institutions | Packaging approach   | Year | Pros                                                                                                                                                                | Cons                                                                                                                                                                                                            |

|------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPES             | MPIPPS               | 1998 | <ul style="list-style-type: none"> <li>• Larger current handling capacity</li> <li>• Achieves direct die to module attachment.</li> <li>• Active cooling</li> </ul> | <ul style="list-style-type: none"> <li>• Copper posts need to be handled</li> <li>• Unreliable at high temperatures</li> </ul>                                                                                  |

|                  | DAI                  | 2001 | <ul style="list-style-type: none"> <li>• Better fatigue resistance</li> <li>• Better thermal management than the MPIPPS</li> </ul>                                  | <ul style="list-style-type: none"> <li>• Dimpled copper plates need to be handled</li> </ul>                                                                                                                    |

|                  | FCOF                 | 2003 | <ul style="list-style-type: none"> <li>• Increased reliability because of the smaller contact area</li> <li>• Better thermal fatigue resistance</li> </ul>          | <ul style="list-style-type: none"> <li>• Limited in voltage and current levels</li> </ul>                                                                                                                       |

|                  | PowERazor            | 2014 | <ul style="list-style-type: none"> <li>• High temperature application</li> <li>• Stress relieving</li> </ul>                                                        | <ul style="list-style-type: none"> <li>• Rework is difficult</li> <li>• High cost because of silver paste</li> </ul>                                                                                            |

| ECPE             | Embedding technology | 2012 | <ul style="list-style-type: none"> <li>• Multilevel integration</li> <li>• Improved thermal management</li> <li>• Light weight</li> </ul>                           | <ul style="list-style-type: none"> <li>• Complex and costly processing</li> <li>• Large thermal mismatch</li> <li>• Increased parasitic capacitance</li> <li>• Limited in voltage and current levels</li> </ul> |

| ORNL             | PBA                  | 2012 | <ul style="list-style-type: none"> <li>• Integrated forced cooling capability</li> <li>• Shorter electrical paths</li> </ul>                                        | <ul style="list-style-type: none"> <li>• Device top metallization</li> <li>• High thermal stress due to direct soldering</li> </ul>                                                                             |

| NCSU             | PCoB                 | 2016 | <ul style="list-style-type: none"> <li>• High integration</li> <li>• Ultralow parasitic inductance</li> </ul>                                                       | <ul style="list-style-type: none"> <li>• Chip top metallization</li> <li>• Complex structure</li> </ul>                                                                                                         |

| GE               | POL                  | 1995 | <ul style="list-style-type: none"> <li>• Shorter electrical paths</li> <li>• Multilevel integration for quasi-3D packaging</li> </ul>                               | <ul style="list-style-type: none"> <li>• Complex and costly processing</li> <li>• Large thermal mismatch</li> <li>• High thermal stress due to direct soldering</li> </ul>                                      |

| Alstom           | Flip Chip            | 2000 | <ul style="list-style-type: none"> <li>• Shorter interconnect lengths</li> <li>• Lower cost than deposited metalization</li> <li>• Increased reliability</li> </ul> | <ul style="list-style-type: none"> <li>• Fatigue of solder joints</li> <li>• Limited in current and voltage levels</li> </ul>                                                                                   |

| Denso            | IPEM                 | 2008 | <ul style="list-style-type: none"> <li>• Lower parasitic inductance</li> <li>• No base plate</li> <li>• Low cost</li> </ul>                                         | <ul style="list-style-type: none"> <li>• Increased complexity</li> <li>• Low power density</li> <li>• Thermal grease is needed</li> </ul>                                                                       |

| Delphi           | Viper                | 2008 | <ul style="list-style-type: none"> <li>• More flexible layout</li> <li>• High power density</li> <li>• Simple fabrication and assembly</li> </ul>                   | <ul style="list-style-type: none"> <li>• More susceptible to early failure</li> <li>• Thermal grease is needed</li> </ul>                                                                                       |

While the results demonstrate improvements in thermal performance of the inverter, the serial approach in the design of inverters, whereby power modules, gate drivers, converters, current measurement, passive components and converters are each developed in isolation, has begun to reach the limit. This presents the need for greater degrees of integration at the functional, structural and design level in order to enable the next step in the evolution of power electronics design. A study of key technological enablers for power module integration is presented in [33] where it is shown that the partitioning of power assemblies into substrate level blocks based on functional commutation cells provide low thermal resistance cooling and minimisation of commutation loop inductance. The integration of passive filter components at the substrate level also improves electromagnetic performance. It is however proposed that while sensing functions are easily accommodated on the power module substrates, the accompanying signal processing and gate drivers are implemented on a separate dedicated substrate using an appropriate technology.

## 2.2 DCDC Converters

PWM switching DCDC converters are used in the majority of DC-to-DC conversion applications due to continuous demand for smaller, lighter and more efficient power converters. Some popular topologies in the automotive space are illustrated in Figure 2.5 [34]. These are often found to have elementary PWM converters- buck, boost and buck-boost as building blocks- with various tweaks to configurations, numbers of parallel converters and circuit manipulation techniques. For instance, the cascade of the boost and buck converter led to the creation of the Cuk converter [35]. The use of other techniques include the inversion of the source and load [36], and differential or parallel connections of two or more converters [37].

Figure 2.5. DCDC converter topologies [34].

### 2.2.1 Challenges Facing the State of the Art

The transition from conventional drive train setups to a more electric drivetrain has dramatically increased the number of providers as well as the demand for power electronic systems, namely sales volumes for modules, discrete devices and integrated circuits (IC) are predicted to experience a compounded annual growth rate (CAGR) of 5.9% taking it from \$26.07 Billion in 2023 to \$43.67 Billion by 2030 [13]. This places enormous pressure on designers to optimise the entire vehicle power distribution network in terms of component utilisation by targeting cost and volumetric minimisation; with the key restrictions being application requirements. An example of a three-port multiport converter is presented in Figure 2.6; where the design has to condition power from 3 galvanically isolated sources- a high voltage (HV), low voltage (LV) and single phase AC grid connection for a vehicle onboard charging application. Here, the designers were able to integrate two dual active bridges (DAB) into a single Triple Active Bridge (TAB) converter thus achieving a component saving by commonising the isolation transformer and removing a H-bridge [38]. Despite this, the TAB is not ideal for the application due to the large operational voltage range of the each of the ports, making the design of the transformer nearly impossible to optimise for cost. This is a major concern as an added transformer or inductor implies additional cost and losses [40] within the DCDC converter which therefore have to be kept as low as possible so as to not compromise the advantages offered by the rest of the powertrain architecture [41].

Figure 2.6: Potential component saving achieved through integrated converter design [38].

## 2.2.2 Cost Optimisation via Hardware

A key challenge facing the state of the art is that Electric Drive Vehicles should cost no more than comparable ICE vehicles [7]. All in all, the cost targets set as part of the US Drive 2025 target-setting process, the cost difference should be no greater than 3 years of fuel costs savings and this resulted in a \$6/kW for a 100kW peak power drive system. This objective is further refined into a specific DCDC converter cost reduction target of \$30/kW, a 40% reduction from the current cost in tandem with specific power increase of more than 300% to 4kW/kg by 2025. In this chapter, DCDC converters are selected due to the simpler scope of its function compared to the inverter, despite sharing nearly all its components with the DC-AC counterpart. This makes technical developments and cost savings for DCDC converters highly transferable to inverter designs. The mitigation approach taken appears two-fold: reduction of cost per kilowatt through component selection and design, and secondly, increase kilowatt per kilogram through efficiency improvements like advanced converter topologies and devices.

### Power Modules and Gate Drivers

According to US Drive, Power Modules and their corresponding Gate Drive circuitry account for approximately half the cost of a traction inverter (graphically represented in Figure 1.3), making it a clear optimisation target for the industry. The cost of a power module can be divided into two main parts- the cost of the bare die and the packaging costs. When considering the manufacturing process of SiC power devices, four major factors, SiC substrate, cost of epitaxy, device fabrication and the yield are the main drivers of cost. As described in [42], the seeded sublimation process used to produce SiC is slow, requiring significant energy to enable the 2200°C growth process producing a final usable boule of no more than 25mm in length. There are also the additional costs of epitaxy - growth of a high quality SiC device layer on the substrate surface and device fabrication, both requiring higher temperatures and more expensive consumables. Finally, the yield, which is the percentage of good dies produced per wafer has a direct impact on the cost of production [43]. A larger chip

area would result in a lower yield and therefore result in higher cost as illustrated in Figure 2.7.

Figure 2.7. SiC MOSFET cost vs active chip area at different voltage levels.

While a year-on-year downward trend in cost (presented in Figure 2.8) is predicted due the increasing market penetration of SiC devices and corresponding supplier offerings, there are multiple steps designers can take to mitigate against the cost of power devices and drivers. One method is to incorporate SiC MOSFETs where possible to utilise the built-in body diode to eliminate the need for a separate anti-parallel diode. The application of SiC will also provide more efficient power conversion leading to reduced baseplate cooling requirement.

Figure 2.8: PGC Consultancy SiC cost forecast model based on a best-in-class 2021 1200V/100A device [42].

Several low-cost gate driver topologies have been proposed in literature that utilise novel techniques to achieve the same or better control performance of SiC MOSFETs, while providing sufficient bandwidth and voltage swing to appropriately drive the power module. One such approach is through the application of a method known as Active Gate Driver (AGD). While variants of this concept have been investigated and presented in gate driver optimisation studies - Lobsinger and Kolar [44] present a closed loop solution for Si IGBTs where  $dv/dt$  and  $di/dt$  are added to a single reference and Krishna and Hatua [45] propose a transistor based custom solution to circumvent the use of costly OPAMPs, these approaches fail to consider fast turn of SiC MOSFETs. The solution presented in [46] overcomes these weaknesses through the implementation of a turn-on methodology to arrest the current overshoot without reducing turn on  $di/dt$  through a transistor-based implementation. By performing closed-loop control of the gate driver, drain-source current and voltage can be accurately controlled during turn-off and turn-on transients. During turn-off switching transition, the turn-off voltage overshoot is limited by controlling turn-off  $di_{ds}/dt$ . Conversely, during the turn-on transition, control of drain current prevents drain current overshoot and fast switching speed. This concept demonstrates the possibility to achieve more efficient switching and less overall losses through a low-cost gate driver design.

### Passive Components: Capacitors

US Drive lists capacitors as contributing 12% to the estimated overall cost of an inverter as illustrated in Figure 1.3. The challenge with DCDC converters however, is that different topologies entail varying numbers of capacitors needed, and the specific capacitance in order to realise the design. The three main capacitor technologies available today are: multi-layer ceramic capacitors (MLCC), metalized polymer films (MPPF) and Al electrolyte (Al). A comparison of energy densities versus cost is presented in [47] where, although Al electrolytic capacitors achieve the highest densities and MLCC offer high current ratings within a small package size, polymer film capacitors provide the most well balanced properties

regarding the key parameters such as ESR and operational temperature range ruggedness.

A comparison of the power density of the three capacitor technologies is presented in Figure 2.9 where it is shown that high purity biaxial oriented polypropylene (BOPP) film material capacitor achieves a very close energy density compared to Al electrolytic capacitors when the loss of energy storage density in the winding construction because of the overhead necessary to achieve self-healing property.

Figure 2.9: Energy storage capacity of various dielectric materials compared [47].

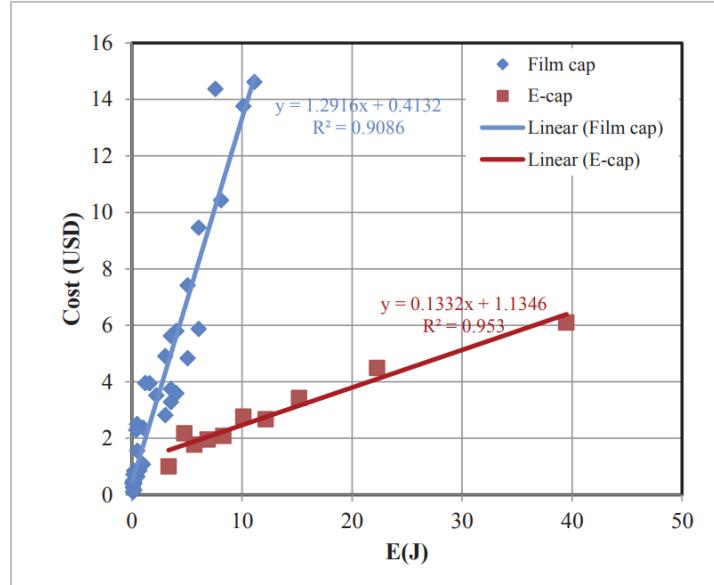

When compared cost wise, a study of capacitors of a similar voltage rating, lifetime and operational temperature showed that film capacitors were nearly 9.7 times (depicted in Figure 2.10) more costly than electrolytic capacitors [48].

Figure 2.10: Statistical results of unit cost of standard film capacitors and Aluminium electrolytic capacitors [48].

When considering the trade-off in capacitor selection and sizing, it is important to weigh the cost against the following parameters:

- i) Expected lifetime definition [49], [50], [51]: it is possible to select capacitor technology to achieve a certain lifetime target. Therefore, lifetime itself is not a deterministic factor on which capacitors should be chosen.

- ii) Capacitance required: the primary selection criteria for capacitance required is typically driven by voltage ripple from initial analysis of a converter design.

- iii) Electrical Stress: the voltage stress across the capacitor is a result of the system specification and the voltage ripple ratio due to the relationship between the modulation ratio and DC link voltage at a particular operating point.

- iv) Power loss calculation: the power loss of a capacitor is dependent on ESR and ripple current stress. An equivalent electrical model can

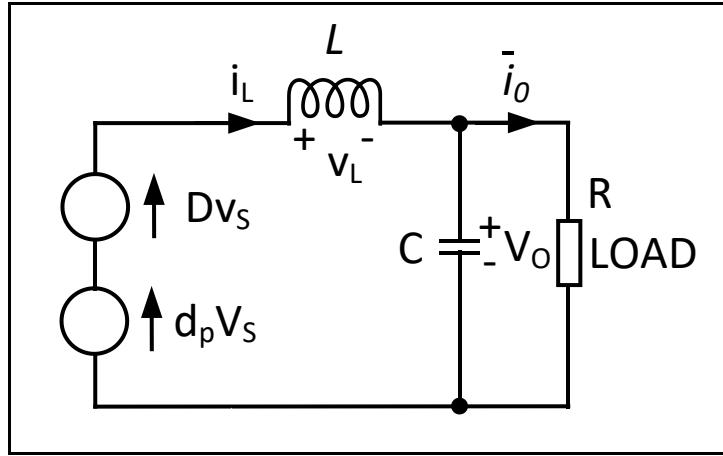

be used to calculate the root mean square (RMS) value of the low frequency ripple. This topic is further explored in Chapter 4 along with a novel technique for mitigating against these losses through carrier phase displacement.