# Wide-Bandgap Semiconductor Based Power Converters for Renewable Energy Systems

Emre Gürpınar, MSc

Submitted to the University of Nottingham for the degree of Doctor of Philosophy, January 2017.

#### Abstract

The demand for low carbon economy and limited fossil resources for energy generation drives the research on renewable energy sources and the key technology for utilisation of renewable energy sources: power electronics. Innovative inverter topologies and emerging WBG semiconductor based devices at 600 V blocking class are the enabling technologies for more efficient, reliable and accessible photovoltaic based electricity generation.

This thesis is concerned with the impact of WBG semiconductor based power devices on residential scale PV inverter topologies in terms of efficiency, volume reduction and reliability. The static and dynamic characterisation of the Si and WBG based devices are carried out, gate drive requirements are assessed and experimental performance comparison in a single phase inverter is discussed under wide range of operating conditions. The optimisation of GaN HEMT based single phase inverter is conducted in terms of converter efficiency, switching frequency and converter volume. The long term mission-profile based analysis of GaN and Si based devices is conducted and impact of WBG devices under low and high switching frequency conditions in terms of power loss and thermal loading are presented. Finally, a novel five-level hybrid inverter topology based on WBG devices is proposed, simulated and experimentally verified for higher power applications.

### Resume

E-mail: gurpinar.emre@gmail.com

### Education

- MSc in Electrical Energy Conversion Systems

University of Manchester, UK, November 2010

- BSc in Electrical Engineering

Istanbul Technical University, Turkey, June 2009

## Professional Experience

| • Guest PhD Student<br>CORPE, Aalborg University, Denmark   | 08/2015 - 11/2015 |

|-------------------------------------------------------------|-------------------|

| • R&D Power Electronics Engineer<br>GE Power Conversion, UK | 10/2011 - 07/2013 |

• R&D Engineer

University of Reading, UK 12/2010 - 10/2011

#### Scientific Contribution

Emerging wide-bandgap (WBG) power semiconductor devices at 600 V blocking class have been gaining attention from power electronic converter developers with special focus on the application for renewable energy systems. The focus of this thesis is the state-of-the-art inverter topologies and impact of WBG devices at 600 V blocking class on residential scale PV systems.

The first contribution of this thesis is benchmarking of emerging WBG power semiconductor devices at 600 V blocking class, SiC MOSFET and GaN HEMT, and comparison to Si based devices including static and dynamic characterisation, gate drive

requirements and performance evaluation in a single phase inverter. The benchmarking of devices has shown that GaN HEMT has excellent switching and conduction

properties at low current conditions with negligible temperature dependency, but a

relatively higher complex gate driver design is required for safe operation and the

design has a strong impact on switching losses. The performance results of WBG

devices in single phase inverter shows that SiC and GaN devices provide performance

enhancement over Si under wide load, temperature and switching frequency conditions. In terms of switching performance, GaN HEMT has the best performance

among three technologies and allows high efficiency at high-frequency applications.

The robust performance provides optimisation of system volume and weight by changing switching frequency and heat sink temperature, without compromising system

efficiency.

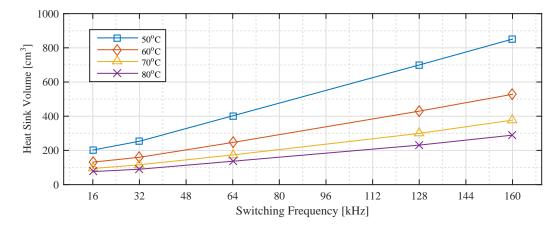

The second contribution is the investigation of impact of the GaN HEMT devices to a PV inverter in terms of power loss, converter efficiency, heat sink and output filter volume, and thermal stress reliability analysis based on a real-field mission profile. The excellent switching and conduction performance of GaN HEMT under different load and heat sink temperature conditions results in very high efficiency and low power cell loss. It is shown that combined heat sink and output filter volume can be reduced by increasing the heat sink temperature from 50 °C to 80 °C, and increasing the switching frequency from 16 kHz to 64 kHz, without compromising the

efficiency of the system. The mission-profile based analysis of the GaN HEMT based inverter shows that GaN HEMT based system has significantly lower thermal stress in comparison to Si IGBT based system at both low and high switching frequency conditions. The reduced thermal stress brought lower junction temperature variation and reduced mean temperature across most stress device throughout the year.

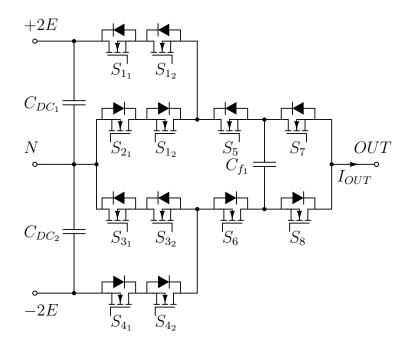

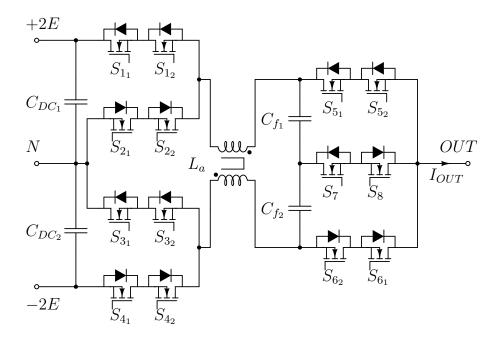

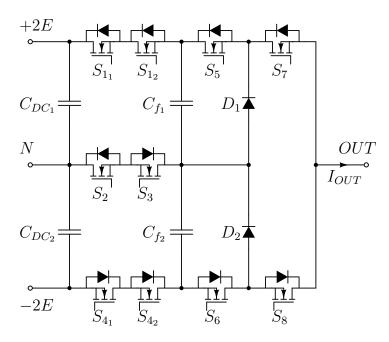

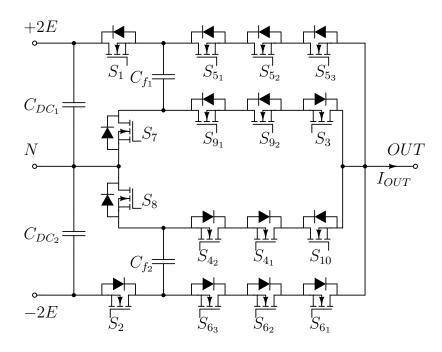

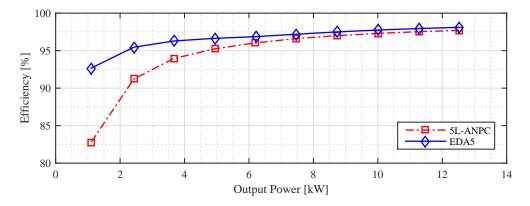

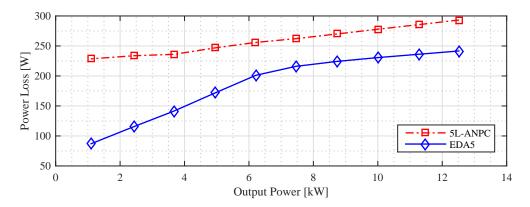

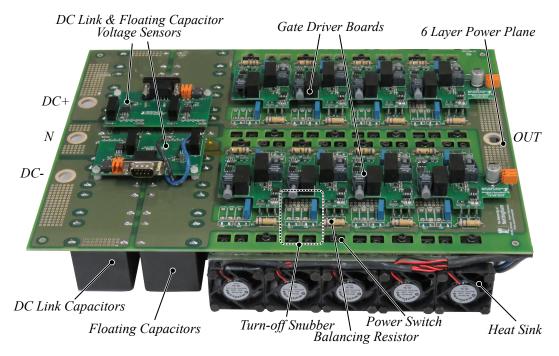

The final contribution of this work is introduction of a novel five-level hybrid inverter topology based on SiC MOSFETs dedicated for renewable energy systems and high power applications, such as variable speed drives or propulsion systems. The results showed that proposed topology provides higher efficiency in comparison to state-of-the-art hybrid topology 5L-ANPC, especially at lighter load conditions. The functionality of the topology was verified experimentally with 650 V SiC MOSFETs in a 12 kW single phase prototype under different load and heat sink temperature conditions.

## Journal Papers

#### First Author

- 1. **E. Gurpinar** and A. Castellazzi, "Single-Phase T-Type Inverter Performance Benchmark Using Si IGBTs, SiC MOSFETs, and GaN HEMTs," in *IEEE Transactions on Power Electronics*, vol. 31, no. 10, pp. 7148-7160, Oct. 2016.

- 2. **E. Gurpinar**, Y. Yang, F. Iannuzzo, A. Castellazzi and F. Blaabjerg, "Reliability-Driven Assessment of GaN HEMTs and Si IGBTs in 3L-ANPC PV Inverters," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 956-969, Sept. 2016.

#### Other Author

D. Barater, C. Concari, G. Buticchi, E. Gurpinar, D. De and A. Castellazzi, "Performance Evaluation of a Three-Level ANPC Photovoltaic Grid-Connected Inverter With 650-V SiC Devices and Optimized PWM," in *IEEE Transactions* on *Industry Applications*, vol. 52, no. 3, pp. 2475-2485, May-June 2016.

#### Journal Papers under Review

#### First Author

- 1. **E. Gurpinar**, F. Iannuzzo, Y. Yang, A. Castellazzi and F. Blaabjerg, "Low Inductance Switching Power Cell Design for GaN HEMT Based Inverter," in *IEEE Transactions on Industry Applications*.

- 2. **E. Gurpinar** and A. Castellazzi, "GaN HEMT Based Single Phase Inverter Design Optimisation," in *IEEE Transactions on Power Electronics*.

#### Other Author

1. J. Li, A. Castellazzi, M. A. Eleffendi, **E. Gurpinar**, C. M. Johnson and L. Mills "A Physical RC Network Model for Electro-Thermal Analysis of a Multichip SiC Powe rModule" in *IEEE Transactions on Power Electronics*.

## Conference Papers

#### First Author

1. **E. Gurpinar**, and A. Castellazzi, "600V Normally-Off p-Gate GaN HEMT based 3-Level Inverter" in *IEEE International Future Energy Electronics Conference (IFEEC ECCE-Asia*), 3-7 June 2017, Kaohsiung, Taiwan (In Press).

- 2. **E. Gurpinar**, F. Iannuzzo, Y. Yang, A. Castellazzi, F. Blaabjerg, "Ultra-low inductance design for a GaN HEMT Based 3L-ANPC Inverter" in *IEEE Energy Conversion Congress & Expo (ECCE 2016)*, 18-22 Sept 2016, Milwaukee, Wisconsin, pp. 1-8.

- 3. **E. Gurpinar** and A. Castellazzi, "Novel Multilevel Hybrid Inverter Topology with Power Scalability" in 42<sup>nd</sup> Annual Conference of IEEE Industrial Electronics Society (IECON 2016), 24-27 Oct 2016, Florence (In Press).

- 4. **E. Gurpinar** and A. Castellazzi, "SiC and GaN based BSNPC inverter for photovoltaic systems," *Power Electronics and Applications (EPE'15 ECCE-Europe)*, 2015 17th European Conference on, Geneva, 2015, pp. 1-10.

- 5. **E. Gurpinar**, D. De, A. Castellazzi, D. Barater, G. Buticchi and G. Francheschini, "Performance analysis of SiC MOSFET based 3-level ANPC grid-connected inverter with novel modulation scheme," 2014 IEEE 15th Workshop on Control and Modeling for Power Electronics (COMPEL), Santander, 2014, pp. 1-7.

- 6. E. Gurpinar, S. Lopez-Arevalo, J. Li, D. De, A. Castellazzi and L. Mills, "Testing of a lightweight SiC power module for avionic applications," Power Electronics, Machines and Drives (PEMD 2014), 7th IET International Conference on, Manchester, 2014, pp. 1-6.

#### Other Author

- 1. C. Chowdhury, **E. Gurpinar**, and A. Castellazzi, "Full SiC Version of the EDA5 Inverter" in *IEEE International Future Energy Electronics Conference* (*IFEEC ECCE-Asia*), 3-7 June 2017, Kaohsiung, Taiwan (In Press).

- 2. J. Garcia, **E. Gurpinar**, and A. Castellazzi, "High-Frequency Modulated Secondary-Side Self-Powered Isolated Gate Driver for Full Range PWM Operation of SiC Power MOSFETs," 2017 IEEE Applied Power Electronics Conference (APEC), 26-30 March 2017, Tampa, FL (In Press).

- 3. J. Garcia, **E. Gurpinar**, and A. Castellazzi, "Impulse transformer based secondary-side self-powered gate-driver for wide-range PWM operation of SiC power MOSFETs," 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, 2016, pp. 59-63.

- 4. D. Barater, E. Gurpinar, G. Buticchi, C. Concari, D. De, A. Castellazzi, "Performance analysis of UniTL-H6 inverter with SiC MOSFETs," 2014 International Power Electronics Conference (IPEC-Hiroshima 2014 ECCE ASIA), Hiroshima, 2014, pp. 433-439.

- Jianfeng Li, E. Gurpinar, S. Lopez-Arevalo, A. Castellazzi and L. Mills, "Built-in reliability design of a high-frequency SiC MOSFET power module," 2014 International Power Electronics Conference (IPEC-Hiroshima 2014 - ECCE ASIA), Hiroshima, 2014, pp. 3718-3725.

- 6. D. Barater, C. Concari, G. Buticchi, E. Gurpinar, D. De and A. Castellazzi, "Performance evaluation of a 3-level ANPC photovoltaic grid-connected inverter with 650V SiC devices and optimized PWM," 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, 2014, pp. 2233-2240.

## Patents (Pending)

1. **E. Gurpinar**, D. De, A. Castellazzi, "Power Converter", GB Patent App. 1520961.2, 27 November 2015

#### Acknowledgements

I would like to express my appreciation and gratitude to my supervisor Dr. Alberto Castellazzi for his encouragement, valuable advice and financial support throughout the progress of this work. I also would to thank all my colleagues and friends in the Power Electronics, Control and Machine (PEMC) Group at University of Nottingham for the support and valuable discussions. In particular, appreciation is extended to those who have made my research more interesting and enjoyable, there are too many to mention but particularly Attahir Aliyu, Shajjad Chowdhury, Maria Jankovic, Savvas Papadopoulos, Stefano Nuzzo, Francesco Tardelli, Sara Roggia, Sharmila Sumsurooah, Manjusha Vijayagopal and Bilal Arif. Thanks are also due to Faculty of Engineering, University of Nottingham for providing the studentship for my studies.

I also would like to thank Nottingham Rowing Club members Stephen Ferguson, Clarke Camilleri, Richard Mynett and Paula Dihman for their friendship and sharing the pain/joy of rowing during early morning trainings, erg sessions and races.

Also, I place on record, my gratitude to Dr. Yongheng Yang and Prof. Francesco Iannuzzo for their kindness and professional supervision during my study abroad at the Department of Energy Technology, Aalborg University, Denmark. Additionally, many thanks to Dr. Davide Barater, Dr. Giampaolo Buticchi and Dr. Carlo Concari from the University of Parma, Italy, for their collaboration and guidance.

Finally, I owe the greatest debt of gratitude to my family. I would like to thank my parents Esin and Fatih Gürpınar, my sister Gözde Seda Aksoy and my brother-in-law Emrah Aksoy for a lifetime of support, encouragement, and education. Without them, I would not have the courage and dedication to start and complete this work.

Emre Gürpınar

3 January 2017 Nottingham, UK

#### List of Terms

- 2DEG Two-dimensional Electron Gas

- AC Alternating Current

- ANPC Active Neutral Point Clamped

- $BFoM\,$  Baliga's Figure of Merit

- $BSNPC\,$  Bi-directional Switched Neutral Point Clamped

- BJT Bipolar Junction Transistor

- CM Common-Mode

- $CMR\,$  Common-Mode Noise Rejection

- DUT Device Under Test

- DC Direct Current

- $E_{crit}\,$  Electric Breakdown Field

- EU European Union

- $E_{on}$  Turn-on switching energy

- $E_{off}$  Turn-off switching energy

- GaN Gallium-nitride

- HEMT -High Electron Mobility Transistor

- HERIC -Highly Efficient and Reliable Inverter Concept

- $IEEE\,$  Institute of Electrical and Electronic Engineers

- $IEC\,$  International Electrotechnical Commission

- $n_i$  Intrinsic carrier concentration

- $IGBT\,$  Insulated-Gate Bipolar Transistor

- JFET Junction Field-Effect Transistor

- LFT Line Frequency Transformer

- MPP Maximum Power Point

MPPT - Maximum Power Point Tracking

MOSFET - Metal-Oxide-Semiconductor Field-Effect Transistor

$N_a$  - Acceptor Doping density

$N_d$  - Donor Doping density

NPC - Neutral Point Clamped

NPP - Neutral Point Piloted

NPT - Non-punch through

PV - Photovoltaic

PT - Punch through

$r_{on}\,$  - Resistance of Drift Region

RMS - Root Mean Square

$q\,$  - Elementary charge

$Q_{rr}\,$  - Reverse recovery charge

Si - Silicon

$SiC\,$  - Silicon-carbide

$SBD\,$  - Schottky-barrier Diode

$THD\,$  - Total Harmonic Distortion

$V_{bi}$  - Built-in potential across pn junction

${\cal V}_{BR}\,$  - Breakdown voltage

UK - United Kingdom

${\cal U}{\cal S}\,$  - United States

WBG - Wide-Bandgap

$w_{drift}$  - Drift region thickness

$\varepsilon_0$  - Permittivity of Vacuum

$\varepsilon_r$  - Dielectric Constant

# Contents

| 1        | Intr | roducti | ion                                      | 2  |

|----------|------|---------|------------------------------------------|----|

|          | 1.1  | Resear  | rch Objectives                           | 4  |

|          | 1.2  | Thesis  | s Outline                                | 5  |

| <b>2</b> | Rev  | view of | PV Inverter Topologies                   | 7  |

|          | 2.1  | PV Sy   | ystem Architectures                      | 8  |

|          |      | 2.1.1   | Centralised Technology                   | 12 |

|          |      | 2.1.2   | String Technology                        | 13 |

|          |      | 2.1.3   | Multi String and AC-Module Technologies  | 13 |

|          |      | 2.1.4   | Current Status of String Technology      | 14 |

|          |      | 2.1.5   | Common Mode Current                      | 15 |

|          | 2.2  | Revie   | w of Single Phase PV Inverter Topologies | 18 |

|          |      | 2.2.1   | Full-Bridge Derived Topologies           | 19 |

CONTENTS xii

|   |     |        | 2.2.1.1   | ulation                                      | 19 |

|---|-----|--------|-----------|----------------------------------------------|----|

|   |     |        | 2.2.1.2   | H5 Inverter                                  | 21 |

|   |     |        | 2.2.1.3   | HERIC Inverter                               | 23 |

|   |     |        | 2.2.1.4   | H6 Inverter                                  | 24 |

|   |     | 2.2.2  | Half-Bri  | dge Derived Topologies                       | 27 |

|   |     |        | 2.2.2.1   | Neutral Point Clamped (NPC) Inverter         | 27 |

|   |     |        | 2.2.2.2   | Active Neutral Point Clamped (ANPC) Inverter | 29 |

|   |     |        | 2.2.2.3   | T-Type Inverter                              | 32 |

|   | 2.3 | Simula | ation-Bas | ed Benchmark and Analysis                    | 34 |

|   | 2.4 | Concl  | usions .  |                                              | 39 |

| 3 | Wio | de-Ban | ıdgap Po  | ower Devices                                 | 40 |

|   | 3.1 | Wide-  | Bandgap   | Material Properties                          | 41 |

|   | 3.2 | State- | of-the-Ar | t WBG Power Devices                          | 46 |

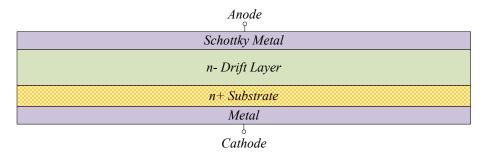

|   |     | 3.2.1  | P-i-N D   | iode and Schottky Barrier Diode              | 46 |

|   |     |        | 3.2.1.1   | Si P-i-N Diode                               | 46 |

|   |     |        | 3.2.1.2   | SiC Schottky Barrier Diode                   | 49 |

|   |     | 3.2.2  | SiC MO    | SFET                                         | 51 |

| CONTERNICO | ••  |

|------------|-----|

| CONTENTS   | XII |

| 001(121)   |     |

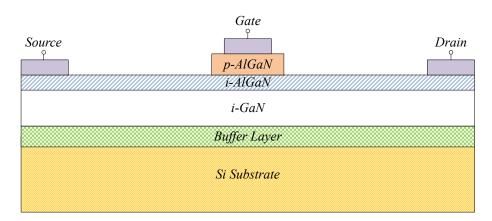

|       | 3.2.3                    | GaN HEMT                                                                                                | 57             |

|-------|--------------------------|---------------------------------------------------------------------------------------------------------|----------------|

| 3.3   | Concl                    | usion                                                                                                   | 59             |

| Si, S | SiC an                   | d GaN Device Benchmark in PV Inverters                                                                  | 60             |

| 4.1   | Static                   | and Dynamic Characterisation of 600 V Devices                                                           | 61             |

|       | 4.1.1                    | Static Characterisation                                                                                 | 63             |

|       |                          | 4.1.1.1 Si P-i-N, SiC SBD and SiC P-i-N                                                                 | 65             |

|       |                          | 4.1.1.2 Si IGBT, SiC MOSFET and GaN HEMT                                                                | 66             |

|       | 4.1.2                    | Gate Driver Requirements                                                                                | 69             |

|       | 4.1.3                    | Dynamic Characterisation                                                                                | 73             |

| 4.2   | Overa                    | ll Comparison                                                                                           | 86             |

| 4.3   | WBG                      | Devices in Power Electronic Converters                                                                  | 87             |

| 4.4   | Bench                    | mark of 600 V Devices in T-Type Inverter                                                                | 88             |

|       | 4.4.1                    | Test Setup                                                                                              | 89             |

|       | 4.4.2                    | Experimental Results                                                                                    | 91             |

|       |                          | 4.4.2.1 Efficiency Performance                                                                          | 91             |

|       |                          | 4.4.2.2 Switching Performance                                                                           | 95             |

| 4.5   | Concl                    | usion                                                                                                   | 99             |

|       | 4.1<br>4.2<br>4.3<br>4.4 | 3.3 Conclusions  Si, SiC and 4.1 Static 4.1.1  4.1.2  4.1.3  4.2 Overal 4.3 WBG  4.4 Bench 4.4.1  4.4.2 | 3.3 Conclusion |

CONTENTS

|   | 5.1 | ANPC Inverter and Test Setup                       | .01 |

|---|-----|----------------------------------------------------|-----|

|   | 5.2 | Experimental Results and Loss Analysis             | .04 |

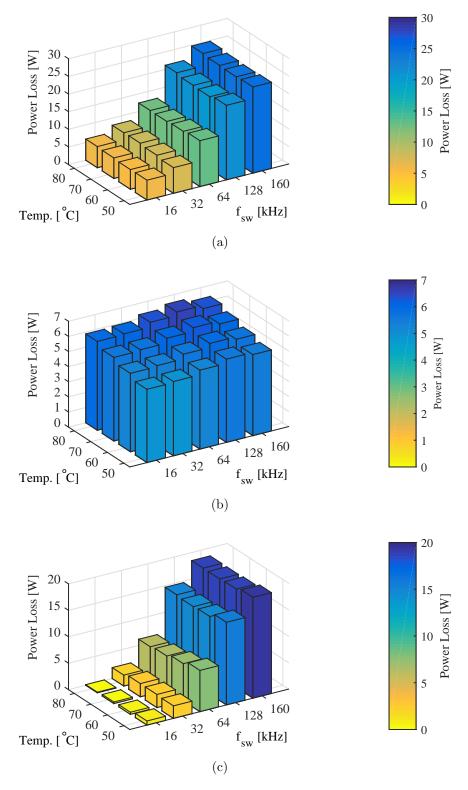

|   |     | 5.2.1 Loss Breakdown                               | .09 |

|   | 5.3 | Impact on Converter Volume                         | .17 |

|   |     | 5.3.1 Heat Sink Design                             | .17 |

|   |     | 5.3.2 Output Filter Design                         | .20 |

|   |     | 5.3.3 Dead Time Impact                             | .31 |

|   | 5.4 | Mission Profile Based Analysis                     | .34 |

|   |     | 5.4.1 Simulation Results                           | .41 |

|   |     | 5.4.1.1 Overall Power Loss and Energy Generation 1 | .43 |

|   |     | 5.4.1.2 Thermal Stress Comparison                  | 45  |

|   | 5.5 | Conclusions                                        | .52 |

| 6 | WB  | G in Higher Power Applications 1                   | 53  |

|   | 6.1 | Review of Five-Level Inverter Topologies           | .54 |

|   | 6.2 | Proposed Inverter Topology                         | .57 |

|   |     | 6.2.1 Switching States                             | .58 |

|   |     | 6.2.2 Commutation Scheme                           | .59 |

|   | 6.3 | Simulation Results                                 | 62  |

CONTENTS

|              | 6.4 | Experi   | imental Results                     | 167 |

|--------------|-----|----------|-------------------------------------|-----|

|              | 6.5 | Conclu   | ısion                               | 170 |

| 7            | Con | ıclusioı | n and Future Works                  | 171 |

|              | 7.1 | Conclu   | asion                               | 171 |

|              | 7.2 | Future   | e Works                             | 173 |

| $\mathbf{A}$ | Per | forman   | nce Benchmark in H6 Inverter        | 193 |

|              |     | A.0.1    | Test Setup                          | 193 |

|              |     | A.0.2    | Experimental Results                | 196 |

|              |     |          | A.0.2.1 Efficiency Performance      | 196 |

|              |     |          | A.0.2.2 Switching Performance       | 197 |

|              |     | A.0.3    | Grid Connection                     | 202 |

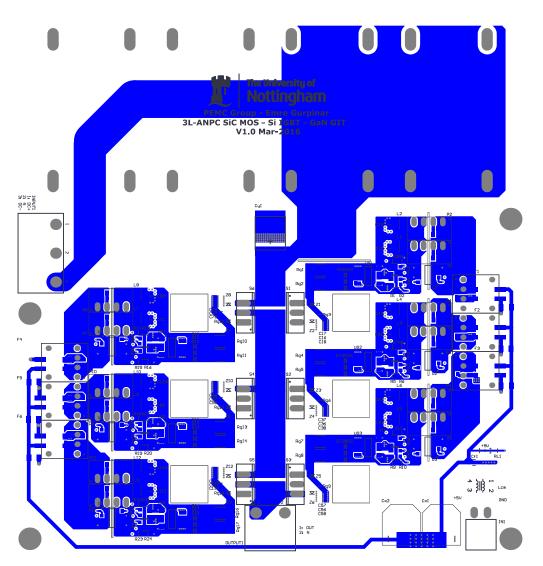

| В            | PCI | B Desi   | gn for GaN HEMT Based ANPC Inverter | 205 |

# List of Figures

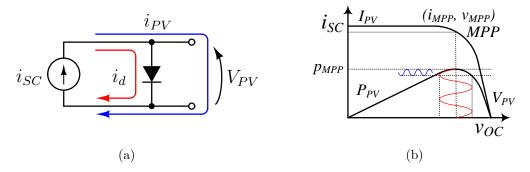

| 2.1  | (a) PV cell model and (b) PV cell characteristics                                        | 9  |

|------|------------------------------------------------------------------------------------------|----|

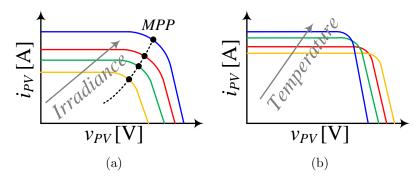

| 2.2  | PV cell characteristics with respect to (a) solar irradiance and (b) ambient temperature | 10 |

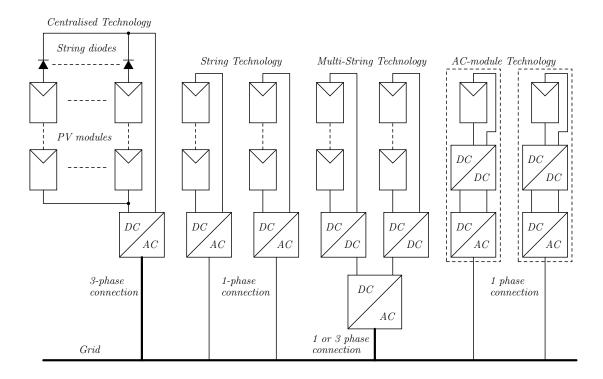

| 2.3  | Historical overview of PV systems [11]                                                   | 12 |

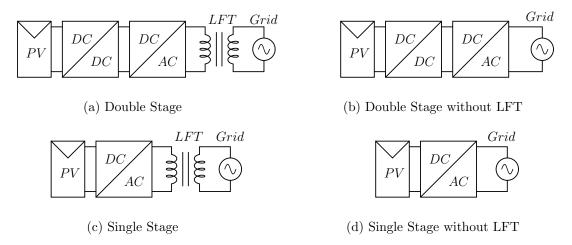

| 2.4  | Conversion stages for grid-connected PV systems                                          | 15 |

| 2.5  | Common-mode current path for full-bridge inverter                                        | 16 |

| 2.6  | Common-mode current path for half-bridge inverter                                        | 16 |

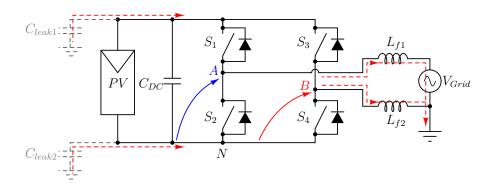

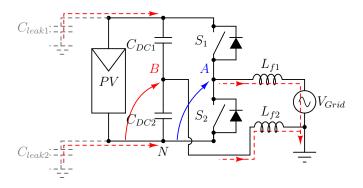

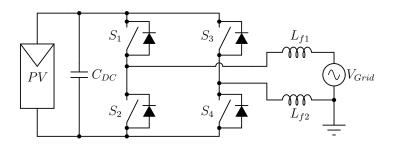

| 2.7  | Full-bridge inverter                                                                     | 19 |

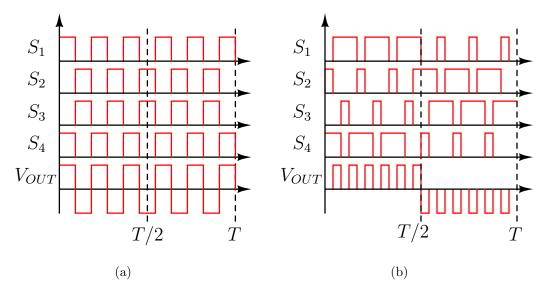

| 2.8  | PWM signals for (a) bipolar modulation and (b) unipolar modulation.                      | 22 |

| 2.9  | H5 inverter                                                                              | 22 |

| 2.10 | PWM Signals for H5 inverter                                                              | 23 |

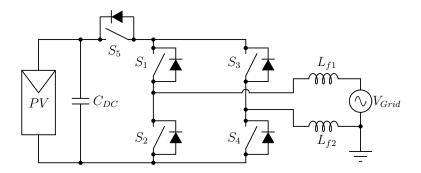

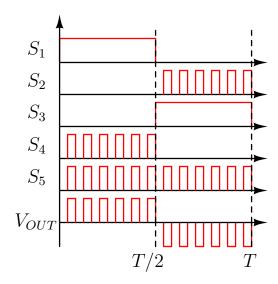

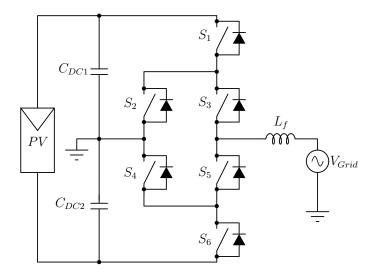

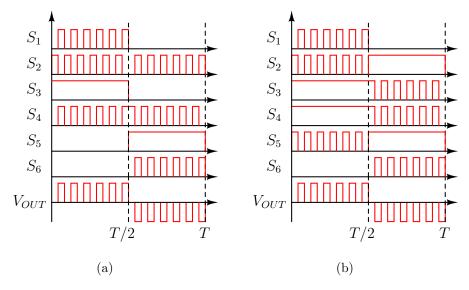

| 2.11 | HERIC inverter                                                                           | 24 |

| 2.12 | PWM Signals for HERIC inverter                                                           | 25 |

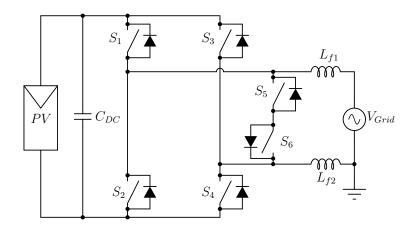

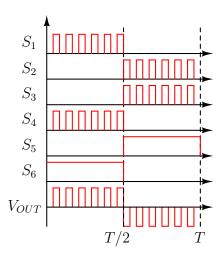

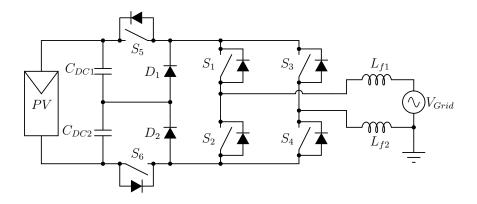

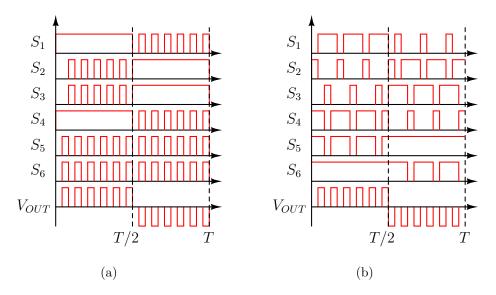

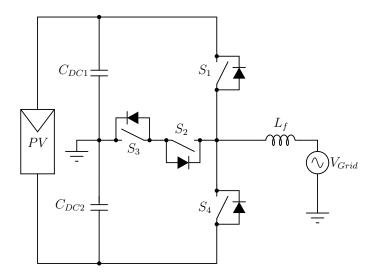

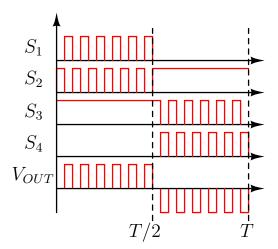

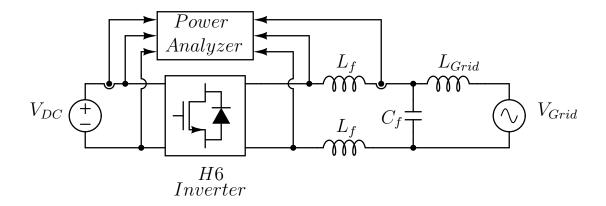

| 2.13 | H6 inverter                                                                                                       | 25 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | PWM signals for (a) standard and (b) UniTL modulation                                                             | 26 |

| 2.15 | Neutral-point-clamped (NPC) inverter                                                                              | 28 |

| 2.16 | PWM signals for NPC inverter                                                                                      | 29 |

| 2.17 | Active neutral-point-clamped (ANPC) inverter                                                                      | 30 |

| 2.18 | PWM signals for (a) conventional modulation and (b) optimised modulation for reverse conduction capability        | 31 |

| 2.19 | T-Type inverter                                                                                                   | 33 |

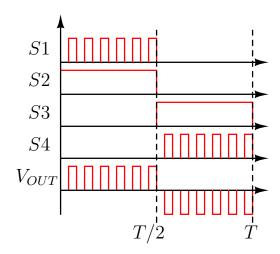

| 2.20 | PWM signals for T-Type inverter                                                                                   | 33 |

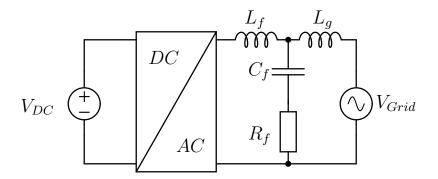

| 2.21 | Grid connected string inverter                                                                                    | 34 |

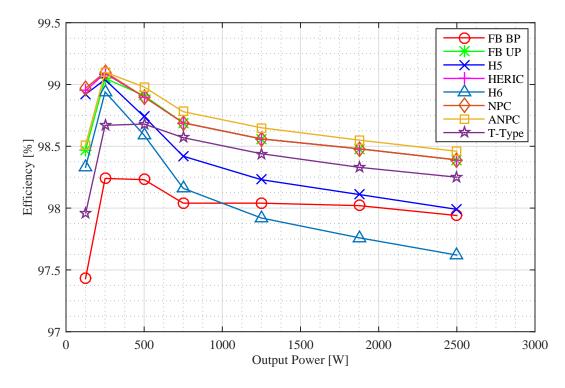

| 2.22 | Efficiency comparison of full bridge and neutral point clamped based inverters under different load conditions    | 35 |

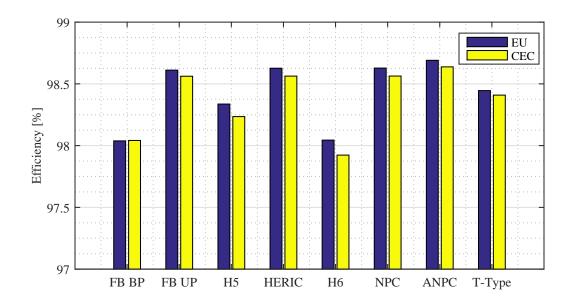

| 2.23 | Efficiency comparison of full-bridge and half-bridge derived inverters based on EU and CEC efficiency definitions | 38 |

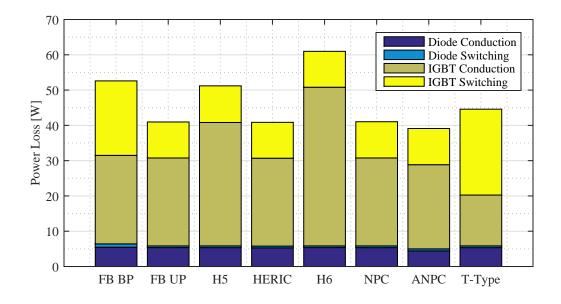

| 2.24 | Semiconductor loss breakdown for each converter at 2.5 kW output power                                            | 38 |

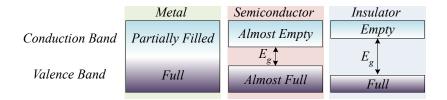

| 3.1  | Simplified energy diagram of solid metal, semiconductor and insulators.                                           | 42 |

| 3.2  | Leakage currents in a P-i-N diode under reverse bias voltage [57]                                                 | 43 |

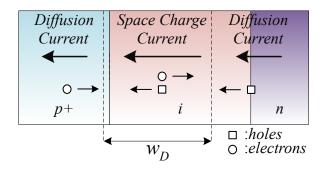

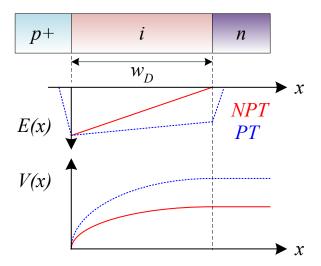

| 3.3  | Electric field and voltage across depletion region in a P-i-N diode                                               | 45 |

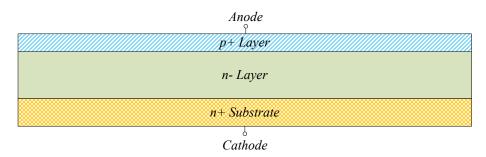

| 3.4  | P-i-N diode structure                                                                                             | 47 |

| 3.5  | SiC based planar Schottky barrier diode structure                                                                                                                                            | 50 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

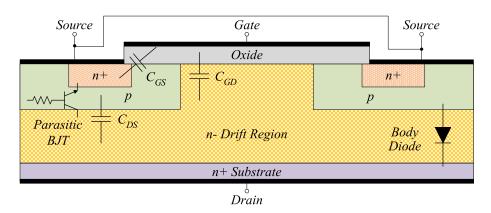

| 3.6  | Vertical enhancement mode MOSFET structure                                                                                                                                                   | 52 |

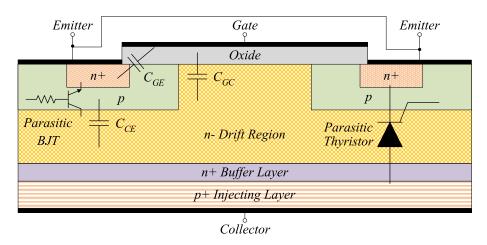

| 3.7  | Vertical IGBT structure                                                                                                                                                                      | 55 |

| 3.8  | Enhancement mode GaN HEMT structure                                                                                                                                                          | 58 |

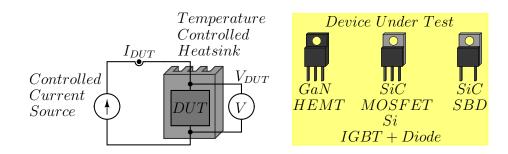

| 4.1  | Test setup for conduction performance analysis                                                                                                                                               | 65 |

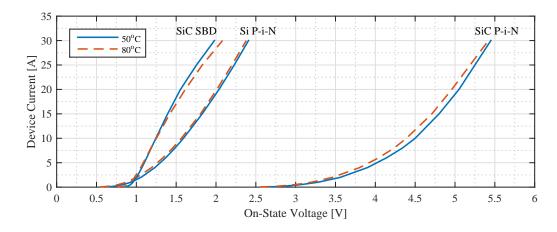

| 4.2  | On-state characteristic of Si P-i-N diode, SiC SBD and SiC P-i-N diode.                                                                                                                      | 66 |

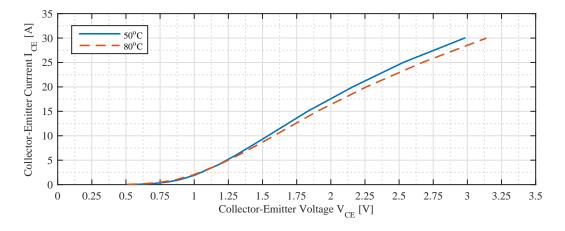

| 4.3  | On-state characteristic of Si IGBT with 15 V gate-emitter voltage                                                                                                                            | 66 |

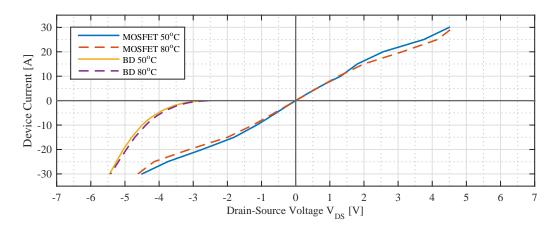

| 4.4  | On-state and body diode characteristic of SiC MOSFET with 20 V gate-source voltage                                                                                                           | 67 |

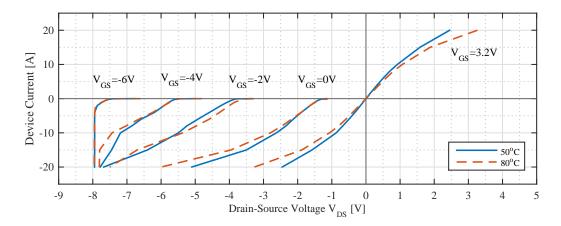

| 4.5  | On-state and reverse conduction characteristics of GaN HEMT with different gate-source voltages                                                                                              | 68 |

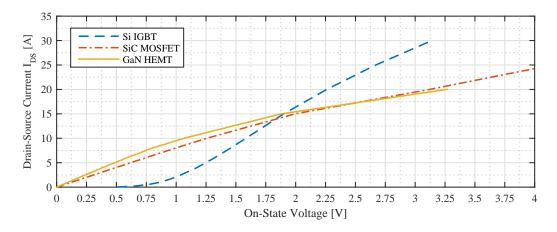

| 4.6  | Comparison of on-state characteristic of Si IGBT, SiC MOSFET and GaN HEMT at 80 °C case temperature                                                                                          | 69 |

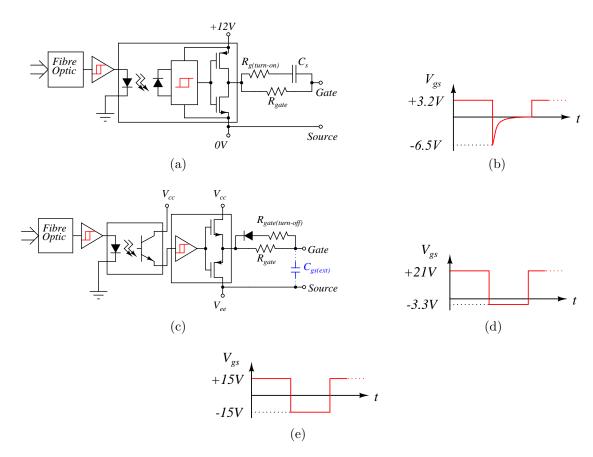

| 4.7  | Gate driver schematics and waveforms: (a) GaN HEMT gate driver, (b) GaN HEMT gate waveform, (c) SiC MOSFET and Si IGBT gate driver, (d) SiC MOSFET gate waveform, (e) Si IGBT gate waveform. | 71 |

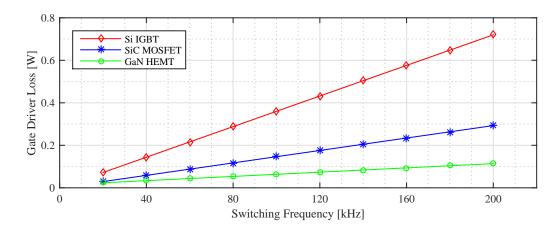

| 4.8  | Gate loss comparison of single Si IGBT, SiC MOSFET and GaN HEMT.                                                                                                                             | 72 |

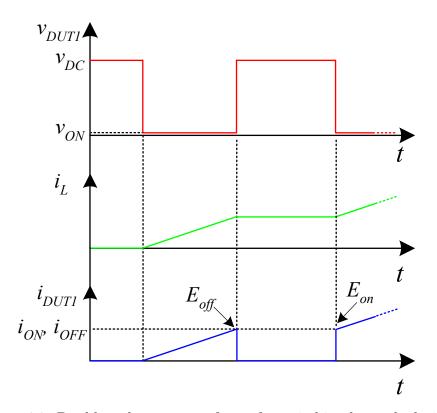

| 4.9  | Double pulse test waveforms for switching loss calculation                                                                                                                                   | 74 |

| 4.10 | Double pulse test configuration for switching analysis of Si, SiC and GaN devices.                                                                                                           | 75 |

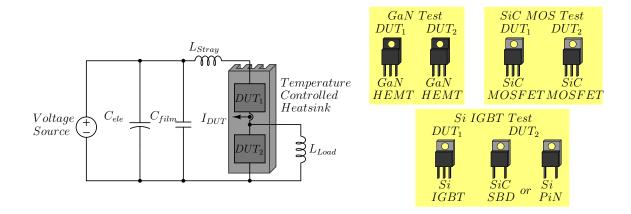

| 4.11 | Switching waveforms for Si IGBT with Si Diode and SiC SBD: a) Turn-on transition b) Turn-off transition                                                                         | 76 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

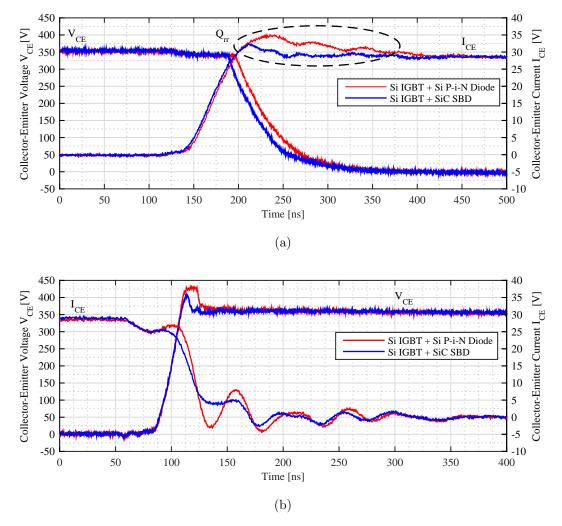

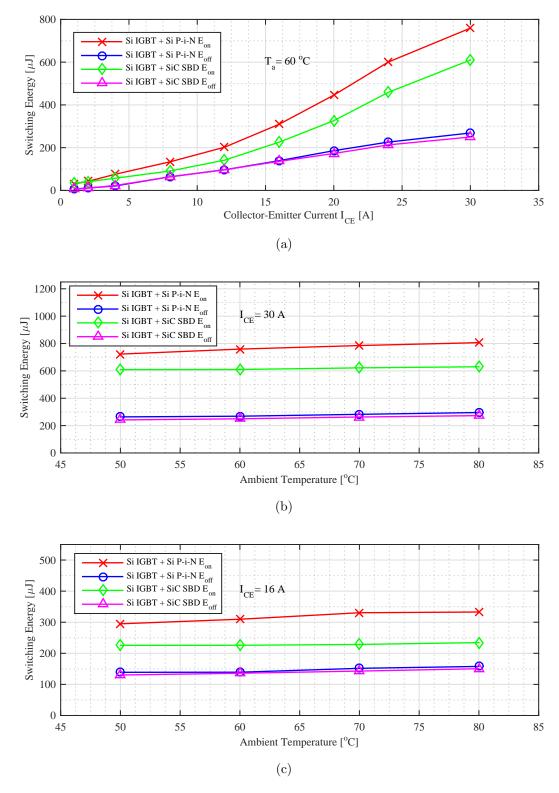

| 4.12 | Turn-on and turn-off switching loss of Si IGBT with Si Diode and SiC SBD: a) 60 °C ambient temperature, b) 30 A collector-emitter current and c) 16 A collector-emitter current | 79 |

| 4.13 | Switching waveforms for SiC MOSFET: a) Turn-on transition b) Turn-off transition                                                                                                | 80 |

| 4.14 | Turn-on and turn-off switching loss of SiC MOSFET: a) 60 °C ambient temperature b) 30 A and 16 A drain-source current                                                           | 81 |

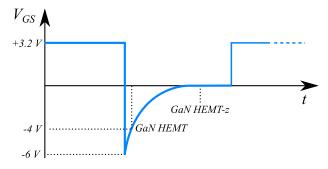

| 4.15 | Illustration of applied gate-source drive voltage waveform for GaN HEMT                                                                                                         | 81 |

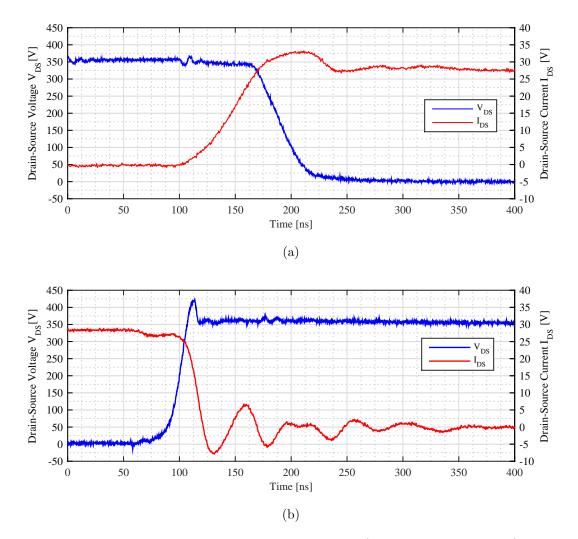

| 4.16 | Switching waveforms for GaN HEMT: a) Turn-on transition b) Turn-off transition                                                                                                  | 82 |

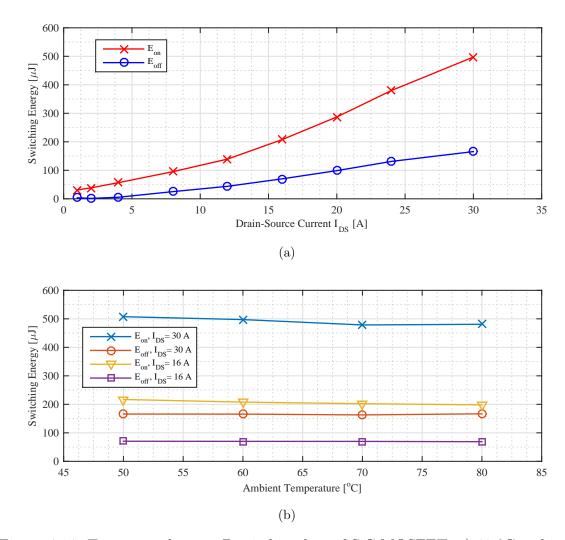

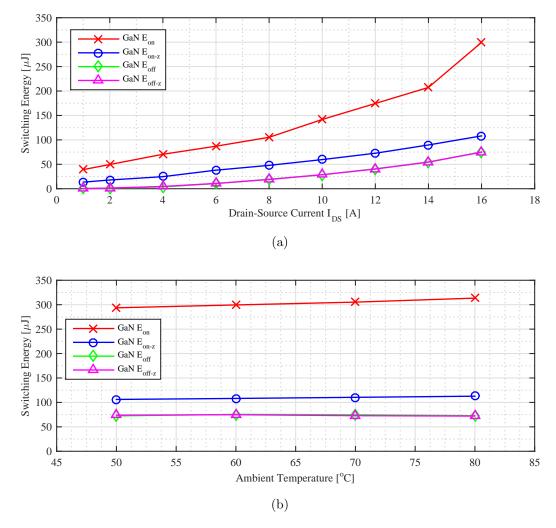

| 4.17 | Turn-on and turn-off switching loss of GaN HEMT: a) 60 °C ambient temperature b) 16 A collector-emitter current                                                                 | 83 |

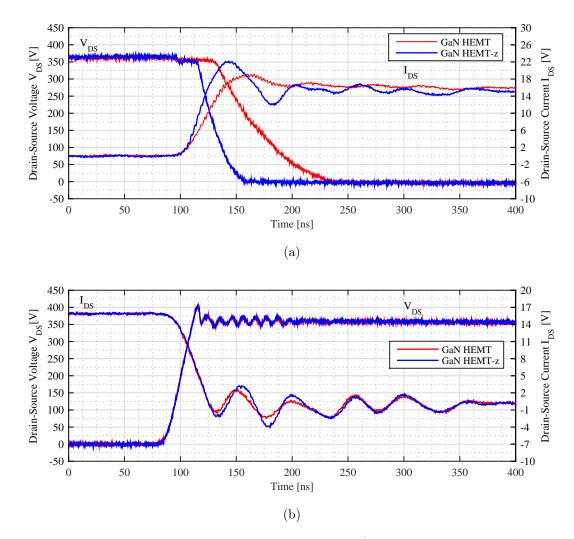

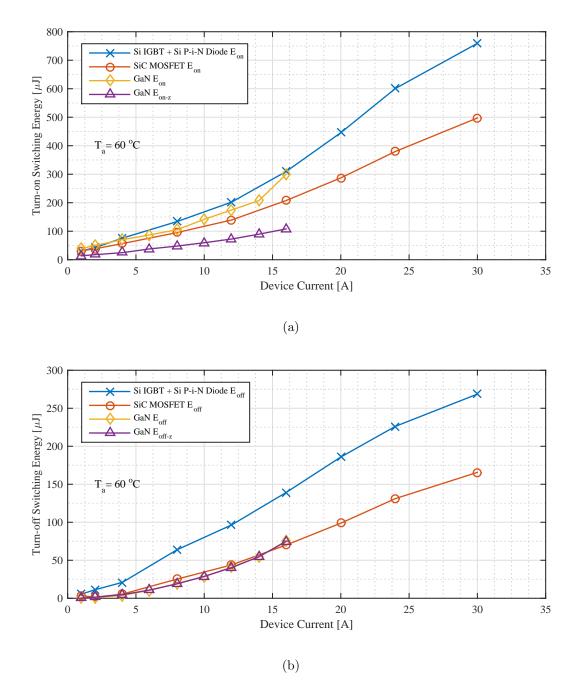

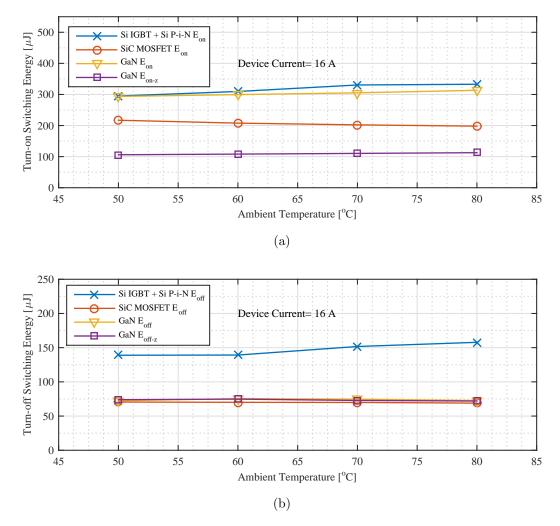

| 4.18 | Switching loss comparison of Si IGBT, SiC MOSFET and GaN HEMT: a) Turn-on at 60 °C ambient temperature b) Turn-off at 60 °C ambient temperature                                 | 84 |

| 4.19 | Switching loss comparison of Si IGBT, SiC MOSFET and GaN HEMT: a) Turn-on at 16 A device current b) Turn-off at 16 A device current.                                            | 85 |

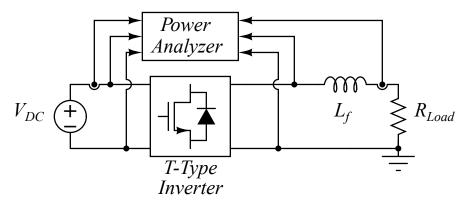

| 4.20 | Test setup for T-Type inverter                                                                                                                                                  | 91 |

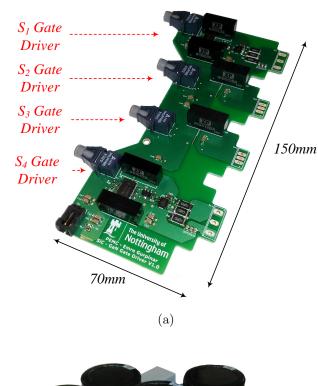

| 4.21 | Single phase T-type inverter: (a) gate driver and (b) power cell                                                                                                                | 92 |

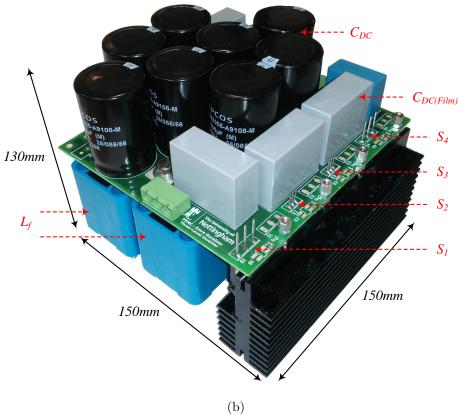

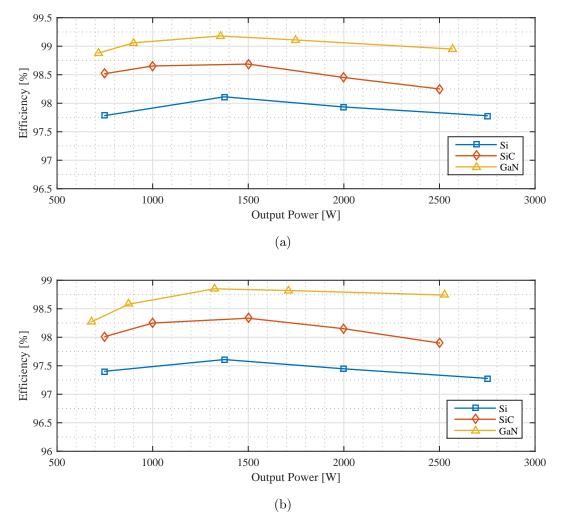

| 4.22 | Efficiency comparison at: (a) 16 kHz and (b) 32 kHz switching frequencies at 50 °C heatsink temperature                                                                                                            | 93  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

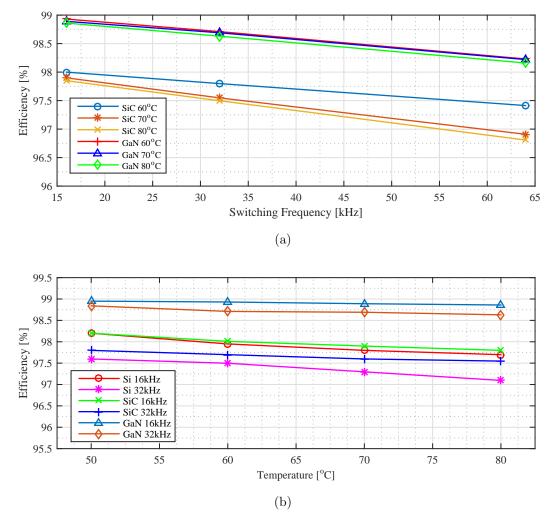

| 4.23 | Efficiency vs switching frequency comparison at different heatsink temperatures for (a) SiC and GaN , and (b) efficiency vs temperature comparison for SiC, GaN and Si at 16 kHz and 32 kHz switching frequencies. | 96  |

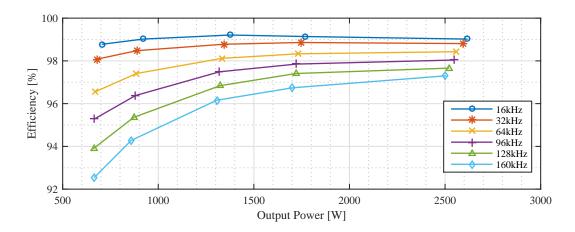

| 4.24 | Efficiency versus output power of SiC + GaN inverter at 50 °C heatsink temperature and between 16 kHz and 160 kHz switching frequencies.                                                                           | 97  |

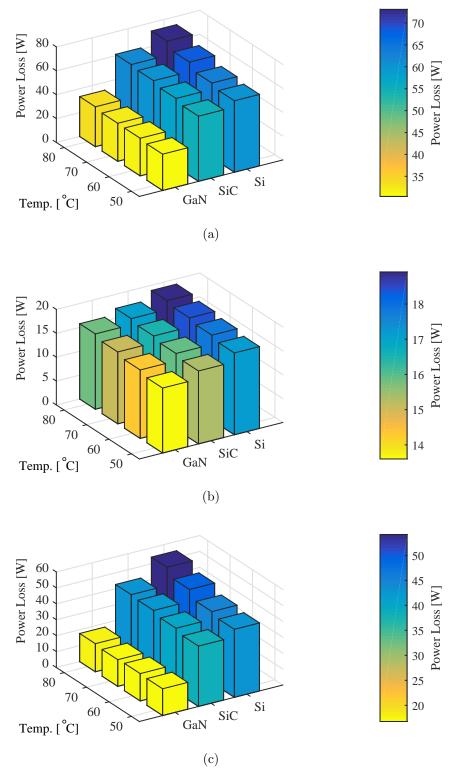

| 4.25 | Loss breakdown for GaN, SiC and Si based converter at 1.3 kW output, 32 kHz switching frequency: (a) total power device loss, (b) conduction loss, (c) switching loss                                              | 98  |

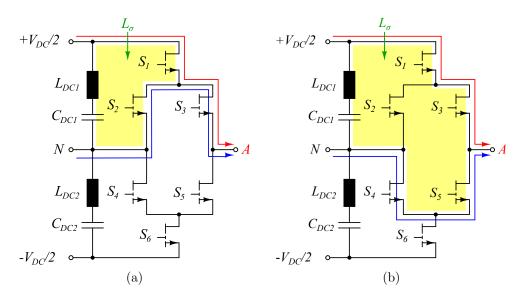

| 5.1  | Commutation loops in ANPC from positive to neutral states: (a) positive state to upper neutral state (b) positive state to lower neutral state                                                                     | 102 |

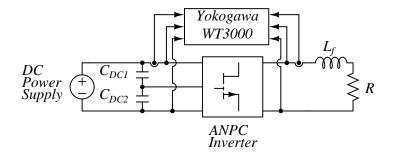

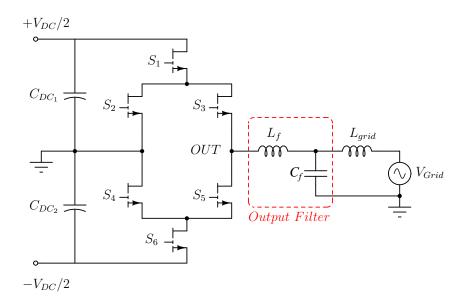

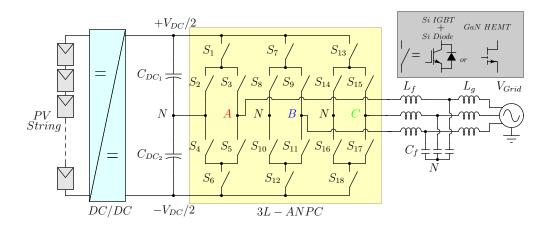

| 5.2  | Single phase GaN HEMT based ANPC inverter                                                                                                                                                                          | 103 |

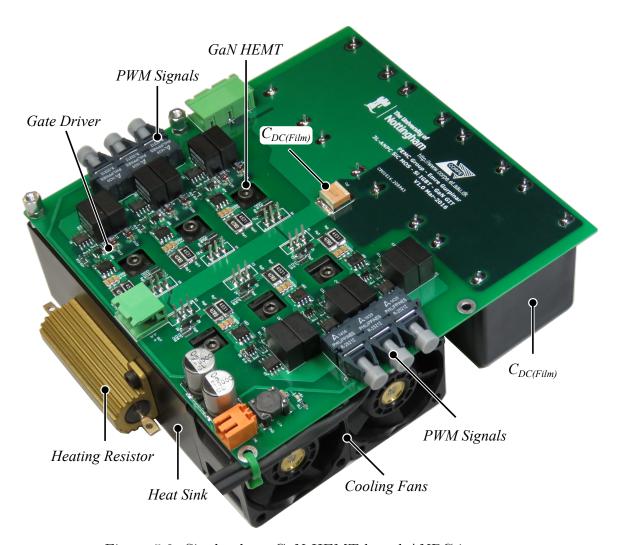

| 5.3  | Test setup for GaN HEMT based ANPC inverter                                                                                                                                                                        | 103 |

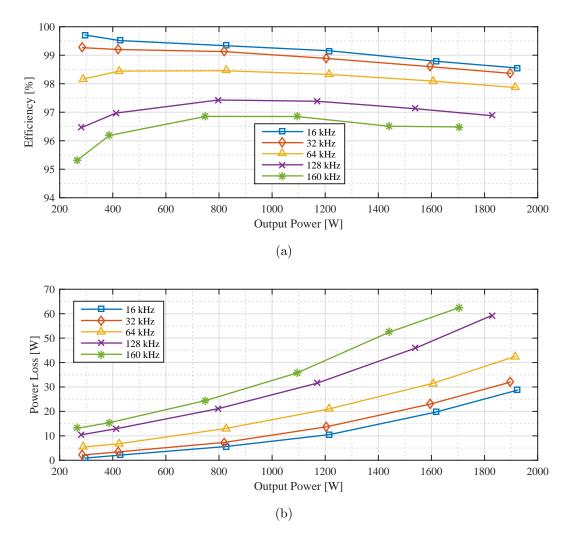

| 5.4  | Performance of GaN HEMT based ANPC power cell versus output power at 50 $^o\mathrm{C}$ heat sink temperature: a) efficiency, b) power loss 1                                                                       | 106 |

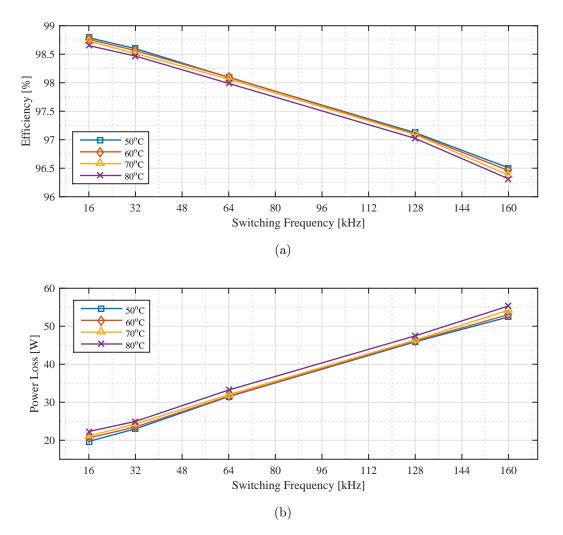

| 5.5  | Performance of GaN HEMT based ANPC power cell versus switching frequency at 2 kW output power: a) efficiency, b) power loss                                                                                        | 107 |

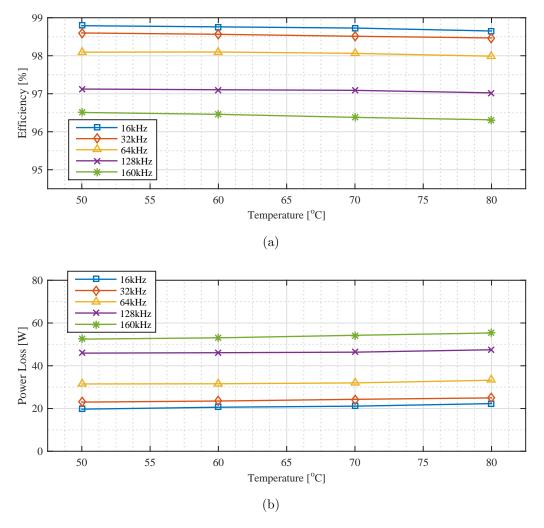

| 5.6  | Performance of GaN HEMT based ANPC power cell versus heat sink temperature at 2 kW output power: a) efficiency, b) power loss                                                                                      | 108 |

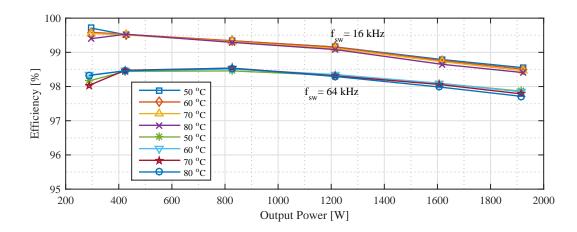

| 5.7  | Efficiency of GaN based ANPC power cell versus output power for 16 kHz and 64 kHz switching frequencies at different heat sink temperatures.                                                                       | 109 |

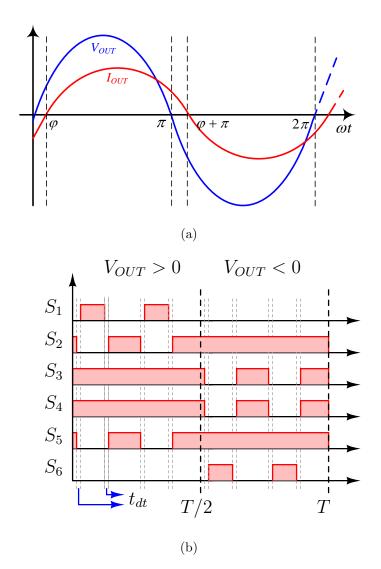

| 5.8  | a) Approximated output voltage and current waveforms for loss analysis and b) PWM signals for ANPC inverter with dead time                                                                                                                                                                                                                             | 110 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

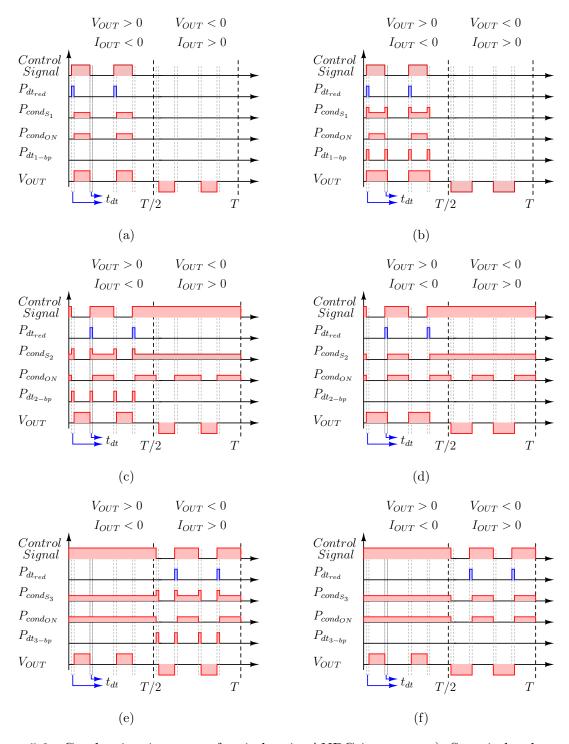

| 5.9  | Conduction instants of switches in ANPC inverter: a) $S_1$ switch when power factor is equal to 1, b) $S_1$ switch when power factor is equal to 0, c) $S_2$ switch when power factor is equal to 1, d) $S_2$ switch when power factor is equal to 0, e) $S_3$ switch when power factor is equal to 1, f) $S_3$ switch when power factor is equal to 0 | 114 |

| 5.10 | Loss breakdown for GaN based ANPC converter at 1.3 kW output: (a) total power device loss, (b) conduction loss, (c) switching loss                                                                                                                                                                                                                     | 116 |

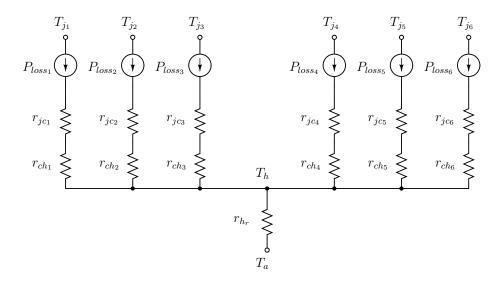

| 5.11 | Thermal network for ANPC inverter                                                                                                                                                                                                                                                                                                                      | 118 |

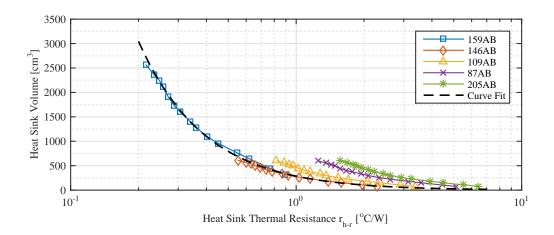

| 5.12 | Commercial naturally cooled heat sink volumes [100]                                                                                                                                                                                                                                                                                                    | 119 |

| 5.13 | Heat sink volume versus switching frequency at different heat sink temperatures                                                                                                                                                                                                                                                                        | 119 |

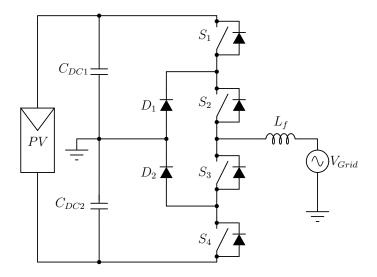

| 5.14 | Grid connected single-phase T-type inverter                                                                                                                                                                                                                                                                                                            | 121 |

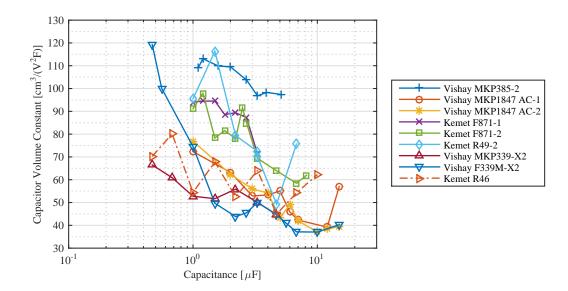

| 5.15 | Capacitor volume constant for various filter capacitors for grid connected applications                                                                                                                                                                                                                                                                | 123 |

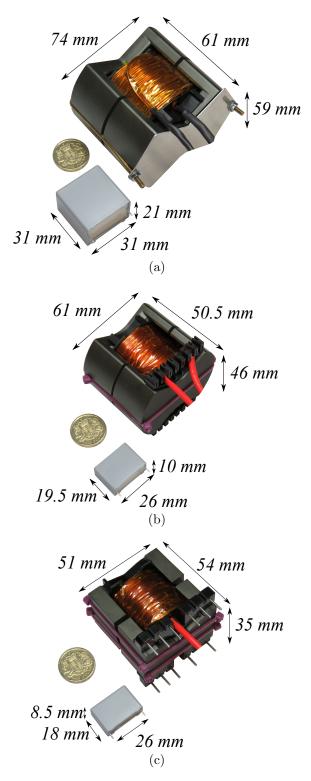

| 5.16 | Designed LC filters for three different switching frequencies: a) 16 kHz b) 64 kHz and c) 128 kHz                                                                                                                                                                                                                                                      | 125 |

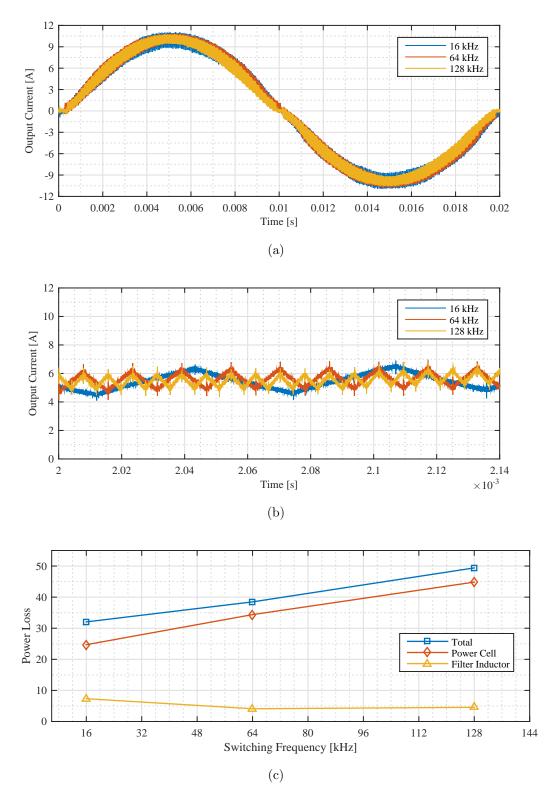

| 5.17 | Output current waveform with designed inductor at 1.6 kW output power and 16 kHz, 64 kHz and 128 kHz switching frequencies: a) fundamental waveform, b) switching ripple, c) total, power cell and inductor loss                                                                                                                                       | 127 |

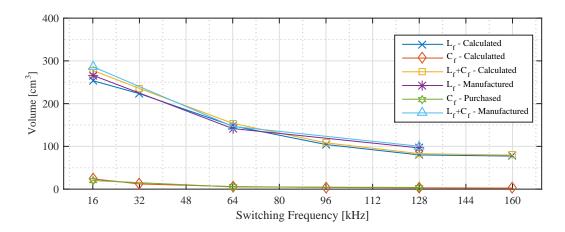

| 5.18 | Calculated and realised inductor, capacitor and total filter volume versus switching frequency                                                                                                                                                                                                                                                         | 128 |

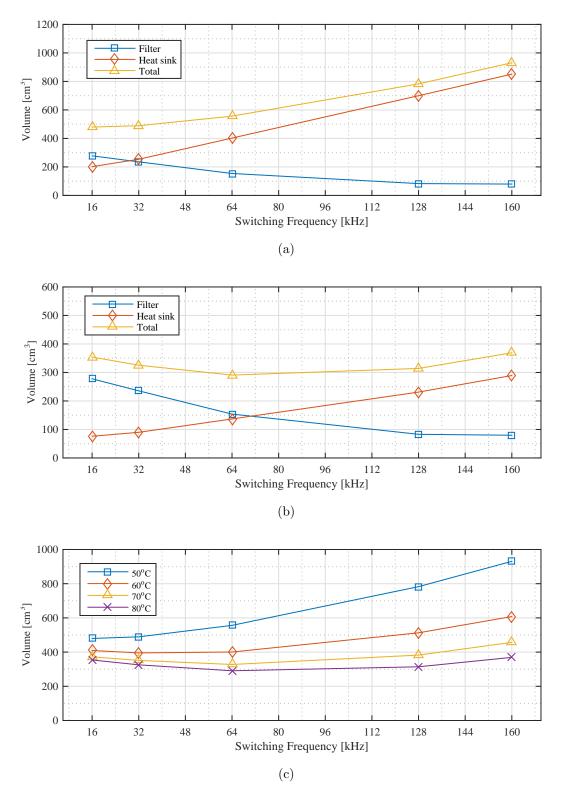

| 5.19 | Filter, heat sink and total volume versus switching frequency: a) at 50 °C heat sink temperature, b) at 80 °C heat sink temperature and c) total volume versus switching frequency at four different heat sink temperature | 129 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

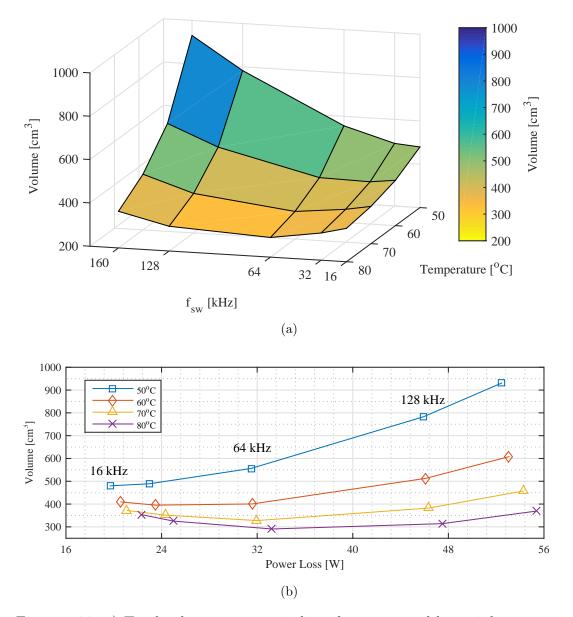

| 5.20 | <ul><li>a) Total volume versus switching frequency and heat sink temperature,</li><li>b) total volume versus power cell loss</li></ul>                                                                                     | 130 |

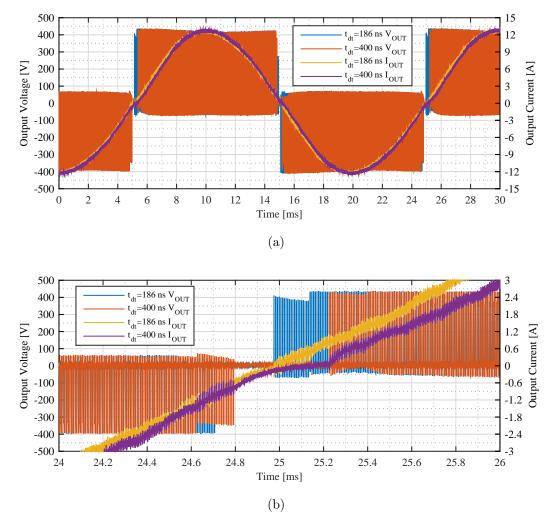

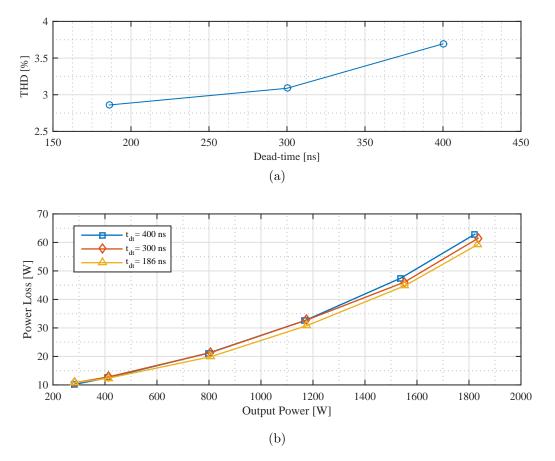

| 5.21 | Effect of different dead time values a) fundamental period, b) zoomed at zero crossing                                                                                                                                     | 132 |

| 5.22 | Effect of different dead time values to a) output current total harmonic distortion, b) power cell loss                                                                                                                    | 133 |

| 5.23 | Grid-connected three-phase double-stage 3L-ANPC inverter with an LCL filter in PV applications                                                                                                                             | 135 |

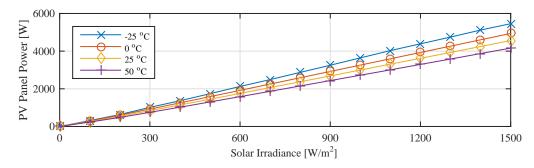

| 5.24 | PV panel output power with respect to solar irradiance and ambient temperature                                                                                                                                             | 137 |

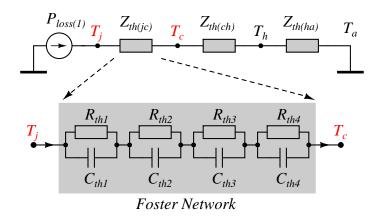

| 5.25 | Thermal model of a single power device, where the RC layer number is related to the device packaging technology as indicated in Table 5.5.                                                                                 | 137 |

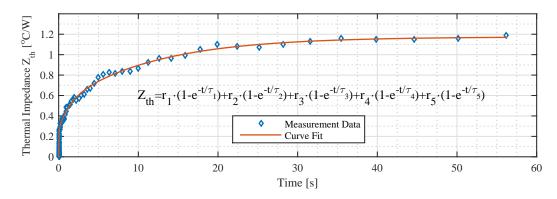

| 5.26 | Thermal impedance of GaN HEMT and applied curve fit for derivation of Foster network                                                                                                                                       | 138 |

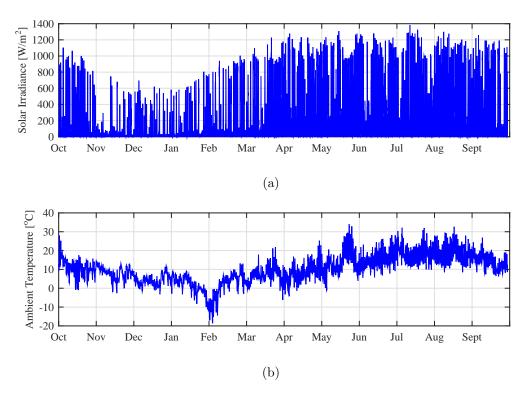

| 5.27 | An annual mission profile used in this thesis: (a) solar irradiance and (b) ambient temperature profile in Aalborg                                                                                                         | 140 |

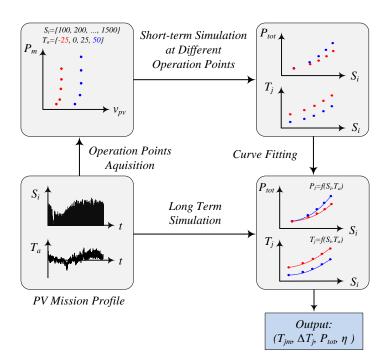

| 5.28 | Realisation of the long-term mission profile based analysis approach                                                                                                                                                       | 140 |

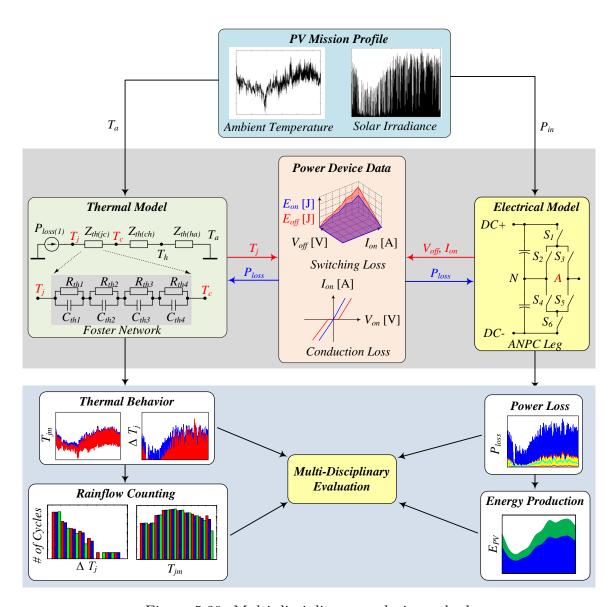

| 5.29 | Multi-disciplinary analysis method                                                                                                                                                                                         | 142 |

LIST OF FIGURES xxiii

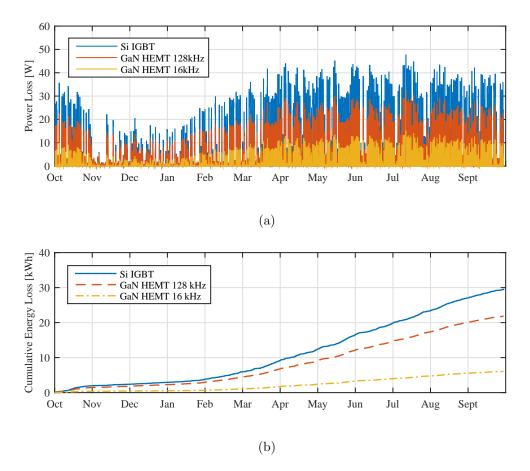

| 5.30 | Estimated annual power losses and cumulative energy loss of the ANPC                                                                                                                                                                                                                                                                                                                         |        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|      | inverter based on different technologies using the mission-profile anal-                                                                                                                                                                                                                                                                                                                     |        |

|      | ysis approach: (a) annual power losses and (b) cumulative energy losses                                                                                                                                                                                                                                                                                                                      | s. 144 |

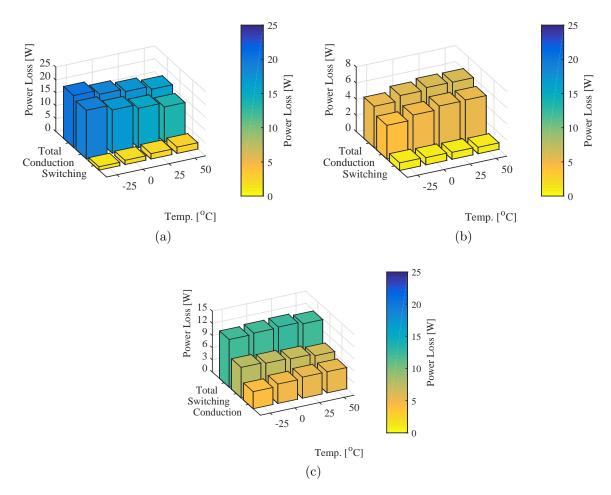

| 5.31 | Semiconductor total, conduction, and switching losses per phase leg of the ANPC inverter based on: (a) Si IGBT technology with a switching frequency of 16 kHz, (b) GaN HEMT technology with a switching frequency of 16 kHz, and (c) GaN HEMT technology with a switching frequency of 128 kHz, where different ambient temperatures with the maximum solar irradiance level are considered | 146    |

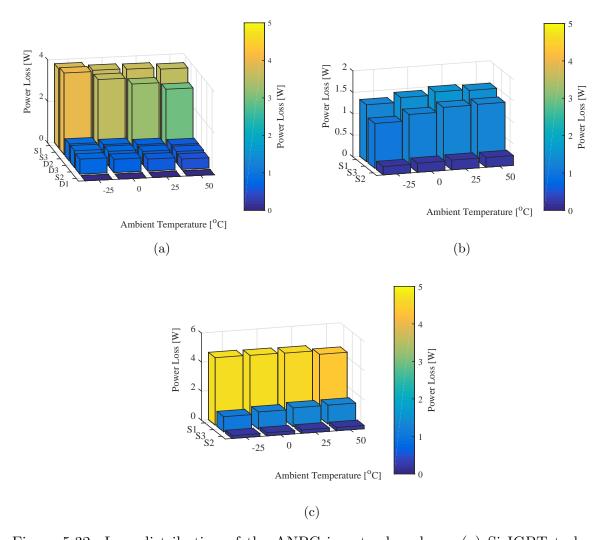

| 5.32 | Loss distribution of the ANPC inverter based on: (a) Si IGBT technology with a switching frequency of 16 kHz, (b) GaN technology with a switching frequency of 16 kHz, and (c) GaN technology with a switching frequency of 300 kHz, where different ambient temperatures with the maximum solar irradiance level are considered                                                             | 147    |

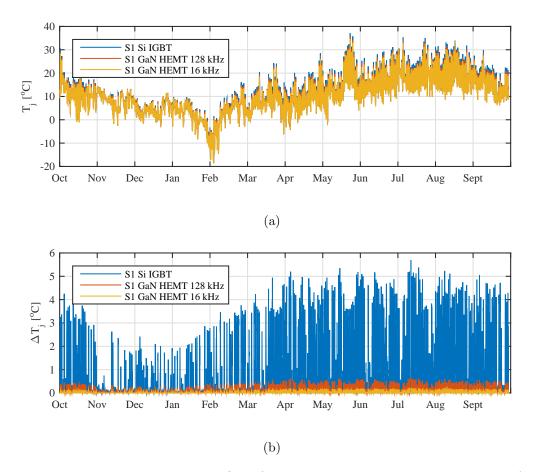

| 5.33 | Thermal loading profiles for the most stressed devices in 3L-ANPC inverter through a year: (a) mean junction temperature and (b) junction temperature variation                                                                                                                                                                                                                              | 149    |

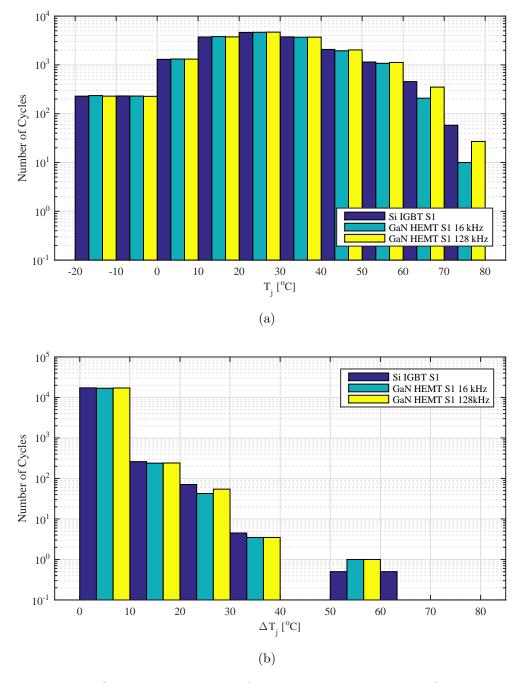

| 5.34 | Rainflow counting results for the thermal loading profiles shown in Fig. 5.33 under a yearly mission profile: (a) mean junction temperature and (b) cycle amplitude                                                                                                                                                                                                                          | 151    |

| 6.1  | 5L-ANPC inverter                                                                                                                                                                                                                                                                                                                                                                             | 155    |

| 6.2  | FUJI five-level inverter                                                                                                                                                                                                                                                                                                                                                                     | 156    |

| 6.3  | Five-level stacked multicell inverter                                                                                                                                                                                                                                                                                                                                                        | 156    |

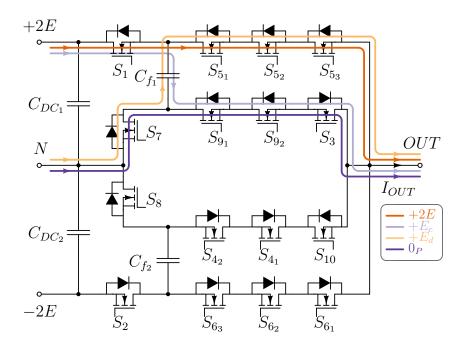

| 6.4  | Proposed five-level inverter topology: EDA5                                                                                                                                                                                                                                                                                                                                                  | 158    |

| 6.5  | Current paths for $+2E$ , $+E_C$ , $+E_D$ and $0_P$ states during positive half of output voltage | 160 |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | or output votage.                                                                                 | 200 |

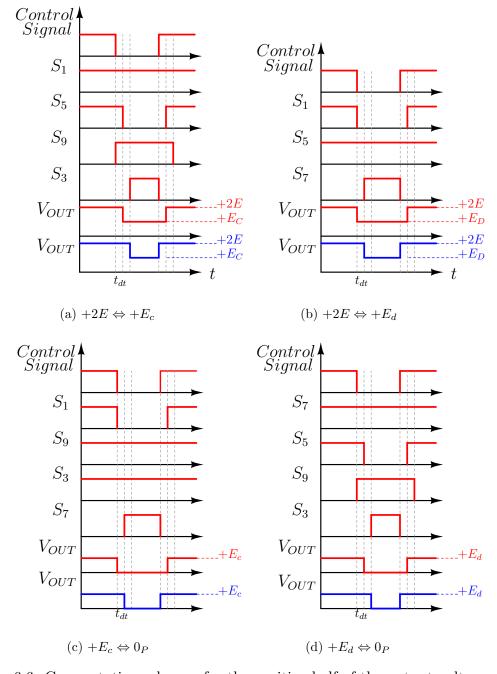

| 6.6  | Commutation schemes for the positive half of the output voltage                                   | 161 |

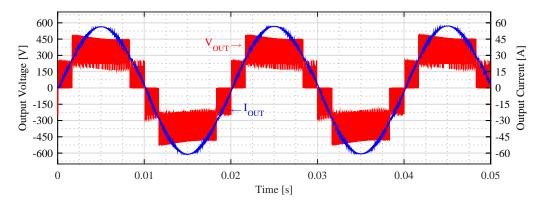

| 6.7  | Simulated output voltage and current waveforms                                                    | 162 |

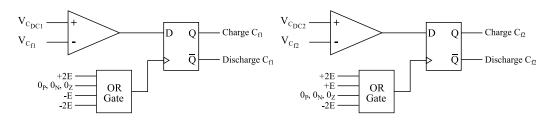

| 6.8  | Floating capacitor voltage control scheme used in simulation and experimental validation          | 164 |

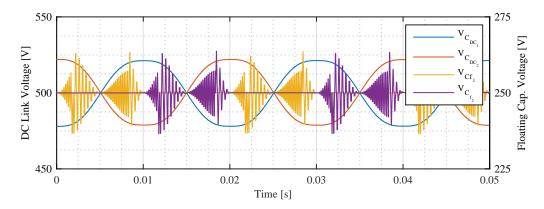

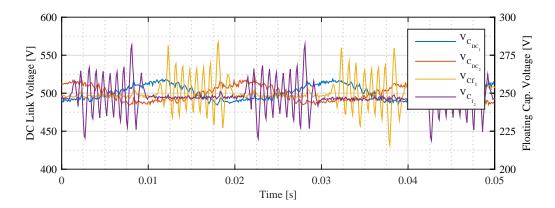

| 6.9  | Simulated $C_{f_1}$ and $C_{f_2}$ floating capacitor voltages                                     | 164 |

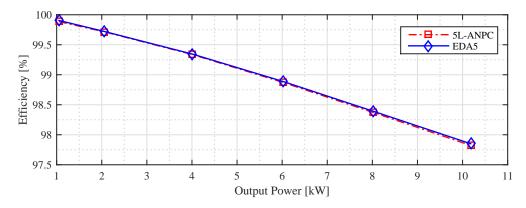

| 6.10 | Efficiency comparison with voltage controlled mode operation                                      | 165 |

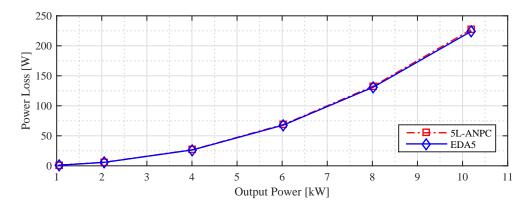

| 6.11 | Efficiency comparison with current controlled mode operation                                      | 165 |

| 6.12 | Power cell loss comparison with voltage controlled mode operation                                 | 166 |

| 6.13 | Power cell loss comparison with current controlled mode operation                                 | 166 |

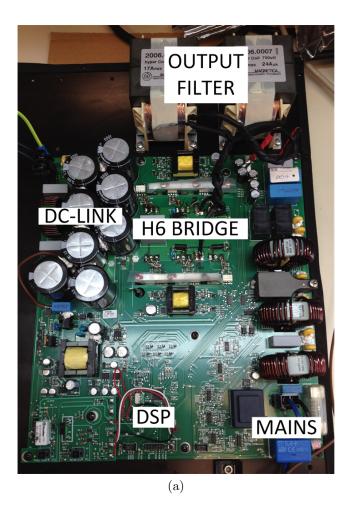

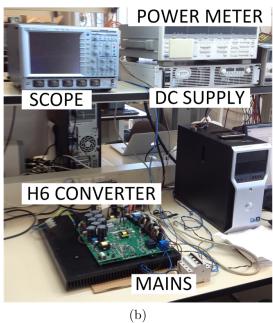

| 6.14 | Single phase 12 kW prototype of proposed five-level hybrid topology: EDA5                         | 168 |

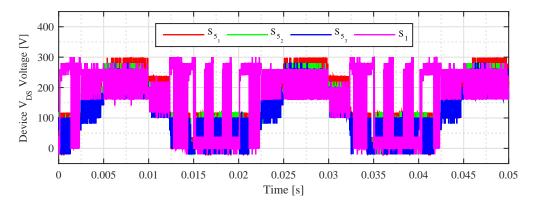

| 6.15 | Voltage across $S_1$ , $S_{5_1}$ , $S_{5_2}$ and $S_{5_3}$ at 1 kV DC link voltage                | 168 |

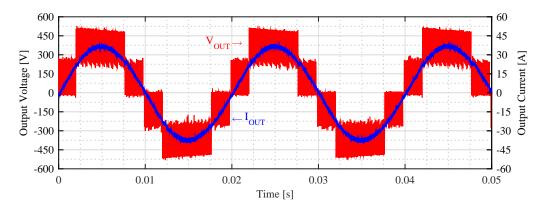

| 6.16 | Experimental output voltage and current waveforms at 7 kW output power                            | 169 |

| 6.17 | DC link and floating capacitor voltages at 7 kW output power                                      | 169 |

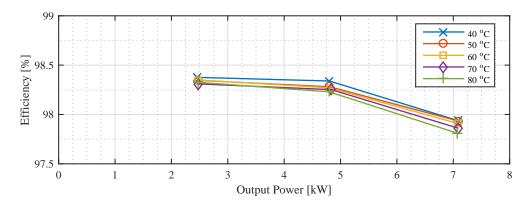

| 6.18 | Efficiency of the prototype at 1 kV DC link voltage and 0.8 modulation index                      | 170 |

| A.1  | Single phase H6 inverter: (a) prototype and (b) test bed                                          | 195 |

| A.2 | Test setup for H6 inverter                                                                                                                                                                | 196 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A.3 | Efficiency comparison at: (a) 10 kHz, (b) 20 kHz and (c) 40 kHz switching frequencies at 60 $^o$ C heatsink temperature                                                                   | 198 |

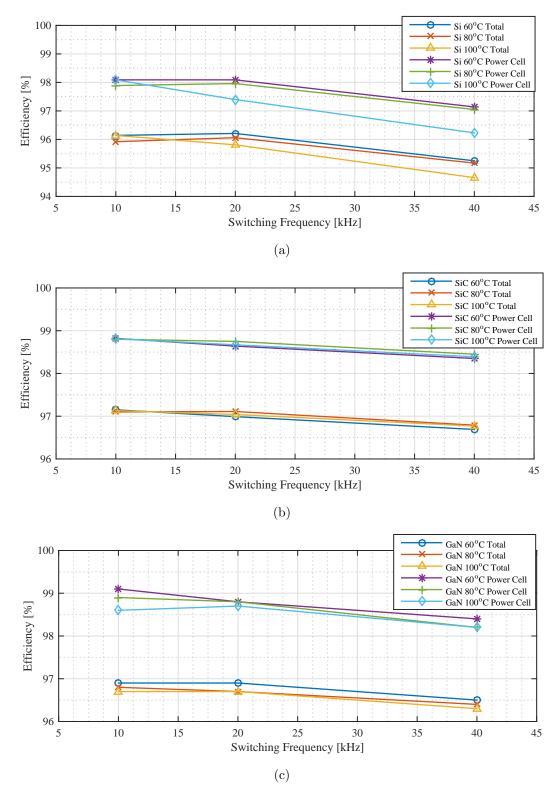

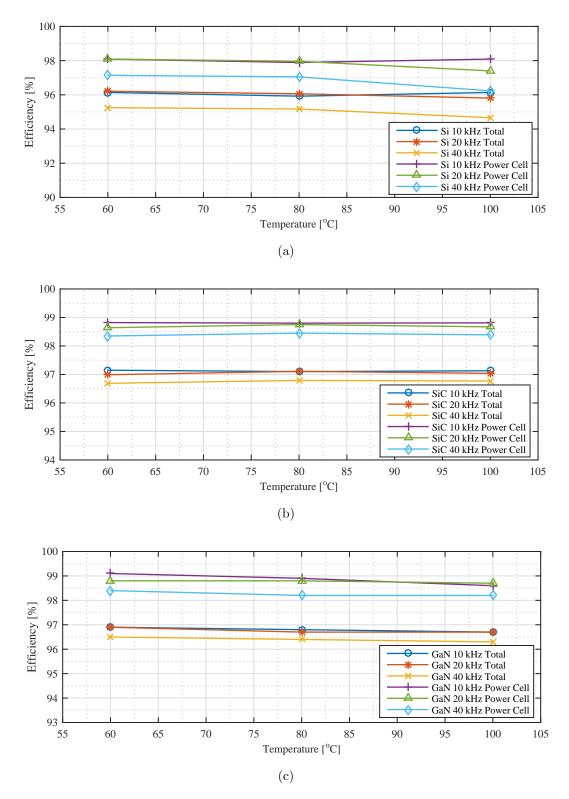

| A.4 | Efficiency comparison of (a) Si IGBT, (b) SiC MOSFET and (c) GaN HEMT based H6 inverter at 1 kW output power and different switching frequencies                                          | 199 |

| A.5 | Efficiency comparison of (a) Si IGBT, (b) SiC MOSFET and (c) GaN HEMT based H6 inverter at 1.5 kW output power and different heatsink temperatures                                        | 200 |

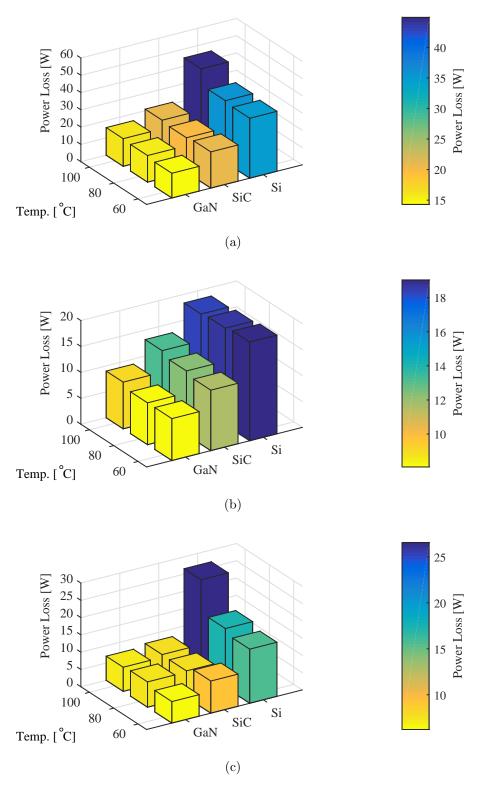

| A.6 | Loss breakdown for GaN, SiC and Si based converter at 1.3 kW output, 40 kHz switching frequency: (a) total power device loss, (b) conduction loss, (c) switching loss                     | 203 |

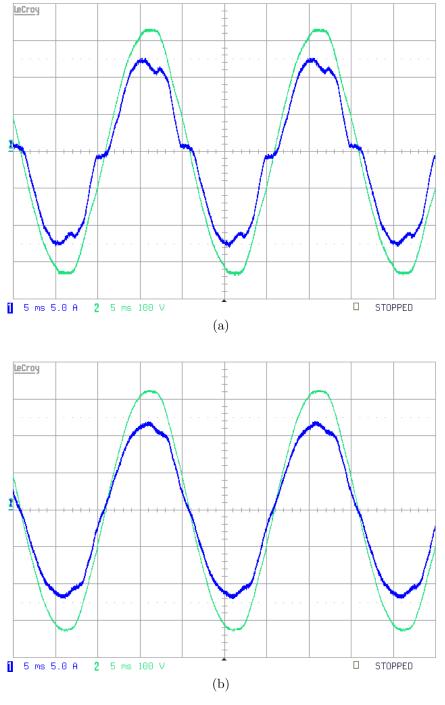

| A.7 | Grid voltage and current waveforms with (a) Si IGBTs and (b) SiC MOSFETs at 40 kHz switching frequency (CH <sub>1</sub> : Grid current 5 A\div, CH <sub>1</sub> : Grid voltage 100 V\div) | 204 |

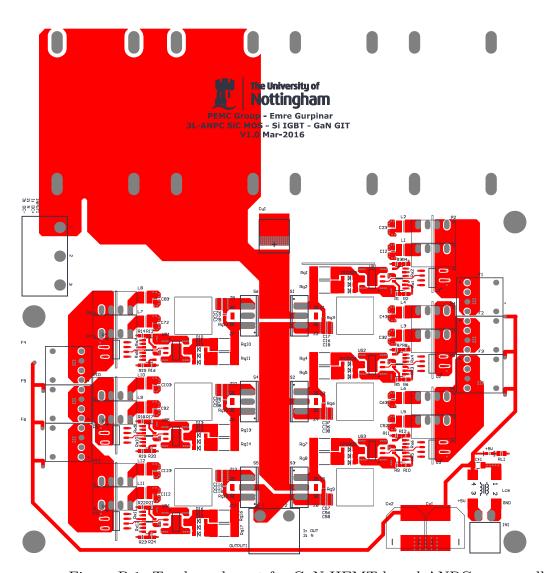

| B.1 | Top layer layout for GaN HEMT based ANPC power cell                                                                                                                                       | 206 |

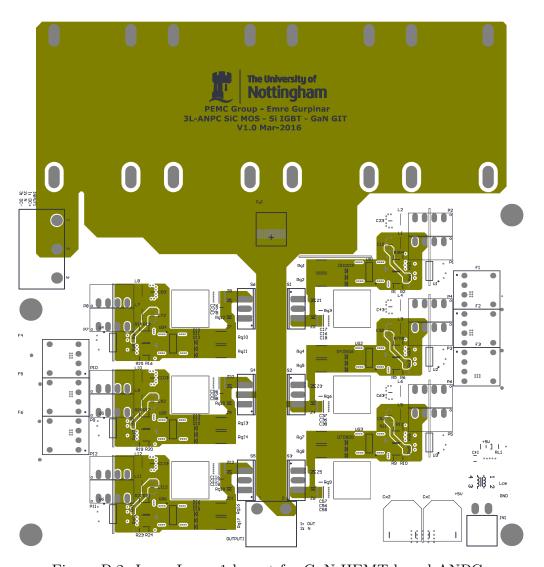

| B.2 | Inner Layer 1 layout for GaN HEMT based ANPC power cell                                                                                                                                   | 207 |

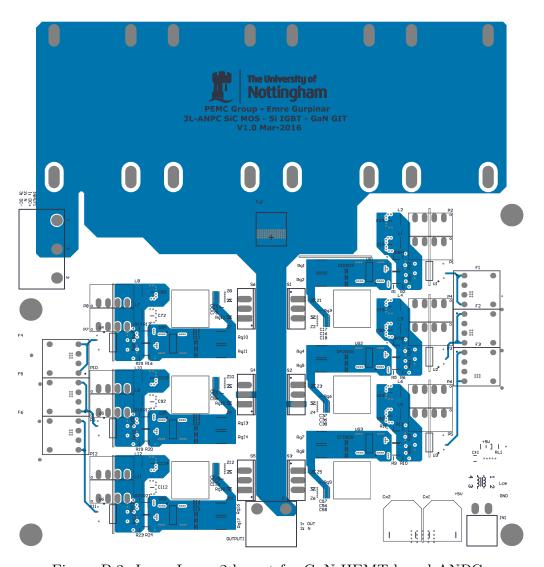

| B.3 | Inner Layer 2 layout for GaN HEMT based ANPC power cell                                                                                                                                   | 208 |

| B.4 | Bottom Layer layout for GaN HEMT based ANPC power cell                                                                                                                                    | 209 |

# List of Tables

| 2.1  | Grid requirements for interconnections of PV systems to the grid [11].                 | 11 |

|------|----------------------------------------------------------------------------------------|----|

| 2.2  | Current harmonic limits for Class A devices                                            | 11 |

| 2.3  | Switching states for full-bridge inverter with bipolar and unipolar modulation scheme. | 21 |

| 2.4  | Switching states for H5 inverter                                                       | 23 |

| 2.5  | Switching states for HERIC inverter                                                    | 24 |

| 2.6  | Switching states for H6 inverter                                                       | 26 |

| 2.7  | Switching states for NPC inverter                                                      | 29 |

| 2.8  | Switching states for ANPC inverter                                                     | 30 |

| 2.9  | Switching states for T-Type inverter                                                   | 32 |

| 2.10 | Simulation conditions for full-bridge and neutral point clamped based inverters        | 35 |

| 2.11 | Acronyms for the simulated topologies presented in Table 2.12                          | 36 |

| 2.12 | Comparison table for different inverter topologies                                     | 36 |

LIST OF TABLES

| 3.1 | Material properties of Si and WBG materials [55], [59]                                             | 42  |

|-----|----------------------------------------------------------------------------------------------------|-----|

| 4.1 | Si P-i-N diode and SiC SBD parameters                                                              | 62  |

| 4.2 | GaN HEMT, SiC MOSFET and Si IGBT parameters                                                        | 64  |

| 4.3 | Overall Comparison of Si IGBT, SiC MOSFET and GaN HEMT. $$                                         | 86  |

| 4.4 | Converter Parameters and Test Conditions                                                           | 90  |

| 5.1 | Converter Parameters and Test Conditions                                                           | 104 |

| 5.2 | Inductance and capacitance values for output filter at different switching frequencies             | 122 |

| 5.3 | Inductor, capacitor and total volume for output filter at 16, 64 and 128 kHz switching frequencies | 124 |

| 5.4 | Converter and System Parameters                                                                    | 136 |

| 5.5 | Thermal parameters for Si IGBT, Si Diode and GaN HEMT                                              | 139 |

| 6.1 | Switching States                                                                                   | 159 |

| 6.2 | Simulation and Converter Parameters                                                                | 163 |

| 6.3 | Prototype Parameters                                                                               | 167 |

| A.1 | Converter Parameters and Test Conditions                                                           | 194 |

## Chapter 1

## Introduction

The ever-increasing demand for energy, limited fossil resources and the need for carbon footprint reduction have raised the awareness for change of the energy production, consumption and management strategies. The aim of creating a low carbon economy with sustainable energy generation and consumption while maintaining energy security has been one of the top priorities for developed and developing countries. The United Kingdom (UK) government, European Union (EU) and United States (US) government have published reports where the importance of low carbon economy and reduction of greenhouses gases have been emphasised, and the increased share of renewable energy sources in electricity generation in the short and long terms has been promised [1], [2].

The renewable energy sources such as wind and photovoltaic (PV) have been at the centre for renewable energy generation. The amount of installed wind power has been increasing rapidly since 1999 and wind power is the major renewable energy source in the world due to increase of wind turbine size and efficiency. In some countries such as Denmark, the aim is to achieve 100 % non fossil-based power generation system by 2050, thanks to large potential of wind along with other renewable sources [3]. In addition to wind power, photovoltaic power has seen strong interest since 2004 and the cumulative installed capacity has increased by factor of 107, from 2000 to

2013 [4]. There are several PV farms in Spain, Germany and Portugal with installed power higher than 40 MW. One of the reasons for increase of PV power penetration to electricity production is the reduction of PV panel price (40 % reduction in 2008) and the other one is advancements in power electronic system, which is the enabling technology for renewable energy systems. Along with high power installations of PV farms, residential scale PV systems have been adopted by the grid users by the subsidies from governments and local authorities in order to reduce the residential electrical energy usage from grid, and potentially feed energy to other users [5].

The share of residential energy generation is increasing rapidly and as mentioned in the previous paragraph, power electronic systems are the enabling technologies for renewable power systems. The power electronic converters provide efficient and flexible connection of residential PV systems to the grid by providing grid synchronisation, maximum power point tracking, anti-islanding and input voltage boosting. As the power generated from a PV panel has to be processed with a power electronic converter, the efficiency and reliability of the converter plays a key role in the overall performance of the system [6]. Therefore, the power electronics research has been focussed on development of systems with higher efficiency and reliability to improve overall performance of the system, reduce cost, increase energy generation and therefore enhance the adoption of PV systems in electrical energy generation.

Two topics have received special attention for residential PV converter development:

1) Converter topologies and 2) Wide-bandgap (WBG) based power semiconductor devices. Innovative converter topologies have been proposed, tailored for PV systems, which provide higher efficiency and lower component count [6]. Moreover, emerging WBG based power semiconductor devices have superior properties in comparison to state-of-the-art Silicon (Si) based power semiconductor devices, and the development of WBG based power devices and penetration to power conversion systems have been announced by US government and European research platforms as one of the priorities in energy research [7], [8]. Hence there is a clear need to assess the impact of emerging WBG power devices in state-of-the-art PV converter topologies to understand the impact of emerging technologies in PV systems.

## 1.1 Research Objectives

The objective of this work is to investigate the impact of emerging WBG power devices on the design, volume, performance and reliability of highly efficient single phase PV inverters.

In this process the following aspects are considered:

- Comparison of state-of-the-art half-bridge and full-bridge based inverter topologies for residential scale transformerless PV systems.

- Benchmarking of Si and WBG based power devices at 600 V blocking class which are suitable for high efficient single-phase inverters. The benchmarking includes the discussion of devices structures, gate drive requirements, static and dynamic characterisation, and application in PV inverter topologies.

- Experimental performance evaluation of residential scale single phase inverters with Si and WBG devices under wide range of operation conditions (e.g. switching frequency, output power and heat sink temperature).

- Optimisation of WBG device based residential scale single phase inverter in terms of inverter volume, switching frequency and efficiency.

- Mission-profile based reliability-driven assessment of WBG and Si devices in a residential scale PV inverter under long term operating conditions.

- Transfer of knowledge gained about WBG devices to higher power applications, such as multilevel inverters.

### 1.2 Thesis Outline

The thesis is structured as follows.

Chapter 2 introduces the present status and the background of PV system architectures. PV cell characteristics, and historical background of PV system architectures have been discussed. Grid requirements for the power converters that is used in PV systems have been presented and the impact of these requirements on converter architectures has been discussed in terms of isolation, efficiency and user safety. Review of full-bridge and half-bridge based state-of-the-art PV inverter topologies, which eliminates common-mode current generation, has been presented including inverter operation principles, and comparison in terms of component count and complexity. This chapter ends with simulation based benchmark and analysis of the reviewed topologies in a single phase, grid connected scenario.

In Chapter 3, material properties of Si and WBG materials, and state-of-the art power devices are discussed. The material properties of Si and WBG are compared and the benefits of WBG materials for power devices in terms of blocking and conduction capability are discussed. The material comparison is followed by discussion of power diodes and controlled devices at 600 V blocking class.

In Chapter 4, benchmark of Si and WBG devices in PV inverters is presented. The benchmarking starts with static and dynamic characterisation of 600 V devices under different current and heat sink temperature conditions. Furthermore, gate driver requirements for Si and WBG devices are evaluated. This is followed by performance evaluation of a T-type inverter with Si and WBG devices under different switching frequency, output power and heat sink temperature conditions.

In Chapter 5, a Gallium Nitride (GaN) based PV inverter is analysed to explore the benefits of GaN devices in PV inverters in terms of efficiency, converter volume reduction (heat sink and output filter) and mission-profile based reliability. The discussion starts with the description of the inverter and test setup, followed by experimental

results including efficiency and power loss under different switching frequency, heat sink temperature and load conditions. This is followed by loss breakdown under different temperature and switching frequency conditions to evaluate performance of devices and influence of static and dynamic losses to power cell efficiency. Furthermore, the impact of GaN devices on converter volume is assessed in terms of heat sink and output filter volume. Finally, evaluation of GaN HEMTs and Si IGBTs is presented considering real-field long-term PV mission profiles (e.g., ambient temperature and solar irradiance) to assess the thermal loading and performance of devices in a three-phase grid-connected configuration.

In Chapter 6, potential benefits of WBG devices at higher power applications is explored. The chapter starts with the review of five-level multilevel topologies, with special focus on hybrid topologies. The review is followed by introduction of a new five-level hybrid inverter, which is suitable for WBG based applications with high efficiency. The details of the proposed topology including switching states and commutation scheme are presented and followed by the simulation results including efficiency comparison with respect to state-of-the-art hybrid topology 5L-ANPC. Finally, the experimental results based on 12 kW prototype are presented discussed.

In Chapter 7, conclusions and future works are discussed.

## Chapter 2

## Review of PV Inverter Topologies

The industrialised economies have been demanding cheap and reliable energy resources in order to produce levels of energy that cannot be achieved by human or animal muscle power since the beginning of industrial revolution. Fossil based natural resources such as coal and petroleum have been widely exploited for this purpose, despite the undesirable side effects such as air pollution and climate change. In  $20^{th}$  century, nuclear based energy production was introduced as an alternative to fossil based resources, but has been recently considered as an unsustainable solution due to safety and political problems. As a result of environmental concerns about fossil fuels, and safety and political concerns about nuclear resources, renewable sources such as photovoltaic, wind and hydro-electric have gained popularity in late  $20^{th}$  century [9]. As 2012, 19% of world's total energy consumption has been provided by renewable sources [10].

Photovoltaic (PV) energy is a key renewable energy resource along with hydro and wind, and as of 2013, the global installed PV capacity has been over 138 GW with a potential of 160 TWh energy generation every year. In addition to the current-installed capacity, the worst case scenario for annual PV installation until 2018 is expected to be around 35 GW [4]. Even with the worst case scenario, there is a strong demand for energy generation with PV systems, where power electronic con-

verters are vital components for realisation of this demand. The intermittent nature of photovoltaic and wind resources require an interface system (e.g. power electronic converter) between the power grid and the source for two reasons: 1) maximum utilization of the source and 2) satisfying the requirements of the power grid. Therefore, renewable power generation is one of the main focus areas of highly efficient and reliable power electronic systems.

In this chapter, first, single stage and double stage PV converter systems are presented. The main advantages and drawbacks of each configuration are discussed. Then some specific aspects of modern inverter systems such as common-mode (CM) current requirements and transformerless topologies are discussed. The review of single phase transformerless topologies that are designed to eliminate CM current and deliver high efficiency are presented. Finally, efficiency and overall comparison of topologies based on simulation results is presented.

## 2.1 PV System Architectures

Photovoltaic panels are used in PV based energy generation systems and are formed by series and/or parallel connected PV cells, which are silicon based pn junctions with large surface area, depending on output power, voltage and current requirements at specified solar irrandiance and ambient temperature. The output of a PV panel is direct current (DC) and variable in terms of output current, voltage and power. Therefore the output of PV panel has to be controlled for operating at maximum available power and converted to alternating current (AC) for grid connected applications. Within this context, the power electronic converters must cater for two main functionalities: 1) maximisation of energy utilisation by means of Maximum Power Point Tracking (MPPT) control; 2) integration with the AC grid by converting the generated electricity from DC to AC (i.e., using DC-AC inverters) in a grid-friendly manner. That is to say, a certain amount of demands to PV systems should be taken into account in the planning, design, and operation phases such as PV panel

characteristics, ambient operating conditions and grid regulations.

The model and characteristics of most common PV cell technologies are presented in Fig. 2.1a and 2.1b respectively [11]. The model and characteristics show that a PV cell operates as a constant DC current source up to maximum power point (MPP) and the cell has to be operated at MPP in order to maximise the energy generation at any ambient temperature and solar irradiance. The output dependence of a PV cell to solar irradiance and ambient temperature is presented in Fig. 2.2a and 2.2b respectively. During steady state operation, the ripple voltage at the output of the PV cell should be minimised in order to minimise power variation and maximise energy generation. The studies show that ripple voltage at the output of PV cell  $(V_{PV})$  should be below 8.5% for achieving 98% utilization ratio [11].

Figure 2.1: (a) PV cell model and (b) PV cell characteristics.

According to [12], the relation between output voltage and current of a PV cell presented in Fig. 2.1a can be expressed as:

$$i_{PV} = i_{pv,cell} - i_{0,cell} \left[ \exp\left(\frac{q \cdot v_{PV}}{a \cdot k \cdot T}\right) - 1 \right]$$

(2.1)

where  $i_{pv,cell}$  is the current generated by the incident light,  $i_{0,cell}$  is the leakage current of the diode, q is the electron charge, k is the Boltzmann constant, T is the temperature of pn junction and a is the diode ideality constant.

Figure 2.2: PV cell characteristics with respect to (a) solar irradiance and (b) ambient temperature.

On the other hand, integration of the PV system to AC grids is regulated and controlled by grid operators based on national grid legislations. The national grid legislations are based on the international standards set by international bodies such as IEEE (Institute of Electrical and Electronic Engineers) and IEC (International Electrotechnical Commission). Most relevant IEC standards for grid-connected PV systems are IEC 61727 "Photovoltaic (PV) Systems - Characteristics of the Utility Interface", IEC 61000 Electromagnetic Compatibility (EMC) and IEC 62116 "Utilityinterconnected photovoltaic inverters - Test procedure of islanding prevention measures". IEC 61727 lays down the requirements for interconnection of PV systems to the utility distribution system including power quality, response to abnormal grid conditions such as voltage deviations and frequency deviations [13]. IEC 62116 defines the test procedure for evaluation of the performance of anti-islanding measures for grid-connected PV systems [14]. Finally, IEC 61000 deals with the limitations of harmonic currents injected to the systems where IEC 61000-3-2 covers for devices up to 16 A per phase [15] and IEC 61000-3-3 covers limitations of voltage fluctuations and flickers impressed on the grid [5], [16]. A summary of some standards regarding interconnections of PV systems to the grid is presented in Tables 2.1. In addition to Table 2.1, current harmonic limits for class A devices, such as solar inverters, with less than 16 A output current are presented in Table 2.2. It is clear that the grid has strict harmonic regulations in order to minimise the impact of the inverter to other equipment connected to the grid. It should be noted that the parameters presented

| Issue                                 | IEC 61727 [13]                         |

|---------------------------------------|----------------------------------------|

| Nominal power                         | 10 kW                                  |

| Harmonic Currents                     | (3-9) 4%                               |

| (Order -h) Limits                     | (11-15) 2%                             |

|                                       | (17-21) 1.5%                           |

|                                       | (23-33) 0.6%                           |

| Maximum THD                           | 5%                                     |

| Power factor at 50% rated power       | 0.90                                   |

| DC current injection                  | Less than 1.0% of rated output current |

| Voltage range for nominal operation   | 85% - 110%                             |

|                                       | (196 V - 253 V)                        |

| Frequency range for nominal operation | $50 \pm 1 \text{ Hz}$                  |

Table 2.1: Grid requirements for interconnections of PV systems to the grid [11].

| IEC 61000-3-2 [15] |                      |                  |                     |  |  |  |  |  |  |  |

|--------------------|----------------------|------------------|---------------------|--|--|--|--|--|--|--|

| Odd Ha             | armonics             | Even Harmonics   |                     |  |  |  |  |  |  |  |

| Order h            | Current [A]          | Order h          | Current [A]         |  |  |  |  |  |  |  |

| 3                  | 2.30                 | 2                | 1.08                |  |  |  |  |  |  |  |

| 5                  | 1.14                 | 4                | 0.43                |  |  |  |  |  |  |  |

| 7                  | 0.77                 | 6                | 0.30                |  |  |  |  |  |  |  |

| 9                  | 0.40                 | $8 \le h \le 40$ | $0.23 \times 8 / h$ |  |  |  |  |  |  |  |

| 11                 | 0.33                 |                  |                     |  |  |  |  |  |  |  |

| 13                 | 0.21                 |                  |                     |  |  |  |  |  |  |  |

| $13 \le h \le 39$  | $0.15 \times 15 / h$ |                  |                     |  |  |  |  |  |  |  |

Table 2.2: Current harmonic limits for Class A devices.

in Table 2.1 and 2.2 apply to regions where IEC regulations are set as standard. Therefore, performance and design of the PV systems must be compatible with the requirements of installed PV array and also requirements from grid operator in the installed region.

Based on the requirements of PV panels and AC grids, various PV systems have been developed throughout the years. Here four main concepts are considered: centralised, string, multi-string and ac-module technologies shown in Fig. 2.3.

Figure 2.3: Historical overview of PV systems [11].

## 2.1.1 Centralised Technology

Development of the electricity generation from PV cells started with centralised inverter technology. In centralised technology, large number of PV modules are connected in series and parallel in order to achieve required DC link voltage and power rating. According to required DC link voltage, PV cells are connected in series to form the string with required voltage capacity, and in order to achieve required power level, the strings are connected in parallel with string diodes in series to avoid current flow between strings. The centralised converter has severe limitations such as high voltage cables between strings, maximum power point mismatch between PV modules and losses in string diodes. The centralised converter was generally based on line commutated converter topologies that suffer from high current harmonics and low power quality.

#### 2.1.2 String Technology

With the advancement in Insulated-Gate Bipolar Transistor (IGBT) and Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) technologies up to 1000 V blocking class, self-commutated (fully controlled) topologies gained interest in PV systems as string inverters in order to overcome relatively high harmonics generated by line-commutated converters (i.e. thyristor based converters), high voltage cabling between strings, maximum power point mismatch and string diode losses. The number of series connected PV modules can also be reduced with string technology by using a DC-DC converter between PV string and an inverter, or a line-frequency transformer at the output of the inverter. The string approach has higher efficiency and reduced cost due to removal of string diodes, separate MPPT applied to each string and modular production [5], [11].

## 2.1.3 Multi String and AC-Module Technologies

Multi string and AC-module technologies in Fig. 2.3 are considered the next-generation concepts for PV inverter systems that will overcome the challenges of the centralised and the string technologies such as operating point mismatch between PV cells, single point of failure that can disable an entire PV string, and can provide flexible PV voltage and power ratings. In multi string configuration, a DC-DC converter is used for each string for maximum power point control and stepping up the PV string voltage to the main DC bus voltage where as the inverter is responsible for feeding the generated power to the AC grid. This configuration allows further expansion of the system by adding new PV string with a DC-DC converter to the existing PV structure. Therefore it provides a flexible design with high efficiency. On the other hand, AC-module technology is proposed as a plug and play concept where one large PV module is connected to a DC-DC converter and an inverter. This configuration removes the mismatch losses between PV modules since each module is controlled by a single converter and therefore each module can be connected directly to grid. The

system provides simplicity and ease of use for the users that do not have knowledge of electrical installations. The main challenges for AC-module are achieving high voltage amplification ratio with high efficiency in the DC-DC converter due to low output voltage of single PV module (5 V  $\sim$  20 V), and high power density with high efficiency. Therefore, novel converter topologies, power device and passive technologies are required along with mass production of the inverters in order to make the technology viable. In addition to this, the stability of the grid and harmonic content in the grid caused by multiple inverters working in parallel are the challenges with AC module technology [17].

#### 2.1.4 Current Status of String Technology

Although the system structures presented in Fig. 2.3 are different, the architecture is eventually the same, with different power ratings based on PV module configuration. Due to the limitations of multi string and AC-module technologies, and high efficiency and simplicity against centralised technology, string is the most popular technology for PV systems. Different power electronics based systems and converter topologies based on single-staged, double-staged, and with or without galvanic isolation have been proposed in literature for string technology based PV systems in order to comply with grid requirements, which are mentioned earlier while maximising PV energy generation. Different converter topologies and system structures based on single and double-staged conversion systems are published and reviewed in literature [11, 18, 19], whereas the aforementioned power electronics converters are widely utilized. Fundamental structures of single stage and double stage conversion systems with and without isolation transformer are presented in Fig. 2.4. The traditional solution with multiple conversion stages and galvanic isolation as shown in Fig. 2.4a provide flexibility in PV module design and maximum user safety with the penalty of increased system cost and efficiency. Isolation transformer or line frequency transformer (LFT) provide galvanic isolation of PV module from grid and can also provide step-up of generated output voltage at lower PV output voltage. In double-staged conversion, a DC-DC converter is responsible for stepping up the PV output voltage and maximum power point tracking, where the LFT can be used to provide galvanic isolation and elimination of ground leakage current. The ground leakage current is caused by the voltage variation across the parasitic capacitance between the PV panel and the earth connection, and the source of voltage variation is the common-mode voltage variation at the output of the inverter, which will be explained in detail in Section 2.1.5. Single stage inverter in Fig. 2.4c is the first designs of grid-connected inverters featured a line-frequency transformer for the coupling to the mains. In recent converters, high-frequency transformer coupling or transformerless inverters are preferred, as shown in Fig. 2.4d, due to higher system efficiency and lower system cost.