# NON-VOLATILE FPGA ARCHITECTURE USING RESISTIVE SWITCHING DEVICES

PATRICK HO WAN CHUAN

B.ENG (HONS) M.SC

DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR

THE DEGREE OF DOCTOR OF PHILOSOPHY (PhD) IN ELECTRICAL & ELECTRONIC

ENGINEERING FROM THE UNIVERSITY OF NOTTINGHAM MALAYSIA CAMPUS

#### **ABSTRACT**

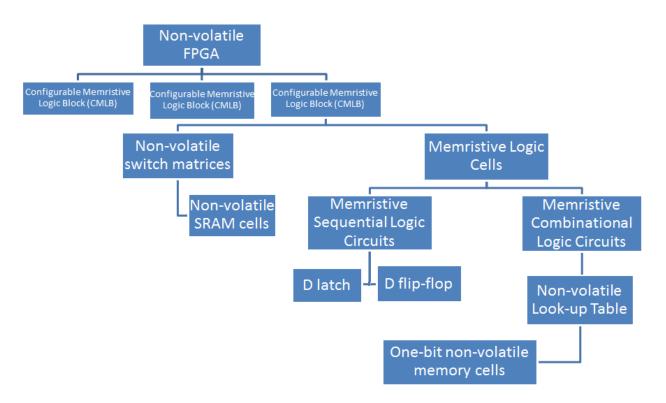

This dissertation reports the research work that was conducted to propose a non-volatile architecture for FPGA using resistive switching devices. This is achieved by designing a Configurable Memristive Logic Block (CMLB). The CMLB comprises of memristive logic cells (MLC) interconnected to each other using memristive switch matrices. In the MLC, novel memristive D flip-flop (MDFF), 6bit non-volatile look-up table (NVLUT), and CMOS-based multiplexers are used. Other than the MDFF, a non-volatile D-latch (NVDL) was also designed. The MDFF and the NVDL are proposed to replace CMOS-based D flip-flops and Dlatches to improve energy consumption. The CMLB shows a reduction of 8.6% of device area and 1.094 times lesser critical path delay against the SRAM-based FPGA architecture. Against similar CMOS-based circuits, the MDFF provides switching speed of 1.08 times faster; the NVLUT reduces power consumption by 6.25nW and improves device area by 128 transistors; while the memristive logic cells reduce overall device area by 60.416µm<sup>2</sup>. The NVLUT is constructed using novel 2TG1M memory cells, which has the fastest switching times of 12.14ns, compared to other similar memristive memory cells. This is due to the usage of transmission gates which improves voltage transfer from input to the memristor. The novel 2TG1M memory cell also has lower energy consumption than the CMOS-based 6T SRAM cell. The memristive-based switch matrices that interconnects the MLCs together comprises of novel 7T1M SRAM cells, which has the lowest energy-delay-areaproduct value of 1.61 among other memristive SRAM cells. Two memristive logic gates (MLG) were also designed (OR and AND), that introduces non-volatility into conventional logic gates. All the above circuits and design simulations were performed on an enhanced SPICE memristor model, which was improved from a previously published memristor model. The previously published memristor model was fault to not be in good agreement with memristor theory and the physical model of memristors. Therefore, the enhanced SPICE memristor model provides a memristor model which is in good agreement with the memristor theory and the physical model of memristors, which is used throughout this research work.

#### **ACKNOWLEDGEMENT**

Thank you to my supervisor Dr. T. Nandha Kumar and co-supervisor Prof. Haider Abbas F. Almurib for giving constant guidance and supervision on the direction of my research.

I would also like to express my gratitude towards my PhD colleagues, Firas O. Hatem and Nemat Al-Hassan for their teamwork and dedication to complete projects together.

My family, loved ones, especially Ming Teng, and my godmother have been the greatest source of determination and motivation to complete this research, as well as friends that have also given their tremendous support.

I would also like to thank God almighty for His blessings upon me for me to complete my PhD.

#### LIST OF PUBLICATIONS

#### List of published works in journals:

- 1. P. W. C. Ho, H. A. F. Almurib, and T. Nandha Kumar, "Configurable Memristive Logic Block for Memristive-based FPGA Architectures" in *INTEGRATION, the VLSI journal*, re-submitted with minor revision.

- 2. P. W. C. Ho, F. O. Hatem, H. A. F. Almurib, and T. N. Kumar, "Comparison between Pt/TiO2/Pt and Pt/TaOX/TaOY/Pt based bipolar resistive switching devices," *IOP Journal of Semiconductors*, vol. 37, no. 6, p. 064001, 2016.

- 3. F. O. Hatem, P. W. C. Ho, H. A. F. Almurib, and T. N. Kumar, "Modeling of Bipolar Resistive Switching of Nonlinear MISM Memristor" in *IOP Semiconductor Science and Technology*, vol. 30, no. 11, pp. 115009, 2015. (journal highlight article)

- 4. P. W. C. Ho, H. A. F. Almurib, and T. Nandha Kumar, "Novel Memristive SRAM with 7 transistors and 1 memristor" in *IOP Journal of Semiconductors*. (article confirmed for publication, volume and issue number not yet assigned)

## List of published works in conferences:

1. P. W. C. Ho, H. A. F. Almurib, and T. Nandha Kumar, "One-bit Non-Volatile Memory Cell Using Memristor and Transmission Gates," in *IEEE International Conference on Electronic Design*, 2014, pp. 244 – 248. (Presented in 2014, Penang, Malaysia)

- 2. P. W. C. Ho, F. O. Hatem, H. A. F. Almurib, and T. N. Kumar, "Comparison on TiO<sub>2</sub> and TaO<sub>2</sub> Based Bipolar Resistive Switching Devices," in *IEEE International Conference on Electronic Design*, 2014, pp. 249 254. (Presented in 2014, Penang, Malaysia)

- P. W. C. Ho, N. H. El-Hassan, T. N. Kumar, and H. A. F. Almurib, "PCM and Memristor Based Nanocrossbars," in *IEEE International Conference on Nanotechnology (NANO 2015)*, 2015, pp. 456 – 459.

(Presented in 2015, Rome, Italy)

- 4. P. W. C. Ho, F. O. Hatem, H. A. F. Almurib, and T. N. Kumar, "Enhanced SPICE Memristor Model with Dynamic Ground," in *IEEE International Circuits and Systems Symposium (ICSyS)*, 2015, pp. 130 132. (Presented in 2015, Langkawi Island, Malaysia)

- P. W. C. Ho, H. A. F. Almurib, and T. Nandha Kumar, "Non-volatile D-latch for sequential logic circuits using memristors" in *IEEE Region 10 Conference*, *TENCON* 2015, 2015, pp. 1 4.

(Presented in 2015, Macau)

#### List of published works submitted to journals for possible publication:

- 1. P. W. C. Ho, H. A. F. Almurib, and T. Nandha Kumar, "Non-volatile look-up table using memristive memory cells" in *IET Circuits, Devices & Systems resubmission after addressing of reviewer comments*.

(Currently awaiting reviewer response)

- 2. P. W. C. Ho, H. K. Hoi, H. A. F. Almurib, and T. Nandha Kumar, "Memristive Logic Gates in Combinational Circuits" *pending submission to journal*.

## TABLE OF CONTENTS

| Cont            | ent        |                                                   | Page number |

|-----------------|------------|---------------------------------------------------|-------------|

| 4.1             |            |                                                   |             |

| Abstr           |            |                                                   | i<br>       |

| Acknowledgement |            | iii                                               |             |

|                 | of publica |                                                   | iv          |

|                 | of conte   |                                                   | vi          |

|                 | of figures |                                                   | xi          |

| List c          | of tables  |                                                   | XV          |

|                 |            |                                                   |             |

| Chap            | oter 1. In | troduction                                        |             |

| 1 1             | D 1        | 1                                                 | 10          |

| 1.1             | Backgro    |                                                   | 18          |

|                 |            | Statement                                         | 20          |

| 1.3             |            | the research                                      | 21          |

| 1.4             | Thesis o   | outline                                           | 23          |

| Chap            | oter 2. Li | terature Review                                   |             |

| 2.1             | Field-pr   | ogrammable Gate Arrays (FPGA)                     | 27          |

| 2.2             | Types of   | f FPGA                                            | 30          |

| 2.3             | Non-vol    | atile memory (NVM) devices                        | 32          |

|                 | 2.3.1      | Phase-Change Memory (PCM) cells                   | 33          |

|                 | 2.3.2      | FeRAM devices                                     | 33          |

|                 | 2.3.3      | MRAM devices                                      | 34          |

| 2.4             | Memrist    | cor                                               | 35          |

|                 | 2.4.1      | Advantages of memristor against other NVM devices | 37          |

|                 | 2.4.2      | Types of memristors                               | 38          |

|      | 2.4.3    | Application of memristors                                            | 39        |

|------|----------|----------------------------------------------------------------------|-----------|

| 2.5  | The dev  | elopment of memristor models                                         | 40        |

| 2.6  | Window   | functions                                                            | 44        |

| 2.7  | Simmon   | s tunnelling current density equation                                | 47        |

| 2.8  | Memrist  | for modelling for MIM devices                                        | 49        |

| 2.9  | Memrist  | for modelling for MISM devices                                       | 51        |

| 2.10 | Develop  | ment of FPGA architectures                                           | 52        |

| 2.11 | Sequent  | ial logic circuits                                                   | 55        |

| 2.12 | Combin   | ational logic circuits                                               | 57        |

| 2.13 | Crossba  | r topology                                                           | 60        |

| 2.14 | General  | device structure of TiO <sub>2</sub> and TaO <sub>2</sub> memristors | 63        |

| 2.15 | Electrof | ormation of NVM devices                                              | 65        |

|      | 2.15.1   | Gibbs free energy of formation                                       | 67        |

|      | 2.15.2   | Dearnaley theory                                                     | 70        |

|      | 2.15.3   | Preventing electroformation in memristive devices                    | 71        |

| 2.16 | Resistiv | e switching mechanism                                                | 72        |

|      | 2.16.1   | Unipolar Resistive Switching (URS)                                   | 72        |

|      | 2.16.2   | Bipolar Resistive Switching (BRS)                                    | 73        |

|      | 2.16.3   | MIM memristive device switching mechanism                            | 75        |

|      | 2.16.4   | MISM memristive device switching mechanism                           | 77        |

|      | 2.16.5   | Comparison between MIM and MISM switching mechanisms                 | <b>79</b> |

| 2.17 | Evaluati | on of TiO <sub>2</sub> and TaO <sub>2</sub> memristive devices       | 80        |

|      | 2.17.1   | Switching speed                                                      | 80        |

|      | 2.17.2   | Switching energy                                                     | 81        |

|      | 2.17.3   | Resistance ratio                                                     | 81        |

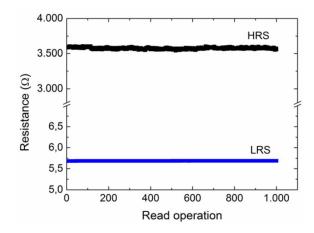

|      | 2.17.4   | Retention                                                            | 84        |

|      | 2.17.5   | Endurance                                                            | 87        |

| 2.18 | Physical | factors of memristive devices                                        | 91        |

|      | 2.18.1   | Thickness of bulk layer                                              | 91        |

|      | 2.18.2   | Device size of memristive devices                                    | 94        |

|      | 2.18.3   | Band gaps                                                            | 95        |

|      | 2.18.4   | Electrode material selection                                         | 95        |

# **Chapter 3. Memristor modelling**

| 3.1 | Batas d   | & Fiedler memristor model                                    | 99  |

|-----|-----------|--------------------------------------------------------------|-----|

|     | 3.1.1     | Fixed ground bidirectional current                           | 99  |

|     | 3.1.2     | Dynamic ground bidirectional current                         | 101 |

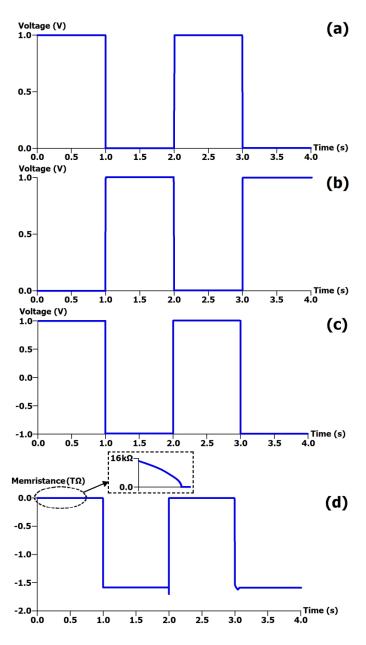

|     | 3.1.3     | Fault in the Batas & Fiedler memristor model                 | 103 |

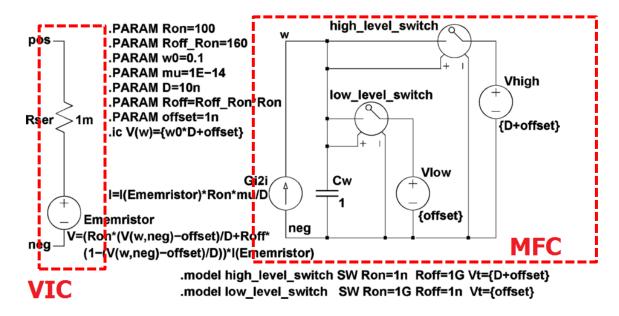

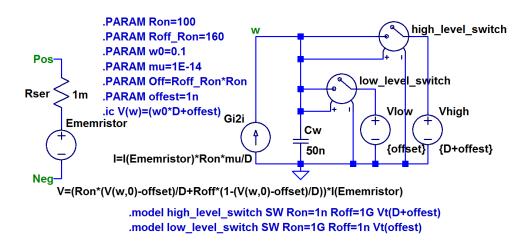

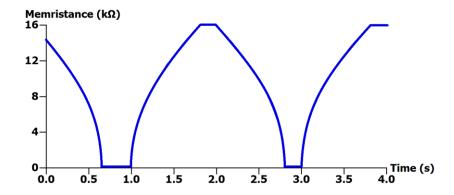

| 3.2 | Enhan     | ced SPICE Memristor Model with Dynamic Ground                | 105 |

| Cha | pter 4. S | Sequential logic circuits                                    |     |

| 4.1 | Non-vo    | olatile memristive D-latch (NVDL)                            | 111 |

|     | 4.1.1     | Latch function of NVDL                                       | 112 |

|     | 4.1.2     | Retention of logic in NVDL                                   | 113 |

|     | 4.1.3     | Resistive switching in NVDL                                  | 113 |

|     | 4.1.4     | Steady-state operation of NVDL                               | 116 |

| 4.2 | Memri     | stive D flip-flop (MDFF)                                     | 117 |

| 4.3 | Simula    | ntion results of memristive sequential logic circuits (MSLC) | 119 |

|     | 4.3.1     | Time measurements                                            | 121 |

|     | 4.3.2     | Energy measurement and non-volatile features                 | 124 |

|     | 4.3.3     | Device area                                                  | 127 |

|     | 4.3.4     | Summary of memristive sequential logic circuits (MSLC)       | 128 |

| Cha | pter 5. ( | Combinational logic circuits                                 |     |

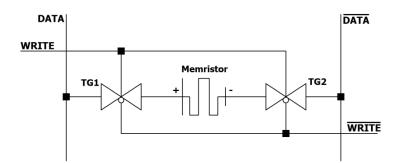

| 5.1 | 2TG1N     | M memory cell                                                | 130 |

|     | 5.1.1     | Write operation of 2TG1M memory cell                         | 132 |

|     | 5.1.2     | Read operation of 2TG1M memory cell                          | 134 |

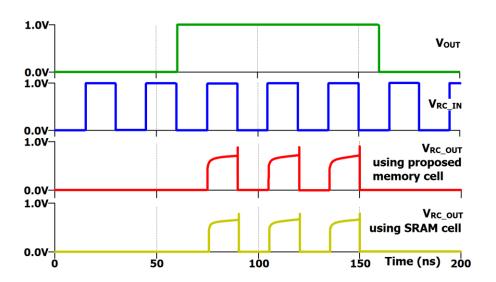

| 5.2 | Simula    | ation results of 2TG1M memory cell                           | 135 |

|     | 5.2.1     | Comparison against one-bit SRAM memory cell                  | 135 |

|     | 5.2.2     | Comparison against 1T1M memory cell                          | 139 |

| 5.3 | Non-ve    | olatile Look-up Table (NVLUT)                                | 142 |

|     | 5.3.1     | Operation of NVLUT                                           | 143 |

|     | 5.3.2     | Application of Boolean algebra into NVLUT                    | 145 |

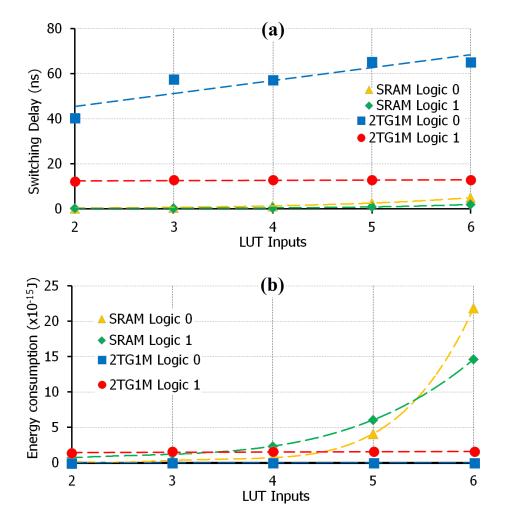

|     | 5.3.3     | Expansion of NVLUT                                           | 147 |

| 5.4 | Anaiys         | sis of NVLU1 using different memristive memory cells     | 148 |

|-----|----------------|----------------------------------------------------------|-----|

|     | 5.4.1          | Switching energy consumption                             | 148 |

|     | 5.4.2          | Device area of NVLUT                                     | 151 |

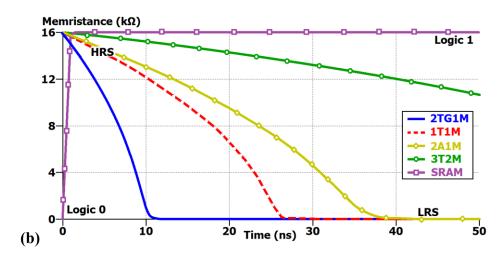

|     | 5.4.3          | Switching speed of memory cells in NVLUT                 | 152 |

|     | 5.4.4          | Energy-Delay-Area product comparison of NVLUTs           | 156 |

| 5.5 | Compa          | arison against SRAM-based LUT                            | 157 |

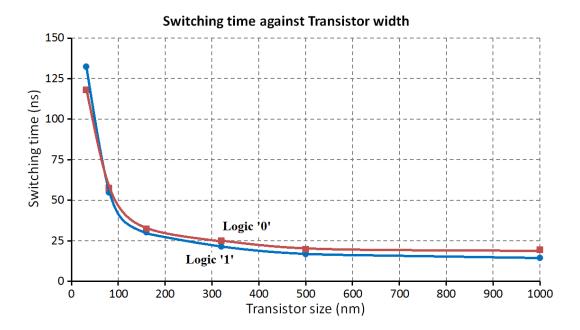

| 5.6 | Switch         | ing time against transistor width                        | 160 |

| 5.7 | Memri          | stive Ratioed Logic (MRL)                                | 161 |

| 5.8 | Memri          | stive Logic Gate (MLG)                                   | 166 |

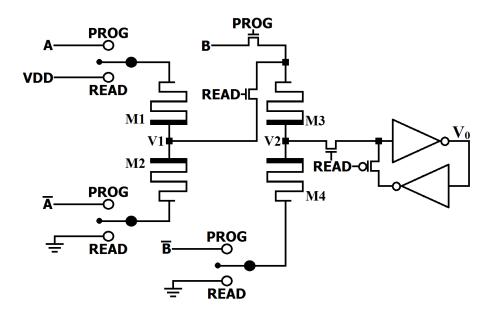

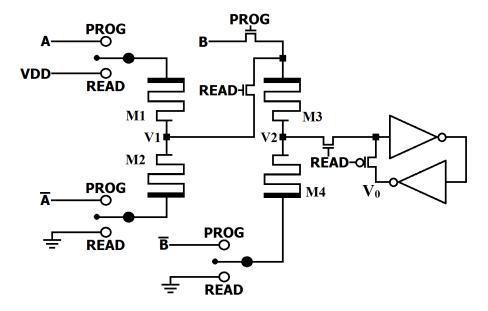

|     | 5.8.1          | Programming mode of MLG                                  | 168 |

|     | 5.8.2          | Reading mode of MLG                                      | 172 |

|     | 5.8.3          | Steady-state mode of MLG                                 | 175 |

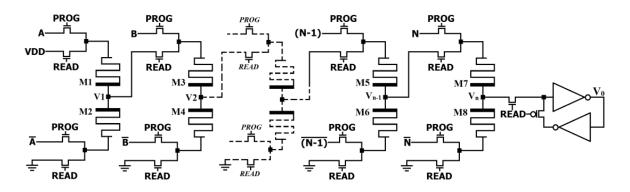

|     | 5.8.4          | Expansion of the 2-bit input MLG                         | 176 |

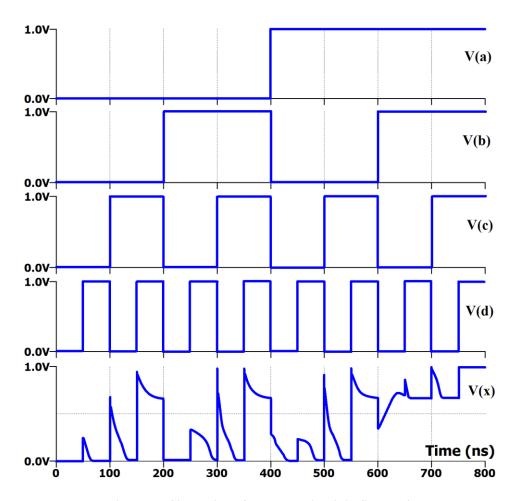

| 5.9 | Simula         | ation results of MLG and MRL combinational circuits      | 179 |

|     | 5.9.1          | Energy consumption of MLG combinational circuit          | 181 |

|     | 5.9.2          | Output delay of MLG combinational circuit                | 182 |

|     | 5.9.3          | Comparison against CMOS combinational circuit            | 183 |

| Cha | pter 6. S      | Switch block                                             |     |

| 6.1 | Switch         | block and switch matrix                                  | 186 |

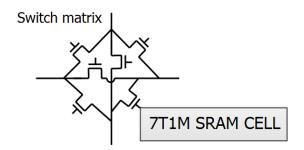

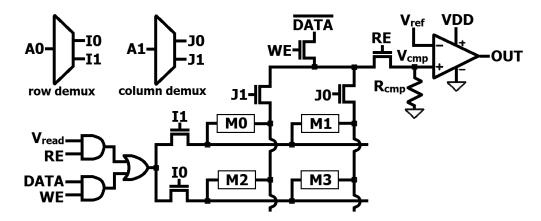

| 6.2 | 7T1M SRAM cell |                                                          |     |

|     | 6.2.1          | Write operation of 7T1M SRAM cell                        | 188 |

|     | 6.2.2          | Read operation of 7T1M SRAM cell                         | 190 |

|     | 6.2.3          | Non-volatile feature of 7T1M SRAM cell                   | 191 |

| 6.3 | Compa          | arison of memristive SRAM cells                          | 194 |

| 6.4 | Applic         | ation of 7T1M SRAM cell in a switch matrix               | 197 |

| Cha | pter 7. I      | Memristive-based FPGA architecture                       |     |

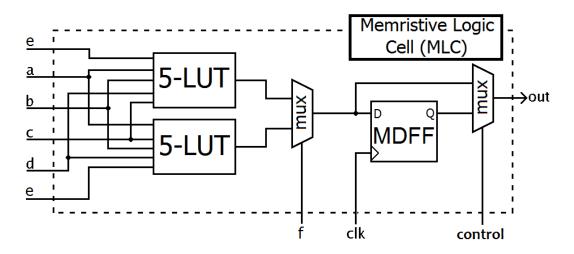

| 7.1 | Memri          | stive Logic Cell (MLC) and Configurable Memristive Logic |     |

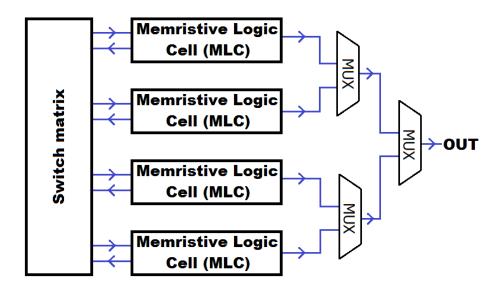

|     | Block          | (CMLB)                                                   | 200 |

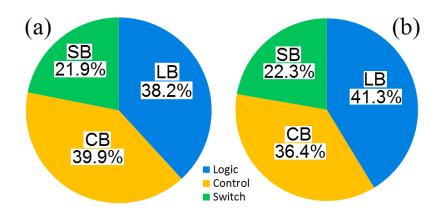

| 7.2 | Evalua         | tion of MLC and CMLB                                     | 202 |

|     | 7.2.1          | Resource utilization of test designs                     | 203 |

|      | 7.2.2     | Power consumption of test designs                       |     | 206  |

|------|-----------|---------------------------------------------------------|-----|------|

|      | 7.2.3     | Critical path delay in logic cell                       |     | 206  |

| 7.3  | Compar    | rison against other memristive-based FPGA architectures | in  | the  |

|      | literatur | e                                                       |     | 208  |

| 7.4  | Memris    | tive and PCM cells crossbar                             |     | 212  |

|      | 7.4.1     | Write operation of the crossbar                         |     | 214  |

|      | 7.4.2     | Read operation of the crossbar                          |     | 216  |

|      | 7.4.3     | Simulation results of memristive and PCM cells crossbar |     | 219  |

|      | 7.4.4     | Delay of memristive and PCM cells crossbar              |     | 222  |

|      | 7.4.5     | Energy consumption of memristive and PCM cells crossbar |     | 223  |

|      | 7.4.6     | Summary of the comparison of memristive and PCM cells   |     |      |

|      |           | Crossbar                                                |     | 224  |

|      | -         | onclusion                                               |     |      |

| 8.1  | Conclus   | sion                                                    |     | 227  |

| 8.2  | Future r  | research                                                |     | 231  |

| Bibl | iography  | ,                                                       |     | 234  |

| App  | endices   |                                                         |     |      |

| A:   | Netlist   | for enhanced SPICE memristor model with dynamic         | gro | ound |

|      | (MEMF     | RISTOR.lib)                                             |     | 255  |

| B:   | Netlist 1 | for Non-volatile D-Latch (NVDL.lib)                     |     | 256  |

| C:   | Netlist 1 | for Memristive D Flip-flop (MDFF.lib)                   |     | 257  |

| D:   | Netlist 1 | for 2TG1M memory cell (2TG1M.lib)                       |     | 258  |

| E:   | Netlist 1 | for Transmission Gate (T_GATE.lib)                      |     | 259  |

| F:   | Netlist 1 | for CMOS inverter (INVERTER.lib)                        |     | 260  |

| G:   | Netlist 1 | for 6-bit Non-Volatile Look-Up Table (NVLUT.lib)        |     | 261  |

| H:   | Netlist 1 | for 7T1M SRAM cell (7T1M.lib)                           |     | 265  |

# LIST OF FIGURES

| Figu | ure no. & title Page r                                                              | umber       |

|------|-------------------------------------------------------------------------------------|-------------|

| Cha  | pter 1. Introduction                                                                |             |

| 1.   | Summary of the aims of research                                                     | 22          |

| Cha  | pter 2. Literature Review                                                           |             |

| 2.   | General FPGA architecture                                                           | 27          |

| 3.   | The relationship between the four fundamental electric quantities                   | 35          |

| 4.   | Barrier width in the bulk layer of MIM memristive devices                           | 41          |

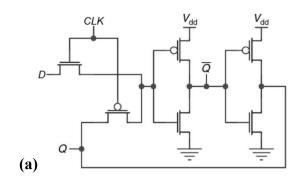

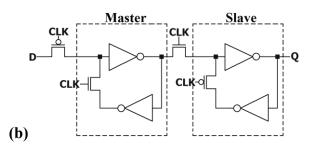

| 5.   | CMOS sequential logic circuits                                                      | 55          |

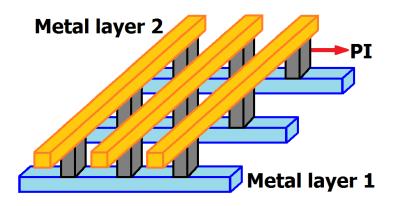

| 6.   | Structure of a crossbar array                                                       | 57          |

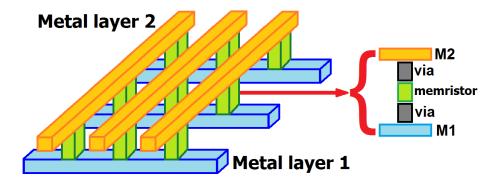

| 7.   | Structure of memristive crossbar                                                    | 61          |

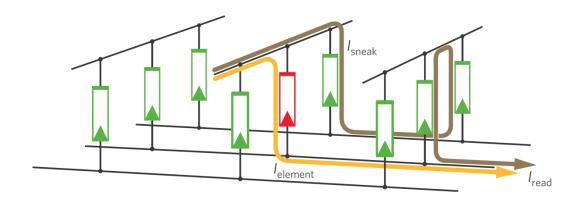

| 8.   | Leakage current issue in crossbar array                                             | 61          |

| 9.   | Typical construction of memristive devices                                          | 63          |

| 10.  | Resistive switching in memristive devices of TaO <sub>2</sub> and Cu <sub>2</sub> O | 68          |

| 11.  | Unipolar Resistance Switching observed in ZrO <sub>2</sub>                          | 72          |

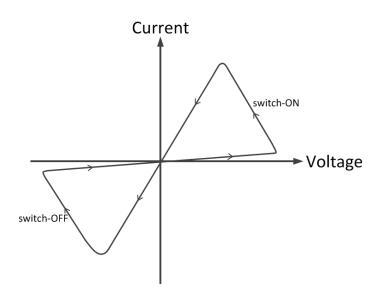

| 12.  | Current-Voltage curve for clockwise bipolar resistance switching                    | 74          |

| 13.  | Current-Voltage curve for counter-clockwise bipolar resistance switchin             | g <b>74</b> |

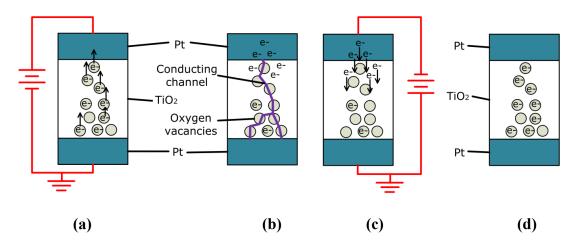

| 14.  | Switching mechanism of TiO <sub>2</sub> devices                                     | 76          |

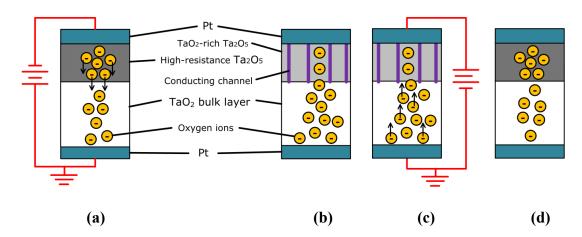

| 15.  | Switching mechanism of TaO <sub>2</sub> devices                                     | 78          |

| 16.  | Resistance switching of memristive devices                                          | 83          |

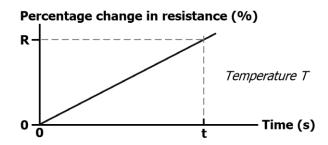

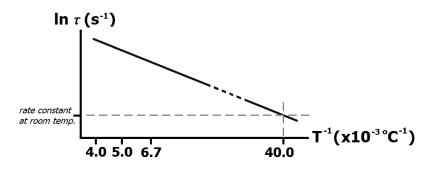

| 17.  | Temperature-accelerated degradation plot                                            | 85          |

| 18.  | Arrhenius plot to find rate constant of at room temperature                         | 86          |

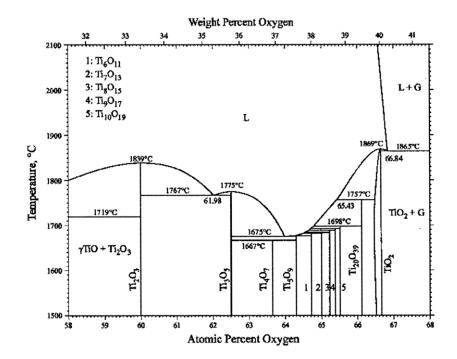

| 19.  | Ti-O phase diagram                                                                  | 89          |

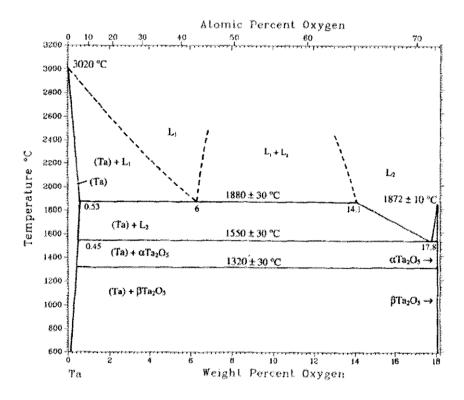

| 20.  | Ta-O phase diagram                                                                  | 89          |

# **Chapter 3. Memristor modelling**

40.

memory cell

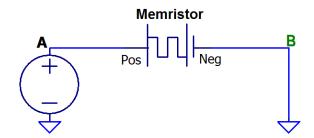

| 21.  | Memristor connected using fixed ground method                         | 100   |

|------|-----------------------------------------------------------------------|-------|

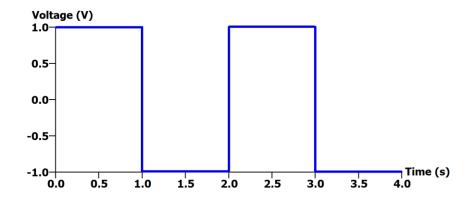

| 22.  | Voltage input at A for the circuit in figure 21                       | 100   |

| 23.  | Memristive behaviour exhibited by the Batas & Fiedler memristor model | using |

|      | fixed ground method                                                   | 100   |

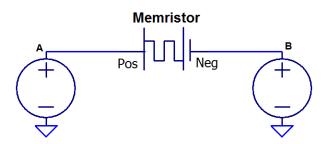

| 24.  | Memristor connected using dynamic ground method                       | 101   |

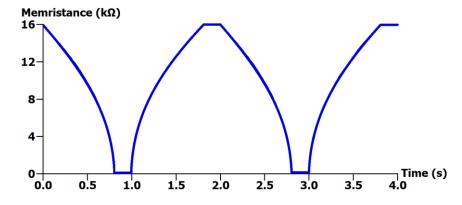

| 25.  | Simulation results of the memristor connected using dynamic g         | round |

|      | method                                                                | 102   |

| 26.  | Batas & Fiedler memristor model                                       | 104   |

| 27.  | Enhanced SPICE memristor model with dynamic ground                    | 106   |

| 28.  | Memristive behaviour exhibited by the proposed memristor model using  | fixed |

|      | and dynamic ground method                                             | 107   |

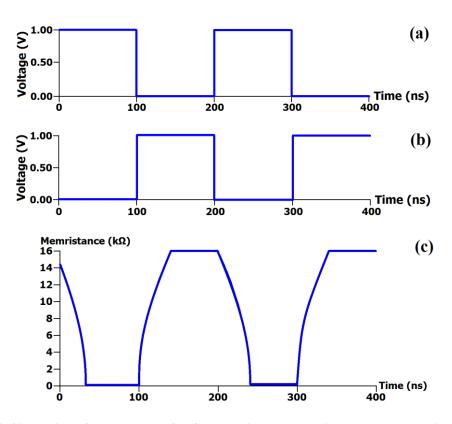

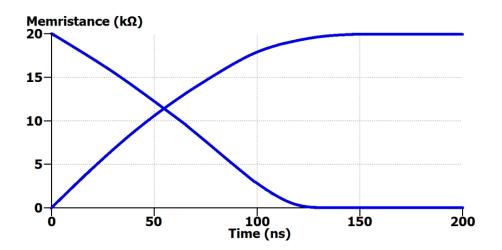

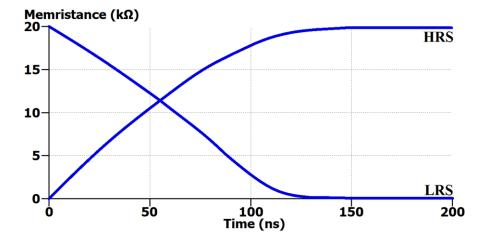

| 29.  | Simulation of the enhanced SPICE memristor model with nanose          | conds |

|      | switching                                                             | 108   |

| •    |                                                                       |       |

| 20   |                                                                       | 111   |

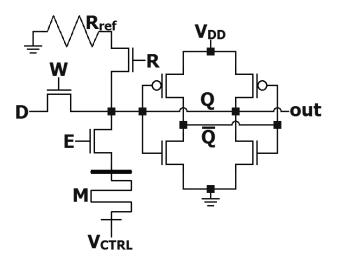

| 30.  | Schematic circuit of the non-volatile memristive D-latch (NVDL)       | 111   |

| 31.  | Equivalent circuit when restoring logic information in the NVDL       | 115   |

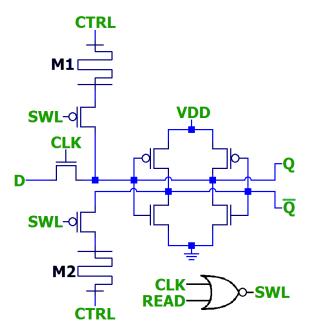

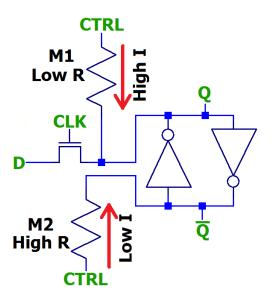

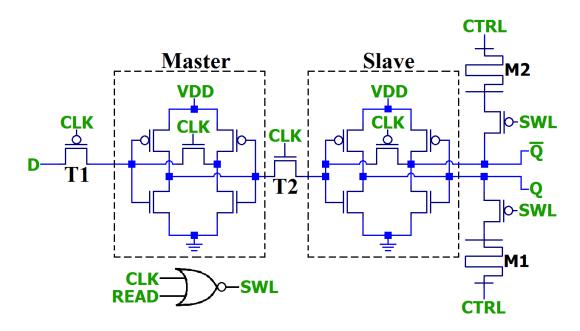

| 32.  | Schematic circuit of the Memristive D Flip-Flop (MDFF)                | 117   |

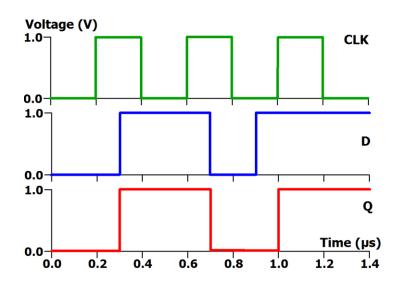

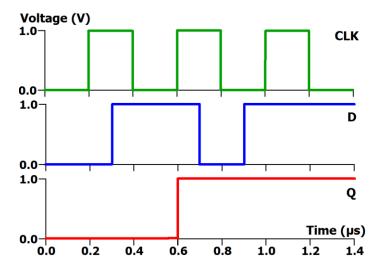

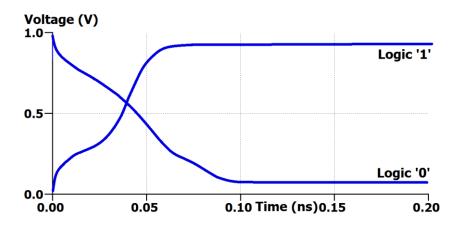

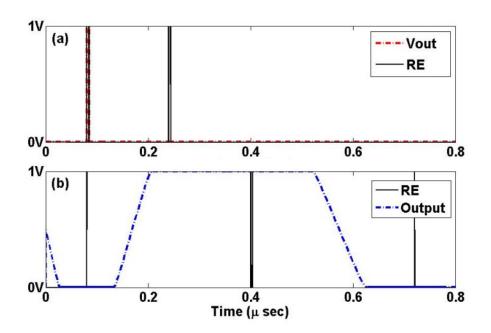

| 33.  | Simulation of the NVDL                                                | 120   |

| 34.  | Simulation of the MDFF                                                | 120   |

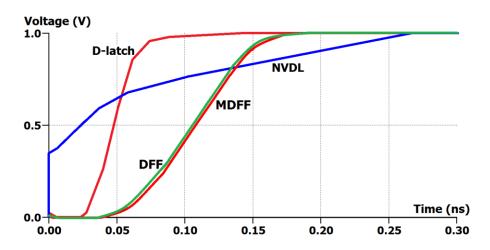

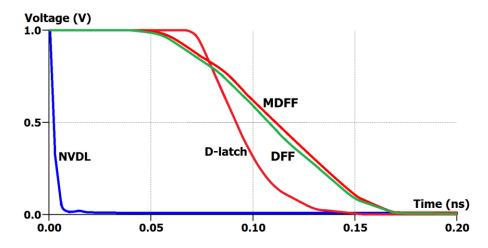

| 35.  | Output '1' delay of sequential logic circuits                         | 122   |

| 36.  | Output '0' delay of sequential logic circuits                         | 122   |

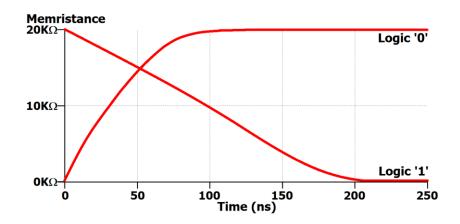

| 37.  | Resistive switching delay in the memristors of NVDL                   | 123   |

| 38.  | Resistive switching delay in the memristors of MDFF                   | 123   |

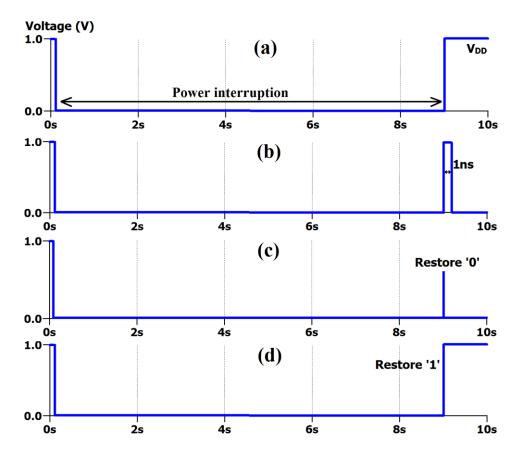

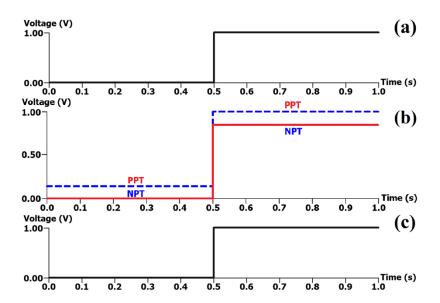

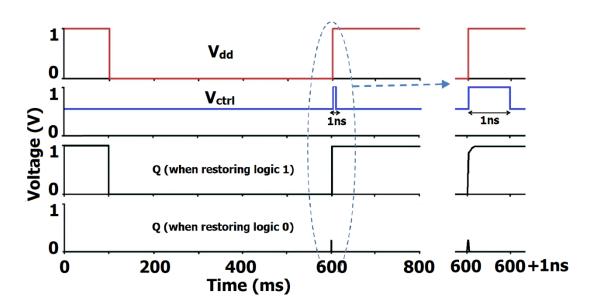

| 39.  | Restoration of logic information in the NVDL and MDFF circuits        | 126   |

|      |                                                                       |       |

| Chaj | pter 5. Combinational logic circuits                                  |       |

Schematic circuit of the two transmission gate one memristor (2TG1M)

130

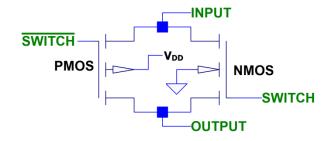

| 41. | Schematic diagram of the CMOS transmission gate                       | 131   |

|-----|-----------------------------------------------------------------------|-------|

| 42. | Simulation of pass transistors and transmission gate                  | 131   |

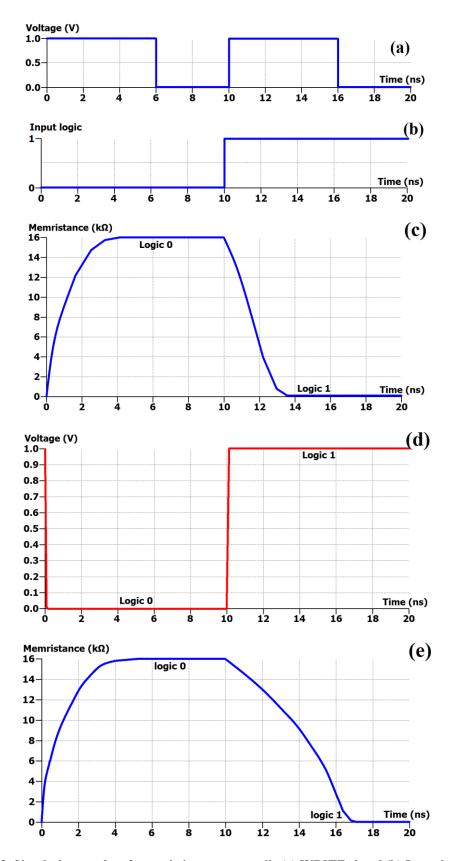

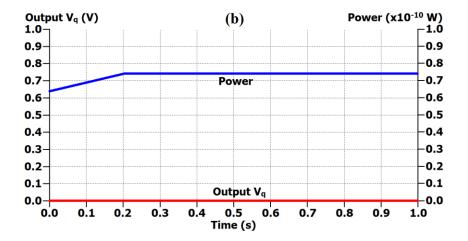

| 43. | Simulation results of memristive memory cells                         | 136   |

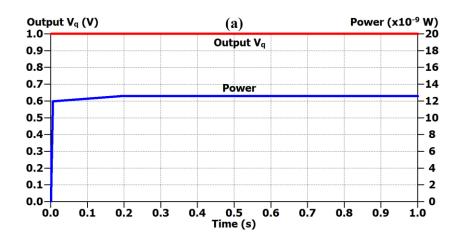

| 44. | Energy dissipation for 1s in a one-bit SRAM memory cell               | 138   |

| 45. | Simulations results of the proposed 2TG1M and the 1T1M memory cells v | vhen  |

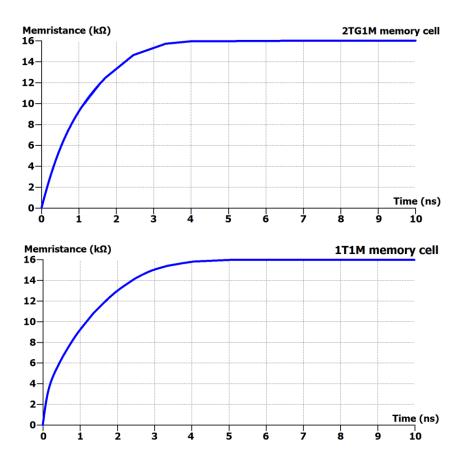

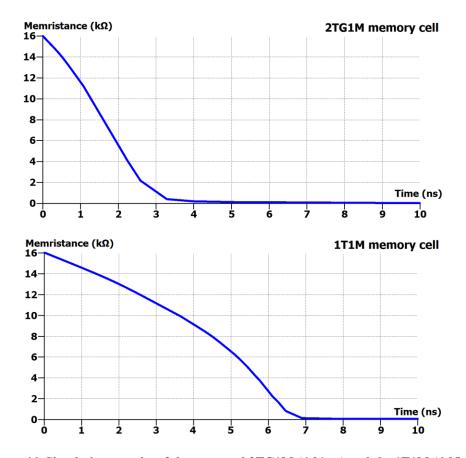

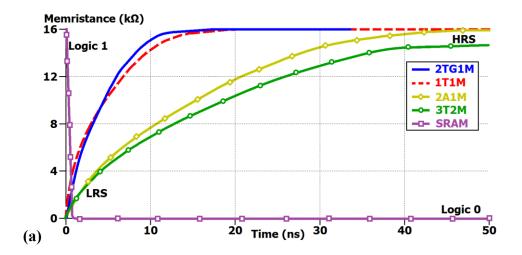

|     | writing logic '1'                                                     | 140   |

| 46. | Simulations results of the proposed 2TG1M and the 1T1M memory cells v | vhen  |

|     | writing logic '0'                                                     | 141   |

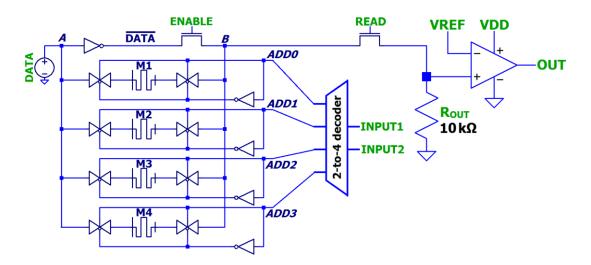

| 47. | 2-bit input NVLUT constructed with four 2TG1M memory cells            | 142   |

| 48. | Simulation of the 2-bit NVLUT of 2TG1M memory cells                   | 144   |

| 49. | n-bit input NVLUT constructed with non-volatile one-bit memory cells  | 147   |

| 50. | Switching delay of NVLUT using different memristive memory cells      | 154   |

| 51. | Switching delay and energy consumption of 6-bit input NVLUT and LUT   | 157   |

| 52. | Switching time against NMOS transistor widths                         | 160   |

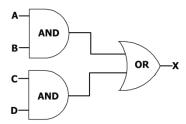

| 53. | Boolean algebra $X = AB + CD$ realized using CMOS logic gates         | 161   |

| 54. | Schematic circuit for the MRL circuit implementing the Boo            | olean |

|     | algebra $X = AB + CD$                                                 | 162   |

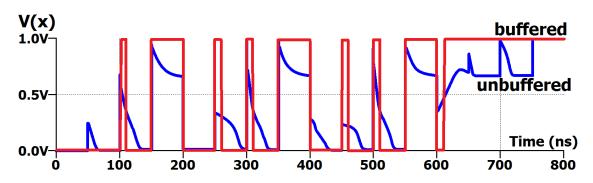

| 55. | Simulation of the MRL circuit in figure 54                            | 163   |

| 56. | Improved MRL circuit by inserting buffers                             | 164   |

| 57. | Simulation of the improved MRL circuit with buffers                   | 164   |

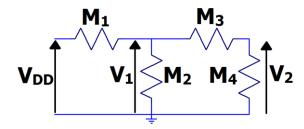

| 58. | Schematic circuit of the OR-MLG                                       | 167   |

| 59. | Schematic circuit of the AND-MLG                                      | 167   |

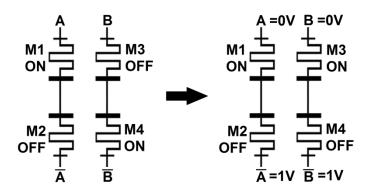

| 60. | An example of a case of programming OR-MLG                            | 168   |

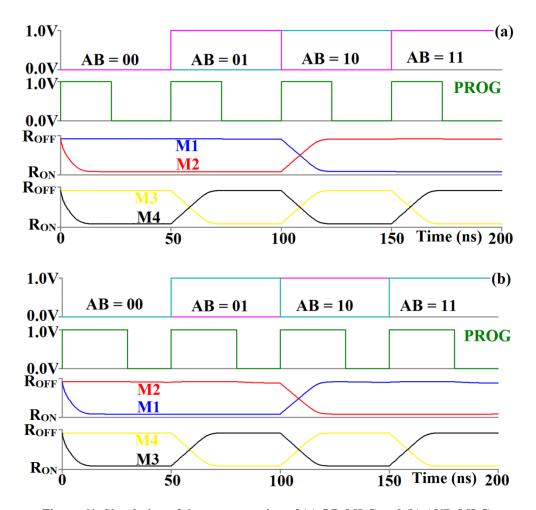

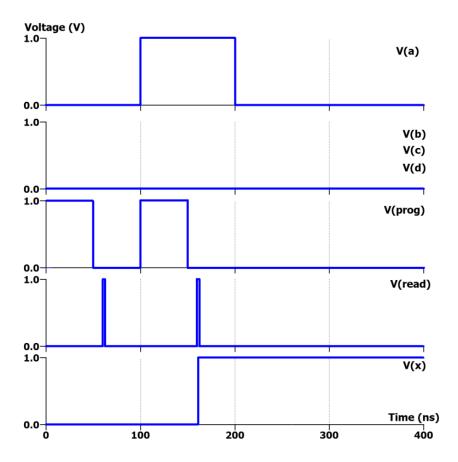

| 61. | Simulation of the programming of OR-MLG and AND-MLG                   | 171   |

| 62. | Equivalent circuit of the MLG during reading mode                     | 173   |

| 63. | Expanded OR-MLG to <i>n</i> -number of inputs                         | 177   |

| 64. | Simulation results of a 4-bit input OR-MLG.                           | 177   |

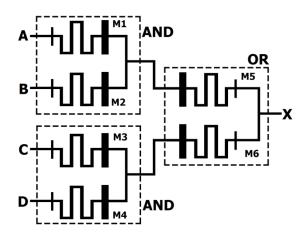

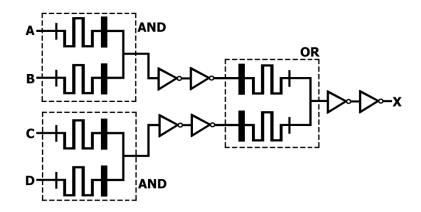

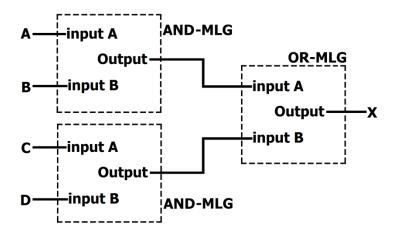

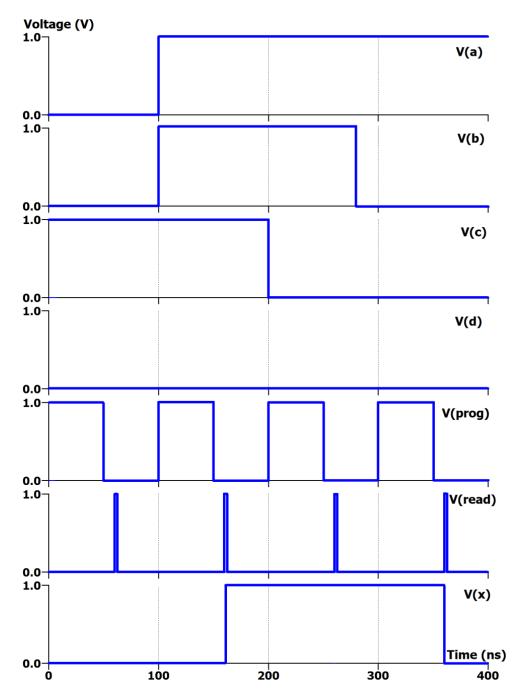

| 65. | Boolean algebra $X = AB + CD$ realized using MLG                      | 179   |

| 66. | Simulation results of the circuit in figure 65                        | 180   |

# **Chapter 6. Switch block**

| 67. | General structure of a switch matrix in a switch block.              | 186       |

|-----|----------------------------------------------------------------------|-----------|

| 68. | Schematic circuit of the 7T1M SRAM cell                              | 187       |

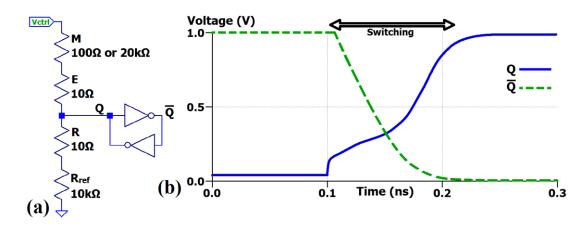

| 69. | Simulation of the write process of the 7T1M SRAM cell                | 189       |

| 70. | Simulation of the read process of the 7T1M SRAM cell                 | 191       |

| 71. | Equivalent circuit of the 7T1M SRAM cell during reading and the si   | mulation  |

|     | of the inverter loop between $Q$ and $\overline{Q}$                  | 192       |

| 72. | Demonstration of the non-volatile properties of the proposed me      | emristive |

|     | SRAM cell                                                            | 193       |

| 73. | Output Q of 7T1M SRAM cell connected to a pass-transistor in         | a switch  |

|     | matrix                                                               | 197       |

| 74. | Switch matrix pass-transistor controlled by the memristive switch r  | natrix o  |

|     | 7T1M SRAM cells and CMOS SRAM-based switch matrix.                   | 197       |

| Cha | pter 7. Memristive-based FPGA architecture                           |           |

| 75. | Memristive logic cell (MLC)                                          | 200       |

| 76. | Block diagram of configurable memristive logic block (CMLB)          | 202       |

| 77. | Resource utilization of the test designs in memristive-based and SRA | M-based   |

|     | FPGA architectures                                                   | 205       |

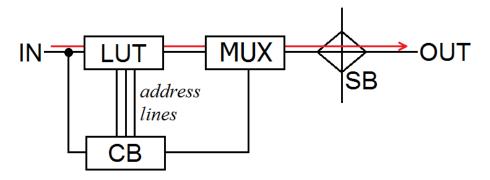

| 78. | Typical critical path through a logic cell                           | 207       |

| 79. | Schematic diagram the crossbar architecture used in this research    | 212       |

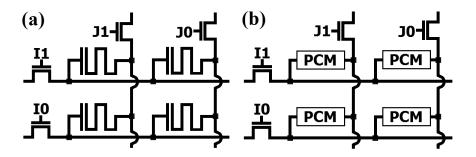

| 80. | Crossbar memory cells replaced memristors and PCM cells              | 214       |

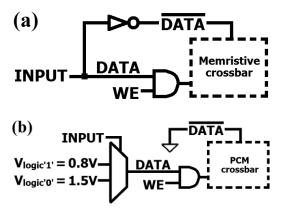

| 81. | Write circuit of memristor crossbar and PCM cells crossbar           | 214       |

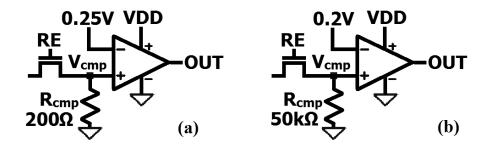

| 82. | Read circuitry for memristive crossbar and PCM cells crossbar        | 216       |

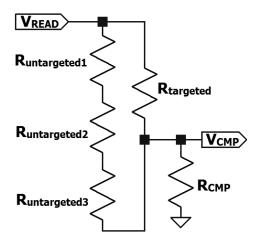

| 83. | Equivalent circuit when reading crossbar                             | 217       |

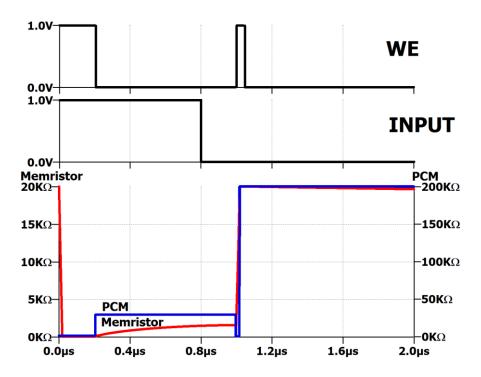

| 84. | Average programming delay of memristive and PCM cells crossbar       | 220       |

| 85. | Average read delay of memristive and PCM cells crossbar              | 221       |

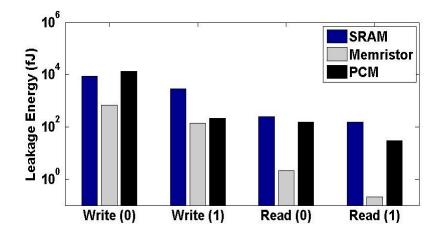

| 86. | Leakage Energy in SRAM, Memristive, and PCM crossbars                | 221       |

# LIST OF TABLES

Table no. & title

| Cha | pter 2. Literature review                                                                    |                  |

|-----|----------------------------------------------------------------------------------------------|------------------|

| 1.  | Proposed window functions for the behaviour of charge carriers approach electrode boundaries | ing<br><b>45</b> |

| 2.  | Gibbs free energy of the formation of metal oxides used in MIM resist                        | tive             |

|     | switching devices                                                                            | 67               |

| Cha | pter 4. Sequential logic circuits                                                            |                  |

| 3.  | Summary of the operation of NVDL 1                                                           | 116              |

| 4.  | Output delays of sequential logic circuits                                                   | 121              |

| Cha | pter 5. Combinational logic circuits                                                         |                  |

| 5.  | Comparison of switching delay and energy costs for writing logic '1'                         | 141              |

| 6.  | Comparison of switching delay and energy costs for writing logic '0'                         | 141              |

| 7.  | An extract of the truth table for $X = (AB + CD) \cdot (E + F)$                              | 146              |

| 8.  | Average energy consumption of memristive memory cells                                        | 149              |

| 9.  | Summary of device area utilized by each unit of the memristive mem-                          | ory              |

|     | cell 1                                                                                       | 152              |

| 10. | Writing time of memristive memory cells                                                      | 153              |

| 11. | Summary of results of energy, delay, and device area, and values of Energy                   | gy-              |

|     | Delay-Area Product for the memristive memory cells                                           | 156              |

| 12. | Writing time and energy requirements of memory cells in a 6-bit input NVL                    | UT               |

|     | of 2TG1M memory cells and LUT of SRAM memory cells                                           | 158              |

Page number

| 14. | Summary of programming of memristors and the output from reading mode for         |        |  |

|-----|-----------------------------------------------------------------------------------|--------|--|

|     | OR-MLG and AND-MLG                                                                | 174    |  |

| Cha | pter 6. Switch block                                                              |        |  |

| 15. | Summary of the memristive SRAM cells and their EDAP value                         | 195    |  |

| Cha | pter 7. Memristive-based FPGA architecture                                        |        |  |

| 16. | Comparison of FPGA architecture performance based on one set of CMLE              | 3 and  |  |

|     | one switch matrix                                                                 | 204    |  |

| 17. | Comparison of memristive FPGA architectures in the literature against SR          | AM-    |  |

|     | based FPGA architecture                                                           | 208    |  |

| 18. | Comparison of device area used by each design in terms of $\mu m^2$               | 209    |  |

| 19. | Comparison of power consumption and critical path delay of each design            | 210    |  |

| 20. | Voltage formed at node V <sub>CMP</sub> for different cases of reading memristive | and    |  |

|     | PCM cells crossbar                                                                | 218    |  |

| 21. | Summary of simulation results performed on crossbar arrays of memr                | istor, |  |

|     | PCM, and SRAM                                                                     | 224    |  |

|     |                                                                                   |        |  |

|     |                                                                                   |        |  |

13. The four typical cases of programming in the MLG

170

# 1. INTRODUCTION

#### INTRODUCTION

#### 1.1 Background

Field-Programmable Gate Arrays (FPGA) has become increasingly popular compared to Application Specific Integrated Circuits (ASIC) due to their configurability, programmability and versatility. With the reduction of gate-length in the CMOS process technology, FPGA chips are smaller in size relative to ASIC chips and the rising cost of ASIC is at a higher rate than that for FPGA chips [1]. Current Static Random Access Memory (SRAM) FPGAs have fast switching speeds but are volatile. Furthermore, SRAM cells require 6 transistors to store one-bit logic. These factors contribute to larger device area and an increased routing path length, which eventually leads to higher power consumption and longer critical path delays. Although FPGAs are fully programmable, all programmed information are only kept temporarily due to the volatility of SRAM cells. Thus, programmed information is lost when power supply to the FPGA is disrupted and hence, requires reprogramming of the FPGA.

The volatility of SRAM cells and the increased demands for density and speed in electronic devices has driven an increase in the amount of research and in the number of electronic applications being proposed for migration to using non-volatile memory devices. Such applications have adopted memristors in their designs [2]–[4], while other applications that uses memristors include memristor oscillators [5], memristor-based chaotic circuits [6] and memristor-based adaptive coupling [7]. By using memristors in these electronic applications, these applications have benefitted from reductions of switching delay, power consumption, and device area. Similarly, FPGA applications would also benefit from adopting memristor-based architectures [8]. Using memristor-based FPGA architectures also allow the programmed information to be retained in the FPGAs even if the power supply is interrupted.

The current FPGA market is dominated by SRAM-based architectures [9]. However the SRAM based FGPA architecture is volatile; hence programmed information will be lost in the event of power interruption causing the design in the FPGA to malfunction. Therefore, to address this issue and improve the performance of the FPGA operation in terms of increasing speed, reducing area and reducing power dissipation, the main objective of the research work presented in this dissertation is to propose a novel non-volatile Configurable Memristive Logic Block (CMLB) that can be used in a non-volatile FPGA architecture.

#### 1.2 Problem statement

Due to the numerous memristor models available in the literature review, a single memristor model has to be selected for use throughout the entire research if a novel memristor model is not designed. The selection of the memristor model from the literature is based on the flexibility of the memristor model which allows researchers to adapt the memristor model to different simulation environments.

In the FPGA, there are many CMOS-based memory cells and circuits which are volatile. The objective of this research is to produce a non-volatile FPGA architecture which is based on non-volatile memory cells and circuits. Therefore, novel non-volatile memory cells and circuits are to be designed using memristors. Comparison of these designed non-volatile memory cells and circuits are then compared against similar works in the literature review for verification and justification of selection to be used in the non-volatile FPGA. The following section explains novel memory cells and circuits that must be designed to produce the non-volatile FPGA architecture, as well as the summary of the aims of this research.

#### 1.3 Aims of the research

To achieve the objective of designing a non-volatile FPGA architecture using resistive switching devices, the aim of the research works is to produce a non-volatile configurable logic block. Configurable logic blocks contain various types of electronic and electrical components. For the configurable non-volatile configurable logic block to be novel, the following categories of circuits must also be designed in novelty:

- (i) non-volatile memory cell

- (ii) non-volatile combinational logic circuit

- (iii) non-volatile sequential logic circuit

To produce the above circuits, a single simulation model needs to be identified to be used throughout this research. This is performed by conducting a literature review on the existing SPICE models of resistive switching devices. The SPICE model that is used in this research is obtained by developing an enhanced SPICE memristor model, which was adopted and improved from one of the SPICE models available in the literature. This SPICE model was then used throughout this research to simulate every circuit that are presented in this dissertation, including the simulation of the circuits from the literature and other sources, to ensure simulations are performed on a similar simulation environment and that the results are unbiased.

All the experiments presented in this dissertation are all conducted in SPICE simulation environment. All circuit designs and experiments presented in this dissertation are performed on the LTspice 4.2 software, which is the latest version of the LTspice at the time of the start of this research work. The 32nm transistor gatelength process technology SPICE model is adopted from Predictive Technology Model [10], hence V<sub>DD</sub> in all simulations are set to 1.0V based on the transistor technology. The aims of this research are summarized in figure 1, where each block in the diagram is a circuit that needs to be designed using the same memristor model and simulation parameters as described.

Figure 1. Summary of the aims of research.

#### 1.4 Thesis outline

The literature review to the research work presented in this dissertation is described in chapter 2. The preliminaries include the types of FPGA architectures available in the literature and an overview of the CMOS-based FPGA architecture. The preliminaries also include the different types of non-volatile memory devices, and a brief background on the development of memristors. This chapter also explains the development of memristor modelling and SPICE memristor models. How previous researches have tried to improve on the FPGA architecture by using non-volatile memory devices are explained in this chapter. Further literature review is conducted on memristive sequential and combinational logic circuit, as well as previously proposed improvements on switch matrices. The research work that was conducted to provide a detailed comparison between TiO<sub>2</sub> and TaO<sub>2</sub> memristive devices is presented in this chapter also. This chapter concludes by explaining the electrical and physical factors that differentiate memristors.

Chapter 3 presents an enhanced SPICE memristor model is presented that is based on a previous SPICE memristor model that was found to be working differently from the theories of the memristor.

Chapter 4 presents two types of memristive sequential logic circuits, D-latch and D flip-flop, as well as their simulation results and analysis. Other memristive sequential logic circuits from the literature are also analysed and compared against the memristive sequential logic circuits.

In chapter 5, the research findings on combinational logic circuits are divided into two sections. The first section shows the construction of a non-volatile look-up table using a novel one-bit non-volatile memory cell that was designed using memristors and transmission gates. The memory cell was compared against other similar memory cells available in the literature. In the second section of chapter 5, two novel memristive logic gates are proposed (OR and AND). The analysis and simulation results are presented in this chapter. Additionally, a method to improve a previously published memristive logic circuit in the literature is also discussed and explained.

Chapter 6 introduces and discusses the general switch blocks and crossbar arrays. The arrangement of memristors in a crossbar array is also discussed in this chapter. A research was conducted to compare and analyse crossbars of memristor and phase-change memory cells. Upon these results, a memristive memory cell is designed to create a memristive switch matrix, which is presented in this chapter. Simulation experiments were conducted on this switch matrix memristive memory cell along with other similar memory cells found in the literature.

Subsequently, chapter 7 introduces the configurable memristive logic block (CMLB) that encapsulates all the research work presented in the previous chapters. The CMLB is a network of memristive logic cells (MLC), interconnected to each other using memristive switch matrices. The MLC comprises of the non-volatile look-up table and the memristive D flip-flop. The CMLB is then proposed to be used in a memristive-based FPGA architecture. This chapter also presents the simulation results and analysis of the MLC and CMLB using various FPGA test designs.

Chapter 8 provides the conclusion to this dissertation and the researches that has been conducted and presented. This chapter also discusses all the possible future researches that stems from this dissertation.

2. LITERATURE REVIEW

#### LITERATURE REVIEW

## 2.1 Field-programmable Gate Arrays (FPGA)

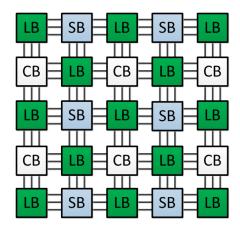

Field-programmable Gate Arrays (FPGA) are integrated circuits containing various types of resource blocks that are programmable and configurable to any manner desired by the programmer. Examples of resources that are built in FPGAs are built-in memory, clock generators, I/O interfaces, multipliers, arithmetic units, Digital Signal Processor (DSP), and logic blocks. Hardware description language (HDL) is used to program these resources to however a user wishes it to behave. The common SRAM-based FPGA architecture (figure 2) consists of logic blocks (LB) and control blocks (CB) interconnected to one another by switch blocks (SB).

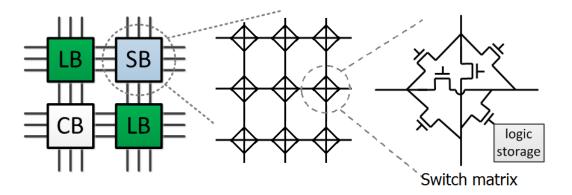

Figure 2. General FPGA architecture where logic blocks (LB) are interconnected with control blocks (CB) and switch blocks (SB).

Switch blocks contain switch matrices, where each switch matrix is a network of routing channels interconnected to one another via pass-transistors. Switch matrices complete the connections between blocks in an FPGA.

Logic blocks are the basic building block for memory storages in an FPGA. They are meant to provide an avenue for users to program logical functions, utilize built-in functions and modules, such as memory blocks, counters, and registers; or perform arithmetic functions. LBs can also be programmed to function as combinational logic circuits or sequential logic circuits in synchronous or asynchronous manner. Programmable logic blocks are also known as configurable logic blocks (CLB) whereas non-programmable logic blocks are called hard-wired logic blocks.

LBs are usually constructed from several logic cells (also known as configurable logic blocks (CLB), slice, or adaptive logic modules (ALM)), interconnected by programmable switch matrices, multiplexers and other logic components [11]. Multiple logic cells can be connected to each other to execute complexed logic functions. Each logic cell generally consists of look-up tables (LUT), multiplexers, full-adders, and D flip-flops. Logic cells are also called as Configurable Logic Blocks (CLB) [12], slice [13], Logic Elements [14] or Adaptive Logic Modules (ALM) [15], depending on the FPGA manufacturer.

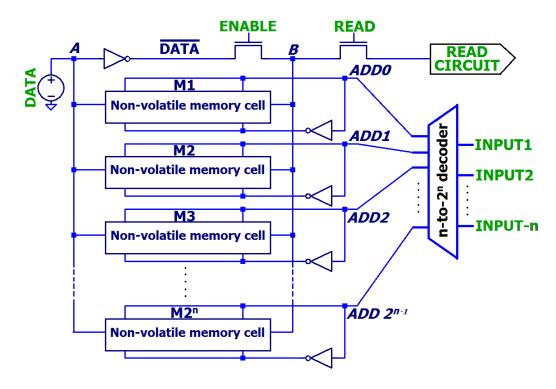

In general, an LUT consists of memory cells which are addressed by the LUT inputs. A decoder is used to decode the LUT inputs to select and enable specific memory cells for programming or reading, and the output of the LUT is the logic

information stored in the accessed memory cell. The LUT functions as a programmable combinational logic circuit, where the LUT address inputs are analogous to the combinational logic circuit input, while the output of the combinational logic circuit is the logic information stored in the memory cell with the address that corresponds to the LUT input. Thus, LUTs are usually used to execute complex Boolean algebra functions.

Control blocks govern the operating functions of logic blocks and switch blocks. To perform this, CBs contain memory elements to store user-programmed information and use sequential logic circuits to channel appropriate control signals. These control signals configure the operation of the pass-transistors in the switch matrices and the functions of the LBs by enabling or disabling transistors, switches, multiplexers, and memory cells in the LBs and SBs. There are various types of control blocks in an FPGA to control different sections or resources of the FPGA. Some examples are clock control block [16], memory controller block [17], communication or Transceiver Reconfiguration Controller [18], and I/O control block [19], [20].

FPGAs are mainly used when designing or testing integrated circuits (IC) and electronic applications because FPGAs are easily programmable which gives short programming and testing times. This shortens debugging and verification processes. Conversely, Application Specific Integrated Circuits (ASIC) are non-programmable and does not allow flexibility in its applications. ASICs also take a longer time from designing stage to fabrication, and are expensive for low volume production.

The major concern for FPGAs is the high cost per chip and large device area required to manufacture a programmable integrated circuit. Furthermore, the amount of power consumption is higher in FPGAs than ASICs due to the various resources built into an FPGA chip to accommodate its programmable functionality. However, due to the emergence of 20nm and 16nm process technologies, FPGA devices are becoming smaller [21]–[23]. Moreover, various articles have also shown that the decreasing costs of FPGA could also lead to the possibility of FPGA replacing ASIC for medium to high volume production in the near future [1], [24], [25].

#### 2.2 Types of FPGA

FPGAs are manufactured by semiconductor companies such as Altera (now Intel), Xilinx, Lattice Semiconductor, Microsemi, and QuickLogic. These manufacturing companies can be divided based on the switching technology used in the FPGA: Static Random-Access Memory (SRAM), antifuse or flash.

Out of the three types of switching technology, antifuse FPGAs have the densest structure but are not re-programmable [26]. Between SRAM and flash, where both are re-programmable, SRAM switching is faster than flash devices. However, flash switching technology consumes lower power consumption and has higher security. Moreover, flash devices are non-volatile, which enables logic information to be retained even after power is disconnected from the device. On the

other hand, SRAM-based FPGAs are usually manufactured with the same type of Complementary Metal—Oxide—Semiconductor (CMOS) technology with the rest of the integrated circuit chip, thus additional manufacturing processes are not required and the cost of fabricating SRAM-based FPGAs is reduced. This is the main reason for SRAM-based FPGAs dominating the FPGA market [9]. Therefore, the SRAM-based FPGA has been selected as the benchmark for comparison in this research work.

One of the disadvantages of SRAM-based FPGAs is the large SRAM devices which reduces the density of FPGA chips, compared to antifuse and flash devices [26]. Although SRAM devices are highly re-programmable, SRAM devices are volatile and lose logic information whenever power supply to the device is disrupted. Despite these disadvantages, SRAM-based FPGAs are widely used in various fields and are also reported to be used for security-related applications [27]. Due to the high demand for SRAM-based FPGAs, researchers have proposed several methods to improve or reduce the disadvantages of SRAM-based FPGAs [28]–[30].

A study was conducted on various architectures of SRAM cells used in FPGAs [28]. The purpose of the study was to propose a 9T SRAM cell with high data stability and low power consumption, but suffers from large device area and volatility. A novel FPGA architecture that uses controllable-polarity transistors was designed [29], which forms the basic building blocks of ultrafine grain cells. These ultrafine grain cells function as computational or logic cells and offers an improvement on the routing imbalance in traditional FPGA architecture [31], as well as reductions in delay and device area. Evolvable processing array-based FPGA

architecture constructed using Dynamic Partial Reconfiguration (DPR) was proposed [30]. This architecture applies evolvable processing array which features protection mechanism against permanent and transient faults, and improve processing quality.

Although these methods to improve SRAM-based FPGA show reliable results, they still use CMOS process technologies and researchers were motivated in breaking away from conventional CMOS devices. This give birth to resistive switching devices and subsequently, FPGA architectures have been proposed and designed using resistive switching devices, or non-volatile memory (NVM) devices, such phase-change memory cells [32], spintronic devices [33], and magnetoresistive memories [34].

## 2.3 Non-volatile memory (NVM) devices

Resistive switching devices or non-volatile memory (NVM) devices became a sought-after technology due to its relatively faster switching speed, higher endurance cycles, and smaller device area per component [35]. Researchers have also managed to fabricate flexible NVM devices [36]–[38]. Most of all, NVM devices are becoming increasingly popular due to their non-volatility properties, as well as multi-level storage capabilities [39]–[41]. NVM devices are also known as resistive switching devices because NVM devices use different resistance levels to indicate different logic information. The common context is to assign logic '0' to the high

resistance state (HRS) and logic '1' to the low resistance state (LRS) of the NVM device. So far, the non-volatile memories that have been developed are:

- (i) Phase-Change Memory (PCM) [42]

- (ii) Ferroelectric Random-Access Memory (FeRAM) [43]

- (iii) magnetoresistive memory (MRAM) [44]

- (iv) Memristors

## 2.3.1 Phase-Change Memory (PCM) cells

PCM cells switch between resistance states by manipulating the phase of chalcogenide materials. Amorphous state of the chalcogenide material is highly-resistive (logic '0'), while crystalline state is of lower resistance (logic '1'). The phase change is attained by heating or cooling. Rapid cooling of chalcogenide causes the material to turn into amorphous state (HRS), while heating it below its melting point causes the chalcogenide to crystallize (LRS) [45]. The rate of cooling or heating is controlled by manipulating magnitude of input current and pulse width.

#### 2.3.2 FeRAM devices

FeRAM devices use ferroelectric materials where an application of electric field across the device causes polarization in the form of small shifts in the atomic

dipoles. The atomic dipoles have the tendency to align themselves according to the electric field. Thus, the change in the distribution of electric charges in the ferroelectric material causes a change in resistance. The polarization would remain after electric field is removed and ferroelectric materials usually have only two stable polarized states, resulting in two different resistance states [46].

#### 2.3.3 MRAM devices

In MRAM devices, the switching of resistance states in the material is induced by an application of magnetic fields. The device structure contains two magnetized layers sandwiched between two metal electrodes. One of it is a fixed magnetized layer, while another is a freely polarizable magnetized layer. The resistance state of MRAM devices are manipulated by controlling the magnetic orientation of the free layer using magnetic fields. Thus, the resistance of the MRAM devices is dependent on the polarization of the free layer in comparison to the polarization of the fixed layer [44]. If the polarization of the layers is parallel to each other, the device is in low resistance (LRS), and if they are not parallel, the device is in high resistance (HRS).

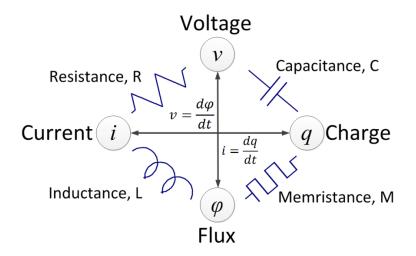

#### 2.4 Memristor

The memristor was first theorized in 1971 by Prof. Leon Chua [47]. The four electrical quantities that relate the three fundamental passive circuit elements are voltage (V), current (I), charge (q) and flux ( $\varphi$ ). Voltage is the rate of change of flux, while current is the rate of charge flow. Resistance is related by voltage and current, capacitance is related by voltage and charge, and inductance is related by current and flux. The only remaining relationship is between charge and flux. Thus, the fourth passive circuit element, known as memristor, was proposed to complete the network of relationships between the four fundamental electrical quantities (figure 3).

Figure 3. The relationship between the four fundamental electric quantities.

In 2002, a physical non-volatile memory device was developed by manipulating the resistance of bulk layer of the device, called as Resistive Random-Access Memory (ReRAM) using colossal magnetoresistance (CMR) materials [48].

CMR materials are usually manganite perovskites and the electrical resistance is manipulated using magnetic fields [49]. The ReRAM device has a two-terminal device with a bulk layer sandwiched between two metal electrodes. A bias potential is applied across the terminals which alters the physical composition of the bulk layer. The physical changes that occur cause a change in the resistance of the bulk layer and of the device. When no potential bias is applied, the bulk layer does not alter its physical composition due to the lack of energy required for physical changes to occur, thus leaving the device in its latest resistance state. This is the non-volatile characteristics of the ReRAM device. With the development of the CMR-ReRAM device, researchers have found a more convenient way to manipulate resistance by using electrical fields instead of magnetic fields [50].

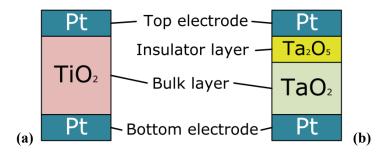

In 2005, TiO<sub>2</sub> thin films were grown by atomic-layer deposition using platinum (Pt) as top and bottom electrodes, and titanium oxide (TiO<sub>2</sub>) as bulk layer [51]. The electrodes are metals, which are conductive while the bulk layer of TiO<sub>2</sub> is highly resistive that makes it similar to an insulator layer. This structure mimics a Metal-Insulator-Metal (MIM) structure and the behaviour of this device is in good agreement with the memristor theory [47]. Around the same time, copper oxide (CuO<sub>2</sub>) was used as the bulk layer to fabricate a device with MIM structure that also exhibits similar resistive switching behaviour [52]. This shows that MIM structures in general are able to exhibit resistance switching abilities. The resistance states of memristors (LRS and HRS) are also commonly known as memristance.

Since then, researchers have shown that other metal oxides could also be used as the bulk material to fabricate nanoscale memristive devices, such as zinc oxide (ZnO) [53], zirconium oxide (ZrO<sub>2</sub>) [54], nickel oxide (NiO) [55], hafnium oxide (HfO) [56], niobium oxide (Nb<sub>2</sub>O<sub>5</sub>) [57], and vanadium oxide (VO<sub>2</sub>) [58], tantalum oxide (TaO<sub>2</sub>) [59], zinc tin oxide [60], bismuth ferrite (BiFeO<sub>3</sub>) [61], and aluminium oxide (Al<sub>2</sub>O<sub>3</sub>) [62]. Resistive switching behaviour was also observed when semimetal oxides are used as the bulk layer (silicon oxide (SiO<sub>2</sub>) [63]). Some chalcogenides have also exhibited memristive properties such as germanium selenide (Ge<sub>2</sub>Se<sub>3</sub>) [64] and copper sulphide (Cu<sub>2</sub>S) [65]. ReRAM and resistance-switching devices are also commonly coined as memristors [66] because the physical structure of MIM devices are similar to ReRAM devices. Moreover, functional behaviour of the ReRAM devices are in good agreement with a memristor [67]. Some authors may also abbreviate ReRAM as RRAM [68]–[70].

### 2.4.1 Advantages of memristor against other NVM devices

The introduction of RRAM devices (or memristors) has significantly attracted more attention than PCM devices because RRAM devices have better switching speeds than PCM. The writing time of RRAM devices is less than 20ns, while PCM devices require at least 100ns for writing time [53], [71]. PCM devices also use large amounts of heat energy during switching which significantly degrades endurance performances [71].

In comparison to MRAM devices, the physical structure of MRAM is larger than a typical RRAM device, where RRAM devices can be fabricated in a nano crossbar array structure [72]. The read time of FeRAM devices (100 ns) is much slower than Dynamic Random-Access Memory (DRAM) devices (40 to 70 ns) [43], which is a common memory device used in computers. It is also reported that are interface issues between Si and the ferroelectric material when fabricating FeRAM devices with current CMOS process technologies [73].

Between PCM, MRAM, FeRAM and memristors, memristors requires the least manufacturing steps to fabricate [74]. In addition, memristors are developed with simple fabrication processes and has high-density structure [75], as well as high compatibility with current CMOS process technologies [50]. Therefore, there are more research and developments in RRAM devices (memristors) than PCM, MRAM and FeRAM devices.

### 2.4.2 Types of memristors

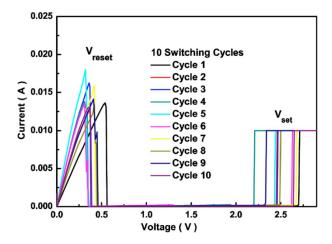

Among the memristive devices that have been developed, TaO<sub>2</sub> is considered as one of the prospective resistive switching material due to its existence in only two stable phases (TaO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>) [76] which gives better control over the stability of the high and low resistance states. The TaO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> layers in the TaO<sub>2</sub> memristor give rise to a Metal-Insulator-Semiconductor-Metal (MISM) structure. In addition, the fabricated TaO<sub>2</sub> memristors have exhibited better resistance switching

characteristics than TiO<sub>2</sub> memristors, in terms of switching speed (5 times faster), endurance (10<sup>8</sup> times more switching cycles) [77], and retention of at least 10 years backed by experimental results [78]. Due to these statistics, a detailed comparison between fabricated TaO<sub>2</sub> and TiO<sub>2</sub> memristive devices was conducted as part of this research to understand the requirements and factors to fabricate better performing memristive devices. TiO<sub>2</sub> memristors are selected as the benchmark for this comparison because the study and fabrication of TiO<sub>2</sub> memristors has been the most extensive among the different types of memristors available in the literature. The detailed comparison between TiO<sub>2</sub> and TaO<sub>2</sub> memristors is further discussed in sections 2.14 to 2.18 of this dissertation [79][80].

# 2.4.3 Applications of memristors

The objectives of using memristors in circuits are either to: (i) improve electrical and physical performance or (ii) introduce non-volatile function. To introduce non-volatile functions, the pioneer applications of memristors were proposals to replace flash memory [81] and DRAM to improve memory performance [82]. Subsequently, memristors are then used to improve electrical and electronic circuits, such as memory cells [83], filters [3] and amplifiers [84], by reducing device area. Other applications of memristors that were found in the literature include neuromorphic circuits [4], Van der Pol Oscillator [85], pH sensors [2], and crossbar arrays [86], which are commonly used in FPGA architectures. These

applications take advantage of the resistance switching behaviour of memristors to improve overall switching speed and energy.

### 2.5 The development of memristor models

Although there were heavy developments on RRAM devices, none have managed to relate it to the memristor that was proposed by Prof. Chua [47]. After many years since Prof. Chua's proposal of the memristor, the breakthrough came in 2005 where resistive switching mechanism was exhibited in TiO<sub>2</sub> thin films [51]. The article however did not directly relate the switching mechanism of the TiO<sub>2</sub> thin films to memristive behaviour. In 2008, a nano-crossbar array with MIM structure that shows similar behaviour to memristors was proposed and fabricated using TiO<sub>2</sub> as the bulk layer [87]. The hysteresis loop in the current-voltage curve and a current-voltage relationship that characterizes the current-voltage behaviour of memristor was subsequently presented [88]. A physical model based on the doping of TiO<sub>2</sub> in the bulk layer was also proposed for the basis of resistive switching mechanism.

According to the physical model proposed in [88], oxygen vacancies act as n-type dopant in TiO<sub>2</sub>. Doping of TiO<sub>2</sub> with oxygen vacancies would cause the highly resistive TiO<sub>2</sub> layer to become less resistive. The asymmetric distribution of oxygen vacancies during doping process causes the TiO<sub>2</sub> layer to have regions of different resistances. The highly-doped region is less resistive, while the lowly-doped region

is more resistive. The drifting of oxygen vacancies from the region of highly-doped TiO<sub>2</sub> towards the oxygen-deficient region causes the overall resistance of TiO<sub>2</sub> to decrease [89], [90].

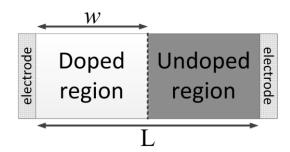

Figure 4. Barrier width in the bulk layer of MIM memristive devices.

Using the above explanation, the physical model presented in [88] have assumed that the bulk layer is divided into two regions of high and low resistance. This is illustrated in figure 4, where w represents the thickness of low resistance doped region of the bulk layer (also known as barrier width) and L is the total length of the bulk layer. The barrier width is modelled to sweep along the bulk length when voltage is applied, ranging from 0 to L. The drifting of oxygen vacancies and movement of barrier width along the bulk length are proposed to be linearly [88], and the rate of change of barrier width is defined as:

$$\frac{dw(t)}{dt} = \frac{\mu R_{ON}}{L} i(t) f(t) \tag{1}$$

where i(t) is the amount of current passing through the device and f(t) is a window function with respect to time. For the relationship between barrier width x(t) = w(t)/L and resistance, the state equation is also proposed by [88]:

$$R(t) = R_{ON}x(t) + R_{OFF}(1 - x(t))$$

(2)

x represents the thickness of low resistance doped region of bulk layer (w) over the total thickness of bulk layer (L), giving x = w/L and x ranges from 0 to 1.  $R_{ON}$  is the resistance of the device when it is in its LRS and  $R_{OFF}$  is the resistance of the device when it is in its HRS.

Equations (1) and (2) assume that: (i) the bulk layer does not have any other titanium oxide phases other than TiO<sub>2</sub> and Ti<sub>4</sub>O<sub>7</sub>, (ii) the device could be in any state of intermediate resistance, where the resistivity of the bulk can be between LRS and HRS, (iii) the drifting of oxygen vacancies or barrier width along the bulk length is linear and (iv) the resistance of the bulk layer is defined by the resistance of the highly and lowly doped regions of the bulk layer.

These assumptions have caused many researchers to propose other nonlinear simulation models [91]–[95] that contradict the linearity of this model. These other theories and simulation models also aim to reduce the assumptions of equations (1) and (2). Biolek [91] was the first published memristor model based on the physical memristor device [87]. However, the memristor model is very close to linear behaviour and does not allow flexibility in changing switching parameters. The most accurate memristor model is the Batas & Fiedler memristor model [92] due to the usage of magnetic flux controlled memristor model and it meet the requirements for simulations of multi memristor circuits. Other than that, the Batas & Fiedler model also allows other researchers to easily modify switching speed and boundary conditions in their SPICE model. Therefore, Batas & Fiedler has been selected for further improvement and used in this research work. Furthermore, the switching

mechanism in memristive devices has been proven to involve the formation and collapse of conducting channels, instead of the manipulation of barrier width in the bulk layer [96].

Another type of resistive switching process incorporates the tunnelling probability factor (TPF) between the semiconductor and the metal layers, which is based heavily on Schottky barrier modulation and tunnelling, where the majority charge carrier is electrons. Resistive switching behaviour based on Schottky barrier modulation differs from the conducting channel theories, but these switching behaviour have also been proven to be correct [97]–[99] and the memristor modelling for these type of switching process for MISM memristor devices has also been proposed [100]. However, at the time of this research, the conducting channel theory was used for memristor modelling due to the lack of MISM memristor models and memristor models that are based on the modulation of Schottky barrier.

#### 2.6 Window functions

The drifting of oxygen vacancies is proposed to be nonlinear in physical devices due to the region of high and low resistance not being easily distinguishable in the bulk layer [101]. The electric field along the bulk layer is also nonlinear due to the asymmetric distribution of oxygen vacancies in the bulk layer, which further justifies the theories of nonlinear drift in the bulk layer [102]. Furthermore, the drift velocity of charge carriers is strongly affected by the varying resistance along the bulk layer [103]. This causes the drift velocity of the charge carriers to change non-uniformly as they approach or leave electrodes. It is also postulated that the change in drift velocity near the electrodes may also be due to the charge carriers moving into another medium of different charge density and resistivity. The nonlinear models have displayed simulation results which are closer in agreement to the physical memristive devices [101], [104], [105]. Therefore, the change of drift velocities of charge carriers when it approaches the boundaries is concluded to be nonlinear.

Several window functions, f(x) were proposed to model the nonlinear change of the mobility of charge carriers when approaching electrode-bulk layer boundaries. The window functions proposed are summarized in table 1, arranged in chronological order.

Table 1. Proposed window functions for the behaviour of charge carriers approaching electrode boundaries.

| Author(s)                 | Window function, f(x)                                                 |

|---------------------------|-----------------------------------------------------------------------|

| Strukov et. al. [88]      | $f(x) = x(L - w)/L^2$                                                 |

| Joglekar et. al. [102]    | $f(x) = 1 - (2x - 1)^{2p}$                                            |

| Biolek et. al. [91]       | $f(x) = 1 - (x - stp(-i))^{2p}$                                       |

| Prodromakis et. al. [106] | $f(x) = 1 - [(x - 0.5)^2 + 0.75]^p$                                   |

| Kvatinsky et. al. [107]   | $f_{on}(x) = exp\left[-exp\left(-\frac{x - a_{on}}{p}\right)\right]$  |

|                           | $f_{off}(x) = exp\left[-exp\left(\frac{x - a_{off}}{p}\right)\right]$ |

The first window function to simulate the rate of change of charge carriers was proposed in [88]. The window function was improved by introducing a parameter p for generalization of nonlinear behaviour [102]. A larger value of p would cause the behaviour to be highly nonlinear, while a value of 1 would give a linear behaviour. However, both of these two window functions cause the barrier width to be stuck at the boundaries because these two window functions give the rate of change of barrier width  $(\frac{dw(t)}{dt})$  a value of zero at the boundaries. Thus, the barrier width of the device cannot be adjusted further and x remains stuck at 0 or 1. For example, if w is at L, meaning x is at 1,

$$f(x) = I(L - L) / L^2 = 0$$

(Strukov window function) (3)

$$f(x) = 1 - [2(1) - 1]^{2p} = 0$$

(Joglekar window function for any value of p) (4)

Substituting either of these values into equation (1) would result in a zero rate of change of barrier width. This causes the barrier width to be permanently stuck at 1 in this example.

In order to avoid the simulation of x being stuck at 0 or 1, a window function was proposed to be dependent of current [91], where:

$$stp(i) = \begin{cases} 1, & for \ i \ge 0 \\ 0, & for \ i < 0 \end{cases}$$

(5)

The addition of the *stp* function allows f(x) value to be non-zero, even though x is at 0 or 1. For example, if both p and x are 1, and current is positive  $(i \ge 0)$ , stp(-i) equals to 0. This causes  $f(x) = 1 - (1 - 0)^2 = 0$ . But if a bias of opposing polarity is the applied, or current is negative (i < 0), stp(-i) equals to 1 and  $f(x) = 1 - (1 - 1)^2 = 1$ . This result in a non-zero rate of change of barrier width at the boundaries and the simulation of x does not stuck at 0 or 1.

Although the window function from [91] has solved the stuck-at issues and has parameter p for curve-fittings, it lacks scalability. A new window function that improves scalability giving a range of  $f_{max}$  where  $0 \le f_{max}(x) \le 1$  was proposed by [106]. The simulation of the barrier width does not stuck at 0 or 1, but it is still mathematically possible for x to be stuck at 0 or 1 with certain input parameters. Thus, the window functions for memristors can still be further improved.

### 2.7 Simmons tunnelling current density equation

Before the memristance state equation (1) was proposed, a tunnelling current density equation, known as the Simmons tunnelling current density equation, for an insulator layer sandwiched between two metals was proposed by J. G. Simmons [108] but was unused in previous simulation models. The advantages of this equation are: (i) it includes the behaviour of current that is dependent on the lengths of the insulator layer in MIM structures and (ii) applicable for a various range of voltages applied across the MIM structure. At hitherto, the most detailed expression relating the current and voltage behaviour for a generalized MIM structure is the Simmons tunnelling current density equation.

Currently, no physical devices correlate to equation 1 or any of the window functions in table 1. On the other hand, two publications have suggested close relations between physical memristive devices and Simmons tunnelling current density equation [63], [109]. Due to the window functions hitherto do not fit the Simmons tunnelling current density equation, a window function which correlates to the Simmons equation was proposed by [107]. The Kvatinsky window function fits Simmons equation but it lacks scalability and does not guarantee symmetrical behaviour. This means that according to their window function and depending on parameters, the rate of change of drift velocity of charge carriers moving towards one electrode may be different from towards the opposite electrode. They also introduced two more fitting parameters in the form of a<sub>on</sub> and a<sub>off</sub>, used to fit the model to the Simmons equation.

The Simmons tunnelling current density is given as:

$$J = \int_0^{E_m} D(E_x) \xi dE_x \tag{6}$$

where  $\zeta$  is defined as:

$$\xi = \frac{4\pi q m^2}{h^3} \int_0^\infty [f(E) - f(E + eV)] dE_r \tag{7}$$

and  $D(E_x)$  is a function of the probability of an electron being able to overcome the potential barrier posed by the insulating layer and penetrate through from one electrode to another. f(E) and f(E+eV) is the Fermi-Dirac functions for electrons following and against the potential barrier respectively, while  $dE_r$  is the integral with respect to the effective electron direction. The Simmons tunnel equation is the most accurate due to its consideration of distribution and drifting of electrons in both directions. However, the probability function  $D(E_x)$  is ambiguous and difficult to obtain. Thus, further research is still needed for the modelling of the general memristive switching behaviour in MIM devices.

### 2.8 Memristor modelling for MIM devices

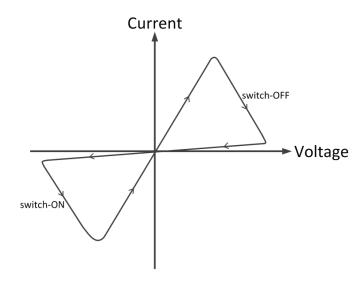

Various SPICE memristor models and various window functions have been published to simulate memristive behaviour of MIM devices [91]–[95] according to the memristor theory [47] and behaviour of physical memristor devices [88]. These memristor models are widely used in simulating various electronic applications due to the absence of memristor component in current Electronic Design Automation (EDA) software. The SPICE memristor models [91]–[95] are based on Bipolar Resistance Switching (BRS) mechanism similar to the characteristics exhibited by physical memristors, which conforms to the memristor theory [47] and behaviour of physical memristor devices [88].

Among the SPICE memristor models, it was observed that there is room for improvement in the Batas & Fiedler model [92]. This memristor model is versatile because it can accommodate a variety of window functions. At the time of writing, this memristor model is being cited by at least 156 other publications, which justifies its popularity and suitability in electronic applications. Thus, chapter 3 of this dissertation explains the research work that has been conducted to improve on the Batas & Fiedler SPICE memristor model. This SPICE memristor model is then used throughout the remainder of this research work [110].

In this SPICE memristor model, noise was not included into the simulation model because noise can be random and is also dependent on the application that uses the memristor. Furthermore, all the MIM memristor models that are available in

the literature review do not include noise into the SPICE memristor models. This is because noise in memristor has not yet been fully researched. Experimental data on the effect of noise on memristance switching behaviour is also not available in the literature. However, the effect of noise in memristor model is important and could be included into future researches.