# Selective Harmonic Elimination Methods for a Cascaded H-Bridge Converter

Alan James Watson MEng. (Hons)

Submitted to the University of Nottingham for the degree of Doctor of Philosophy, September 2008.

#### Abstract

In recent years there has been an increased demand for integration of renewable energy into the electricity grid. This has increased research into power converter solutions required to integrate renewable technology into the electricity supply. One such converter is a Cascaded H-Bridge (CHB) Multilevel Converter.

Operation of such a topology requires strict control of power flow to ensure that energy is distributed equally across the converters energy storage components. For operation at high power levels, advanced modulation methods may be required to ensure that losses due to non-ideal semiconductor switching are minimised, whilst not compromising the quality of the voltage waveform being produced by the converter.

This thesis presents several low switching frequency modulation methods based on Selective Harmonic Elimination (SHE) in order to address these two operational issues. The methods presented involve manipulating the H-Bridge cell voltages of the CHB converter to control power flow. Simulated results are supported by experimental verification from a seven level, single phase CHB converter.

### Acknowledgements

I would like to thank Professor Leopoldo Franquelo and Dr Mark Sumner for sparing their time to examine me on the work in this thesis.

I would also like to thank my supervisors Professor Pat Wheeler and Professor Jon Clare for their support and patience over the duration of this work.

Thanks also to the PEMC group at the University of Nottingham for providing a pleasant environment to work in. I would especially like to thank Dr Ed Christopher, Dr Lee Empringham, Dr Liliana de Lillo and Dr Si Dang for their friendship and support over the last few years. Thank you to Dr Joseph Vassallo and Dr David Gerry for their help in the first few months of the research- even when they were both very busy.

Thanks to my family. My brothers Jason, Andy, Neil, Gary and Jonathan for being supportive over the course of this work and for generally being there when I needed them. Thanks also to my parents for keeping me motivated and for having more confidence in me than I do in myself.

Finally, to Sol. Thanks for all of your support and patience over the last four years... I know it's not been easy. I would also like to thank your family for being supportive over the course of this work.

Thank you.

#### List of Terms

- CHB Cascaded H-Bridge

- $SHE\,$  Selective Harmonic Elimination

- SHE-MC Selective Harmonic Elimination Magnitude Control

- SHE-MPC Selective Harmonic Elimination Magnitude and Phase Control

- $E\,$  DC link capacitor voltage

- $E_n$  DC link capacitor voltage of  $n_{th}$  cell

- $V_o\,$  Output converter voltage

- ${\cal N}\,$  Number of H-bridge cells per phase

- $T_1$  Space vector State 1 time

- $T_2$  Space vector State 2 time

- $T_3$  Space vector State 3 time

- $U_1$  Space vector State 1

- $U_2$  Space vector State 2

- $U_3\,$  Space vector State 3

- $T_s$  Sampling time

- $\theta_{CTOT}\,$  Total converter vector displacement from supply current vector

- $\theta_{Cn}\,$   $n_{th}$  cell vector displacement from supply current vector

- $V_{Cn}\,$   $n_{th}$  cell converter voltage

- $I_s$  Supply Current

- $V_s$  Supply Voltage

- $V_l$  Inductor Voltage

- ${\cal L}\,$  Converter inductance

- $R_n$   $n_{th}$  cell DC side load resistance

- $P_{CTOT}$  Total converter active power

$Q_{CTOT}$  - Total converter reactive power

$P_{Cn}$  -  $n_{th}$  cell active power

$Q_{Cn}$  -  $n_{th}$  cell reactive power

$i - i_{th}$  SHE switching angle

$V_1$  - Fundamental voltage magnitude

n -  $n_{th}$  harmonic component

M - Number of switching angles per quarter cycle of SHE

$\lambda\,$  - Modulation Index

$\lambda_n$  - Modulation Index of  $n_{th}$  cell

$\alpha_i$  -  $i_{th}$  switching angle in SHE waveform

$V_{CTOT}$  - Total Converter Voltage

$P_{TOTAL}$  - SHE-MPC calculation total converter active power

$Q_{TOTAL}\,$  - SHE-MPC calculation total converter reactive power

$\delta_n$  - Displacement angle of the  $n_{th}$  cell voltage vector from the total converter voltage vector

$V_n$  -  $n_{th}$  harmonic voltage

$I_s^*$  - Current Demand

$\lambda_{total}$  - Total converter average modulation index

$I_{s(peak)}$  - Peak of Supply Current

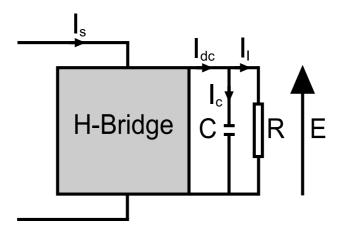

$I_{dc}\,$  - H-Bridge DC side current

$\mathcal{I}_l$ - H-Bridge DC side load current

${\cal I}_c\,$  - H-Bridge DC side capacitor current

$S_n$  - Switching function of  $n_{th}$  cell

$\lambda_{upper}$  - Lowest modulation index in solution space

$\lambda_{lower}$  - Highest modulation index in solution space

$\lambda_{max}^*$  - Maximum demanded modulation index

$\lambda_{min}^*$  - Minimum demanded modulation index

$E_{peak}$  - Total DC Link Capacitor Voltage

$V_{s(peak)}$  - Peak supply voltage

$V_{s\alpha}$  -  $\alpha$  axis component of supply voltage

$V_{s\beta}$  -  $\beta$  axis component of supply voltage

$V_{sd}\,$  - d-axis component of supply voltage

$V_{sd}\,$  - q-axis component of supply voltage

${\cal I}_{sd}\,$  - d-axis component of supply current

$I_{sd}\,$  - q-axis component of supply current

$V_{cd}\,$  - d-axis component of converter voltage

$V_{cd}\,$  - q-axis component of converter voltage

## Contents

| 1 | Inti | oduct  | ion                                        | 2  |

|---|------|--------|--------------------------------------------|----|

|   |      | 1.0.1  | Thesis plan                                | 8  |

| 2 | Ove  | erview | of Multilevel Technology                   | 10 |

|   | 2.1  | Introd | luction                                    | 10 |

|   | 2.2  | Multil | level Converters                           | 10 |

|   |      | 2.2.1  | Neutral Point Clamped Multilevel Converter | 12 |

|   |      | 2.2.2  | 'Flying' Capacitor Multilevel Converter    | 14 |

|   |      | 2.2.3  | Cascaded H-Bridge Multilevel Converter     | 15 |

|   |      | 2.2.4  | Comparison of Multilevel topologies        | 17 |

|   | 2.3  | Modu   | lation methods for the CHB topology        | 17 |

|   |      | 2.3.1  | Level shifted Carrier PWM                  | 18 |

|   |      | 2.3.2  | Phase Shifted Carrier PWM                  | 20 |

CONTENTS vii

|   |     | 2.3.3  | Selective Harmonic Elimination (SHE)                     | 20 |

|---|-----|--------|----------------------------------------------------------|----|

|   |     | 2.3.4  | Staircase Modulation                                     | 24 |

|   |     | 2.3.5  | Space Vector Modulation                                  | 26 |

|   | 2.4 | Summ   | nary                                                     | 28 |

| 3 | SHI | E-PWI  | M for power flow control                                 | 30 |

|   | 3.1 | Introd | luction                                                  | 30 |

|   | 3.2 | Backg  | round to balancing using SHE                             | 30 |

|   | 3.3 | Formu  | nlation of SHE waveform                                  | 34 |

|   | 3.4 | Solvin | g SHE equations                                          | 36 |

|   | 3.5 | Comp   | lete phase decoupling                                    | 39 |

|   | 3.6 | Multil | level SHE-PWM for active power balancing                 | 40 |

|   | 3.7 | Decou  | apled SHE-PWM with magnitude control (SHE-MC)            | 44 |

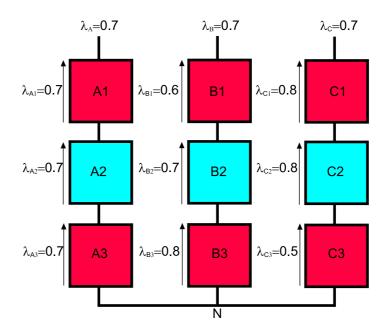

|   |     | 3.7.1  | SHE-MC assuming triplen harmonic cancellation            | 45 |

|   |     | 3.7.2  | SHE-MC with triplen harmonic elimination                 | 51 |

|   | 3.8 | Decou  | apled SHE-PWM with magnitude and phase control (SHE-MPC) | 59 |

|   |     | 3.8.1  | Choice of $\delta$                                       | 65 |

|   |     | 3.8.2  | SHE-MPC assuming third harmonic cancellation             | 67 |

|   |     | 3.8.3  | SHE-MPC with triplen harmonic elimination                | 68 |

CONTENTS viii

|   | 3.9  | Summary                                                        | 74  |

|---|------|----------------------------------------------------------------|-----|

| 4 | Con  | verter balancing control                                       | 75  |

|   | 4.1  | Introduction                                                   | 75  |

|   | 4.2  | Requirements of the balancing scheme                           | 75  |

|   | 4.3  | Balancing control structure                                    | 77  |

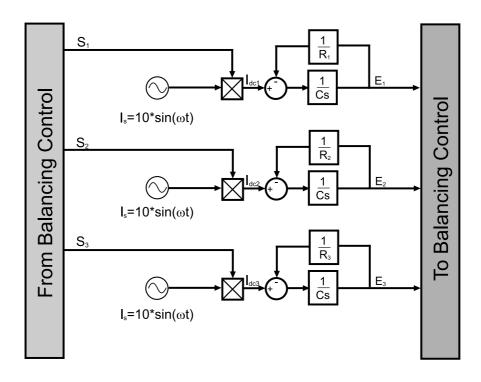

|   | 4.4  | Modelling and control design                                   | 78  |

|   | 4.5  | Balancing Control applied to model converter                   | 79  |

|   | 4.6  | Simulation using SHE- Magnitude Control (SHE-MC)               | 83  |

|   | 4.7  | Simulations using SHE magnitude and phase control (SHE-MPC) $$ | 87  |

|   |      | 4.7.1 Alternative Implementation of SHE-MPC                    | 88  |

|   | 4.8  | Simulation with PSC-PWM                                        | 90  |

|   | 4.9  | Limits of balance using SHE-MC and SHE-MPC                     | 92  |

|   | 4.10 | Summary                                                        | 95  |

| 5 | Des  | ign and Simulation of Converter                                | 97  |

|   | 5.1  | Introduction                                                   | 97  |

|   | 5.2  | Configuration of CHB converter                                 | 98  |

|   |      | 5.2.1 Line Inductance Value                                    | 99  |

|   |      | 5.2.2 DC link Capacitance                                      | 100 |

CONTENTS ix

|   | 5.3 | Syncre | onisation to grid                        | 101 |

|---|-----|--------|------------------------------------------|-----|

|   | 5.4 | Conve  | erter control loop formulation           | 105 |

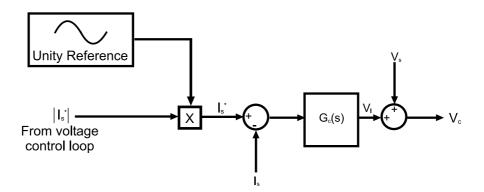

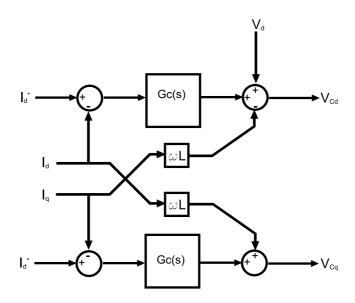

|   |     | 5.4.1  | Current Control                          | 105 |

|   |     |        | 5.4.1.1 Stationary Frame current control | 106 |

|   |     |        | 5.4.1.2 Rotating Frame current control   | 107 |

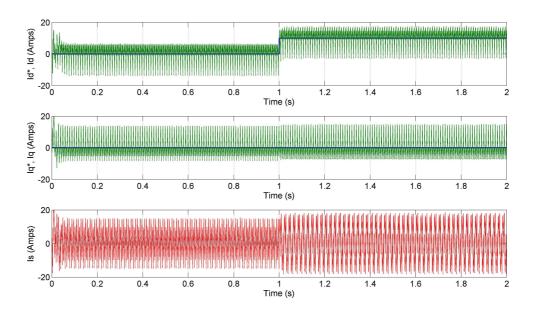

|   |     | 5.4.2  | Simulation of Current Control            | 110 |

|   |     | 5.4.3  | Voltage control                          | 112 |

|   |     | 5.4.4  | Application of balancing control         | 116 |

|   |     | 5.4.5  | Balancing Control using SHE-MC           | 117 |

|   |     | 5.4.6  | Balancing Control using SHE-MPC          | 120 |

|   | 5.5 | Summ   | nary                                     | 128 |

| 6 | Exp | erime  | ntal Converter                           | 129 |

|   | 6.1 | Introd | luction                                  | 129 |

|   | 6.2 | Rectif | dier Design                              | 129 |

|   | 6.3 | H-brio | dge design                               | 133 |

|   | 6.4 | Contr  | ol of Converter                          | 136 |

|   |     | 6.4.1  | FPGA Card                                | 137 |

|   |     | 6.4.2  | C6711DSK                                 | 140 |

CONTENTS

|              |     | 6.4.3   | Summary                                           | 141 |

|--------------|-----|---------|---------------------------------------------------|-----|

| 7            | Exp | erime   | ntal Results                                      | 142 |

|              | 7.1 | Introd  | uction                                            | 142 |

|              | 7.2 | Exper   | imental Setup                                     | 142 |

|              | 7.3 | SHE-N   | MC Results                                        | 143 |

|              |     | 7.3.1   | Comparison with simulation                        | 149 |

|              | 7.4 | SHE-N   | MPC Results                                       | 151 |

|              |     | 7.4.1   | Changes to SHE-MPC                                | 151 |

|              |     | 7.4.2   | SHE-MPC Experimental Results                      | 151 |

|              |     |         | 7.4.2.1 Comparison with simulation                | 156 |

|              |     | 7.4.3   | SHE-MPC Reduced Calculations Experimental results | 158 |

|              |     |         | 7.4.3.1 Comparison with simulation                | 163 |

|              | 7.5 | Summ    | ary                                               | 165 |

| 8            | Cor | clusio  | $\mathbf{n}\mathbf{s}$                            | 167 |

|              |     | 8.0.1   | Summary of achievements                           | 171 |

|              |     | 8.0.2   | Further work                                      | 172 |

| $\mathbf{A}$ | Mo  | dulatio | on Index Operating Point                          | 184 |

| COMPENIE |    |

|----------|----|

| CONTENTS | VI |

| CONTENIO | Al |

| В            | Twice Power Pulsation on H-bridge | 186 |

|--------------|-----------------------------------|-----|

| $\mathbf{C}$ | Derivation of DQ current control  | 188 |

| D            | Voltage Control Plant             | 190 |

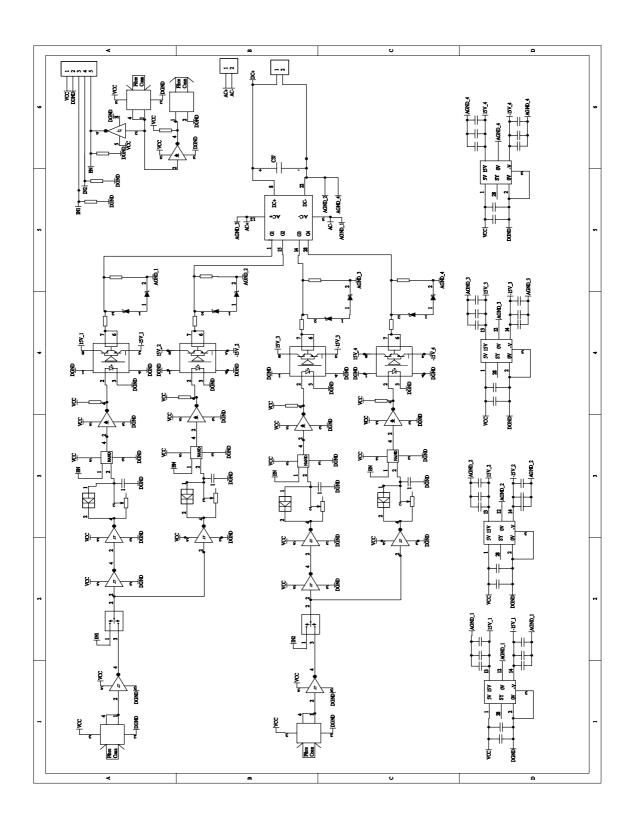

| ${f E}$      | H-Bridge Schematic                | 191 |

| $\mathbf{F}$ | Published Papers                  | 193 |

# List of Figures

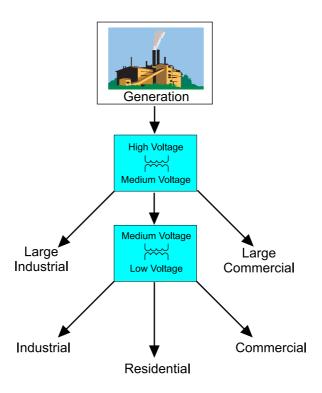

| 1.1 | Diagram showing functionality of a classical electricity grid system              | 3  |

|-----|-----------------------------------------------------------------------------------|----|

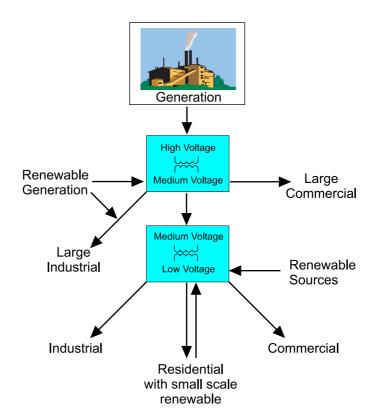

| 1.2 | Diagram showing functionality of a Distributed Generation electricity grid system | 4  |

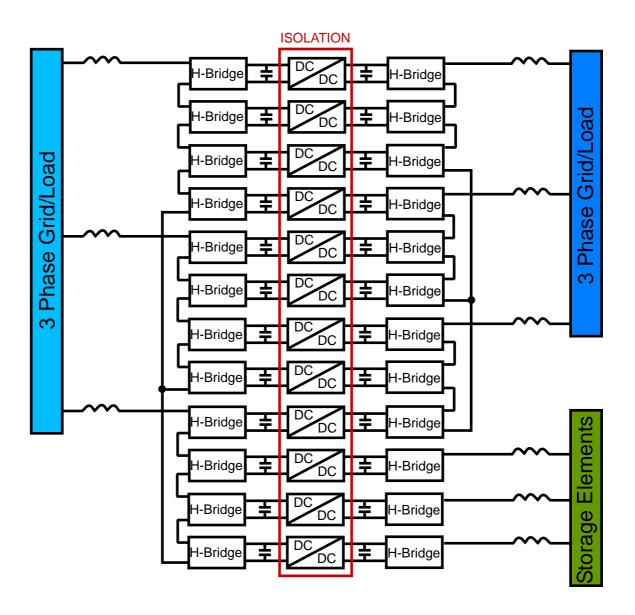

| 1.3 | The UNIFLEX converter structure for three port power flow                         | 6  |

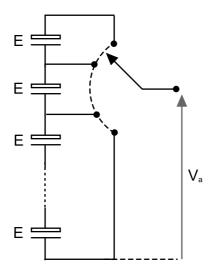

| 2.1 | General concept of a Multilevel voltage converter                                 | 11 |

| 2.2 | Three Level Neutral Point Clamped converter                                       | 13 |

| 2.3 | Three Level 'Flying' Capacitor Multilevel Converter                               | 14 |

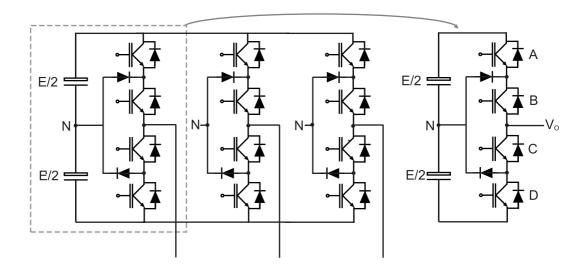

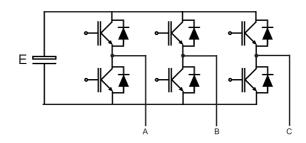

| 2.4 | Five Level Cascaded H-Bridge Multilevel Converter                                 | 16 |

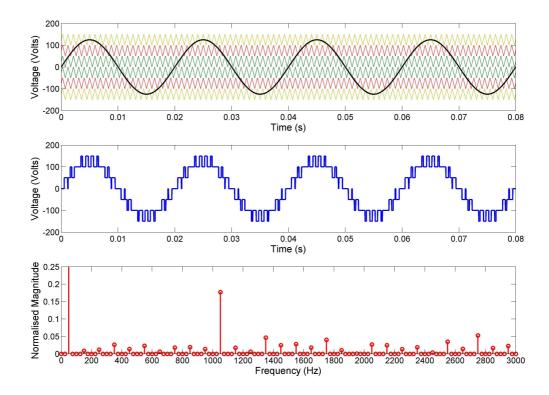

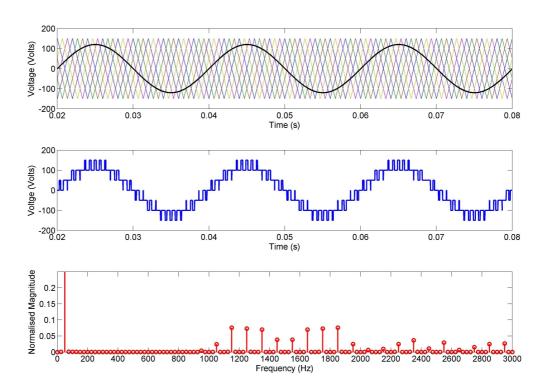

| 2.5 | Seven Level, Level Shifted Carrier Waveforms and associated spectrum              | 19 |

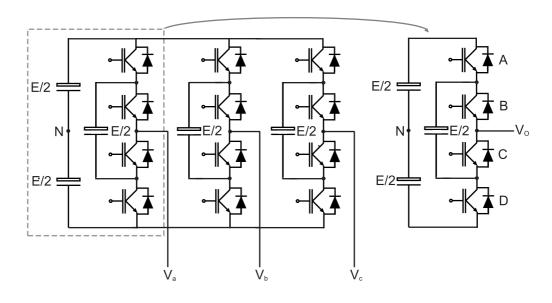

| 2.6 | Seven Level, Phase shifted Carrier Waveform and FFT, $f_{sw}$ =250Hz .            | 21 |

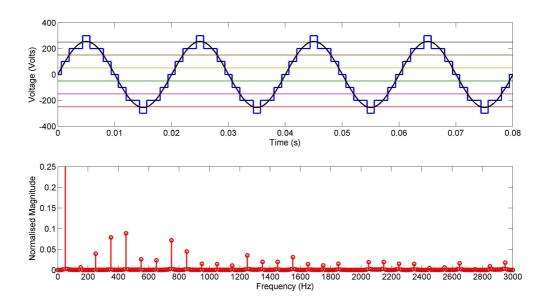

| 2.7 | Staircase modulation waveform and spectrum                                        | 24 |

| 2.8 | Application of SHE to staircase modulation                                        | 25 |

LIST OF FIGURES xiii

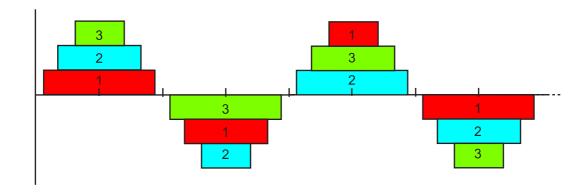

| 2.9  | Example of swapping scheme use for power balancing in staircase mod-                                                                                                                             |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ulation scheme                                                                                                                                                                                   | 25 |

| 2.10 | Classical three phase converter                                                                                                                                                                  | 26 |

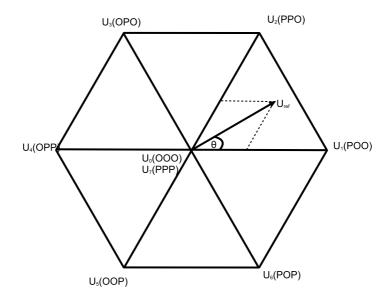

| 2.11 | Two level SVM state diagram                                                                                                                                                                      | 27 |

| 2.12 | Three level SVM state diagram                                                                                                                                                                    | 27 |

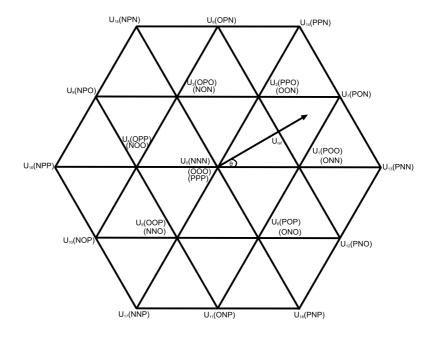

| 3.1  | Diagram showing the power flow relationships for each cell of a seven level CHB converter                                                                                                        | 32 |

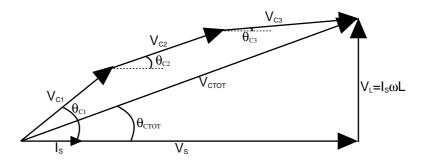

| 3.2  | Phasor diagram of seven level converter manipulating cell phase and voltage magnitude                                                                                                            | 32 |

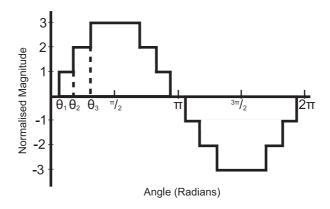

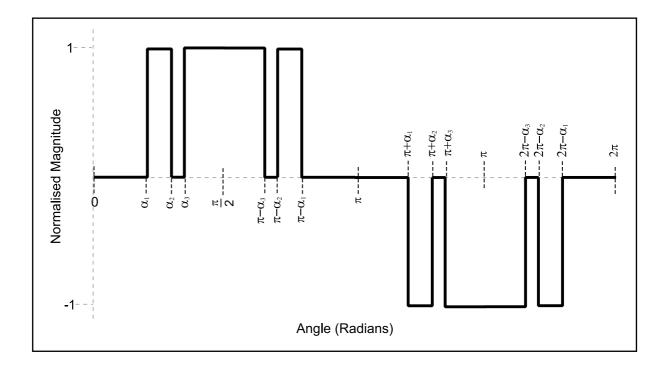

| 3.3  | Example of a three level SHE waveform with three switching angles per quarter cycle                                                                                                              | 34 |

| 3.4  | Diagram showing example of three balanced phases with differently imbalanced cell loads. In this case the triplen harmonic components may not always cancel to zero in the line to line waveform | 40 |

| 3.5  | Plot of solution space for 150Hz multilevel SHE balancing scheme. This plot is for a $\pm 1\%$ imbalance set                                                                                     | 42 |

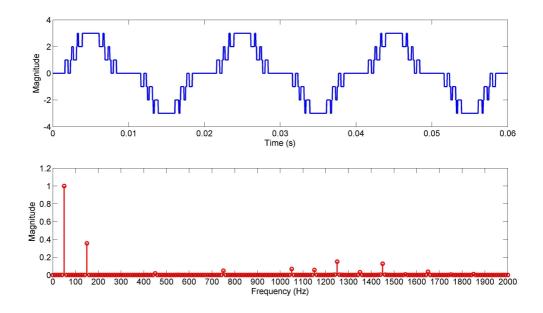

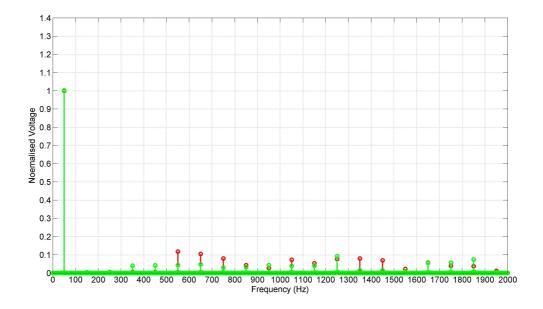

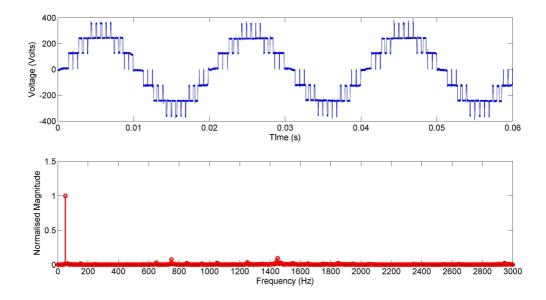

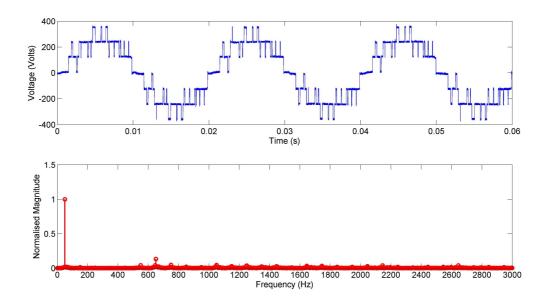

| 3.6  | Plot of switching waveform and FFT spectrum for 150Hz $\pm 1\%$ imbalance angle set at $\lambda=0.6$                                                                                             | 43 |

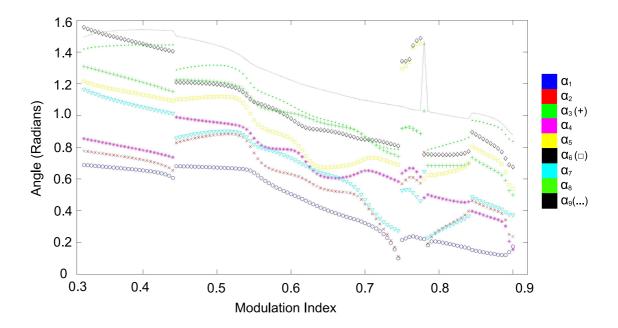

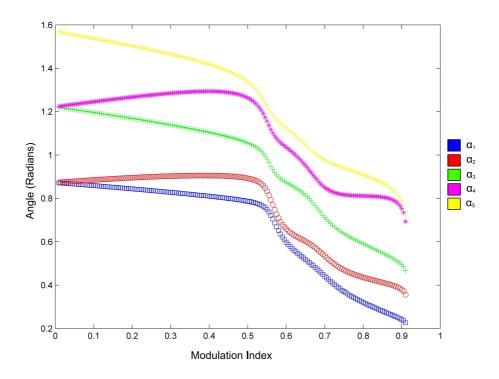

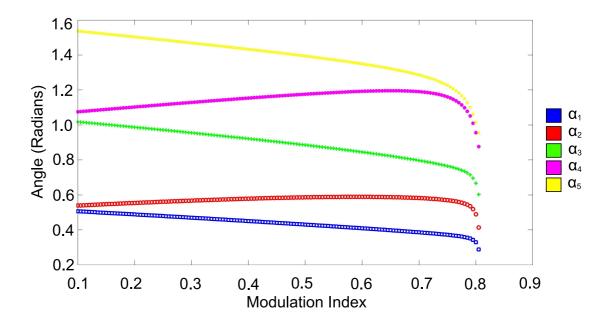

| 3.7  | Solutions for 250Hz SHE balancing system without triplen harmonic elimination                                                                                                                    | 47 |

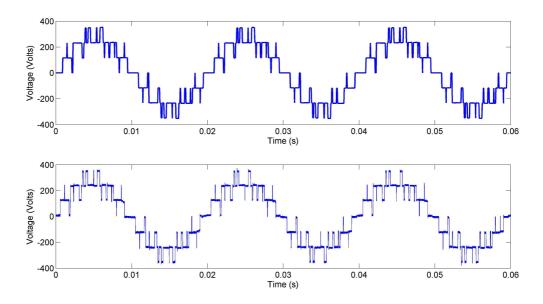

| 3.8  | (Top) Simulated AC waveform with $\lambda_1$ =0.6, $\lambda_2$ =0.4, $\lambda_3$ =0.8. (Bottom) FFT spectrum of waveform up to 2000Hz                                                            | 48 |

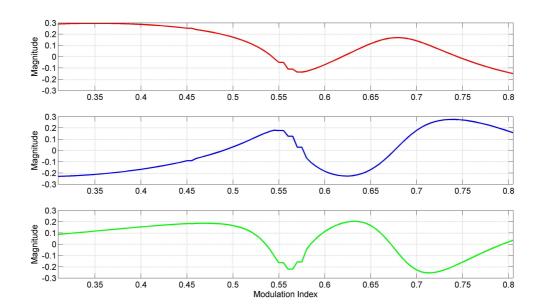

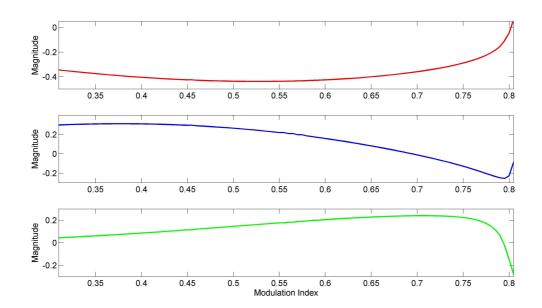

| 3.9  | (Bottom) 23rd harmonic magnitude (Middle) 19th narmonic magnitude (Bottom) 23rd harmonic amplitude (normalised to a DC link value of unity) for full range of modulation indices            | 49 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

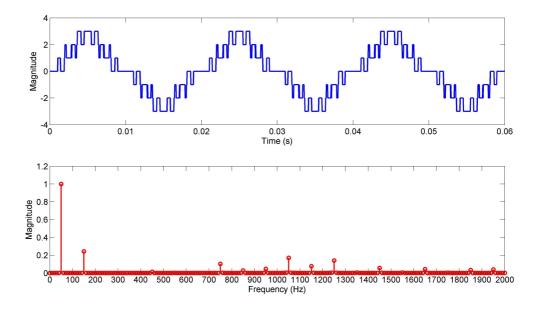

| 3.10 | Plot of solution space for 250Hz imbalance scheme with triplen harmonic elimination                                                                                                         | 53 |

| 3.11 | (Top) 11th harmonic magnitude (Middle) 13th harmonic magnitude (Bottom) 15th harmonic magnitude (normalised to a DC link value of unity) for full range of modulation indices.              | 54 |

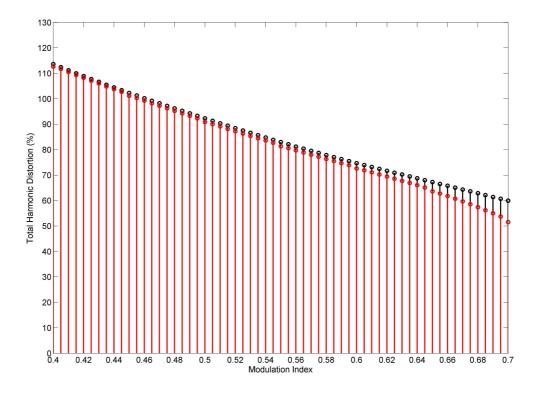

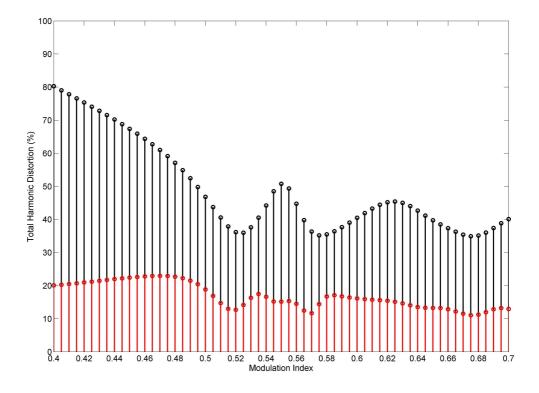

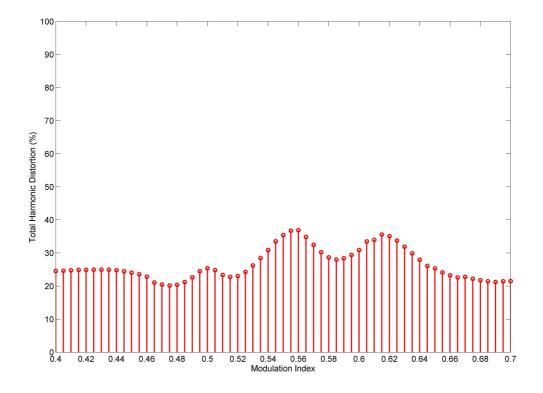

| 3.12 | THD versus modulation index for (Black) balanced cells and (Red) $\pm 10\%$ imbalanced cells                                                                                                | 57 |

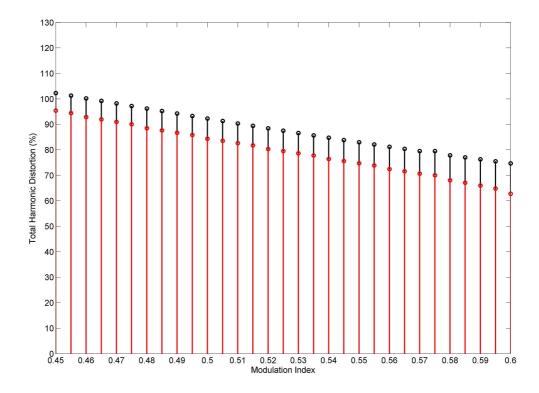

| 3.13 | THD versus modulation index for (Black) balanced cells and (Red) $\pm 25\%$ imbalanced cells. A smaller range has been used due to the limitations in the calculated switching angles range | 58 |

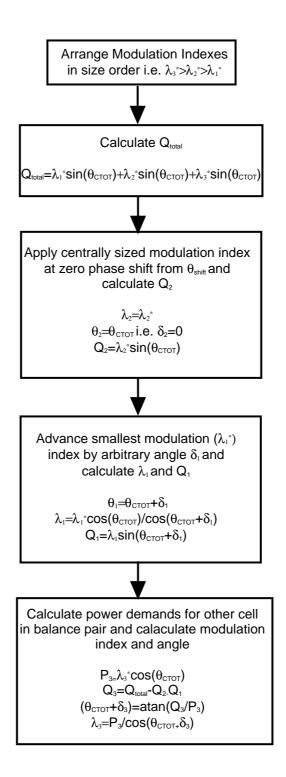

| 3.14 | Flow diagram of SHE-MPC system for a seven level converter where $\lambda_3^*>\lambda_2^*>\lambda_1^*$                                                                                      | 64 |

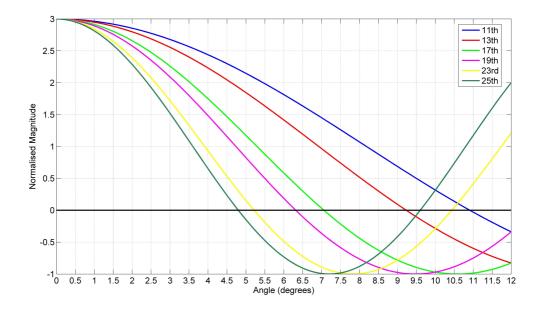

| 3.15 | Reduction of harmonics as a function of converter cell phase shift                                                                                                                          | 66 |

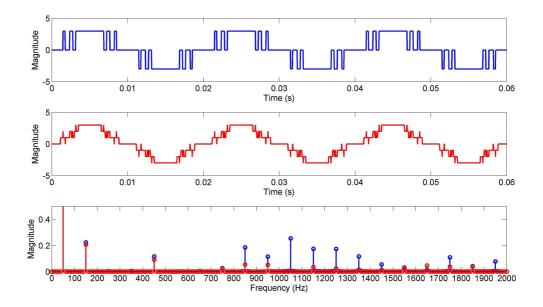

| 3.16 | SHE-MC waveform (Blue) with SHE-MPC waveform (Red) for $\lambda_1^* = \lambda_2^* = \lambda_3^* = 0.7$ and $\theta_{total} = 7.05^o$                                                        | 68 |

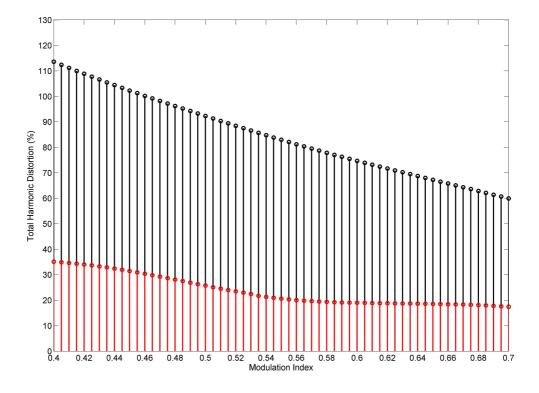

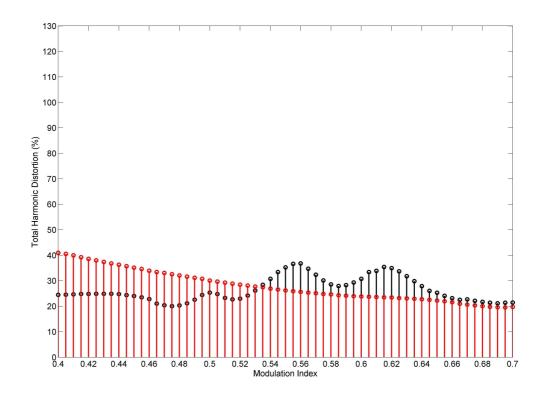

| 3.17 | THD over modulation index range for $0\%$ imbalance using SHE-MC(Black) and SHE-MPC (Red) when the triplens are assumed to cancel                                                           | 69 |

| 3.18 | THD over modulation index range for $\pm 10\%$ imbalance using SHE-MPC when the triplens are assumed to cancel                                                                              | 70 |

| 3.19 | THD over modulation index range for $0\%$ imbalance using SHE-MC(Black) and SHE-MPC with triplen harmonic elimination(Red)                                                                  | 71 |

| 3.20 | THD over modulation index range for $\pm 10\%$ imbalance using SHE-MPC without triplen elimination (Black) and SHE-MPC with triplen |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

|      | elimnation (Red)                                                                                                                    | 73 |

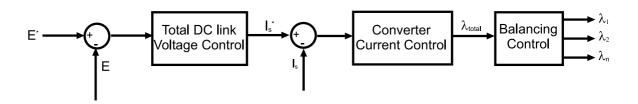

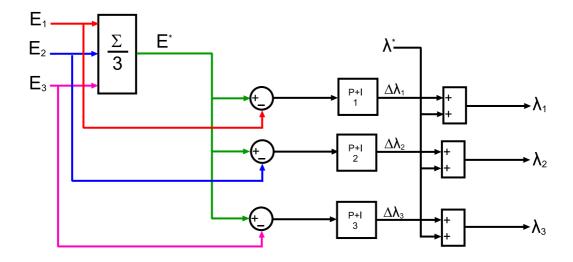

| 4.1  | General Active Rectifer controller with balancing                                                                                   | 76 |

| 4.2  | Diagram of proposed balancing control system                                                                                        | 77 |

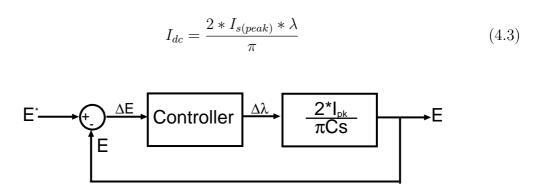

| 4.3  | General structure used for balancing control loop design                                                                            | 78 |

| 4.4  | Root locus and ideal step response for balancing system                                                                             | 79 |

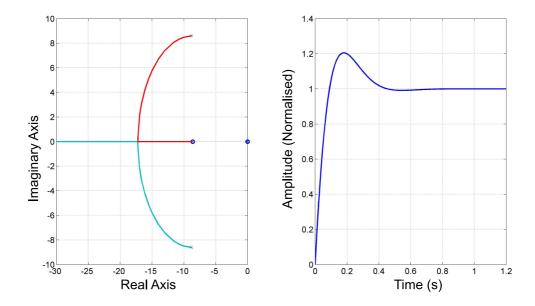

| 4.5  | General model for verification of balancing control                                                                                 | 80 |

| 4.6  | Diagram showing H-bridge Currents for modelling                                                                                     | 81 |

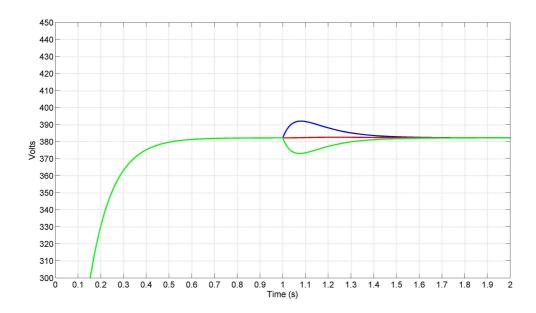

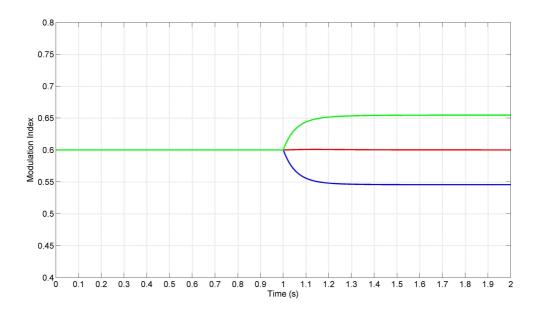

| 4.7  | Plot showing control of DC link voltages using balancing scheme and a simple model. The DC load imbalance is applied at $t=1s.$     | 82 |

| 4.8  | Plot showing variation in modulation index during balancing of an imbalanced load. The DC load imbalance is applied at $t=1s.$      | 82 |

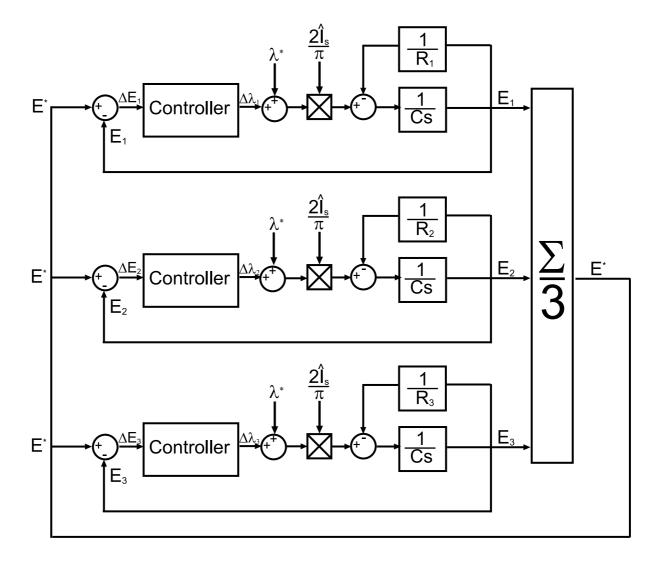

| 4.9  | Switching model for verification of balancing control for a seven level CHB converter                                               | 84 |

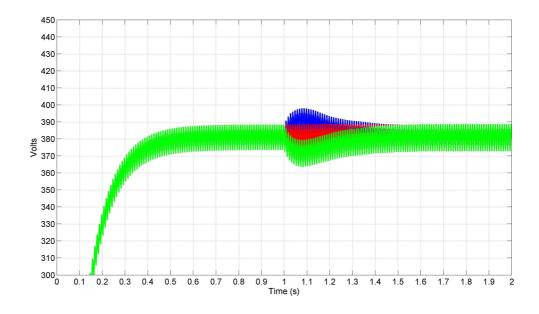

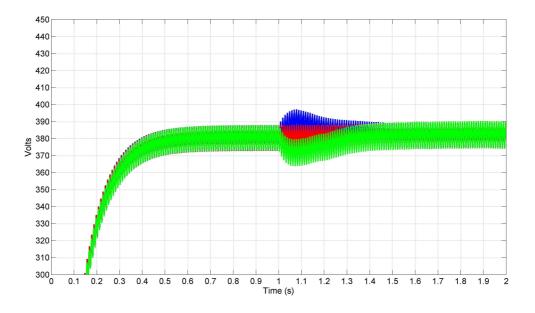

| 4.10 | Balancing control result applied to SHE-MC control. Imbalance applied at t=1s                                                       | 85 |

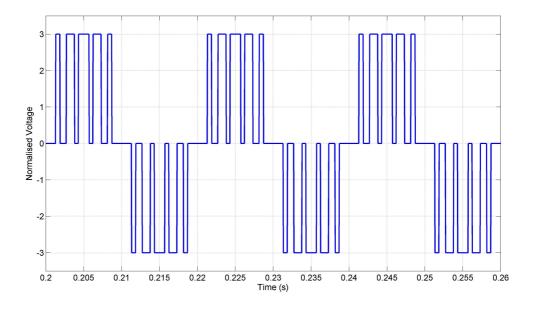

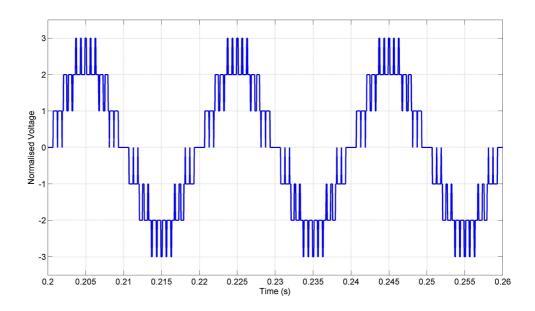

| 4.11 | Waveform under balanced conditions using SHE-MC. Note the resultant three level waveform                                            | 85 |

| 4.12 | Waveform under unbalanced conditions using SHE-MC, note that the waveform is still predominantly three level                        | 86 |

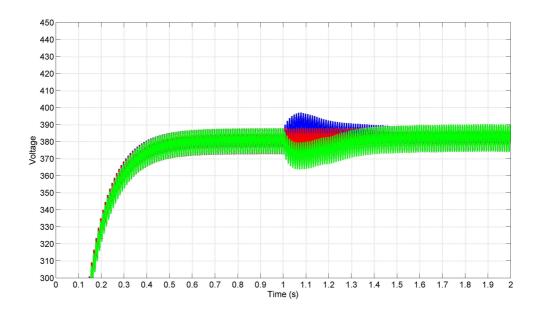

| 4.13 | plied at t=1s                                                                                                                             | 87  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

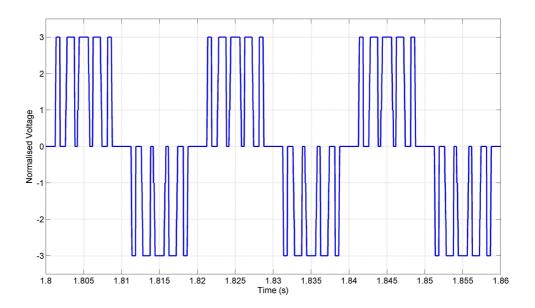

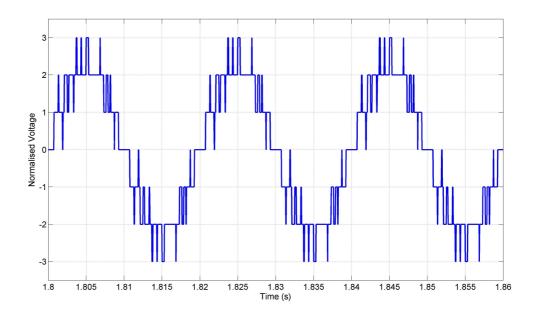

| 4.14 | Waveform under balanced conditions using SHE-MPC                                                                                          | 88  |

| 4.15 | Waveform under unbalanced conditions using SHE-MPC                                                                                        | 89  |

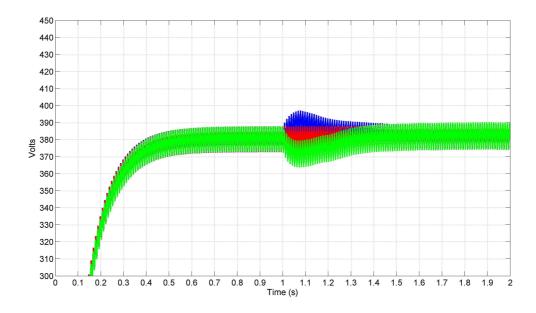

| 4.16 | Balancing control result applied to SHE-MPC with reduced calculations control. Imbalance applied at $t=1s$                                | 90  |

| 4.17 | DC transient results for phase shifted carrier scheme                                                                                     | 91  |

| 4.18 | Comparison of FFT spectrum for SHE-MPC(Red) and PSC (Green) under a $\pm 25\%$ imbalance. Note the low order harmonic content under PSC   | 92  |

| 4.19 | Phasor diagram of seven level converter manipulating cell phase and voltage magnitude                                                     | 93  |

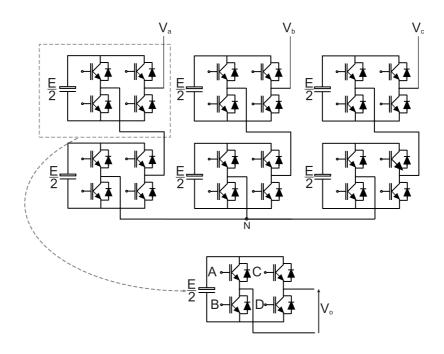

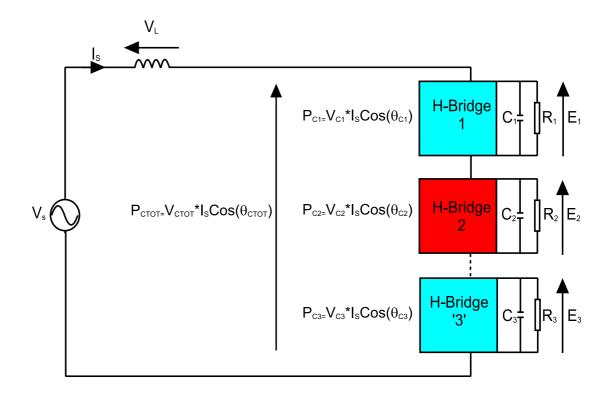

| 5.1  | Schematic of converter topology for simulation and experimental verification                                                              | 98  |

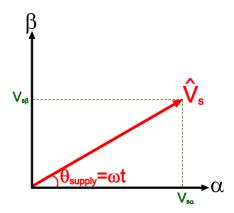

| 5.2  | Vector diagram showing supply voltage vector and its position on the alpha/beta axis                                                      | 102 |

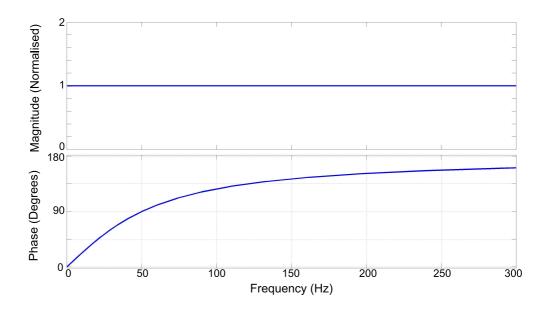

| 5.3  | Plot of Magnitude and Phase for Allpass filter with 90° phase shift at 50Hz                                                               | 104 |

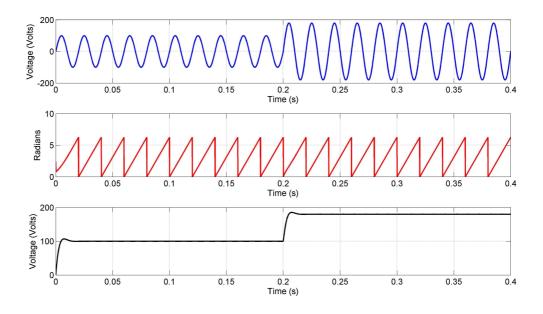

| 5.4  | (Top) Supply Voltage with step change at 0.2s (Middle) Derived $\theta_{supply}$ angle and (Bottom) Derived supply voltage peak magnitude | 104 |

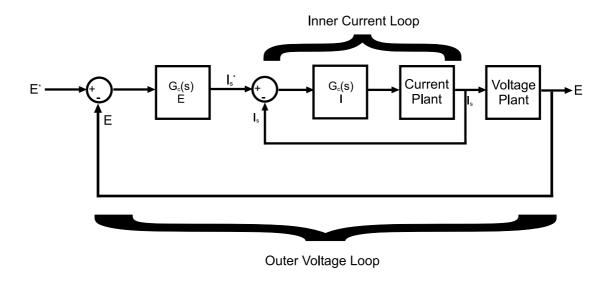

| 5.5  | General Active Rectifier Control Diagram showing nested current loop                                                                      | 105 |

| 5.6  | Basic Stationary Frame Current Controller                                                                                                 | 106 |

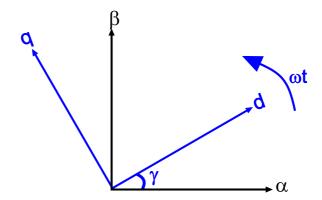

| 5.7  | Vector diagram showing alpha and beta components and their mapping onto the dq axis                                                                                         | 107 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

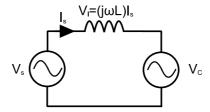

| 5.8  | Model of AC side of converter for derivation of DQ control                                                                                                                  | 108 |

| 5.9  | Diagram showing basic DC current controller for Active Rectifier                                                                                                            | 109 |

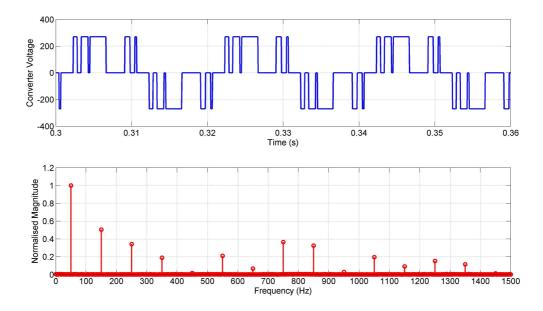

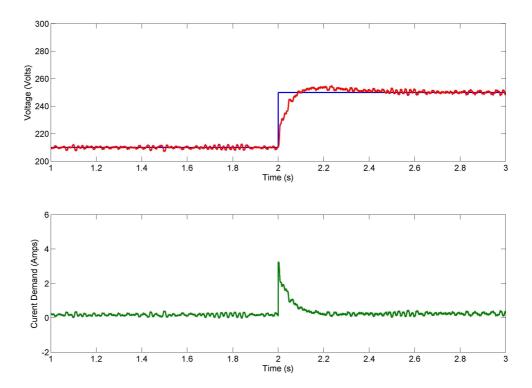

| 5.10 | Plot of test response using SHE for dq control. (Top) Plot of $I_d^*$ and $I_d$ . (Middle)Plot of $I_q^*$ and $I_q$ . (Bottom) Plot of $I_s$                                | 111 |

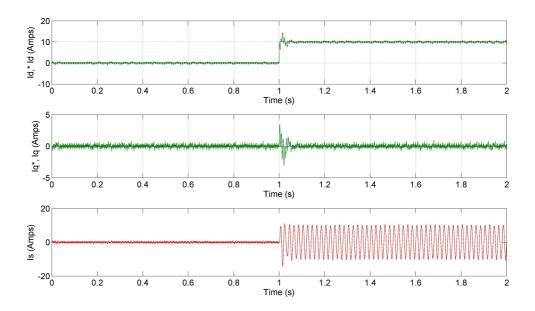

| 5.11 | Converter voltage in steady state when supply current is un-filtered .                                                                                                      | 112 |

| 5.12 | Plot of test response using SHE for dq control with filter applied. (Top) Plot of $I_d^*$ and $I_d$ . (Middle)Plot of $I_q^*$ and $I_q$ . (Bottom) Plot of $I_s$ (filtered) | 113 |

| 5.13 | Converter voltage in steady state when supply current is filtered                                                                                                           | 114 |

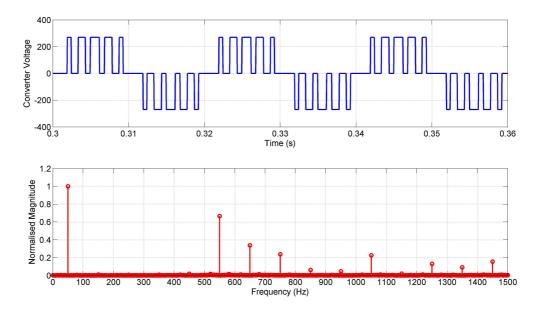

| 5.14 | Step response of designed DC Link Capacitor Voltage and current control (step demand of DC Link Capacitor Voltage)                                                          | 115 |

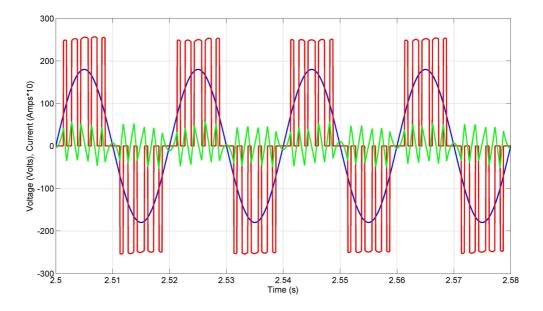

| 5.15 | Closed loop AC Supply Voltage (Blue), Converter Voltage (Red) and Supply Current (Green) under the DC control scheme                                                        | 116 |

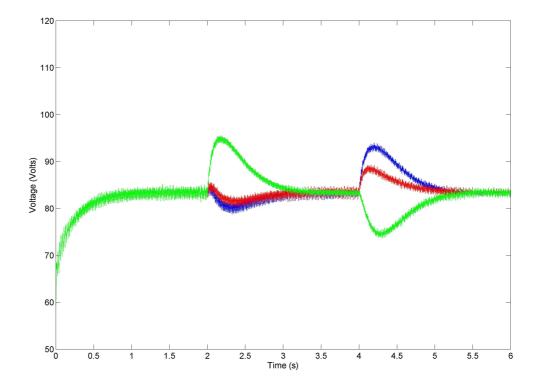

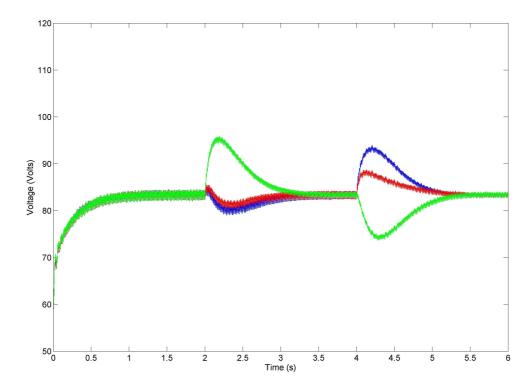

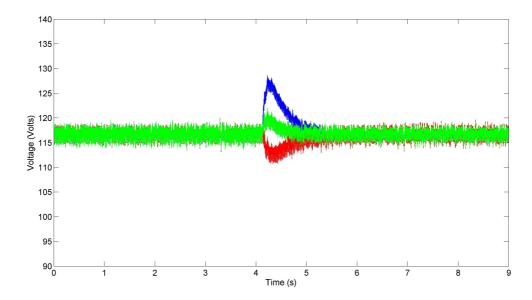

| 5.16 | Balancing of DC link capacitor voltages of active rectifier using SHE-MC                                                                                                    | 118 |

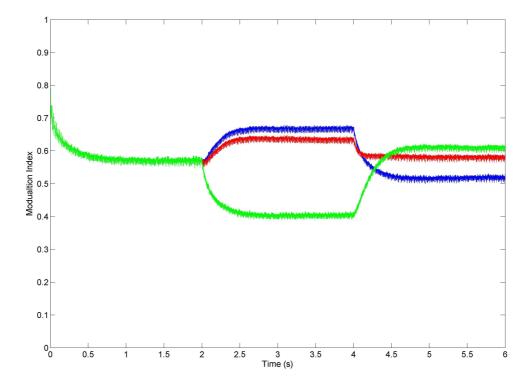

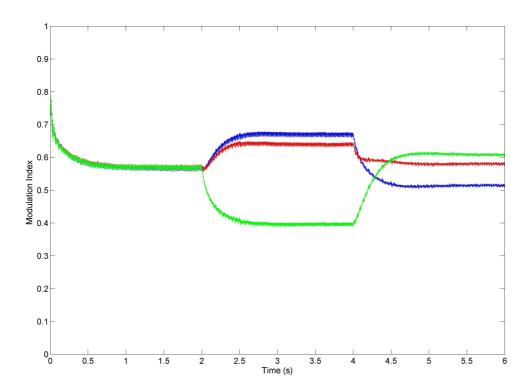

| 5.17 | Variation of modulation index to achieve balancing of DC link capacitor voltages using SHE-MC                                                                               | 119 |

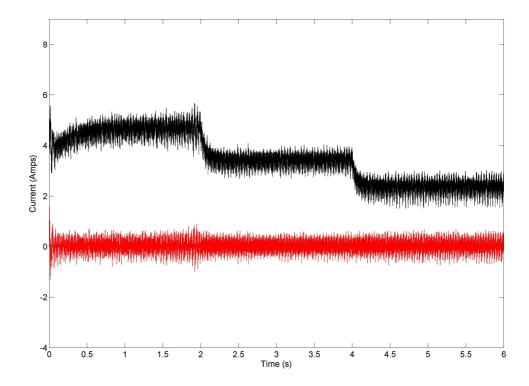

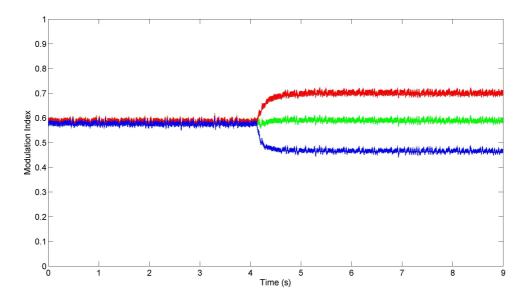

| 5.18 | Variation of $I_q$ (Red) and $I_d$ (Black) under simulation of active rectifier with SHE-MC                                                                                 | 120 |

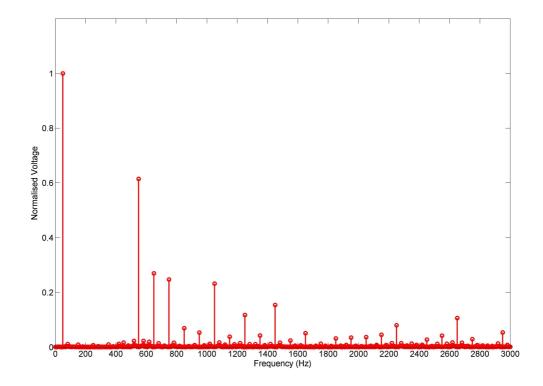

| 5.19 | FFT spectrum for converter voltage under the third imbalance scenario of simulation using SHE-MC                                                                            | 121 |

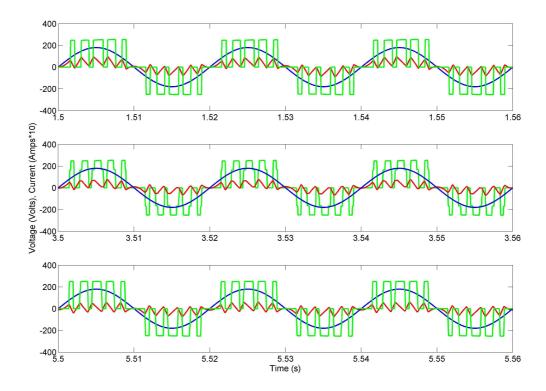

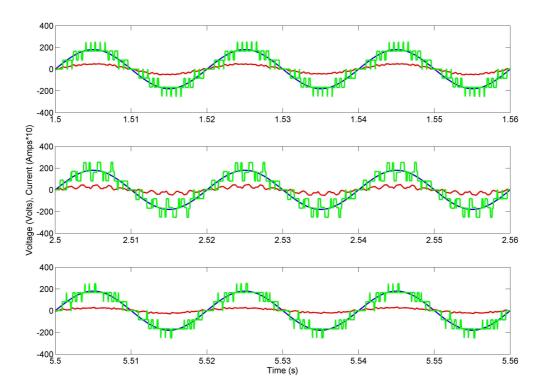

| 5.20 | Converter Voltage (Green), Supply Voltage (Blue) and supply current (Red) for the three imbalance scenarios in steady state using SHE-MC  | 122  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.21 | Balancing of DC link capacitor voltages of active rectifier using SHE-MPC                                                                 | 123  |

| 5.22 | Variation of modulation index to achieve balancing of DC link capacitor voltages using SHE-MPC                                            | 124  |

| 5.23 | Variation of $I_q$ (Red) and $I_d$ (Black) under simulation of active front end with SHE-MPC                                              | 125  |

| 5.24 | FFT spectrum for converter voltage under the third imbalance scenario of simulation using SHE-MPC                                         | 126  |

| 5.25 | Converter Voltage (Green), Supply Voltage (Blue) and supply current (Red) for the three imbalance scenarios in steady state using SHE-MPC | :127 |

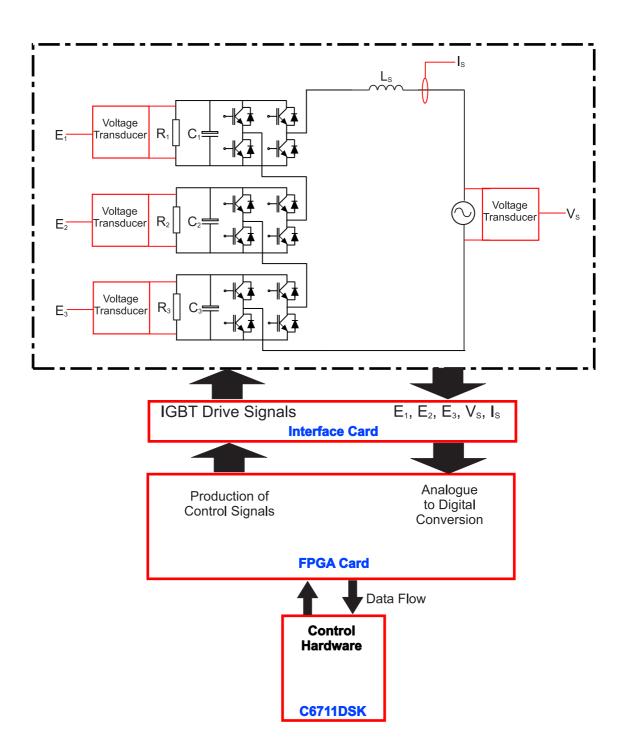

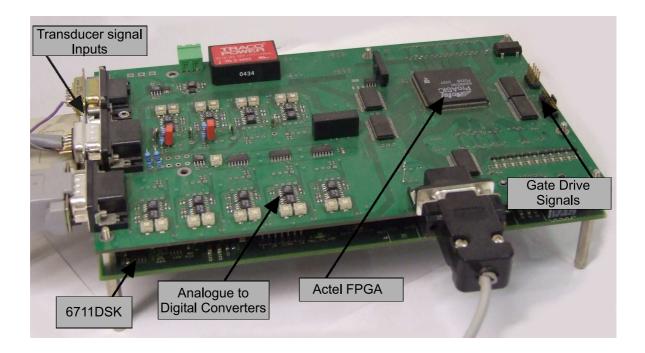

| 6.1  | Block diagram of complete converter                                                                                                       | 130  |

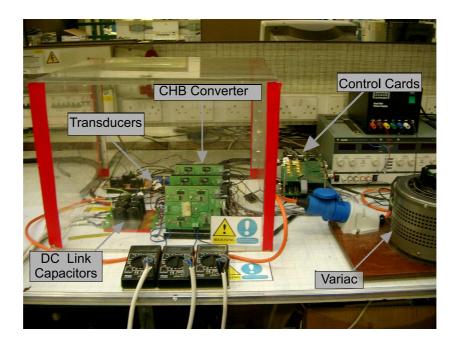

| 6.2  | Photograph of the experimental converter                                                                                                  | 132  |

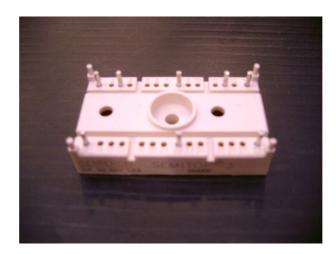

| 6.3  | Photograph of IGBT module used in H-bridge designed during project                                                                        | 133  |

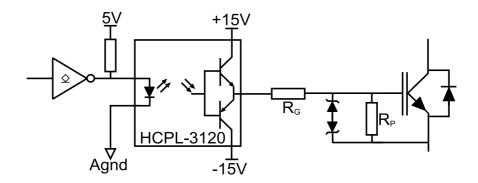

| 6.4  | Gate Drive Design highlighting main components                                                                                            | 135  |

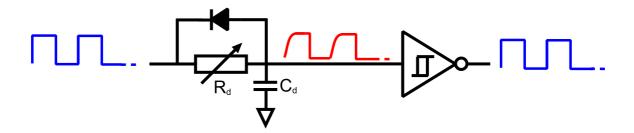

| 6.5  | Analogue deadtime circuit implemented in gate drive design                                                                                | 135  |

| 6.6  | Photograph of the H-bridge circuit board                                                                                                  | 136  |

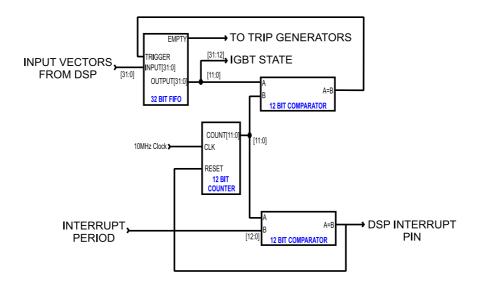

| 6.7  | Simplified block diagram of modulation controller designed for FPGA                                                                       | 138  |

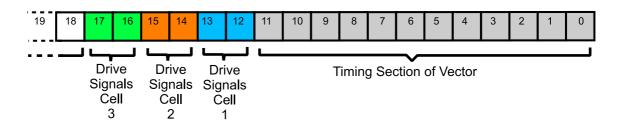

| 6.8  | Diagram showing the 32 bits of the event register used for processing the modulation data                                                 | 138  |

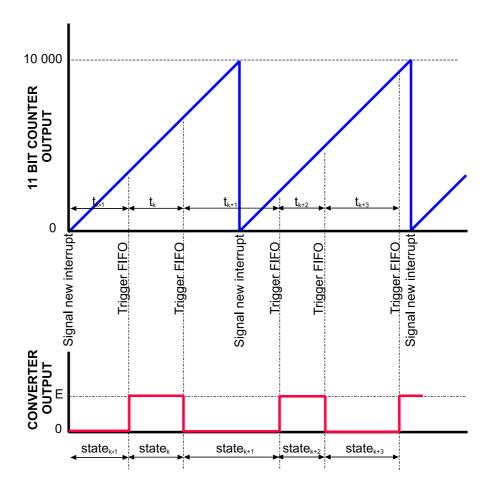

| 6.9  | Example of two periods of the interrupt, showing the use of the timing vector and control waveform generation                      | 139   |

|------|------------------------------------------------------------------------------------------------------------------------------------|-------|

| 6.10 | FPGA and 6711DSK control boards                                                                                                    | 141   |

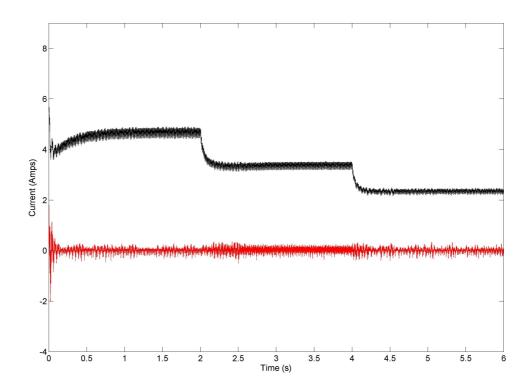

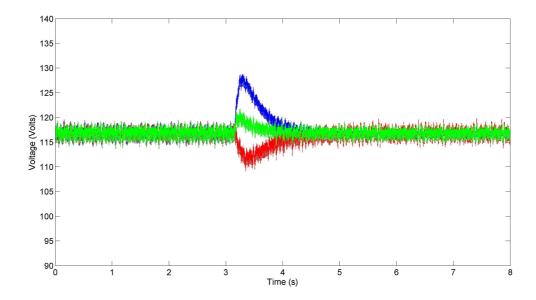

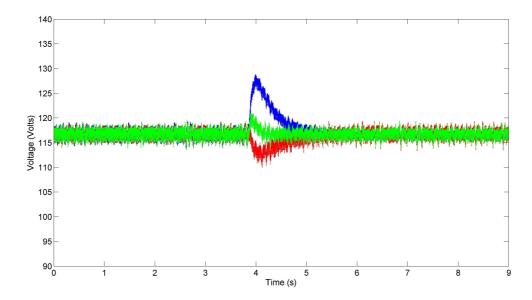

| 7.1  | $\operatorname{DC}$ voltage transient during imbalance using SHE-MC modulation                                                     | 144   |

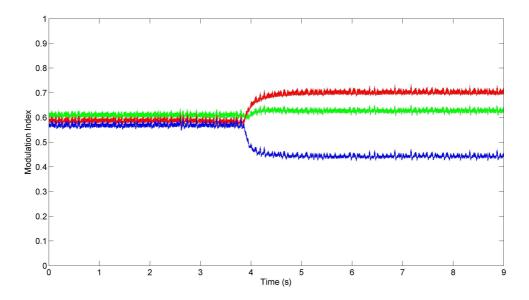

| 7.2  | Modulation Index variation during imbalance using SHE-MC modulation                                                                | n 145 |

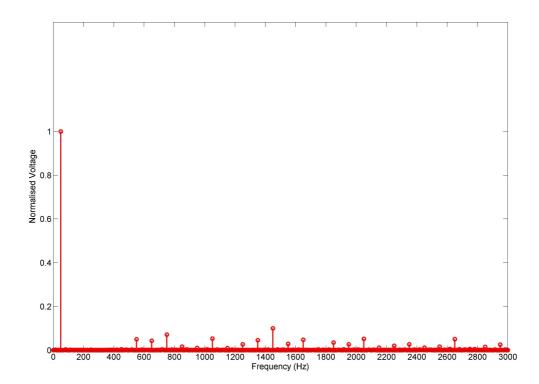

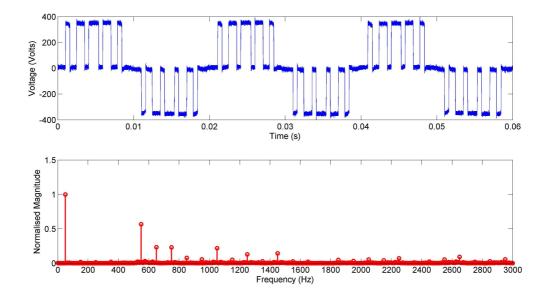

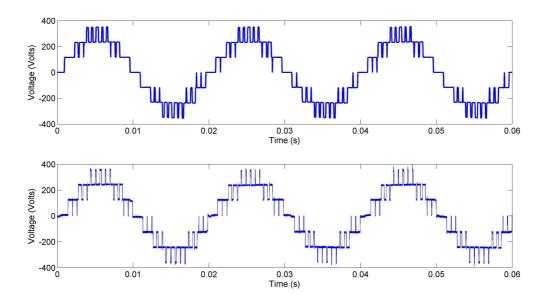

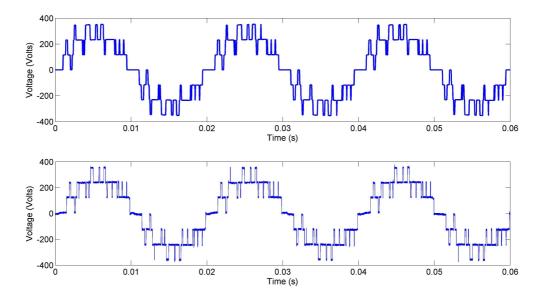

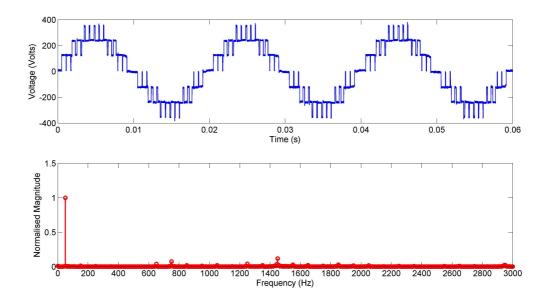

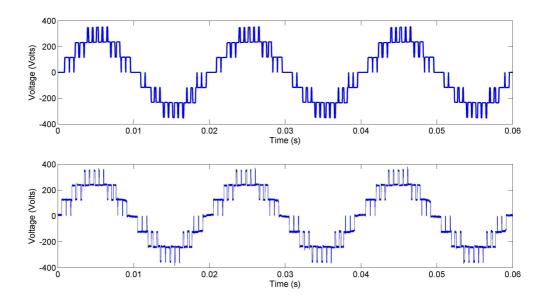

| 7.3  | Steady state converter voltage and FFT spectrum under balanced loads using SHE-MC                                                  | 146   |

| 7.4  | Steady state converter voltage and FFT spectrum under imbalanced loads using SHE-MC                                                | 146   |

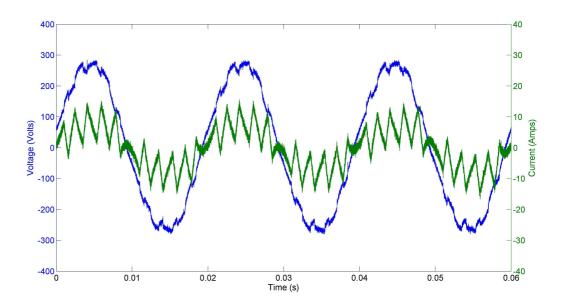

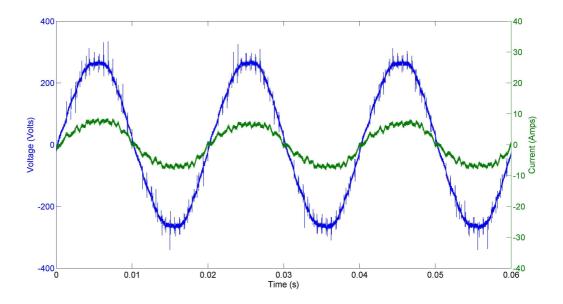

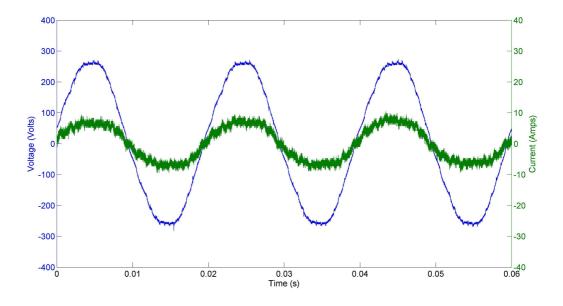

| 7.5  | Steady state supply voltage and current under balanced loads using SHE-MC                                                          | 147   |

| 7.6  | Steady state supply voltage and current under imbalanced loads using SHE-MC                                                        | 147   |

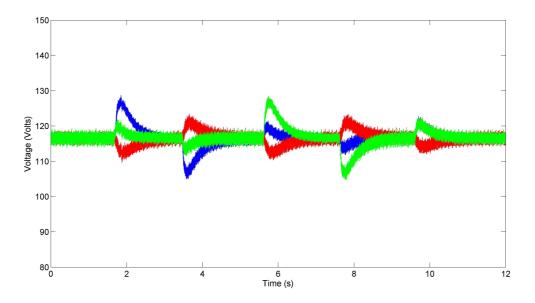

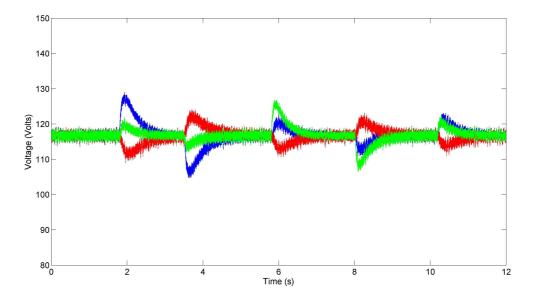

| 7.7  | DC link capacitor voltage response for three cells in response to several step load changes (balanced and unbalanced) using SHE-MC | 148   |

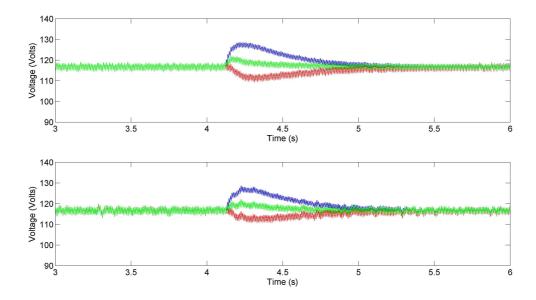

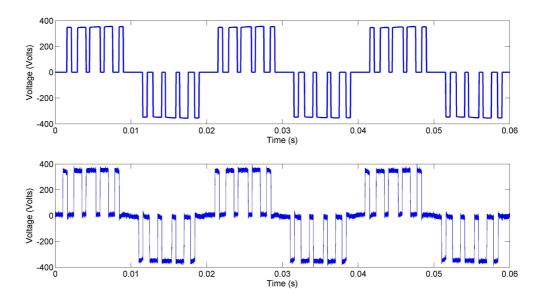

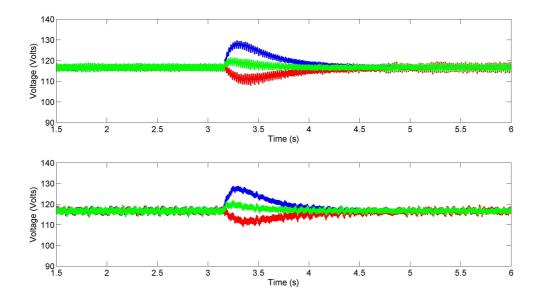

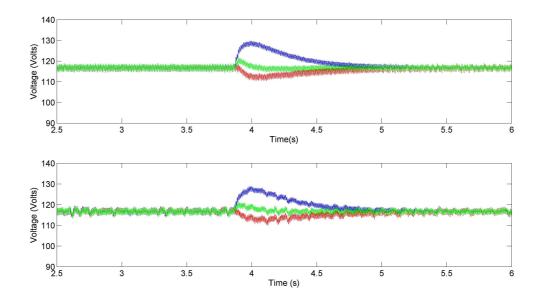

| 7.8  | Comparison of simulated (Top) and Experimental (Bottom) DC Link voltage balancing transient using SHE-MC                           | 149   |

| 7.9  | Comparison of simulated (Top) and Experimental (Bottom) converter voltage under balanced loads                                     | 150   |

| 7.10 | Comparison of simulated (Top) and Experimental (Bottom) converter voltage under imbalanced loads                                   | 150   |

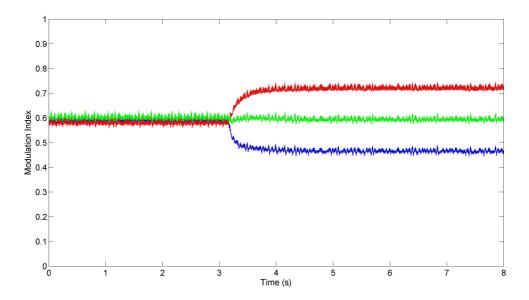

| 7.11 | DC voltage transient during imbalance using SHE-MPC modulation .                                                                   | 152   |

| 7.12 | Modulation Index variation during imbalance using SHE-MPC modulation                                                                      | 153 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

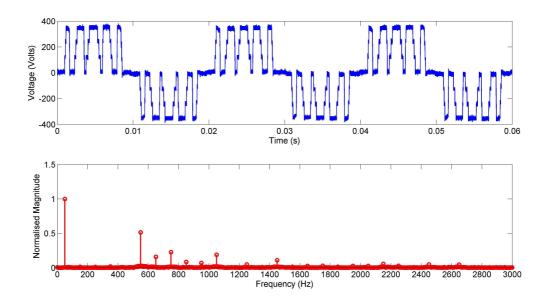

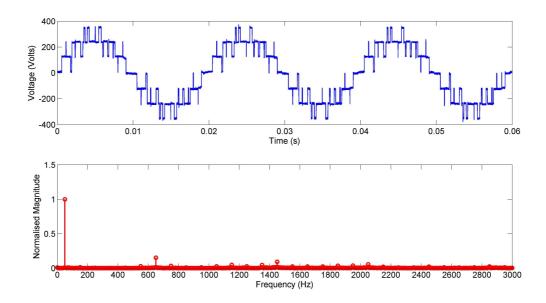

| 7.13 | Steady state converter voltage and FFT spectrum under balanced loads using SHE-MPC                                                        | 154 |

| 7.14 | Steady state converter voltage and FFT spectrum under imbalanced loads using SHE-MPC                                                      | 154 |

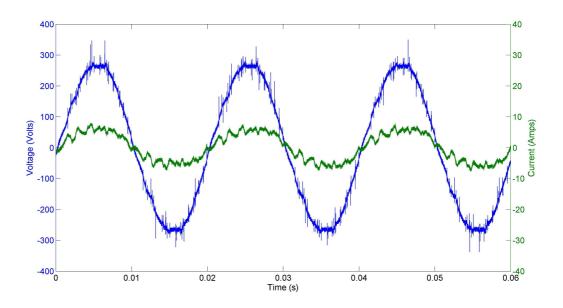

| 7.15 | Steady state supply voltage and current under balanced loads using SHE-MPC                                                                | 155 |

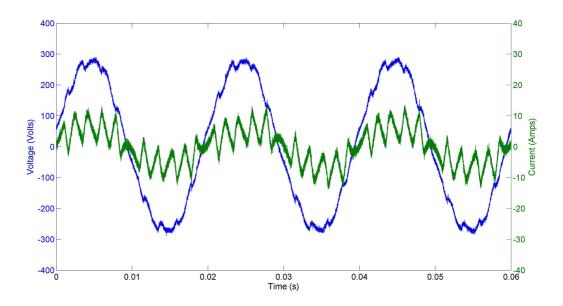

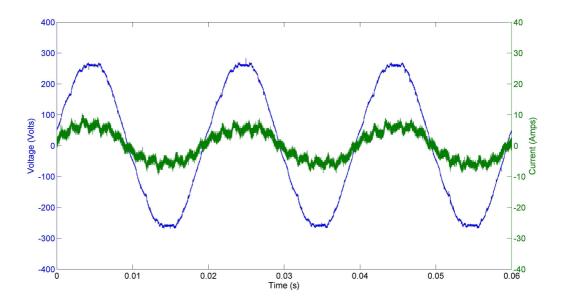

| 7.16 | Steady state supply voltage and current under imbalanced loads using SHE-MPC                                                              | 155 |

| 7.17 | DC link capacitor voltage response for three cells in response to several step load changes (balanced and unbalanced)<br>using SHE-MPC $$ | 156 |

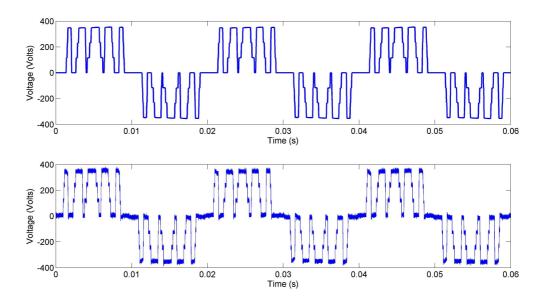

| 7.18 | Comparison of simulated (Top) and Experimental (Bottom) DC Link voltage balancing transient using SHE-MPC                                 | 157 |

| 7.19 | Comparison of simulated (Top) and Experimental (Bottom) converter voltage under balanced loads using SHE-MPC                              | 157 |

| 7.20 | Comparison of simulated (Top) and Experimental (Bottom) converter voltage under imbalanced loads using SHE-MPC                            | 158 |

| 7.21 | DC voltage transient during imbalance using SHE-MPC reduced calculations modulation                                                       | 159 |

| 7.22 | Modulation Index variation during imbalance using SHE-MPC reduced calculations modulation                                                 | 160 |

| 7.23 | steady state converter voltage and FFT spectrum under balanced loads using SHE-MPC reduced calculations method                                                 | 161   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7.24 | Steady state converter voltage and FFT spectrum under imbalanced loads using SHE-MPC reduced calculations method                                               | 161   |

| 7.25 | Steady state supply voltage and current under balanced loads using SHE-MPC reduced calculations method                                                         | 162   |

| 7.26 | Steady state supply voltage and current under imbalanced loads using SHE-MPC reduced calculations method                                                       | 162   |

| 7.27 | DC link capacitor voltage response for three cells in response to several step load changes (balanced and unbalanced)using SHE-MPC reduced calculations method | 163   |

| 7.28 | Comparison of simulated (Top) and Experimental (Bottom) DC Link voltage balancing transient using SHE-MPC reduced calculations method                          | d 164 |

| 7.29 | Comparison of simulated (Top) and Experimental (Bottom) converter voltage under balanced loads using SHE-MPC reduced calculations method                       | 164   |

| 7.30 | Comparison of simulated (Top) and Experimental (Bottom) converter voltage under imbalanced loads using SHE-MPC reduced calculations method                     | 165   |

| A.1  | Phasor diagram used for derivation of modulation index at an operating point                                                                                   | 184   |

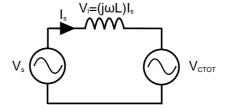

| C.1  | Representation of AC side connection of supply voltage to converter voltage via line inductance                                                                | 188   |

## List of Tables

| 2.1 | Comparison of components required per phase for each of the three Multilevel topologies                                                     | 17 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Breakdown of individual and total harmonic content of 150Hz SHE scheme                                                                      | 43 |

| 3.2 | Individual and total harmonic content SHE-MC with $\pm 10\%$ imbalance at average modulation index of 0.7                                   | 50 |

| 3.3 | Individual and total harmonic content SHE-MC without power imbalance at average modulation index of 0.7                                     | 50 |

| 3.4 | Individual and total harmonic content SHE-MC with $\pm 10\%$ imbalance at average modulation index of 0.4                                   | 51 |

| 3.5 | Individual and total harmonic content SHE-MC without power imbalance at average modulation index of 0.4                                     | 51 |

| 3.6 | Individual and total harmonic content SHE-MC with $\pm 10\%$ imbalance at average modulation index of 0.7 with triplen harmonics eliminated | 55 |

LIST OF TABLES

| 3.7 | Individual and total harmonic content SHE-MC without power imbalance at average modulation index of 0.7 with triplen harmonics eliminated   | 55  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.8 | Individual and total harmonic content SHE-MC with $\pm 10\%$ imbalance at average modulation index of 0.4 with triplen harmonics eliminated | 56  |

| 3.9 | Individual and total harmonic content SHE-MC without power imbalance at average modulation index of 0.4 with triplen harmonics eliminated   | 56  |

| 4.1 | Configuration of DC side loads for simulation of balancing controllers                                                                      | 81  |

| 4.2 | Configuration of converter for derivation of balancing limits for a cell                                                                    | 95  |

| 5.1 | Chosen parameters for seven level CHB converter operating point $$ . $$                                                                     | 99  |

| 5.2 | Main Parameters for simulation of active rectifier                                                                                          | 117 |

| 7.1 | Configuration of DC side loads for experimental verification of simulation work                                                             | 143 |

| 7.2 | Configuration of DC side loads for several imbalances                                                                                       | 148 |

### Chapter 1

### Introduction

The design of modern electricity grid systems is driven by requirements of high efficiency, high reliability and low environmental impact. In an effort to achieve these goals there is an increasing need for renewable energy sources to be integrated into the existing electricity grid. Incorporation of renewable energy systems into the grid requires changes to be made to ensure that the full potential of these systems can be realised whilst still meeting the energy needs of the customers using the grid [1].

Currently the electricity grid consists of a range of generation facilities using fossil fuels, nuclear fuels and hydroelectric energy as well as some small scale renewable sources such as photovoltaic and wind farms [2]. The larger scale generation facilities outputs are then stepped up in voltage ( $\geq 230kV$ ) for transmission over long distances. This step up in voltages reduces the losses caused by current flow along real, non-ideal transmission lines. Once at the required distribution area, the voltage is stepped down in stages until the required level is achieved at the customer connection points. This may be at Medium Voltage levels (1kV-35kV) for some industries and commercial environments or low voltage ( $\approx 400V$ ) levels for residential areas or office buildings. This concept is shown in figure 1.1.

Generation is usually carried out remotely in an effort to avoid pollution of heavily

Figure 1.1: Diagram showing functionality of a classical electricity grid system

populated areas or, in the case of hydroelectric, because the facility needs to be close to water. Power flow in such a system is generally one way, from the interlinked transmission systems that form the high voltage grid to the point where the customers connect to the grid at the local distribution level [3].

Distributed Generation is a term used to describe a system whereby this large transmission system is supplemented by many smaller generation units which are situated in the distribution network, as shown in figure 1.2. Customers are supplied locally and when the local generation is higher than the demand, energy can be transferred to the main network for other customers to utilise, therefore leading to bidirectional power flow [4][5][6].

Renewable energy systems can be incorporated into these small local distribution networks to ensure less reliance on fossil fuels and reduce transmission losses [7][8].

Figure 1.2: Diagram showing functionality of a Distributed Generation electricity grid system

Most of the renewable energy systems currently available require power electronics to be able to interface to the grid [9]. This may be to convert DC to AC or to control power flow from the source into energy storage, such as fuel cells, for use at another time. Amongst the power electronic converters being developed for these applications, multilevel converters have received a lot of interest. Multilevel converters consist of multiple semiconductor switches and energy storage components, interconnected to produce high quality waveforms at high voltages without using high voltage devices [10]. A lot of research has been carried out into these converters in recent years and several development projects have emerged.

UNIFLEX (Advanced Power Converters for <u>Universal</u> and <u>Flexible Power Management in Future Electricity Networks)</u> is such a project and has been funded by the European Community. The project has eight main partners consisting of several EU

universities and manufacturers of components suitable for these applications.

The main aim of the UNIFLEX project is to research advanced converter configurations for flexible power system management. One such converter is connected with the "Solid State Transformer" concept where a power electronics replacement for a distribution level transformer has been conceived [11]. Some of the advantages of using such power converters are:

- Direct connection of renewable energy into the grid systems.

- Connection between asynchronous grids can be made without a HVDC (High Voltage Direct Current) link or complicated transformer arrangement.

- Correction of voltage imbalances can be made to ensure that imbalances do not propagate through the electricity grid.

- Correction of power factor can be achieved.

- Stepping up/down of voltage is still available as with a regular transformer.

- Correction of harmonics to ensure that they do not flow between the ports of the converter.

The converter structure being researched to achieve this functionality is shown in figure 1.3. This structure is multicellular in nature and takes advantage of the Cascaded H-Bridge Multilevel converter, consisting of several H-Bridges connected in series each with its own DC link capacitor for energy storage. The DC/DC stages provide isolation using medium frequency transformers and are capable of bi-directional power flow.

Power flow between each grid system and the converter can be controlled. The converter can also be connected to a lower voltage grid system or to energy storage systems.

Figure 1.3: The UNIFLEX converter structure for three port power flow

Such a converter can only operate correctly when the overall power flow control through the converter is controlled. The distributed energy storage components (i.e. the DC Link Capacitors) must be controlled to ensure that a balanced voltage level is achieved throughout the converter so that the AC voltages produced are optimal and that voltage stress is evenly distributed [12][13].

Another challenge with this type of converter can be selecting a modulation strategy which is capable of producing good quality waveforms with minimum filtering and a low switching frequency. The low switching frequency of the devices is important since for a high power converter the switching losses of the power semiconductor devices will contribute significantly to power losses in the converter, therefore reducing its efficiency [14].

This thesis looks at the application of the Selective Harmonic Elimination (SHE) modulation strategy in an effort to achieve these goals. SHE is a pre-programmed modulation strategy. The location of the switching points on the waveform are calculated to ensure that the required fundamental component is achieved without producing certain low order harmonics. In this way, high quality waveforms can be achieved with relatively low switching frequencies.

The objectives of this thesis are:

- To evaluate the current research into SHE and other types of modulation strategies, in an effort to clearly show the advantages of applying such a modulation strategy.

- To evaluate SHE modulation and its application at a low device switching frequency to address balancing and harmonic distortion issues.

- Research a balancing control scheme which may be used in conjunction with SHE to control the balancing of DC link capacitor voltages in a Cascaded H-Bridge (CHB) converter.

- To simulate a seven level CHB active rectifier to investigate the chosen methods.

• To construct a seven level CHB converter to validate the simulation results.

#### 1.0.1 Thesis plan

Chapter two provides an overview of the main topologies of multilevel converters and evaluates the relative advantages and disadvantages of each topology. An overview of different modulation strategies for CHB converters is then given.

Chapter three presents methods whereby SHE can be applied to capacitor voltage balancing control. Three methods are presented, one which attempts the use of a SHE multilevel waveform in order to gain the best possible harmonic reduction. The other two methods are based on decoupling the H-Bridges control in an effort to reduce the complexity of the balancing control.

Chapter four presents the design of a PI controller based DC link capacitor voltage balancing scheme. The method is based around a system implemented at the end of a nested loop active rectifier control system. Simulation of the balancing system using the SHE methods presented in chapter three are made and a comparison with another modulation scheme using the same balancing method is presented.

Chapter five presents the simulation of the seven level CHB active rectifier and how the system has been designed. Results of DC link capacitor voltage control, closed loop current control and balancing control are presented as well as simulation results of the overall system.

Chapter six presents details for the prototype converter design and construction. The design of the key parts of this converter are given. Implementation of the modulation scheme on a DSP/FPGA platform is explained.

Chapter seven presents the experimental results obtained during experimental verification of the chosen control schemes. Evaluation of the schemes in terms of voltage distortion levels and other comparisons are presented. Chapter eight gives the conclusions for the work as a whole and is followed by several appendices containing information on the derivation of controllers and associated analysis.

### Chapter 2

### Overview of Multilevel Technology

#### 2.1 Introduction

This chapter presents a review of Multilevel Converter technology. The chapter begins with a general introduction to Multilevel converters detailing the main topologies used in high power systems. Pulse Width Modulation schemes for the Cascaded H-Bridge converter are then presented, including the advantages and disadvantages of each strategy.

### 2.2 Multilevel Converters

The concept of a converter with the ability to switch between several magnitudes of DC source (current/voltage) evolved in the 1970's [15]. Unfortunately, due to constraints in switching power devices, they did not receive much attention until the late 1980's, when these constraints became less of a problem.

The basic idea of a multilevel converter is to synthesize high quality AC waveforms from several DC sources via a number of interconnected solid state switches as shown

Figure 2.1: General concept of a Multilevel voltage converter

in Figure 2.1. As can be seen here, any DC source or combination of DC sources can be connected between the output node and the reference point. This means that waveforms can be produced by controlling the connection of these DC levels to the output by using a suitable modulation strategy.

Some advantages of multilevel converters over other topologies are:

- More steps in output voltage waveforms

- Lower distortion of AC current waveform

- Reduction of switching frequency and associated losses.

The first point here is a clear result of applying a high voltage in several multilevel steps rather than in a single large one. This may reduce some of the effects associated with switching converters such as reflections on long load cables [16].

Since there are several steps in the converter waveform it more accurately portrays the AC reference waveform. This means that lower harmonic distortion can be achieved for a given switching frequency.

2.2. MULTILEVEL CONVERTERS

These features are why these topologies are popular in high power applications. It

12

is clear that multilevel converters can be used at high voltage levels by sharing the

voltage amongst several stages. As a result of increasing the number of levels, device

switching frequencies can be reduced without compromising the quality of output

voltage waveform. This may result in lower switching losses which is important in

high power applications [17].

Multilevel converters are already popular in Medium Voltage motor drive applications

and are being considered for grid applications such as static VAR compensation and

active filtering applications as well as grid control solutions, such as the "Solid State

Transformer" mentioned in the Chapter 1 [18][19][20].

Although many possible topologies exist, they are all related to three main types of

Multilevel Converter [21]. These topologies receive the greatest attention and are

therefore reviewed in this chapter.

• Neutral point Clamped Multilevel Converter

• Flying Capacitor Multilevel Converter

• Cascaded H-Bridge Multilevel Converter.

2.2.1 Neutral Point Clamped Multilevel Converter

The topology presented in figure 2.2 is a Neutral Point Clamped or Diode Clamped,

three-level converter [22]. This converter uses diodes to split the DC link voltage

into sub-levels. Using the single leg shown in figure 2.2 as a reference, three output

voltage levels can be defined with respect to the neutral point of the DC link capacitor

voltage (N):

$AB\overline{CD}: V_o = E/2$

$\overline{AB}CD: V_o = -E/2$

$\overline{A}BC\overline{D}: V_o = 0.$

Figure 2.2: Three Level Neutral Point Clamped converter

The number of levels in this converter can be increased by increasing the number of clamping points in the total DC link capacitor "stack" and the number of switching devices between these points. As the number of levels in the converter is increased it becomes apparent that the same voltage state can be achieved across the phases by using several different combinations of switches. When an output is repeatable using several different states it is said to have redundancy. This redundancy in states plays a vital role in ensuring that the semiconductors share switching loss in the converter and that the DC storage components share power utilisation.

Unfortunately selection of the best state to use to ensure sharing of power and losses becomes complicated and calculation intensive for a converter above five levels and controlling the balance of voltage among all the storage components in this converter can present a significant challenge [17].

Another disadvantage of this topology is that the clamping diodes used may have to block high voltages. This may require connecting several diodes in series which increases the component count and power losses in the converter.

## 2.2.2 'Flying' Capacitor Multilevel Converter

A three level 'Flying' Capacitor circuit is shown in Figure 2.3. The converter, in a similar way to the Diode Clamped converter, is controlled by applying switching states to each leg to achieve the required output voltage level. The switching states are similar to the diode clamped topology with respect to the neutral point of the DC link capacitor voltage(N):

$AB\overline{CD}: V_o = E/2$   $\overline{AB}CD: V_o = -E/2$   $\overline{AB}\overline{C}D: V_o = 0$   $A\overline{B}C\overline{D}: V_o = 0.$

Figure 2.3: Three Level 'Flying' Capacitor Multilevel Converter

Redundant switch configurations in this converter topology can again be used to distribute losses throughout the switching devices. There is a large number of bulky energy storage capacitors in this topology, which result in an increase in the converter size as the number of levels increases [23].

15

Another problem with this converter is that pre-charge and maintaining of the capacitor voltages is essential. This usually involves the use of additional circuitry, which adds to the component count of the converter.

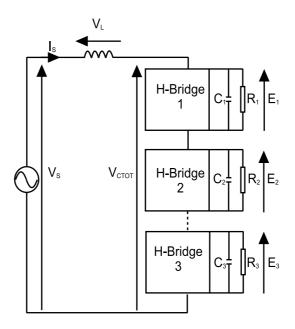

## 2.2.3 Cascaded H-Bridge Multilevel Converter

The Cascaded H-Bridge (CHB) multilevel topology is shown in Figure 2.4. The converter, as the name suggests, consists of a number of H-bridge converter cells which are series connected into a cascade. The operation of a single three level H-bridge consists of four switching states. With reference to figure 2.4 for a single H-bridge cell these states are:

$$A\overline{BC}D : V_o = E/2$$

$$\overline{ABCD} : V_o = -E/2$$

$$A\overline{BCD} : V_o = 0$$

$$\overline{ABCD} : V_o = 0.$$

With this in mind, cascading two H-Bridge cells in series, as shown in the figure 2.4, results in the voltage levels E, E/2, 0, -E/2, -E (i.e. a five level converter). This relationship is explained more generally in equation (2.1), where N is the number of H-bridges connected per phase in the converter structure and it is assumed that each DC source is equal. For example, a converter consisting of seven H-Bridges per phase is capable of producing fifteen levels per phase at the output.

Number of levels in output =

$$2N + 1$$

, (2.1)

This converter topology can have redundant cells built into its structure. This is due to the fact that the AC output terminals of each H-Bridge can be set to produce zero volts, and with the addition of another switch the AC output can also be bypassed.

Figure 2.4: Five Level Cascaded H-Bridge Multilevel Converter

It is then possible to use this redundant bridge if another bridge in the cascade has failed. This feature can be very useful for applications requiring some form of fault ride through capability [24].

It is important that power is drawn equally from each of the H-Bridge cells of the converter. This can be achieved as part of the control or modulation scheme for the converter [25]. One such example is the use of Phase Shifted Carrier modulation (see section 2.3.2). Power flow control is arguably easier on this topology when compared to the other two types since it is possible to control the cells of the CHB almost independently.

One disadvantage with such a converter is the requirement of isolation between the DC sources. This usually leads to the application of bulky phase shifting isolation transformers. These transformers may possibly be used to decrease the harmonic distortion of the supply current into the CHB converter. It is important to note that this harmonic cancellation is only achieved when the power drawn from the cells is

Table 2.1: Comparison of components required per phase for each of the three Multilevel topologies

| 1 0                  |             |               |         |

|----------------------|-------------|---------------|---------|

| Topology             | NPC         | FCC           | СНВ     |

| Switching Devices    | (M-1)*2     | (M-1)*2       | (M-1)*2 |

| Diodes               | (M-1)*2     | (M-1)*2       | (M-1)*2 |

| Clamping Diodes      | (M-1)*(M-2) | 0             | 0       |

| DC Bus Capacitors    | (M-1)       | (M-1)         | (M-1)/2 |

| Balancing Capacitors | 0           | (M-1)*(M-2)/2 | 0       |

the same [26][27].

## 2.2.4 Comparison of Multilevel topologies

The previous sections have given the relative advantages and disadvantages for the three main types of multilevel converters. A table showing a comparison of the components for each of the multilevel converters discussed in this chapter is shown in table 2.1, where M is reference to the number of levels per phase in the converter.

The requirement of bulky energy storage components in the Flying Capacitor presents the biggest disadvantage in the component count for this topology. The NPC circuit is potentially flawed by its requirement of clamping diodes. This is especially the case when the number of levels is increased since the voltage stress is not equally distributed between the diodes and so series connection may be required. Although the CHB circuit appears the most attractive solution from the components point of view, the reader should recall the requirement for isolated DC sources in such a topology. This could potentially increase the size of the converter significantly.

# 2.3 Modulation methods for the CHB topology

Since the topology discussed in this thesis is a Cascaded H-Bridge topology, it is important to provide an overview of the types of modulation that can be used to produce the output waveforms from such a converter.

Modulation methods for a CHB converter can be split into two types. The first are carrier based methods, where the reference waveform is modulated using a higher frequency carrier. The second are digital methods, including space vector modulation and optimised PWM methods, such as Harmonic Elimination PWM. The following sections present an introduction to these modulation strategies, placing emphasis on Selective Harmonic Elimination, since this is the method applied in this work.

#### 2.3.1 Level shifted Carrier PWM

Level shifted carrier PWM is one of several methods based on naturally sampled PWM. Naturally Sampled PWM converts a modulation waveform into a switching waveform by comparing the modulation waveform with a high frequency carrier. For a CHB converter this can be formed using a separate carrier set for each cell, as shown in figure 2.5. The modulation waveform is compared to each of these carriers and when an intersection occurs with a carrier the H-Bridge associated with that carrier is switched accordingly.

The carriers for level shifted carrier PWM can be placed in several different arrangements. Examples are:

- In Phase disposition (IPD)

- Phase Opposite Disposition (POD)

- Alternate phase opposite disposition (APOD)

Since it has been well documented that IPD gives a better harmonic performance it is the only one considered here [28].

As shown in figure 2.5, the harmonic spectrum of the output waveform is as expected for a naturally sampled system. There is a large 50 Hz fundamental component

Figure 2.5: Seven Level, Level Shifted Carrier Waveforms and associated spectrum

along with groups of harmonics and sidebands at the associated carrier waveform frequencies (in this case at 1050Hz).

The device switching frequency for this modulation method is not always evenly distributed amongst the cells of the converter. This results in an uneven distribution of losses between the cells. Another problem which should be noted is that the conduction times for the three cells are not equal, since the cell being switched into the lowest carriers will have a significantly larger conduction time than the other two cells. The worst case is when the modulation waveform is small enough to require the switching of only one cell. In this case a very large imbalance in power flow through the cells is evident and if the DC sources were for example batteries, this cell battery would discharge much faster than the others.

This problem may be alleviated using conduction block swapping schemes whereby at the start of each cycle the carrier position for each cell is swapped so that the conduction blocks over several cycles will be the same and the power flow and switching losses will be distributed evenly throughout the converter [29].

### 2.3.2 Phase Shifted Carrier PWM

Phase shifted carrier PWM attempts to alleviate the natural unbalance problems associated with the previous method by using the same modulation wave for all the cells in the converter [30]. In this case several carriers are utilised, each phase shifted with respect to each other according to the relationship shown in equation (2.2). In equation (2.2)  $\phi$  is the carrier phase angle and N is the number of cells per phase in the converter.

$$\phi = \frac{180^{\circ}}{N} \tag{2.2}$$

A PWM scheme with a 250Hz switching frequency is shown in figure 2.6 for a seven level converter. The conduction times for each cell in a cycle is approximately equal. Furthermore, the modulation scheme naturally balances power flow through the cells of the converter. Another advantage of this scheme is that the device switching frequency of each cell is identical and equal to the carrier frequency of 250Hz. Therefore, there is no requirement for a cell swapping scheme to be used to ensure that power flow for each cell is equal.

## 2.3.3 Selective Harmonic Elimination (SHE)

Selective Harmonic Elimination (SHE) is a pre-programmed PWM method. The switching points must be calculated offline for a range of modulation indices and stored in a lookup table for use by the converter modulation.

Figure 2.6: Seven Level, Phase shifted Carrier Waveform and FFT,  $f_{sw}$ =250Hz

SHE theory is derived from Fourier analysis of a square wave which has several switching points per period. From this theory it is possible to determine that for a converter output voltage with M switching points per quarter cycle, M degrees of freedom are available for manipulation in the waveform. These degrees of freedom can be manipulated to ensure that a fundamental voltage component can be achieved without producing (M-1) harmonics [31][32].

These degrees of freedom are utilised by forming a set of equations to determine when the switching points should occur in the AC waveform. Unfortunately, the equations formed are nonlinear and transcendental in nature and so must be solved using programmed mathematical methods. Since several solutions may be found for each modulation index, a secondary objective function is normally produced. For example, angles may be chosen due to the fact they have the lowest overall harmonic distortion in the waveform, when compared with other possible solutions at the same modulation index.

Selective Harmonic Elimination is derived in detail in Chapter 3 but a short review of its applications are given here. Work given in [33] showed that SHE could be implemented with a staircase modulation scheme working at a switching frequency equal to the converter output voltage fundamental frequency. In this scheme a waveform with seven levels and three switching points per quarter cycle gave three degrees of freedom. One was used to enure that the required fundamental value was achieved in the multilevel waveform whilst the other two were used to ensure that the  $5_{th}$  and  $7_{th}$  harmonics were eliminated. Unfortunately in this case, since the waveform was stepped, there were imbalances in the conduction times for each converter cell. To alleviate this a cell conduction time switching scheme was utilised to ensure balance over several cycles.

A method of producing multilevel SHE was shown in [34] where switching angles for a single H-Bridge were taken and phase shifted for an N level converter to achieve an initial guess for a multilevel set of equations. In this case a multilevel scheme with a 250Hz device switching frequency was achieved and multiple solutions were reduced

by adding a reduced distortion objective function. Due to the imbalance in individual cell conduction blocks a cell swapping scheme was required.

Work shown in [35] attempted to alleviate the requirement of a cell swapping scheme by better utilising the degrees of freedom. In this case each cell of a seven level converter had three degrees of freedom (150Hz device switching frequency), giving a total of nine degrees of freedom. Six of these were used to eliminate the lowest order dominant harmonics whilst the final three were used to ensure that the fundamental component of each cell waveform was equal. This use of the degrees of freedom ensured that for an undistorted current flowing from the converter, the power drawn from each cell would be equal.

Work by [36] used a 250Hz switching frequency scheme in conjunction with extra cells using a high switching frequency to eliminate both lower and higher order harmonics. This results in the production of very high quality waveforms. Disadvantages due to the high switching frequency of this extra cell resulted in an update to this work [37] whereby a lower switching frequency method was used to remove these higher order harmonics.

SHE has also been used in an effort to reduce harmonics rather than eliminate them. In this way an effort can be made to reduce the harmonic content of a waveform in order to ensure that it meets a grid connection codes such as IEEE519 [38] or Engineering Recommendation G5/4 [39]. This was shown in [40] where an effort was made to minimise rather than eliminate certain harmonics to achieve compliance with the harmonic content regulations by reducing, rather than eliminating a higher number of harmonics for a given switching frequency. In this case it was defined as Selective Harmonic Mitigation (SHM).

Figure 2.7: Staircase modulation waveform and spectrum

#### 2.3.4 Staircase Modulation

Staircase modulation is perhaps the simplest of the multilevel converter modulation schemes and works with a device switching frequency equal to the fundamental converter output frequency. To produce the output voltage the reference waveform is compared against n threshold points for an n level converter, as shown in figure 2.7 [41]. Although this scheme is simple it is obvious from this plot that since the output consists of summed quasi-square waves, the spectrum of such a waveform will contain some low order harmonic distortion.

The dominant  $5_{th}$ ,  $7_{th}$  and  $11_{th}$  harmonics cause the biggest problem since they may be difficult to filter. This may result in a requirement for large filtering components which increase the converter loss and size significantly.

A simple way of alleviating these problems is shown in [42]. This scheme uses a simple multilevel harmonic elimination approach on the system to eliminate some of the lower order harmonics. In figure 2.8, this theory is shown for a seven level

Figure 2.8: Application of SHE to staircase modulation

Figure 2.9: Example of swapping scheme use for power balancing in staircase modulation scheme

converter. The three switching angles,  $\theta_1 - \theta_3$ , can be optimised to create the desired fundamental component without producing the undesired  $5_{th}$  and  $7_{th}$  harmonics.

This method also suffers from the same unequal conduction time problem as the Level Shifted Carrier PWM. This can again be alleviated by using a conduction time swapping scheme, as previously mentioned. This swapping of conduction times may lead to extra ripple on the DC side current due to the variation in power flow during the different conduction cycles [41][43].

Figure 2.10: Classical three phase converter

## 2.3.5 Space Vector Modulation

Space Vector Modulation is a type of modulation well suited to microprocessor implementation because the modulation is calculated over each switching period [44].

Traditional Space Vector Modulation (SVM) is best described for the three phase classical inverter shown in figure 2.10. The operation of this inverter is simple with each leg being able to output a voltage of E or zero. There are eight states in such a converter, which are displaced around a hexagon, as shown in figure 2.11. A reference rotating vector moves through this hexagon at the required angular frequency. The nearest states are then used along with the SVM calculations to synthesise the output waveform. P refers to application of E on the chosen phase of the converter and O refers to application of zero for that phase.

The reference is sampled at an arbitrary sampling frequency. At each sampling point the processor calculates the times for the two nearest non-zero states and one or both of the zero states. These values are calculated using the volt-second principle and some trigonometric relationships, i.e. for any point in the first sector equation (2.3) must be obeyed for states  $U_1$ ,  $U_2$  and  $U_0$  or  $U_7$ , along with their respective application times,  $T_1$ ,  $T_2$  and  $T_0$ .

$$V_{ref} * T_s = U_1 * T_1 + U_2 * T_2 + (U_0 or U_7) * T_0$$

(2.3)

Figure 2.11: Two level SVM state diagram

Figure 2.12: Three level SVM state diagram

2.4. SUMMARY

$$T_1 = \left[\frac{\sqrt{3} * T_s * V_{ref}}{E}\right] \sin\left(\frac{\pi}{3} - \theta\right) \tag{2.4}$$

$$T_2 = \left[\frac{\sqrt{3} * T_s * V_{ref}}{E}\right] \sin\left(\theta\right) \tag{2.5}$$

$$T_0 = T_s - T_2 - T_1 \tag{2.6}$$

The output states are switched by the converter for the times calculated in each sampling instant using equations (2.4)-(2.6).

SVM can be extended to a multilevel system by increasing the size of the state diagram as shown for a three level converter in figure 2.12 [45] or by using 3D methods [46]. In this case the output voltage is synthesised by the nearest three states in the triangle that the tip of the reference vector is in. P, O and N refer to application of a positive, zero and negative voltage application for a particular phase.

Due to the high number of states available in this system each output level can be achieved using several different states. These redundant states can be used as part of a balancing scheme where for example, a certain state will be selected over another two redundant ones if the cell which that state switches into conduction requires the available power flow to improve balance.

Space Vector Modulation can also be optimised in an effort to reduce the device switching frequency in the converter. In this case, states are selected so that the minimum number of devices are switched in each switching period of the modulation to ensure that switching losses are potentially minimised [47].

## 2.4 Summary

Multilevel converters provide several possible advantages in their applications such as reduced output harmonic spectrum, reduced switching frequency and suitability for high power applications. These advantages make them ideal for grid applications 2.4. SUMMARY

where reduced switching frequency and high power rating is important. The CHB converter is especially advantageous in these applications due to its modular structure and ease of control with a higher number of levels.

Several switching strategies are available for CHB converters, each with their own unique behaviour. Level shifted carrier modulation is easy to implement and has good harmonic performance. However, it suffers from a natural power imbalance behaviour due to uneven conduction times. Staircase modulation works at a low switching frequency and can be applied with SHE to reduce some of the lower harmonics present in the waveforms. Unfortunately the conduction times for each cell are unequal and so power flow through these cells are also unequal. Phase shifted carrier has inherently balanced fundamental power flow through the cells by using phase shifting in the carrier waveforms and identical modulating waveforms for each cell in the converter. A fixed, low device switching frequency is also obtained.

Space vector modulation is a system optimised for micro-processor implementation. Reduced switching frequency and inherent balancing can be achieved as a result of selecting the best redundant states to achieve these aims.

Selective Harmonic Elimination modulation provides a possible method for reducing the switching frequency without compromising the low frequency harmonic content of the waveform. Degrees of freedom may be manipulated to ensure that power flow from the cells is balanced. Unfortunately, the equations required to find the optimal switching points are transcendental and nonlinear in nature and so solutions require application of advanced mathematical techniques.

# Chapter 3

# SHE-PWM for power flow control

### 3.1 Introduction

This chapter presents three possible SHE methods which can be used to balance the DC link capacitor voltages of a CHB converter. Background information on power balancing in a CHB converter and formulation of SHE waveforms is provided in detail. The method chosen to solve the SHE firing angle equations is presented before examining the three methods used for power flow control using SHE modulation. One of these methods involves the use of multilevel SHE where the converter modulation as a whole is designed to balance the cell powers. The other two methods are based on a decoupled voltage control scheme. The relative advantages and disadvantages of each scheme are presented.

# 3.2 Background to balancing using SHE

Cascaded H-Bridge (CHB) converters consist of a series cascade of several H-Bridge converter cells with DC link capacitors. Whether operated as a rectifier or an inverter,

control of power flow through the converter is of high importance. This is the case whether the voltages of each cell are required to be equal or unbalanced [48].

In the case of an inverter, where power is flowing from the DC side to the AC side, it may be important that the same power is drawn from each energy storage component. This theoretically ensures that each of the energy storage components discharge at the same rate. These energy storage components may for example be batteries or fuel cells.

When the converter is operated as a rectifier with power flowing from the AC side to the DC side, it may be required that all of the DC voltages of the cells are equal. This can be achieved by ensuring that the input powers to each cell match the output powers in steady state, once the required voltage balance is achieved.

The work presented here is applied to a rectifier in an attempt to avoid the requirement of isolated DC sources presented in Chapter 2. It should be noted however that the scheme is directly applicable to the case of an inverter where the power flow from the DC sources to the AC side is being controlled. Operation as a rectifier is now discussed further.

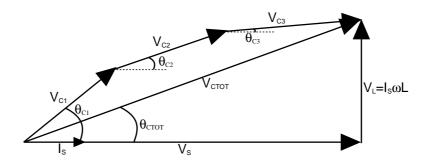

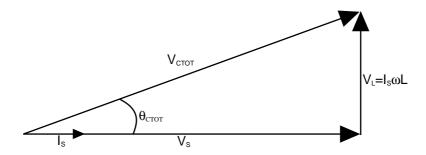

Assuming that the supply current is undistorted and noting that the H-Bridges are series cascaded a simple power flow relationship can be derived. Since the supply current flows through each cell in the converter, the power flowing into the AC side of the cell depends on the fundamental voltage magnitude applied by that cell and the phase shift between the fundamental AC cell voltage and the fundamental component of the supply current. This is shown clearly in figure 3.1 and 3.2 for a seven level converter. It is clear from these diagrams that the powers flowing into each cell are different as determined by the different H-Bridge cell voltage phasor magnitudes and phase shifts from the supply current phasor.

With reference to figures 3.1 and 3.2 the relationships between total converter power and  $n_{th}$  H-Bridge cell power can be defined as in equations (3.1)- (3.2). The  $n_{th}$  cell power  $P_{Cn}$  is a function of the supply current,  $I_s$ , the  $n_{th}$  cell AC voltage magnitude,

Figure 3.1: Diagram showing the power flow relationships for each cell of a seven level CHB converter

Figure 3.2: Phasor diagram of seven level converter manipulating cell phase and voltage magnitude

$V_{Cn}$ , and the phase shift between this voltage and the supply current  $\theta_{Cn}$ . The total converter power,  $P_{CTOT}$ , is a function of the total converter AC voltage,  $V_{CTOT}$ , the supply current,  $I_s$ , and the phase shift between this voltage and the supply current  $\theta_{CTOT}$ . It should be noted that the total converter AC voltage is the sum of the cell AC voltages as shown in equation (3.3).

$$P_{CTOT} = V_{CTOT} * I_s * Cos(\theta_{CTOT})$$

(3.1)

$$P_{Cn} = V_{Cn} * I_s * Cos(\theta_{Cn}) \tag{3.2}$$

$$V_{CTOT} = V_{C1} + V_{C2} + V_{C3} (3.3)$$

The relationships between power, cell voltage magnitude and phase shift mean that it is possible to control the input powers at the AC side of the rectifier to match the output powers in steady state by manipulating these two components. In the case where the loads attached to each converter cell are different, it is possible to match the unbalanced powers on the input side so that in steady state the DC link capacitor voltages of each cell converge.

The methods presented in the rest of this chapter can be used along with a control scheme to control the power flow of the cells in the CHB converter. The methods involve the use of two different types of SHE waveform and a combination of both cell phase and magnitude control to ensure that the power requirements for cell voltage balance are fulfilled.