## Thermal Management of Solid State Power Switches

Christopher James Frederick Tighe

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy  ${\sf June}\ 2011$

School of Mechanical, Materials and Manufacturing Engineering

University of Nottingham, Nottingham, UK

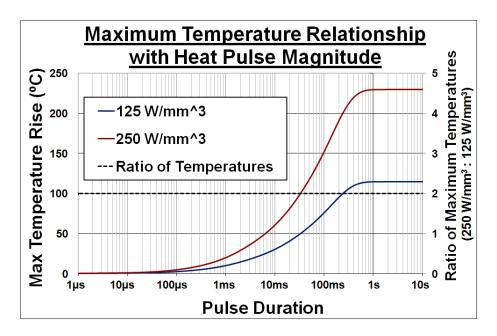

## **Abstract**

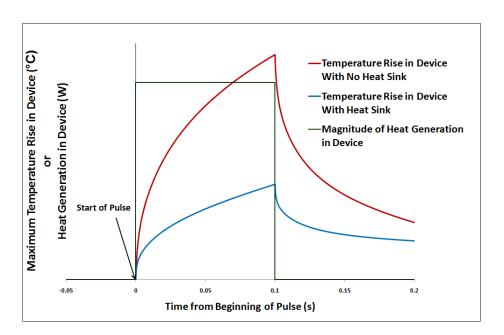

The transient temperature of solid state power switches is investigated using thermal resistance network modelling and experimental testing. The ability of a heat sink mounted to the top of the device to reduce the transient temperature is assessed. Transient temperatures for heat pulses of up to 100ms are of most interest.

The transient temperature distribution inside a typical stack-up of a solid state power switch is characterised. The thermal effects of adding a heat sink to the top of the device are then assessed. A variety of heat sink thicknesses and materials are evaluated. Components of the device stack-up are varied in order to assess their affect on the effectiveness of the heat sink in reducing the device temperature.

Thermal networks are successfully applied to model the transient heat conduction inside the stack-ups. This modelling technique allowed a good understanding of the thermal behaviour inside the stack-up and heat sink during the transient period. The concept of using a heat sink to suppress the transient temperature was validated experimentally on two types of solid state power switch.

## Acknowledgements

I would like to thank my supervisor Dr. Stephen Pickering for his valuable guidance, encouragement and patience during my PhD. Without his support and knowledge the PhD would not have been possible. Thanks also goes to Professor Mark Johnson, whose knowledge and help proved important.

A further thanks goes to Dr. Pearl Agyakwa, whose technical skills and willingness to help is very much appreciated. The technical help received from Paul Evans must also be mentioned.

The financial support provided by the EPSRC and the industry sponsors, GE Aerospace, is kindly acknowledged.

A special thanks goes to all my friends and colleagues I have met during my years at the University of Nottingham, who have made my time as a student enjoyable and memorable.

Lastly, I would like to thank my family, in particular my parents, Brian and Janet, who have whole-heartedly supported me in everything I have done. Without your encouragement and support I would not have been able to achieve what I have.

## Contents

| 1 | Intro | oduction                                            | 1  |

|---|-------|-----------------------------------------------------|----|

|   | 1.1   | Problem Definition                                  | 2  |

|   | 1.2   | Objectives                                          | 4  |

|   | 1.3   | Thesis Structure                                    | 5  |

| 2 | Ove   | rview of Power Electronic Devices and Heat Transfer | 7  |

|   | 2.1   | Power Electronics Overview                          | 8  |

|   |       | 2.1.1 Breakdown Voltage and Avalanche Breakdown     | 8  |

|   | 2.2   | Power Devices                                       | 10 |

|   |       | 2.2.1 Power Diodes                                  | 10 |

|   |       | 2.2.2 MOSFETs                                       | 11 |

|   |       | 2.2.3 IGBTs                                         | 13 |

|   | 2.3   | Heat Generation in Power Electronic Devices         | 15 |

|   |       | 2.3.1 MOSFETs and IGBTs                             | 15 |

|   | 2 4   | Device Failure Mechanisms                           | 18 |

|   | 2.5  | Heat (   | Conduction Theory                        | 9 |

|---|------|----------|------------------------------------------|---|

|   |      | 2.5.1    | Heat Conduction Equation                 | 9 |

|   |      | 2.5.2    | Thermal Diffusivity                      | 1 |

|   | 2.6  | Transie  | ent Heat Conduction                      | 2 |

|   |      | 2.6.1    | Unidirectional Transient Heat Conduction | 2 |

|   |      | 2.6.2    | Fourier Number                           | 8 |

|   | 2.7  | Chapte   | er Conclusion                            | 4 |

| 3 | Lite | rature ( | Overview 3                               | 6 |

|   |      |          |                                          |   |

|   | 3.1  | Coolin   | g Technologies for Semiconductors        | 7 |

|   |      | 3.1.1    | Forced Liquid Convection Techniques      | 8 |

|   |      | 3.1.2    | Double-Sided Chip Cooling                | 4 |

|   |      | 3.1.3    | Thermal Transients                       | 9 |

|   | 3.2  | Model    | ling the Thermal Response of Devices     | 2 |

|   |      | 3.2.1    | Analytical Approaches                    | 2 |

|   |      | 3.2.2    | Developing RC Models                     | 0 |

|   |      | 3.2.3    | Fourier Based Methods 6                  | 9 |

|   |      | 3.2.4    | Review of Modelling Methods              | 4 |

|   | 3.3  | Reliabi  | lity of Semiconductor Devices            | 6 |

|   |      | 3.3.1    | Solder Joint Integrity                   | 6 |

|   |      | 3.3.2    | Substrate Technologies                   | 7 |

|   |     | 3.3.3   | Predictive Modelling of Semiconductor Reliability            | . 89  |

|---|-----|---------|--------------------------------------------------------------|-------|

|   | 3.4 | Compo   | osite Materials and Solder Alternatives                      | . 91  |

|   |     | 3.4.1   | Thermal Management Materials                                 | . 91  |

|   |     | 3.4.2   | Novel Solders and Solder Alternatives                        | . 94  |

|   | 3.5 | Chapte  | er Conclusion                                                | . 96  |

| 4 | Mod | delling | Heat Conduction                                              | 98    |

|   | 4.1 | Analyt  | cical Equations for Unidirectional Transient Heat Conduction | . 99  |

|   |     | 4.1.1   | Isothermal Surface                                           | . 99  |

|   |     | 4.1.2   | Constant Heat Flux Surface                                   | . 100 |

|   | 4.2 | The C   | oefficient of Heat Penetration                               | . 101 |

|   | 4.3 | Model   | ling Transient Heat Conduction Problems                      | . 103 |

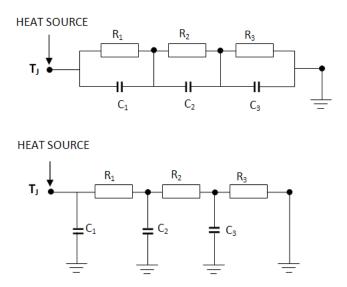

|   |     | 4.3.1   | RC Networks                                                  | . 103 |

|   |     | 4.3.2   | Cauer Network Construction                                   | . 105 |

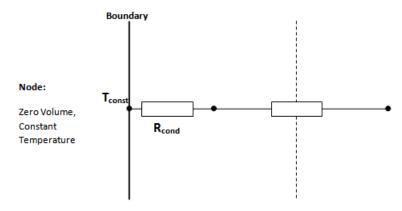

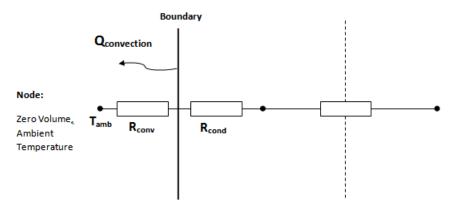

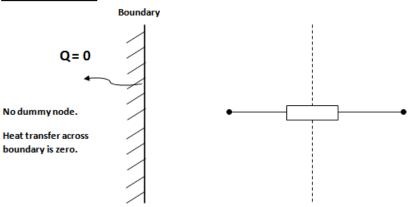

|   |     | 4.3.3   | Boundary Conditions                                          | . 109 |

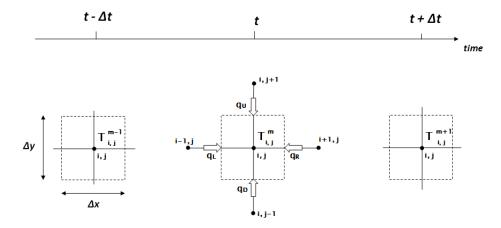

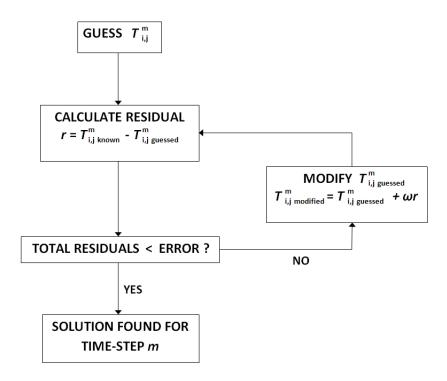

|   |     | 4.3.4   | Solving Thermal Resistance Networks                          | . 112 |

|   | 4.4 | Chapte  | er Conclusion                                                | . 121 |

| 5 | Nun | nerical | Modelling of Heat Sinks                                      | 122   |

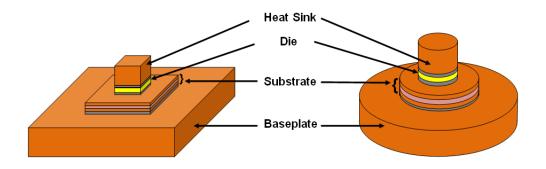

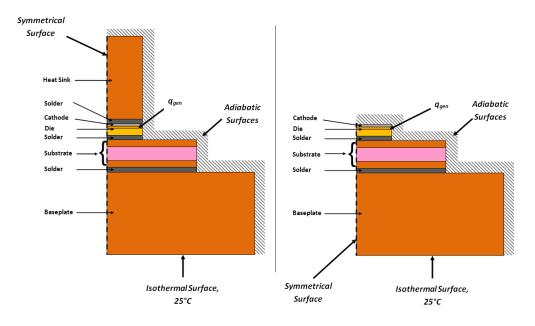

|   | 5.1 | Device  | e Structures                                                 | . 123 |

|   |     | 5.1.1   | Traditional Device Structure                                 | . 123 |

|   |      | 5.1.2   | Device Structure with heat sink         | 124 |

|---|------|---------|-----------------------------------------|-----|

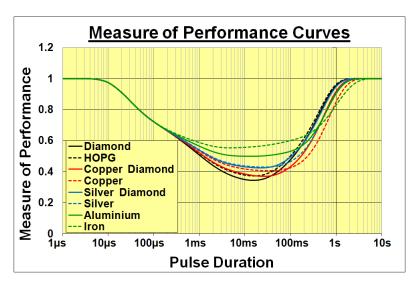

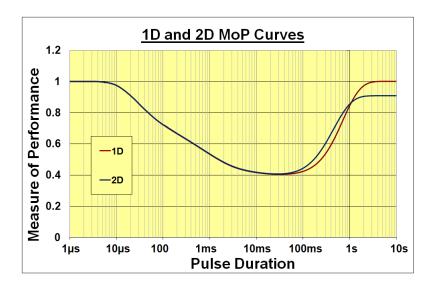

|   | 5.2  | Measu   | re of Performance                       | 126 |

|   | 5.3  | 1D Mo   | odelling Methodology                    | 128 |

|   |      | 5.3.1   | 1D Model Structures                     | 128 |

|   |      | 5.3.2   | Heat Generation in the Model            | 129 |

|   |      | 5.3.3   | Boundary Conditions                     | 131 |

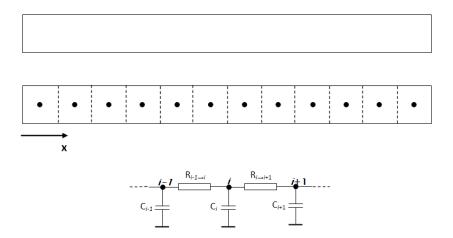

|   |      | 5.3.4   | Domain Discretisation                   | 132 |

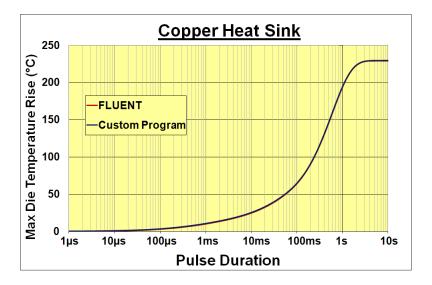

|   |      | 5.3.5   | Program Justification and Validation    | 134 |

|   | 5.4  | 1D Mo   | odelling Results                        | 138 |

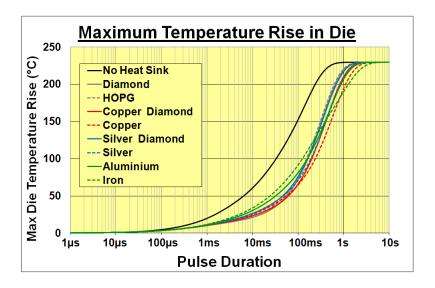

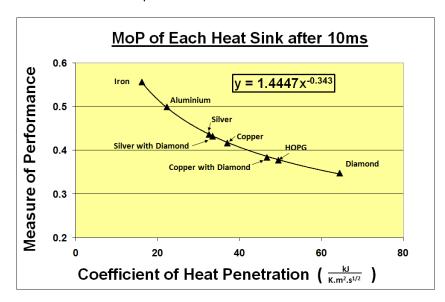

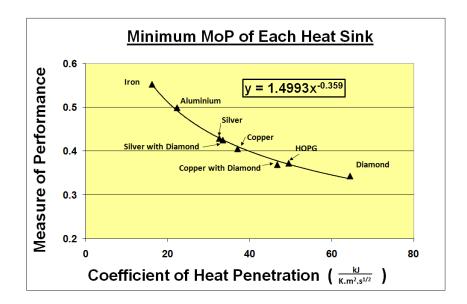

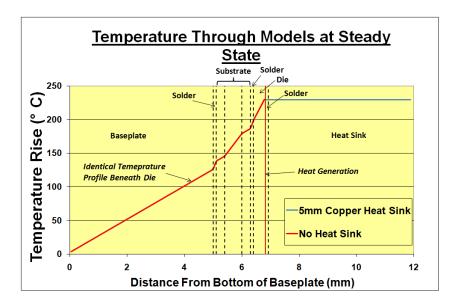

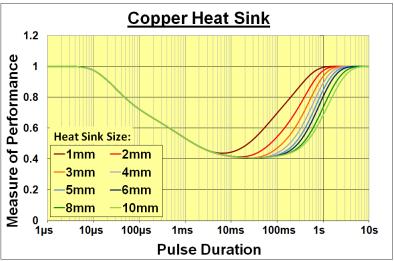

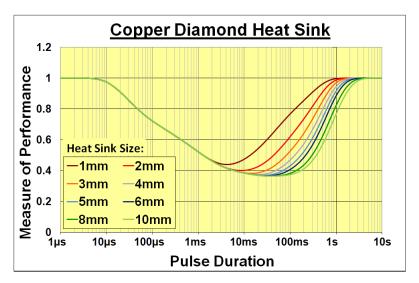

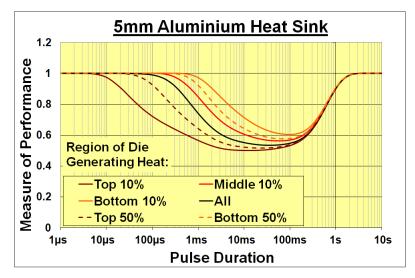

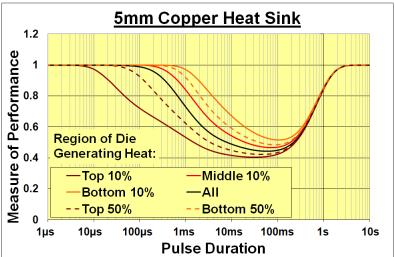

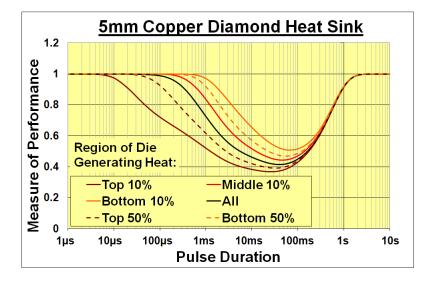

|   |      | 5.4.1   | Heat Sink Material                      | 138 |

|   | 5.5  | 1D Mo   | odelling Sensitivity Analysis           | L48 |

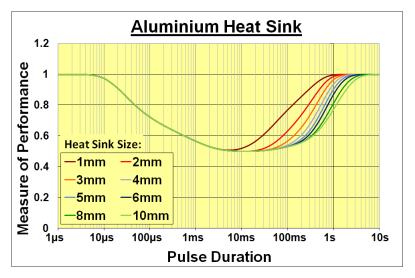

|   |      | 5.5.1   | Heat Sink Thickness                     | L48 |

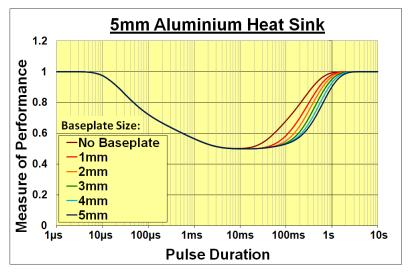

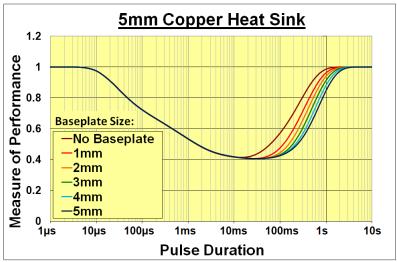

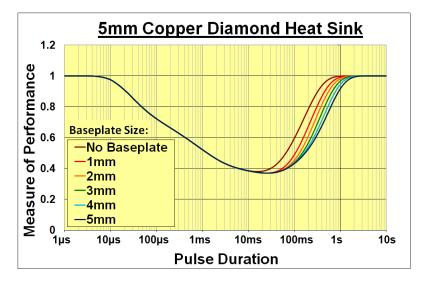

|   |      | 5.5.2   | Baseplate Thickness                     | 151 |

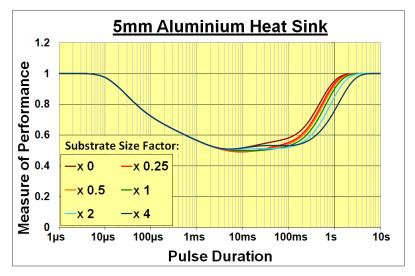

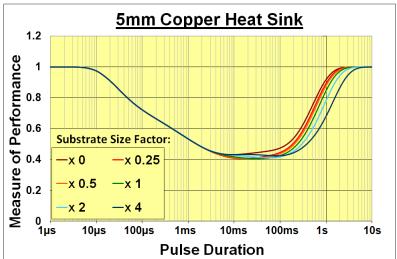

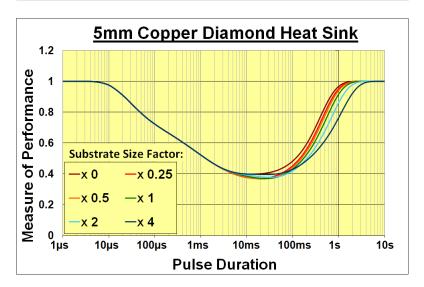

|   |      | 5.5.3   | Substrate Thickness                     | 154 |

|   |      | 5.5.4   | Solder Joint Thickness                  | 157 |

|   |      | 5.5.5   | Heat Generation Region                  | 161 |

|   | 5.6  | Chapte  | er Conclusion                           | 165 |

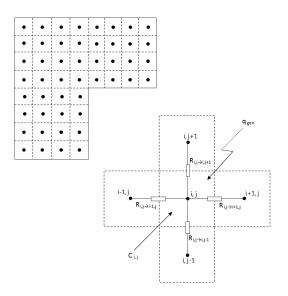

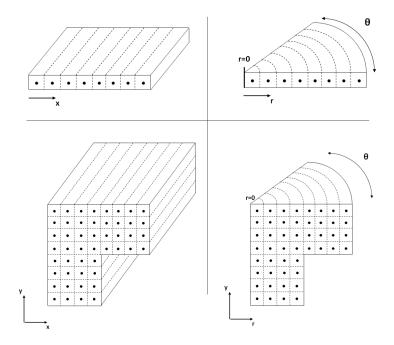

| 6 | 2D I | Modelli | ing 1                                   | .67 |

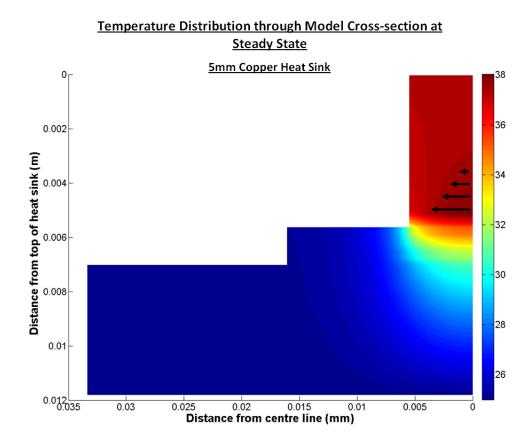

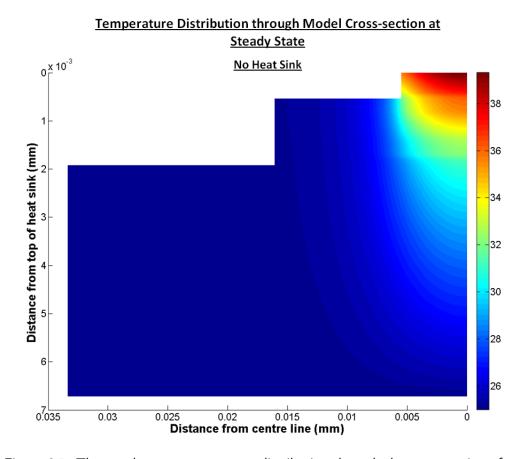

|   | 6.1  | 2D Mo   | odel Structures                         | 168 |

|   |      | 6.1.1   | Heat Generation and Boundary Conditions | 169 |

| J |      | 2D Mo   | odel Structures                         |     |

|   | 6.2 | 2D Modelling Results                                         |                                                                                                                                                                                                                  |                                        |  |

|---|-----|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

|   |     | 6.2.1                                                        | Heat Spreading Effects                                                                                                                                                                                           | 1                                      |  |

|   |     | 6.2.2                                                        | Heat Sink Thickness                                                                                                                                                                                              | 6                                      |  |

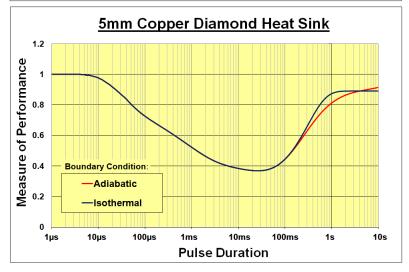

|   |     | 6.2.3                                                        | Baseplate Boundary Condition                                                                                                                                                                                     | 8                                      |  |

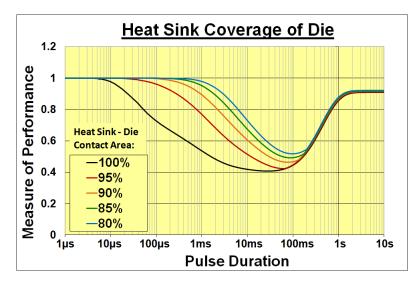

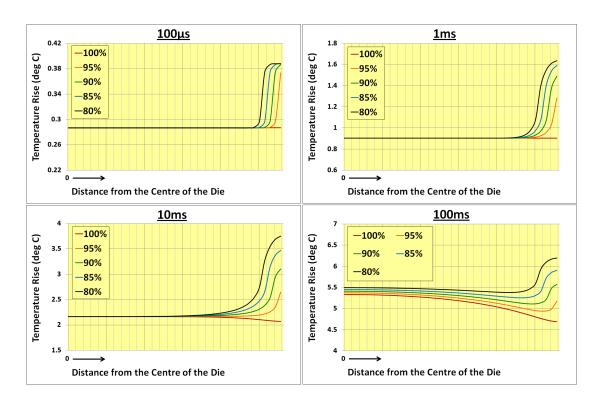

|   |     | 6.2.4                                                        | Heat Sink Coverage of Die                                                                                                                                                                                        | 2                                      |  |

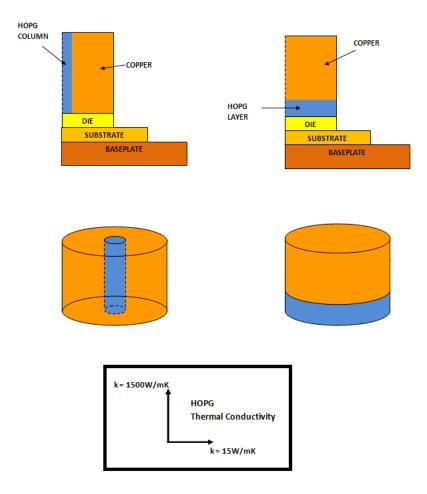

|   |     | 6.2.5                                                        | Composite Heat Sinks                                                                                                                                                                                             | 5                                      |  |

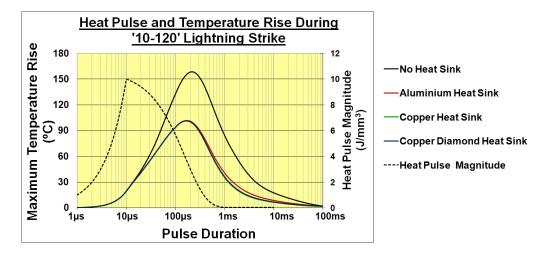

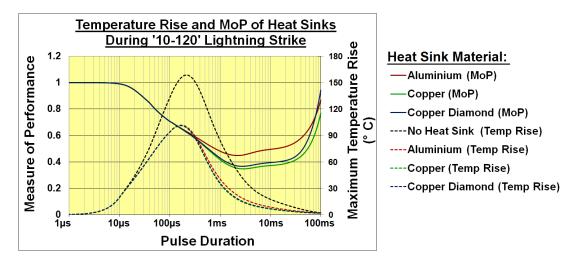

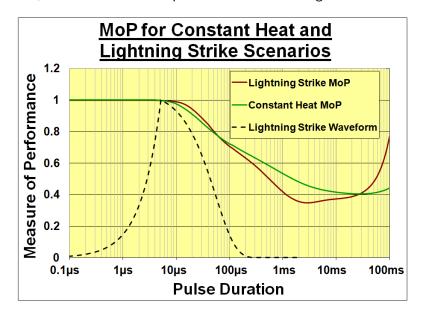

|   | 6.3 | Lightn                                                       | ing Strike Simulation                                                                                                                                                                                            | 1                                      |  |

|   |     | 6.3.1                                                        | Lightning Strike Form                                                                                                                                                                                            | 1                                      |  |

|   |     | 6.3.2                                                        | Heat Sink Performance during Lightning Strike                                                                                                                                                                    | 2                                      |  |

|   | 6.4 | Chapte                                                       | er Conclusion                                                                                                                                                                                                    | 6                                      |  |

| 7 | Exp | erimen                                                       | tal Validation of the Heat Sinks 19                                                                                                                                                                              | 8                                      |  |

|   |     |                                                              |                                                                                                                                                                                                                  |                                        |  |

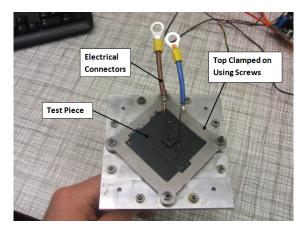

|   | 7.1 | The E                                                        | xperimental Facility                                                                                                                                                                                             | 9                                      |  |

|   | 7.1 | The E                                                        | xperimental Facility                                                                                                                                                                                             |                                        |  |

|   | 7.1 |                                                              |                                                                                                                                                                                                                  | 9                                      |  |

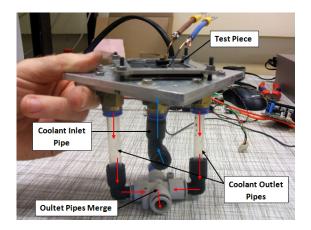

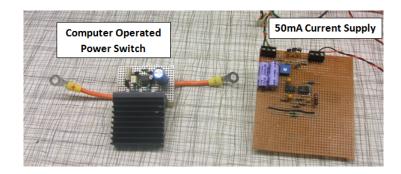

|   | 7.1 | 7.1.1                                                        | Experimental Rig                                                                                                                                                                                                 | 19                                     |  |

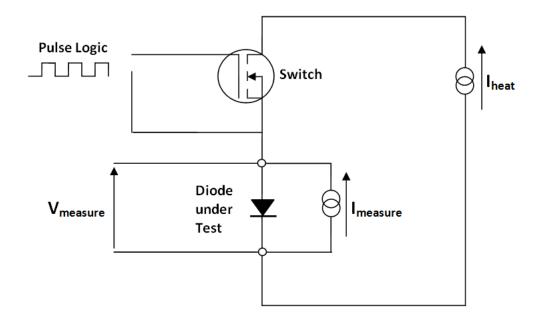

|   | 7.1 | 7.1.1<br>7.1.2<br>7.1.3                                      | Experimental Rig                                                                                                                                                                                                 | 12                                     |  |

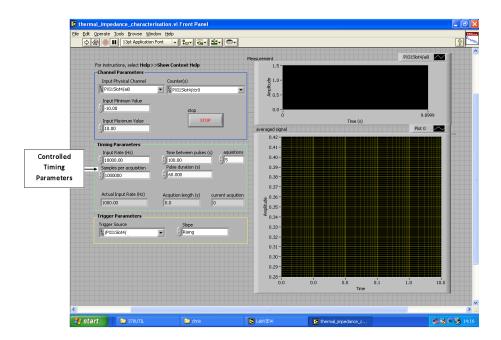

|   |     | 7.1.1<br>7.1.2<br>7.1.3                                      | Experimental Rig                                                                                                                                                                                                 | 13                                     |  |

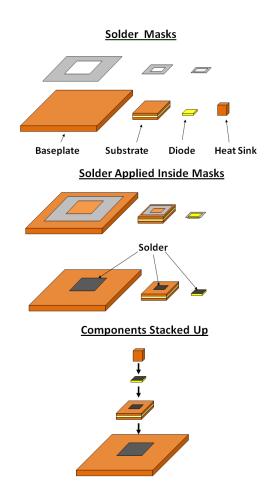

|   |     | 7.1.1<br>7.1.2<br>7.1.3<br>Manuf                             | Experimental Rig                                                                                                                                                                                                 | 13                                     |  |

|   |     | 7.1.1<br>7.1.2<br>7.1.3<br>Manuf<br>7.2.1<br>7.2.2           | Experimental Rig                                                                                                                                                                                                 | 19 13 18 19                            |  |

|   | 7.2 | 7.1.1<br>7.1.2<br>7.1.3<br>Manuf<br>7.2.1<br>7.2.2<br>Device | Experimental Rig                                                                                                                                                                                                 | 9<br>12<br>13<br>13<br>15              |  |

|   | 7.2 | 7.1.1<br>7.1.2<br>7.1.3<br>Manuf<br>7.2.1<br>7.2.2<br>Device | Experimental Rig 19   Device Calibration 20   Experimental Procedure 20   facturing the Test Pieces 20   Solders and Soldering Techniques 20   Electrical Connections 21   Temperature Measurement Techniques 21 | 19<br>12<br>13<br>13<br>18<br>19<br>17 |  |

| 8 | Exp | erimen  | tal Work on Power Switches                             | 224   |

|---|-----|---------|--------------------------------------------------------|-------|

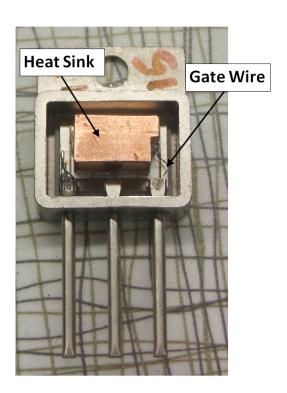

|   | 8.1 | Incorp  | orating a Heat Sink into a MOSFET                      | . 224 |

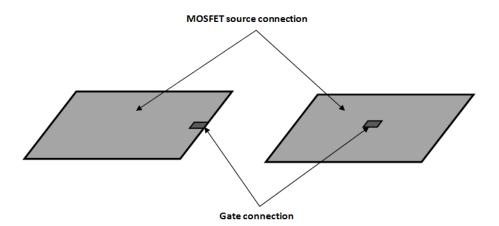

|   |     | 8.1.1   | Gate Position                                          | . 225 |

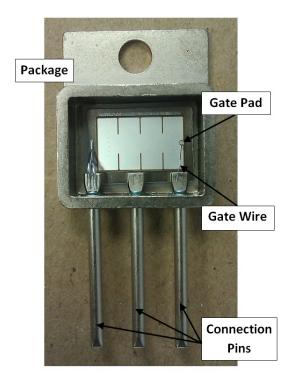

|   | 8.2 | Manuf   | acturing the MOSFETs with Heat Sinks                   | . 227 |

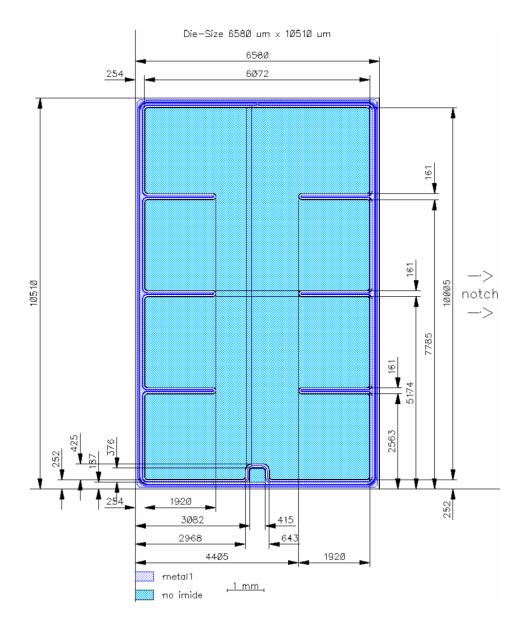

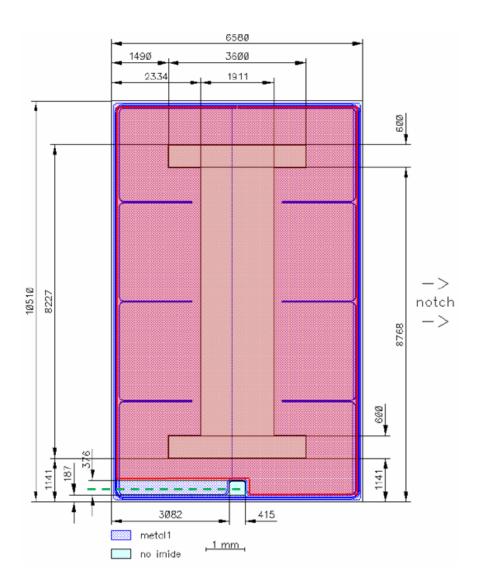

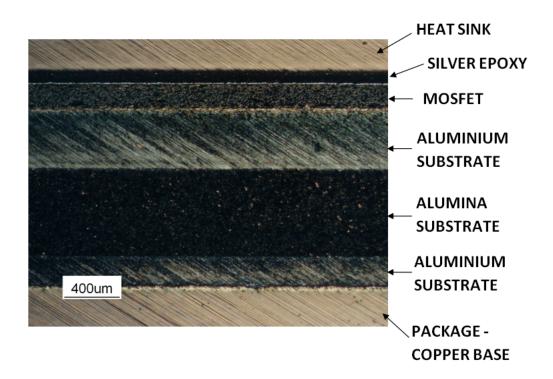

|   |     | 8.2.1   | The MOSFET device                                      | . 227 |

|   |     | 8.2.2   | Packaging the Devices                                  | . 227 |

|   |     | 8.2.3   | Heat Sink Design                                       | . 229 |

|   |     | 8.2.4   | Silver Epoxy                                           | . 230 |

|   |     | 8.2.5   | Heat Sink and Device Preparation                       | . 231 |

|   |     | 8.2.6   | Attaching Heat Sinks to the MOSFET Devices             | . 232 |

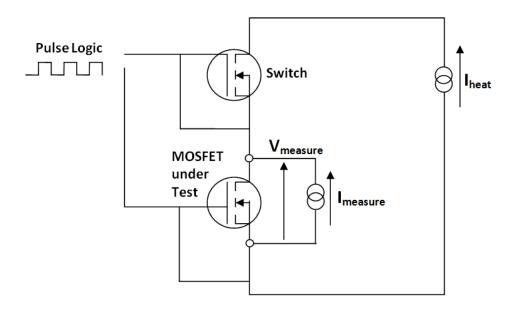

|   | 8.3 | Experi  | mental Procedure                                       | . 234 |

|   |     | 8.3.1   | Mounting Devices in Rig                                | . 234 |

|   |     | 8.3.2   | Water Coolant Pump                                     | . 234 |

|   |     | 8.3.3   | Electrical Setup                                       | . 235 |

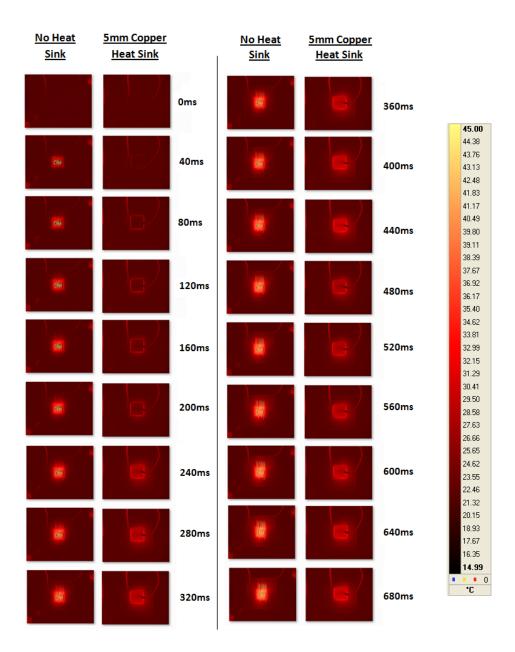

|   | 8.4 | Experi  | mental Results for the MOSFET Devices                  | . 237 |

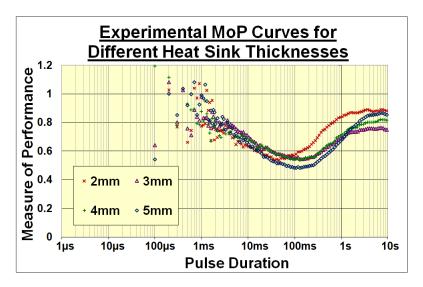

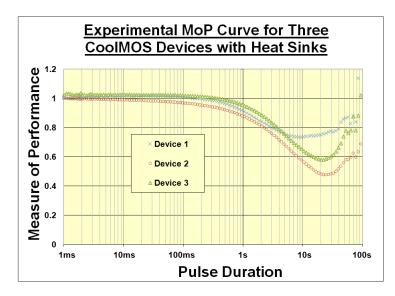

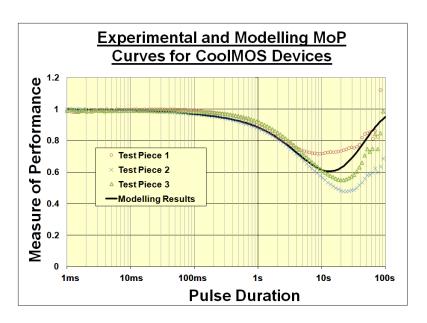

|   |     | 8.4.1   | Experimental MoP Curves                                | . 237 |

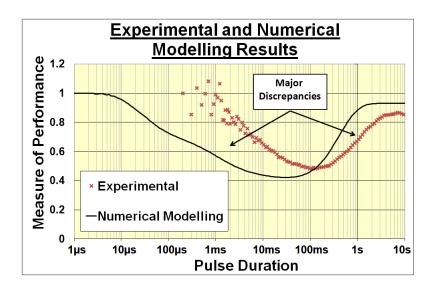

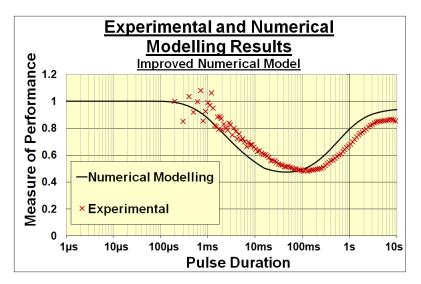

|   | 8.5 | Replica | ating Experimental Results through Numerical Modelling | . 239 |

|   |     | 8.5.1   | Model Composition                                      | . 239 |

|   |     | 8.5.2   | Modelling Results                                      | . 240 |

|   | 8.6 | Chapte  | er Conclusion                                          | . 243 |

| 9 | Con  | clusion | s and Recommendations                                          | 245   |

|---|------|---------|----------------------------------------------------------------|-------|

|   | 9.1  | Conclu  | isions                                                         | 247   |

|   |      | 9.1.1   | Thermal Modelling of Transients in Power Electronic Stack-Ups  | s 247 |

|   |      | 9.1.2   | Heat Sink Performance during Thermal Transients                | 247   |

|   |      | 9.1.3   | Effect of Different Heat Sink Materials                        | 248   |

|   |      | 9.1.4   | Heat Spreading Effects                                         | 248   |

|   |      | 9.1.5   | Experimental Validation of Heat Sink Performance               | 249   |

|   |      | 9.1.6   | Application of Heat Sink to Different Power Electronic Devices | 250   |

|   | 9.2  | Contri  | bution of the Thesis                                           | 251   |

|   | 9.3  | Recom   | mendations for Future Work                                     | 252   |

| Α | The  | rmal P  | roperties of Materials                                         | 263   |

| В | Emi  | ssivity | Coefficients of Selected Surfaces                              | 264   |

| С | Sold | ler Pas | te Methodology                                                 | 265   |

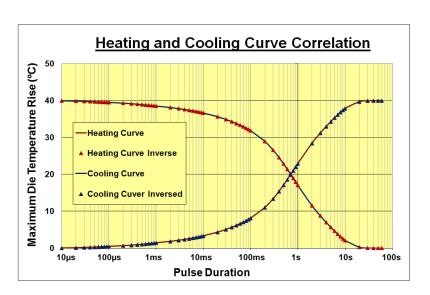

| D | Coo  | ling Cu | rve Inversion                                                  | 266   |

## Notation

| A               | $[m^2]$                  | Area                        |

|-----------------|--------------------------|-----------------------------|

| $c_p$           | [J/kgK]                  | Specific Heat Capacity      |

| C               | [J/K]                    | Thermal Capacity            |

| E               | [J]                      | Energy                      |

| Fo              |                          | Fourier Number              |

| h               | $[W/m^2 K]$              | Heat Transfer Coefficient   |

| I               | [A]                      | Current                     |

| k               | [W/mK]                   | Thermal Conductivity        |

| P               | [W]                      | Power                       |

| q               | [W]                      | Heat Transfer Rate          |

| r               | [m]                      | Radius                      |

| $r_s$           |                          | Residual                    |

| R               | $[\Omega]$               | Resistance                  |

| T               | $[Kor \ ^{\mathbf{Q}}C]$ | Temperature                 |

| V               | [V]                      | Voltage                     |

| u               | [J]                      | Internal Energy             |

| w               | [W]                      | Work Rate                   |

| x               | [m]                      | Length                      |

| $Z_{\theta}(t)$ | [K/W]                    | Transient Thermal Impedance |

## **Greek Symbols**

$\alpha \qquad \qquad [m^2/s] \qquad \text{Thermal Diffusivity}$

$\rho \qquad \qquad [kg/m^3] \qquad {\rm Density}$

au [s] Time-constant

Relaxation Factor

#### Glossary

Active Metal Bonding. A substrate manufacture process where

AMB copper is bonded on the ceramic substrate using

Silver-Copper-Titanium brazing.

Direct Bond Copper. A substrate manufacture process where copper and ceramic are bonded directly.

Imide A thin polymer layer applied to some electronic devices.

A dimensionless number which gives the ratio of the heat transfer rate at the boundary of a model to the heat transfer rate inside the body.

## Chapter 1

## Introduction

Power electronics involves the processing of electrical power (voltage, current and frequency) by means of solid-state electronics. It is used in a wide range of applications, from mobile phones to space shuttle power supply systems. The aerospace industry also heavily employs power electronics to control electrical supplies within aircraft.

A major design limit for modules of power electronic devices, such as solid-state power switches, is the device temperature; an estimated 55% of electronic component failures are related to temperature[1]. The semiconductor industry is driven to decreasing the size of semiconductor devices. Coupled with the continuing increase in power dissipation, the power density of devices is rising which puts pressure on cooling technologies to develop sufficiently to allow progression in the electronics sector without compromising reliability.

This thesis focuses on the use of solid-state power switches as a replacement for mechanical switches in aircraft. The benefits of using solid-state power switches over mechanical switches include faster switching times, as well as quieter operation and increased lifetime as they have no moving parts. However, solid-state power switches experience increased heat dissipation due to the voltage drop across them. Effective management of this heat generation is required in order to increase the operating

lifetime of the devices. In particular, short duration transient heat losses are a key issue which need to be considered when designing thermal management systems.

Power electronic devices must be designed to handle the largest power dissipation to which they may be subjected. Short surges can occur due to over-current faults, which dissipates heat within devices. In some applications it may be adequate to switch devices off during such transients, but in the aerospace industry it is preferred that aircraft equipment is not switched off unnecessarily. Devices are required to ridethrough these transients to allow time for faults to be diagnosed and unnecessary shut downs to be avoided.

In these cases, systems must be designed to handle the transient currents, where heat dissipation may be up to ten times greater than during normal operation. The present method of managing current surges involves over-sizing power modules to provide more thermal mass, which allows more current to be dissipated without exceeding the temperature limit. Power electronic systems designed in this way are over-sized and heavy and are underused for the majority of the time during normal operation.

Some power electronic switches are used for switching at high frequencies. In these applications, a significant amount of heat is generated during the switching process (known as switching losses). This thesis considers the use of power electronics in the 'on' state, which therefore allows switching losses to be ignored.

#### 1.1 Problem Definition

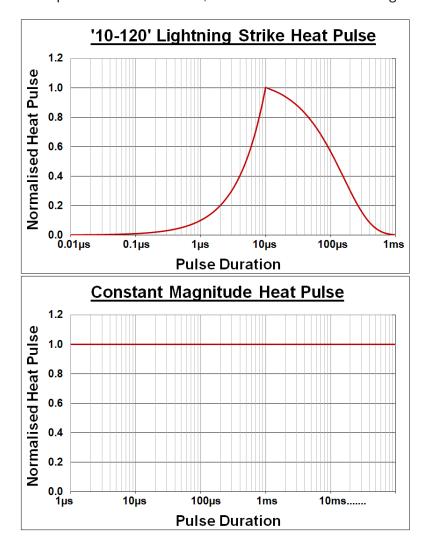

A new device-level thermal design to handle short periods of increased heat generation is required. This would reduce redundancies and give reductions in system size, weight and cost. The new design must therefore be able to reduce the temperature of power electronic devices for transients of up to 100ms in length, the time typically needed to allow for fault diagnosis, or in aircraft, to tolerate lightning strikes.

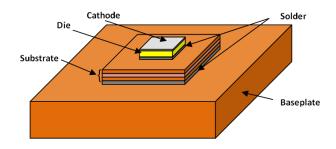

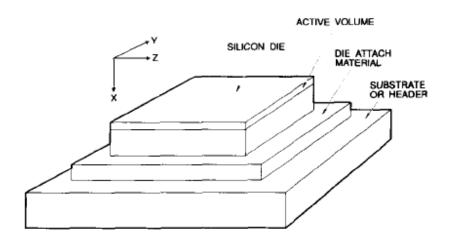

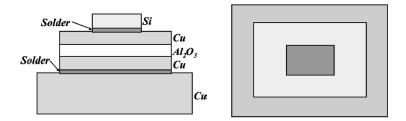

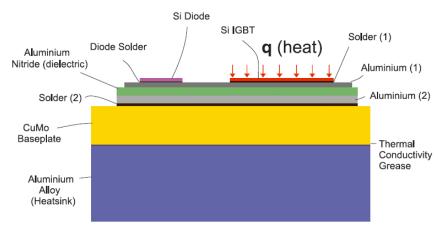

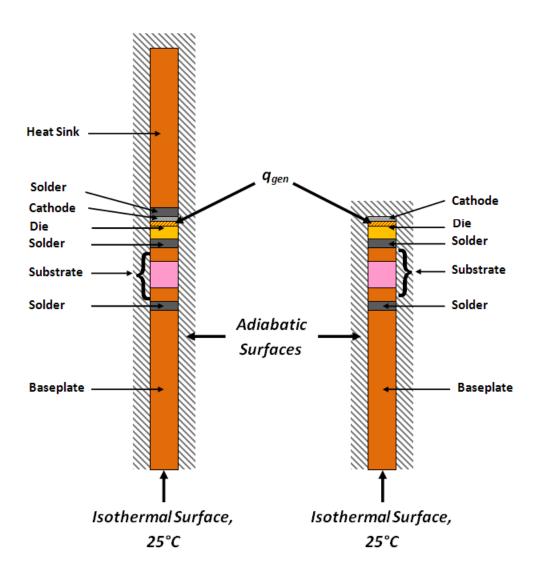

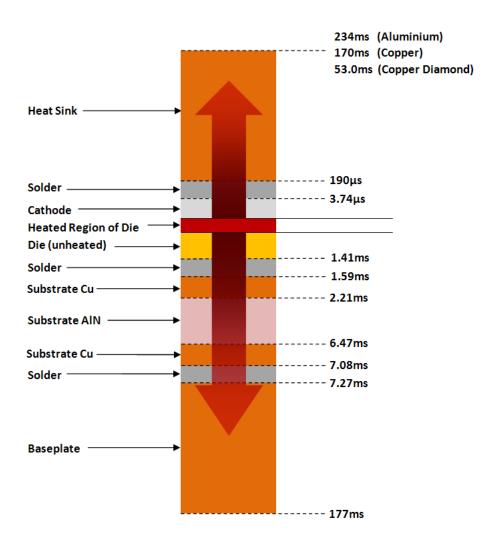

A typical power electronic stack for a semiconductor device (also known as a die) is shown in Figure 1.1. Typical dimensions for the device stack are listed in Table 1.1. The stack is usually packaged for protection (omitted in Figure 1.1), and the only exposed surface is the bottom of the baseplate, which is normally cooled via convection. Heat is generated within the device and is conducted through the stack to the cooled baseplate surface where it is conducted away from the system.

Figure 1.1: A typical device stack.

| Layer             | Thickness | Material            | Width/Depth |

|-------------------|-----------|---------------------|-------------|

|                   | (mm)      |                     | (mm)        |

| Cathode           | 0.02      | Aluminium           | 10          |

| Die               | 0.4       | Silicon             | 10          |

| Solder            | 0.1       | Solder Sn96.5-Ag3.5 | 10          |

| Substrate: Copper | 0.3       | Copper              | 29          |

| Substrate: AIN    | 0.6       | Aluminium Nitride   | 29          |

| Substrate: Copper | 0.3       | Copper              | 29          |

| Solder            | 0.1       | Solder Sn96.5-Ag3.5 | 29          |

| Baseplate         | 5         | Copper              | 60          |

Table 1.1: Typical thickness and material of the components used in the stack.

Conduction is the main heat transport mechanism for heat generated within the device. All heat generated must be conducted to the baseplate surface in order to be convected out of the system. This setup is not effective for cooling short transients, as the cooling fluid at the bottom of the baseplate is too far away from the heat source to allow it to be effective for the shorter transients. The structure of the stack-up must therefore

be modified to improve thermal device management for short heat surges. Minimising the steady state thermal resistance is not a concern as this is not the limiting factor in the thermal design of the system.

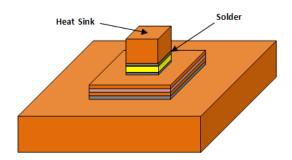

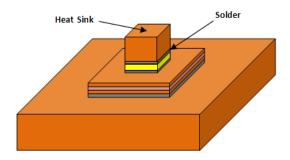

A potential solution to the problem is to use the top surface of the die to provide an additional thermal route for generated heat. A solid heat sink attached to the top of the device would allow the heat to be conducted into the heat sink, where it could be stored during the heat pulse and then conducted back through the device after the heat pulse. A diagram of the modified device stack can be seen in Figure 1.2.

The aim of the project is to investigate the use of the heat sink as a thermal mass close to the die to suppress short thermal transients.

Figure 1.2: The typical device stack with the addition of the heat sink and solder layer on top of the die.

#### 1.2 Objectives

The aim of this thesis is to investigate the heat transfer within a power electronic device stack.

There are two main objectives of this work:

1. To investigate the use of a thermal mass to reduce device temperatures during transients by using thermal resistance networks to model transient heat conduction.

This includes modelling a variety of stack configurations and modifications to assess improvements to the device temperature.

2. To use experimental testing to validate the thermal modelling results. At this stage, the practicality (in terms of cost and ease of manufacture) of the stack designs are considered, as a prototype is manufactured for experimental testing.

#### 1.3 Thesis Structure

The thesis begins with an overview of power electronic devices and heat transfer, presented in Chapter 2. This aims to introduce heat generation mechanisms in power electronics and outline some key heat transfer theory. A literature survey is presented in Chapter 3, which relates the work presented in this thesis to previous work performed and the state-of-the-art. Chapter 4 presents techniques which may be adopted for modelling heat conduction.

The main part of the study consists of two parts:

- Chapter 5 begins with a detailed description of the method chosen for modelling

the transient heat conduction. This leads into the results and analysis from the

1D modelling. A sensitivity analysis of the stack-up on the heat sink performance

is performed and presented. The modelling work is then extended into Chapter

In this chapter the 2D modelling results are presented, along with discussion

into the differences between the 1D and 2D modelling results.

- 2. The experimental verification of the modelling results is presented in Chapter 7. The experimental facility is detailed, including the apparatus, rig setup and thermal measurement techniques used. The manufacture of diodes with a heat sink on is described followed by the results of the experimental testing. The chapter is concluded with the comparison between the modelling and experimental results, with reasons for any discrepancies discussed. The experimental

work is extended in Chapter 8, in which heat sinks are used on MOSFET devices. Difference in the manufacture and testing procedure compared to the experiments using diodes is explained. The experimental results follow, with a comparison to the numerical results when modelling the experimental setup.

General conclusions and recommendations for further work are finally given in Chapter 9.

## Chapter 2

# Overview of Power Electronic Devices and Heat Transfer

This chapter aims to explain some aspects of the physics of power electronic devices that are important to heat generation, beginning with the introduction of Breakdown Voltage and Avalanche Breakdown, which are causes of device failure. Following on from this is a section discussing the mechanisms behind the generation of heat in power electronic devices. Different power electronic devices are then discussed which are relevant to the thesis. The theory section on power devices has been written using the following references: [2, 3, 4, 5, 6, 7].

In the second part of the chapter heat transfer theory is discussed. The heat conduction equation is derived, from which important material properties for heat conduction are identified. The chapter then focuses on transient heat conduction. Three transient heat conduction regimes are identified: the early, transitional and late regime. The behaviour of heat conduction through these regimes is analysed, leading to the definition of the Fourier number. Using the Fourier number, a time constant is defined, which is used throughout the thesis when analysing the thermal behaviour inside the stack.

#### 2.1 Power Electronics Overview

In order to model the heat generation mechanism in power electronic devices, it is necessary to first develop an understanding of the devices. Various different types of device exist, each of which is composed of different regions of doped silicon. Although the operation and architecture of these devices differ, they share some fundamental principals of operation. It is assumed that the fundamental behaviour of power electronic devices, such as that of electrons at p-n junctions, is known.

#### 2.1.1 Breakdown Voltage and Avalanche Breakdown

Power electronic devices are constructed using regions of different doping. By exploiting the electrical behaviour of these junctions, devices can be created that allow electrical flow to be manipulated and controlled. Knowledge of this background theory including semiconductor doping and junction behaviour under forward and reverse bias electrical flow is assumed, and can be found in numerous text books, such as those listed at the beginning of the chapter.

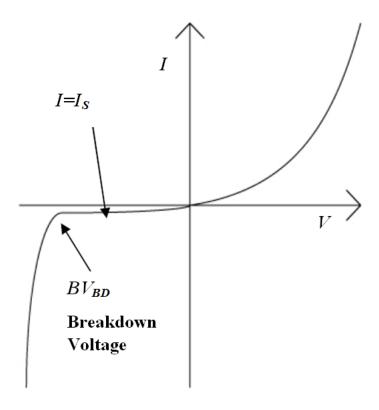

The Breakdown Voltage,  $BV_{BD}$ , is a feature of the reverse biased region of an IV curve such as the one shown in Figure 2.1. When sufficient reverse biased voltage is applied to the junction, a sudden rapid increase in current occurs. The current increase leads to a large amount of power dissipation which results in device failure due to the increased heat within the device. This process is termed the Avalanche Breakdown.

Avalanche breakdown is caused by a process called *Impact Ionisation*. The kinetic energy of electrons is directly proportional to the electric field applied to them. When electrons with a large enough kinetic energy collide with silicon atoms, the transferred energy can break one of the silicon's covalent bonds, releasing an electron. The released electron may then gain enough kinetic energy from the electric field to break a covalent bond in another atom. The numbers of electrons in the field increase as

Figure 2.1: The I-V characteristics of a p-n junction.[2]

covalent bonds are broken, which in turn increases the number of impact ionisations. This cascading effect leads to a dramatic increase in current as the number of electrons increase. Once again, the increased current leads to an increase in power dissipation, which can lead to device destruction through overheating.

#### 2.2 Power Devices

Power devices require a more complicated structure than low-power counterparts. Additional structural features are necessary due to the fact these devices require to handle high power loads. A selection of power electronic devices are discussed which bear relevance to this thesis. The power diode and MOSFET are both used for experimental work, and therefore an understanding of their operation is given.

#### 2.2.1 Power Diodes

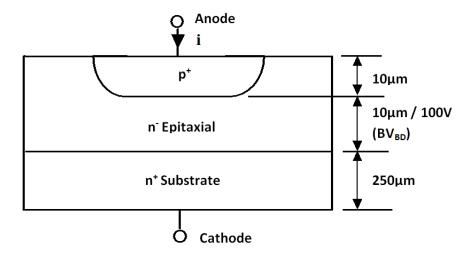

Diodes contain a single p-n junction, as shown in Figure 2.2. Two heavily doped regions, the  $p^+$  and  $n^+$  substrate, are separated by a lightly doped  $n^-$  region, called the epitaxial. This region of light doping absorbs the depletion layer, allowing large reverse biased voltages to be applied across it without the depletion region growing excessively wide. As such, the width of the epitaxial layer is dependent on the designed breakdown voltage, and is around  $10\mu\text{m}/100\text{V}$ . The  $p^+$  and  $n^+$  substrate layers have fixed widths of around  $10\mu\text{m}$  and  $250\mu\text{m}$ , respectively.

Figure 2.2: Vertical cross-section showing the structure of a power diode.[2]

#### 2.2.2 MOSFETs

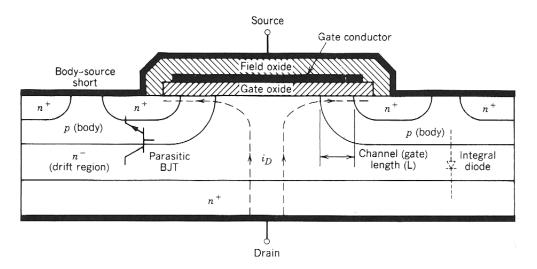

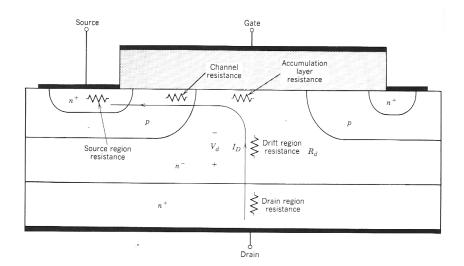

Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) are used in applications where large off-state blocking voltages and high current-carrying capabilities are needed. Figure 2.3 shows the vertical cross-section of a MOSFET cell. Thousands of cells are used in parallel to create a power MOSFET device with large gain and low on-state resistance.

A MOSFET has three connections: the source, drain and gate. The *n-p-n* junctions between the source and drain makes electrical conduction appear impossible between the two. In order to achieve conduction between the source and drain, a voltage must be applied between the gate and source.

Figure 2.3: A cross-sectional view of a MOSFET cell, showing the doped regions and the three connectors: source, drain and gate.[2]

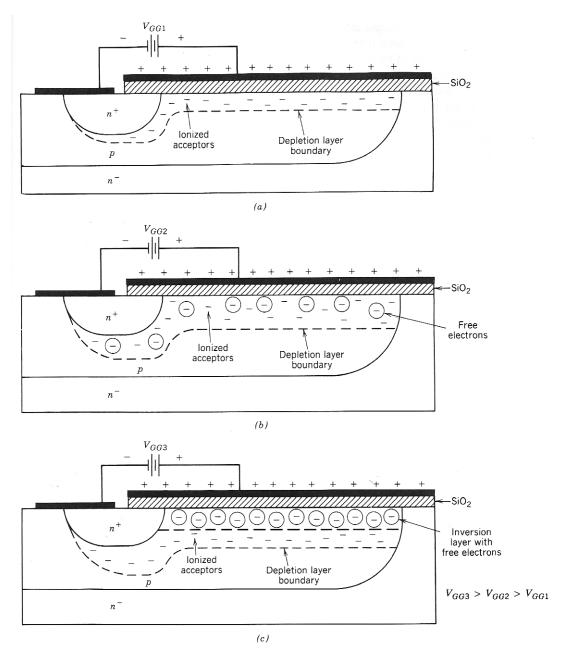

The gate consists of the gate conductor (the metallisation region), a non-conducting silicon dioxide layer ( $SiO_2$ , termed the gate oxide) and the silicon beneath the gate oxide. Applying a small gate-source voltage ( $V_{GS}$ ) creates a depletion region at the interface between the silicon and gate oxide. The positive charge on the gate conductor repels holes directly beneath the gate oxide, allowing electrons from the source connection to ionise the acceptor atoms in the p-region. These negatively charged ionised acceptors are drawn to the negatively charged gate conductor, creating

a depleted region directly beneath the gate oxide.

Figure 2.4: The formation of the depletion and inversion layers beneath the  $SiO_2$  gate oxide as the magnitude of  $V_{GS}$  increases.[2]

Increasing  $V_{GS}$  causes the depletion region to grow in thickness. The electric field at the oxide-silicon interface grows, attracting free electrons to the surface. The layer of electrons is termed the *inversion layer*, providing a conductive path for current between the source and drain. The growth of the inversion layer is shown in Figure

#### 2.4.

The size of the channel created between the source and drain is dependent on the size of  $V_{GS}$ ; increasing  $V_{GS}$  widens the channel width. This reduces the resistance between the source and drain, allowing a greater current flow. For current flow between the source and drain,  $V_{GS}$  must be greater than the threshold value of the MOSFET,  $V_{GS(th)}$ .

#### 2.2.3 IGBTs

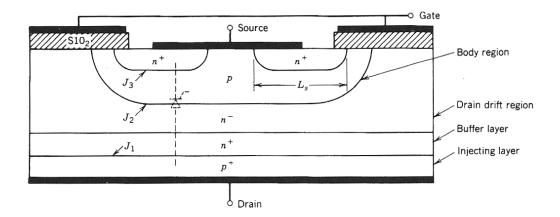

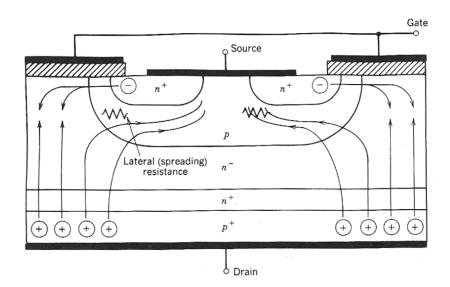

The structure of Insulated Gate Bipolar Transistors (IGBTs) is illustrated in Figure 2.5. They are similar in construction to MOSFETs, with the addition of a  $p^+$  injecting layer which forms the drain of the IGBT. This  $p^+$  injecting layer forms a p-n junction ( $J_1$ ) which injects minority carriers into the buffer layer, which is the drain connection in the MOSFET.

The on-state operation of the IGBT works in a similar manner to the MOSFET. A gate-source voltage  $(V_{GS},$  which must be greater than  $V_{GS(th)})$  creates an inversion layer that shorts the  $n^-$  drift to  $n^+$  source, as demonstrated in Figure 2.4. This allows electron flow though the inversion layer. This results in substantial hole injection from the  $p^+$  drain contact layer into the  $n^-$  drift region. The injected holes move across the drift region and reach the p body region, subsequently attracting electrons from the source p body contact with which they recombine. The flow of holes and electrons is depicted in the bottom of Figure 2.5.

Figure 2.5: *Top*: A cross-sectional view of a IGBT cell, showing the doped regions and the three connectors: source, drain and gate. *Bottom*: The flow of electrons and holes during the IGBT on-state.[2]

#### 2.3 Heat Generation in Power Electronic Devices

Heat generation in semiconductor devices is caused from the power losses within them, and can be calculated by using either of the following equations:

$$P = I^2 R \qquad or \qquad P = \frac{V^2}{R}$$

where I and V are the operating current and voltage, and R is the total resistance through the device. The location of the power loss in the device can be analysed if the local current density and resistances are known.

#### 2.3.1 MOSFETs and IGBTs

The resistance components within the MOSFETs are shown in Figure 2.6. Nearly all power dissipated in a MOSFET occurs during the on-state, and therefore MOSFET design is heavily orientated towards reducing the on-state resistances within the device. The length of the current paths across the large resistance components are minimised, and regions are doped as heavily as the other requirements (such as breakdown voltage) allow. The 'channel' and 'accumulation layer' resistances are affected by the gate-source voltage; larger voltages create larger inversion layers and thus reduce the electrical resistance. The resistive components in Figure 2.6 contribute equally to the total on-state resistance for low breakdown voltages (a few hundred volts or less). At greater breakdown voltages, the drift region resistance is dominant.[2]

The resistances are also temperature dependent. As the device temperature increases, the resistance also increases. This leads to further power dissipation, and as a result, further increases in temperature. This *thermal runaway* causes large increases in device temperature which can lead to device failure.

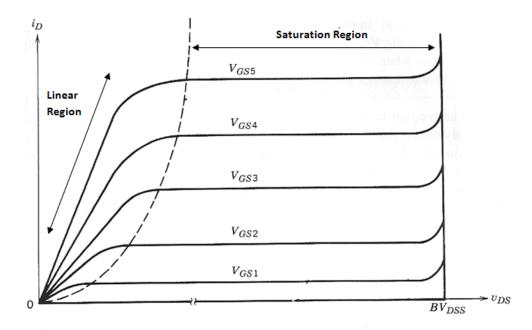

In transient situations, the current demand through the device increases rapidly. The drain current  $(I_D)$  rises until the saturation region is reached, at which point it is said

Figure 2.6: The on-state resistances within a MOSFET device.[2]

Figure 2.7: The linear and saturation regions of the MOSFET I-V curves.[2]

to have 'pinched off'[3]. At pinch off, the channel resistance is the largest resistor in the MOSFET. The power drop across the channel increases with the increase in current demand due to the rise in  $V_{DS}$ , resulting in significant heat generation in the silicon region directly beneath the gate contact. Therefore, in transient situations, the majority of the heat generation occurs in the top part of the MOSFET devices.

As IGBTs function in a similar manner to MOSFETs, the heat generation mechanisms

are also very similar. Trivedi and Shenai [8] demonstrated the region of heat generation in IGBTs during short-circuit (transient) conditions is directly beneath the gate connection.

Another loss mechanism in power MOSFETs is the flow of charge to and from the gate capacitance, termed switching losses. In applications where MOSFETs and IGBTs are switched at high frequencies, these switching losses become significant. However, this thesis will not be considering these applications, and will therefore focus on device losses during the on-state only.

#### 2.4 Device Failure Mechanisms

The temperature of any semiconductor device must be kept under control in order to maintain functionality. The theoretical limit to the temperature is the temperature at which the intrinsic carrier density,  $n_i$ , becomes equal to the majority carrier doping density in the lightest doped region. At this temperature, termed the intrinsic temperature,  $T_i$ , the depletion region at the junction is shorted out by the intrinsic carriers, losing the rectifying characteristics. For power diodes, the lightly doped epitaxial layer has a dopant concentration corresponding to an intrinsic temperature of about  $280^{\circ}$ C. The maximum specified temperature from manufacturers is often around  $125^{\circ}$ C, which represents the maximum temperature at which the device can reliably perform to certain specifications, for example on-state conduction voltages, switching times and switching losses. There are numerous types of device failure that occur, many of which are related to the temperature and are induced prior to the intrinsic temperature.

Avalanche breakdown, as discussed previously, is a common form of device failure which is a result of impact ionisation. Devices that are heated up too much can also develop thermal runaway, due to the relationship between electrical resistance and temperature. Short-circuit failure mechanisms can be divided into four modes [9]. These failure types are defined by the time at which they occur (in relation to the short-circuit), the most common of which is failure during the short circuit, called 'energy limited failure', and is attributed to thermal runaway.

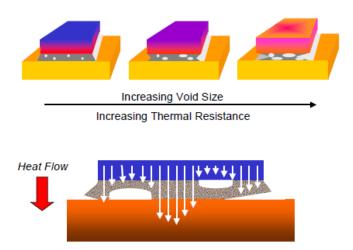

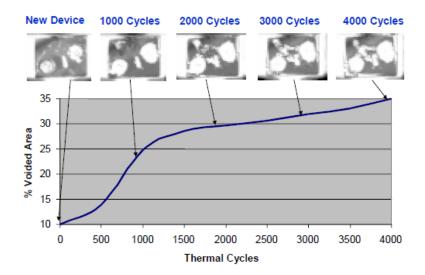

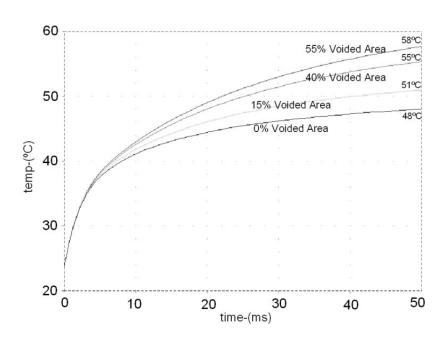

Devices can also fail due to stack components deteriorating over time. Device stacks are subjected to thermal cycling during operation which causes the stack components to expand and contract. Layers in the stack with different Coefficients of Thermal Expansion (CTEs) expand at different rates, leading to mechanical stresses and cracking. The voids created by the cracks increase the thermal resistance between the device and the coolant. As a result, the steady state temperature of the device increases which can subsequently cause the device to fail.

#### 2.5 Heat Conduction Theory

The theory of heat transfer is well established. Heat transfer occurs due to the migration of energy between locations at different temperatures. Thermodynamic principles based on observations have been generalised into laws, and governing equations have been derived that can be applied to any situation. The thermodynamic theory can be used to deduce the heat conduction theory which characterises the flow of heat through solids. Conduction theory can be used to model the heat conduction through electronic devices, allowing the temperatures inside the devices to be calculated when heat pulses are simulated inside them.

#### 2.5.1 Heat Conduction Equation

The general heat conduction equation is derived from the first laws of thermodynamics and Fourier's equation of heat conduction. This common derivation can be found in sources such as [10]. Fourier's equation is used to calculate the heat flux per unit area, q'', between two points distance dx apart with temperature difference dT:

$$q'' = -k \frac{\mathrm{d}T}{\mathrm{d}x} \tag{2.1}$$

Thermal conductivity, k, is a material property that describes how easily heat can travel through a solid. The rate of heat conduction between two points at different temperatures is proportional to the thermal conductivity of the conducting material. In other words, the resistance to the heat conduction is proportional to the inverse of the thermal conductivity:

Thermal Resistance

$$\propto \frac{1}{k}$$

(2.2)

Applying equation 2.1 to a solid and using the first law of thermodynamics produces the 3D conduction equation in partial differential form:

$$\frac{\partial}{\partial x} \left( k \frac{\partial T}{\partial x} \right) + \frac{\partial}{\partial y} \left( k \frac{\partial T}{\partial y} \right) + \frac{\partial}{\partial z} \left( k \frac{\partial T}{\partial z} \right) + \dot{q} = \rho c_p \frac{\partial T}{\partial t}$$

(2.3)

where  $\dot{q}$  is the volumetric internal heat generation with the units W/m<sup>3</sup>. This can be reduced to 1D, to simplify the discussion:

$$\frac{\partial}{\partial x} \left( k \frac{\partial T}{\partial x} \right) + \dot{q} = \rho \, c_p \, \frac{\partial T}{\partial t} \tag{2.4}$$

However, the form of the expression used more commonly is:

$$k A \frac{\mathrm{d}T}{\mathrm{d}x} + q_{gen} = V \rho c_p \triangle T \tag{2.5}$$

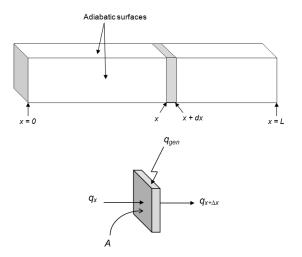

This can be applied to a solid bar through which heat conduction occurs in 1 direction, such as that shown in Figure 2.8. The last term in equation 2.5 contains the expression  $\rho c_p$ , which is called the thermal mass as it determines how quickly a volume, V, responds to a change in thermal surroundings, such as a heat input.

Figure 2.8: 1D heat conduction along a solid bar.

#### 2.5.2 Thermal Diffusivity

The conduction equation can be rearranged to group three important variables together: density, specific heat capacity and thermal conductivity.

$$\frac{\partial^2 T}{\partial x^2} + \frac{\dot{q}}{k} = \frac{1}{\alpha} \frac{\partial T}{\partial t}$$

(2.6)

In which the *thermal diffusivity* ( $\alpha$ ) is:

$$\alpha = \frac{k}{\rho \, c_p} \tag{2.7}$$

Thermal diffusivity is an important property for transient heat conduction, as it determines how quickly a material can adjust to its surrounding thermal environment.

#### 2.6 Transient Heat Conduction

When the boundary conditions of a solid system are known (i.e. the heat transfer conditions at the external surfaces and the locations and magnitudes of any internal heat generation) the steady state temperature distribution within the system can be calculated directly. Solution methods can be found in most heat transfer text books, such as Bejan [10], Kreith and Bohn [11]. A general steady state equation for solids, such as the slice shown in Figure 2.8, can be expressed:

$$q_{x+dx} - q_x + q_{qen} = 0 (2.8)$$

However, a different approach must be taken if the temperature history throughout the transient period is required.

#### 2.6.1 Unidirectional Transient Heat Conduction

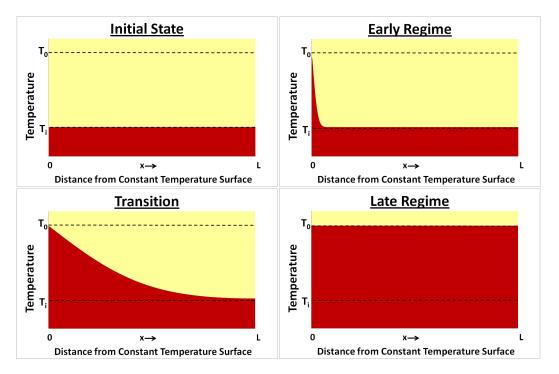

When a solid object undergoes a change from thermal equilibrium, the temperature distribution goes through three different regimes, known as the early regime, the transition stage and the late regime. Each one describes the temperature distribution and rate of heat transfer through the system.

To understand these regimes better, an analysis can be performed for unidirectional conduction by considering a solid bar of length L at an initial starting temperature of  $T_i$  throughout. One end of the bar is suddenly raised to a higher temperature,  $T_0$ , and is held constant at the new temperature. The other surfaces are considered adiabatic.

Once the temperature change is applied, heat flow occurs through the bar due to the imposed temperature gradient. The heat flow continues until thermal equilibrium is achieved and all parts of the bar have increased to the new temperature,  $T_0$ . During this transient phase, the heat conduction can be categorised into three regimes.

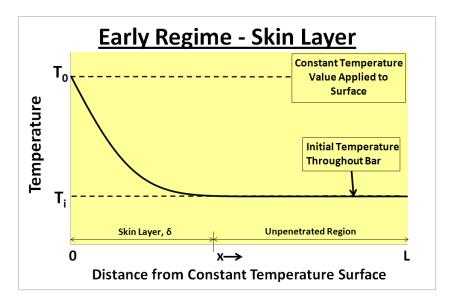

Figure 2.9 shows the temperature profile along the bar at the initial state and during the different regimes. When the temperature has not risen at the far end of the bar, the early regime describes the heat flow. Once the temperature gradients in the bar have decayed and the temperature in the bar can be approximated by a single value,  $T_0$ , the heat flow is in the late regime. The transition period is used for the time in between these two regimes.

Figure 2.9: Typical temperature profiles along the bar for the three regimes which categorises the conduction heat flow. The bar is at an initial temperature,  $T_i$ , before the left surface of the bar is suddenly increased to  $T_0$ .

#### 2.6.1.1 The Early Regime

The early regime is of particular importance for the modelling work conducted in this thesis. The durations of the heat pulses are relatively small from a thermodynamic point of view: most of the heat conduction during this time period will behave within the early regime as there is insufficient time to move to the late regime.

As soon as the temperature at the end of the bar is raised, heat flow in the bar occurs due to the created temperature gradient. Whilst the distance that the heat

has penetrated is less than the length of the bar, the temperature curve follows the same general shape. At the constant temperature boundary (x=0), the temperature is fixed at  $T_0$ . The far end of the bar at x=L, has a temperature equal to  $T_i$ .

The skin layer is a term used to describe the distance that heat has travelled at a certain time during the early regime. This is the distance between x=0 and the point along the bar where the temperature reduces to  $T_i$ . The thickness of the skin layer is dependent on the time elapsed and the thermal properties of the bar.

Figure 2.10: The shape of the temperature through the bar with a constant heat surface during the early regime.

An approximation of the depth of the skin layer,  $\delta$ , can be deduced from the conduction equation, eq.(2.6). As there is no internal heat generation, the equation reduces to:

$$\frac{\partial^2 T}{\partial x^2} = \frac{1}{\alpha} \frac{\partial T}{\partial t} \tag{2.9}$$

Assuming the curvature of the temperature profile over the skin layer,  $\frac{\partial^2 T}{\partial x^2}$ , is constant, the gradient of the temperature curve can be approximated at two points, x=0 and  $x\approx\delta$ :

$$\left(\frac{\partial T}{\partial x}\right)_{x\approx\delta}\approx0\tag{2.10}$$

$$\left(\frac{\partial T}{\partial x}\right)_{x=0} \approx \frac{T_i - T_0}{\delta} \tag{2.11}$$

At the edge of the skin thickness,  $x \approx \delta$ , the temperature approaches  $T_i$  at which point the temperature gradient becomes zero. Therefore the gradient at the edge of the skin layer is assumed to have a gradient of zero. At x=0, where the constant temperature condition is applied, the gradient is assumed to be equal to the change in temperature over the entire skin layer. Using these approximations, the curvature of the temperature across the skin layer can be written:

$$\frac{\partial^2 T}{\partial x^2} \approx \frac{\left(\frac{\partial T}{\partial x}\right)_{x \approx \delta} - \left(\frac{\partial T}{\partial x}\right)_{x=0}}{\delta - 0} \tag{2.12}$$

$$\frac{\partial^2 T}{\partial x^2} \approx -\frac{T_i - T_0}{\delta^2} \tag{2.13}$$

The right hand side of eq.(2.9) relates the thermal properties of the material to the change in temperature over time. This change,  $\frac{\partial T}{\partial t}$ , can be approximated during the early regime. The average temperature within the skin layer changes from  $T_i$  at t=0 to a value approaching  $T_0$  after a time t.

$$\frac{\delta T}{\delta t} \approx \frac{T_0 - T_i}{t - 0} \tag{2.14}$$

Combining eq.(2.14) with eq.(2.13), a form of the conduction equation is produced using the assumptions made about the temperature profile during the early regime:

$$-\frac{T_i - T_0}{\delta^2} \approx \frac{1}{\alpha} \frac{T_0 - T_i}{t - 0} \tag{2.15}$$

From this equation it is possible to arrive at a formula to approximate the thickness of the skin layer at any time during the early regime.

$$\delta \approx \sqrt{(\alpha t)} \tag{2.16}$$

The early regime is assumed while the heat is still penetrating through the solid, i.e. while the skin thickness is less than the length of the solid thickness. The transition period occurs when the heat has reached the end of the bar.

Once the skin layer extends to the entire length of the bar, the assumptions in eqs.(2.10) and (2.11) can no longer be made. The time at which this occurs is the time at which the transition region begins,  $t_T$ . It can be calculated as follows:

$$L \approx \sqrt{(\alpha t_T)}$$

$$t_T \approx \frac{L^2}{\alpha}$$

This transitional time leads to the definition of the Fourier number, Fo, which is an important number used in transient heat conduction. The Fourier number is a dimensionless time that describes the relationship between the distance heat travels in a certain time. A Fourier number of 1 implies that within the time t, the skin layer has fully penetrated a distance L through a solid of thermal diffusivity  $\alpha$ :

$$\frac{\alpha t}{L^2} \approx 1$$

$$Fo = \frac{\alpha t}{L^2} \tag{2.17}$$

The Fourier number can be used to define the times at which the three regimes are dominant during a period of transient conduction. For Fourier numbers less than 1, the heat conduction follows the early regime and Fourier numbers much greater than 1 indicates the late regime is being followed.

Early Regime:

$$Fo \ll 1$$

Late Regime:

$$Fo \gg 1$$

#### 2.6.2 Fourier Number

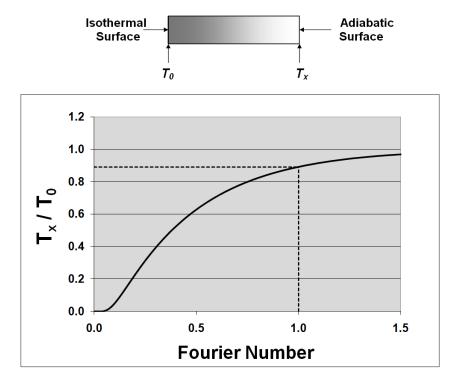

A Fourier number of 1 implies that heat has 'fully penetrated' a distance L during a time t. This can be better defined by quantifying the expression 'fully penetrated'.

Consider the adiabatic bar at an initial constant temperature  $T_i$ , having one end suddenly heated to a constant temperature of  $T_0$ . The induced temperature gradient causes heat flow along the bar. This heat flow continues until a new steady state equilibrium is reached, when all parts of the bar are at temperature  $T_0$ . The temperature at the far end of the bar can be calculated during this transient phase and expressed as a normalised temperature rise, with respect to the final temperature rise  $(T_0 - T_i)$ . When plotted against the Fourier number a plot of the normalised temperature rise is produced, as shown in Figure 2.11. It can be seen that a Fourier number of 1 represents that the temperature at the adiabatic end of the bar has increased to 89% of the final temperature rise.

Figure 2.11: Ratio of the temperature at either end of the bar in relation to Fourier number.

## 2.6.2.1 Significance when Fourier Number Equals 1

The expression 'fully penetrated', which refers to a Fourier number of 1, has been shown to mean that the temperature rise is 89% of the final temperature. This is an important relationship, and will be used later on in the thesis to determine a transient time-constant.

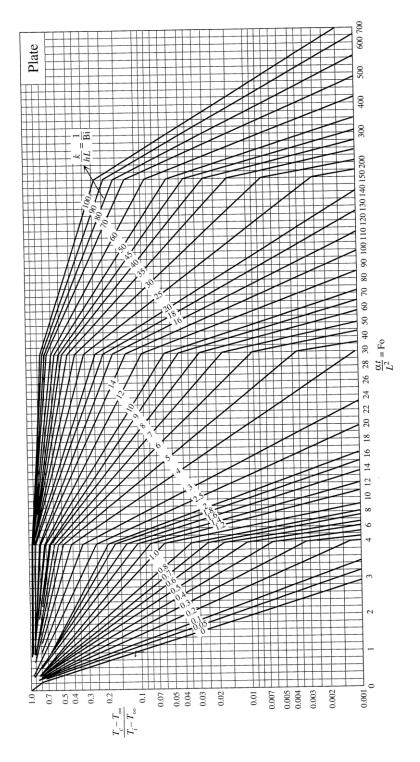

Heisler charts are graphical analysis tools that show the temperature history at the mid-plane of a solid immersed in a fluid. These can also be used to find this correlation. A plot showing the temperature history in the mid-plane of a plate immersed suddenly in a fluid of a different temperature can be found in [10]. The plot lines show the temperature history for different values of 1/Bi, which is equal to k/hL (Bi refers to the Biot number, see Glossary). The scenario in Figure 2.11 represents a sudden increase in temperature, which is representative of an infinite heat transfer coefficient, therefore k/hL=0. This can be seen in the Heisler Chart in Figure 2.12.

The relative temperature rise for a Fourier number of 1 on the line 1/Bi=0 is equal to approximately 0.11, representing a temperature rise at the mid-plane of 89% of the final temperature rise (when the temperature is equal to the fluid temperature).

Figure 2.12: A Heisler Chart, representing the temperature rise at the mid-plane of a plate due to immersion of the plate in a fluid.[10]

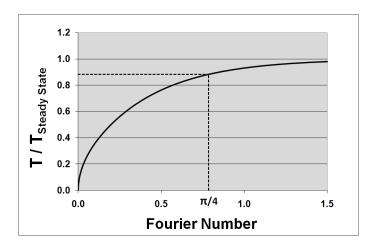

#### 2.6.2.2 Fourier Number Application to Constant Heat Generation

To describe the scenario of power dissipation in an electronic device more accurately, the isothermal end of the bar is replaced with a constant heat flux surface. In this case, the adiabatic end must be replaced by an isothermal surface (held at  $T_i$ ) in order to achieve a steady state solution.

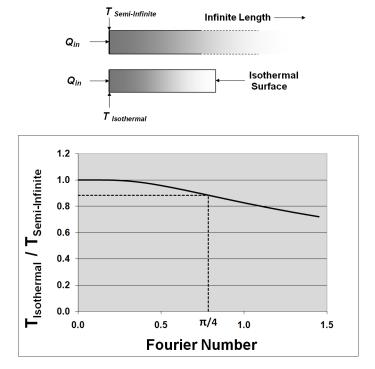

Heat is generated at the heat flux surface and is conducted down the bar. The temperature rise at the heat flux surface can be calculated during the transient phase, and normalised with respect to the final steady state temperature rise. This is plotted against Fourier number, and shown in Figure 2.13.

The temperature at the constant heat flux surface reaches 89% of the steady state value when the Fourier number equals  $\pi/4$ . Thus, when a heat flux surface replaces the raised temperature, the response time of the bar changes.

A further example compares the temperature rise at the constant heat flux surface for two different bars: one with an isothermal end and one that is modelled as semi-infinite. These bars are shown above the plot on right hand side of Figure 2.13.

The temperatures at the heat flux surface will be identical during the early stages of the heat flow. They begin to diverge once the isothermal surface become influential on the temperature at the heat flux surface. A plot of the ratio of the temperatures at the heat flux surfaces against Fourier number at the bottom of Figure 2.13 demonstrates the divergence. The temperature at the heat flux surface with the isothermal end reduces to 89% of that at the semi-infinite heat flux surface after a Fourier number of  $\pi/4$ .

Figure 2.13: *Top:* Temperature rise at the free end of the bar in relation to Fourier number. *Bottom*: Ratio of temperatures at the free end of the bar with different bar length conditions, in relation to Fourier number.

## 2.6.2.3 Defining the Transient Time-Constant

The Fourier number of  $\pi/4$  is very significant to the thesis, and it can be used to formulate an expression for the transient time-constant.

When a heat flux is applied to a surface a Fourier number of  $\pi/4$  demonstrates that the heat has 'fully penetrated' a distance L in time t. The Fourier number equation (eq.(2.17) can be rearranged in terms of time. A time-constant ( $\tau$ ) is defined, which is the time taken for the temperature at the constant heat flux surface to be affected by the geometry at a distance L from the surface:

$$\tau = \frac{\pi}{4} \frac{L^2}{\alpha} \tag{2.18}$$

This time constant is used to calculate the time it takes for the heat to fully penetrate a layer of thickness L. This is very useful as it is possible to analytically calculate the time during a heat pulse that each layer in a device stack-up becomes influential on the device temperature.

# 2.7 Chapter Conclusion

This chapter has provided details of power electronic devices and heat generation mechanisms inside them. The processes of avalanche breakdown and impact ionisation have been described, and their role in device failure explained. In these cases, device failure occurs quickly due to a sudden surge of current through the device.

An overview of the operation of power diodes, MOSFETs and IGBTs has been presented, each of which are relevant to the thesis. It is shown how it is possible to calculate the amount of heat generated in the device at any time. Local electrical resistances and the current flow density within the device dictate where the heat generation occurs during the on-state.

Device failure mechanisms have been identified, including when the temperature exceeds the intrinsic temperature, avalanche breakdown and impact ionisation. These failures are all quick, owing to a sudden increase in current, and temperature. Failures owing to gradual degradation in the stack-up over time have also been discussed, with variations in coefficient of thermal expansion inside the stack being a significant root cause.

The second half of the chapter has introduced some important heat transfer theory. Material properties have been identified using the heat conduction equation, including thermal conductivity and thermal diffusivity.

The three transient heat conduction regimes, early, transitional and late, have been defined. Analysis to the early regime allows the definition of the Fourier number, a highly significant dimensionless time for heat conduction. The Fourier number allows the early and late regime to be defined quantitatively, the transition between the two occurring at a Fourier number of 1.

Further Fourier number analysis provided an equation for a time-constant. This time-constant is used to calculate the time it takes for the heat to fully penetrate a layer of specified thickness in constant heat flux applications. This is very useful as it is

possible to analytically calculate the time during a heat pulse that each layer in a device stack-up becomes influential on the device temperature. The time-constant as presented in the chapter, has not been found in any existing literature.

# Chapter 3

# Literature Overview

This chapter presents a literature review, summarising the state-of-the-art of relevant research and technical areas. The overview begins by discussing cooling technologies used in the semiconductor industry. Different technologies are considered as candidates for reducing the transient temperature in semiconductor dies. Current double-sided device cooling techniques are then examined, with examples given of how it is currently implemented. This is followed by an overview of semiconductor cooling techniques specifically aimed at reducing transient temperatures.

The subsequent section of the literature overview examines different modelling methods for predicting transient semiconductor device temperatures. This includes both analytical and thermal resistance network methods. Different modelling techniques are discussed, together with some published results.

Semiconductor reliability will then be considered. Reliability is shown to be an important issue for semiconductor devices, as the thermal cycling experienced by the stack components induces thermal stresses in the different stack components. This follows on to a discussion of novel composite materials and alternatives to solder for die attachment. The motivation for this examination stems from the desire to optimise the effectiveness of the heat sink, which may involve the employment of novel materials with attractive thermal properties.

# 3.1 Cooling Technologies for Semiconductors

The importance of keeping electronics cool has been recognised for many years, resulting in a wide range of literature presenting different cooling techniques. The state-of-the-art of electronics cooling has been examined in order to identify any techniques which may be relevant to the problem under investigation.

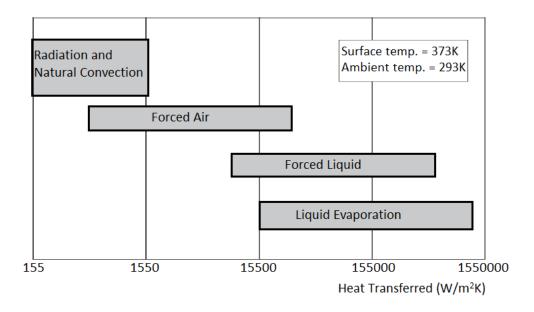

Various methods have been implemented for cooling electronic devices. Anandan and Ramalingam [1] present an overview of these different methods and technologies. Many things must be considered when matching a cooling technology to a specific scenario, such as cost, the heat transfer rate required and size constraints. Scott [12] classified all of the methods into four categories of different heat transfer effectiveness. These are demonstrated in Figure 3.1 which shows the rate of heat transfer between two surfaces with a temperature difference of 80°C. It can be seen that high heat transfer rates are only achievable through forced liquid convection (e.g. water pumped, jet impinged, sprayed) or liquid evaporation (e.g. heat pipes).

Figure 3.1: Range of conventional heat transfer modes.[1]

#### 3.1.1 Forced Liquid Convection Techniques

Cooling electronic devices by spraying them directly with liquid is discussed by Anandan and Ramalingam [1], who identifies advantages of such a method as:

- the thermal resistance in the bonding layer between heat source and heat spreader is eliminated

- the ratio between power spent and heat removed decreases faster for spray cooling than channel cooling

However, it is also pointed out that the choice of liquid is important; whether it is non-conducting or a di-electric liquid. A thin protective layer is coated on components to protect against electrical shorts.

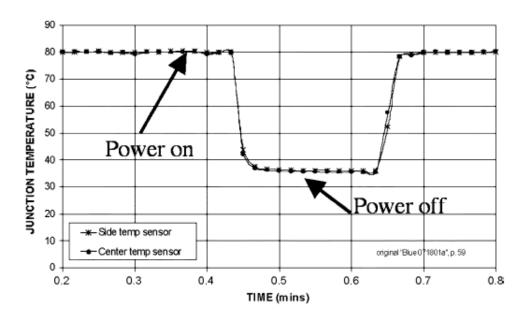

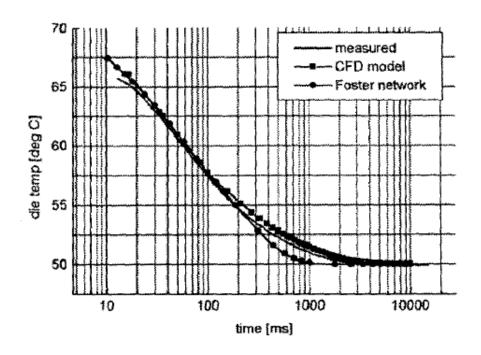

Cader et al. [13] conduct a test to quantify the ability of spray cooling to handle transient power dissipation at the die. Spray cooling the die is reported to provide a shorter transient time between steady state temperatures. At device switch-on and switch-off, the junction temperature (seen in Figure 3.2) behaves 'like a step function', whereas a lidded device (a completely sealed package with an inert gas injected which surrounds the device) 'follows more of an exponential decay when the power is turned off, and an exponential ramp when the power is turned on'. The unlidded data is not presented in the paper, and is only compared qualitatively.

The resolution of the time axis in Figure 3.2 is relatively poor; only three data points define the transient curve. It should also be noted that data from the lidded device is not presented for comparison. It is therefore difficult to assess the benefits of the spray cooling method.

A further paper by Cader and Tilton [14] gives examples of how spray cooling has been implemented successfully in high heat flux applications.

Garimella [15] states that enhanced heat transfer rates obtained with impinging jets make them suitable for cooling electronic devices with very high heat dissipation rates.

Figure 3.2: Junction temperature transient response to spray cooling of bare die. [13]

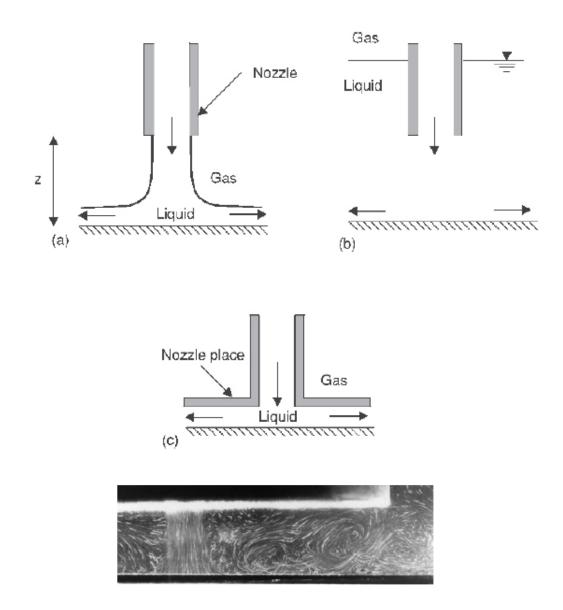

The effectiveness of a jet impingement system is dependent on the configuration of the jet setup, demonstrated in Figure 3.3. The heat transfer is increased by submerging the jet [16]. However, the heat transfer rate is reduced when the jet outflow is confined, as it is in many electronics cooling applications [17].

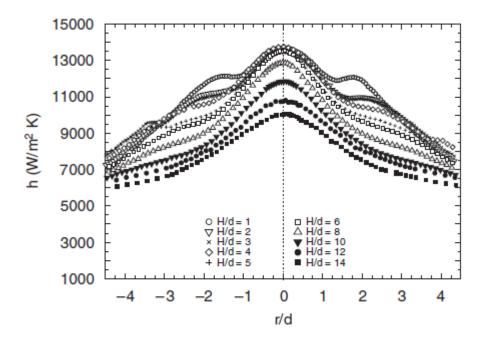

Garimella [18] presents a review of confined jets. Jet geometry configurations have been investigated with the aim of maximising the heat transfer at the impinged surface. Garimella [19] varies the ratio of orifice diameter to height of jet from the surface, and presents the variation of heat transfer in the local area of the jet (Figure 3.4). The results show the significance of the jet configuration on the effectiveness of the jet.

Further enhancements to the heat transfer rate have been achieved through surface enhancements. Finned surfaces have decreased the thermal resistance of liquid jet impingement by approximately 50%. Further roughening of the spreader plate decreased the thermal resistance by as much as 80% [20].

Garimella [15] also discusses the suitability of microchannel cooling for power electronics due to the high transfer coefficients achievable and their compact size. It is

40

Figure 3.3: *Top*: Jet impingement configurations *a*) free-surface jet, *b*) submerged-jet, *c*) confined submerged-jet. *Bottom*: Flow field visualisation in a confined and submerged liquid jet.[18]

claimed that the large pumping requirements are the main reason they are not widely used on a commercial scale. According to Wilson and Simons [21], in many practical cases the small flow rate within micro-channels produces laminar flow resulting in a heat transfer coefficient inversely proportional to the hydraulic diameter. Thus, smaller channels achieve greater heat transfer coefficients. However, the pressure drop in the channels increases with the inverse of the second power of the channel width.

Figure 3.4: Variation in local heat transfer coefficient with jet to surface distance (d) for Re=13000 (based on orifice diameter, d) where d=1.59mm.

Jet impingement and microchannel cooling for high heat flux applications were compared by Lee and Vafai [22] who concluded that microchannel cooling is more effective for areas smaller than  $7 \times 7$  cm [21].

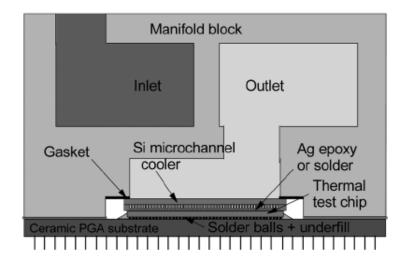

Figure 3.5: Schematic cross-section of the microchannel cooler integrated onto a high-power chip.[23]

Colgan et al. [23] published a practical implementation of a silicon microchannel cooler for high-power chips. Due to practical and cost reasons, a separate microchannel cold plate was bonded to the back of the chip rather than forming the microchannels directly on the chip (Figure 3.5). Power densities in excess of 400W/cm<sup>2</sup> are reported, for a flow of 1.2l/min at 30kPa.

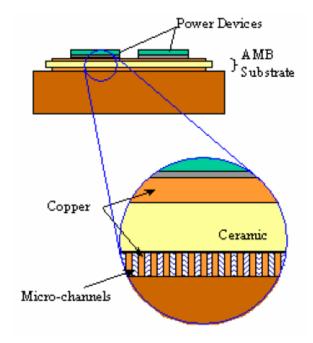

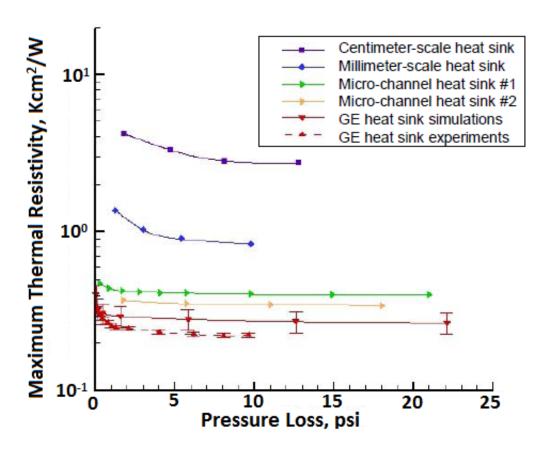

A further microchannel design is presented by Solovitz et al. [24]. A microchannel was built into the substrate of a high power device as shown in Figure 3.6. Sixty-five microchannels were manufactured, with a width of  $100\mu m$  and w height of  $300\mu m$ . The results, also presented in Figure 3.6, demonstrate a thermal performance 'superior to any existing micro-channel heat sink with a comparable electrical assembly'.

Lorenzen et al. [25] demonstrate the use of chemical-vapour-deposited (CVD) diamond as a heat spreader material to enhance a microchannel cooler. The high thermal conductivity of CVD diamond reduces the thermal resistance between the heat source and microchannel, increasing heat diffusivity.

A study by Bergles et al. [26] reports that two-phase microchannels require 20 times less pumping than single-phase liquid microchannels to achieve the same heat sink thermal resistance. However, fluctuations have been witnessed in local heat transfer coefficients when boiling heat transfer in microchannels has been tested.

Figure 3.6: *Top:* Conceptual micro-channel heat sink design. *Bottom:*Thermal resistivity for micro-channel heat sink at various diode power dissipation and coolant flow rates. Note units of Kcm<sup>2</sup>/W for thermal resistivity (the thermal resistance per square-centimeter of the device) which allows a direct comparison between different sized devices. [24]

## 3.1.2 Double-Sided Chip Cooling

A range of different double-sided chip cooling techniques have been investigated. Cooling both sides of the chip produces an additional thermal route for generated heat.

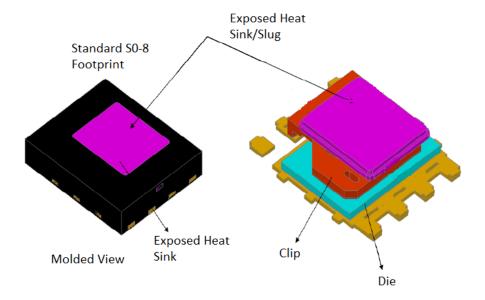

Herbsommer et al. [27] and Charboneau et al. [28] present different double sided cooling techniques. Herbsommer et al. [27] point out that most current packaging technologies have poor junction-to-top thermal resistances, making it difficult to have any significant heat flowing to the top of the device. The DUAL COOL $^{TM}$  technology shown in Figure 3.7 creates a high thermal resistance by more than a factor of ten, compared to standard solutions.

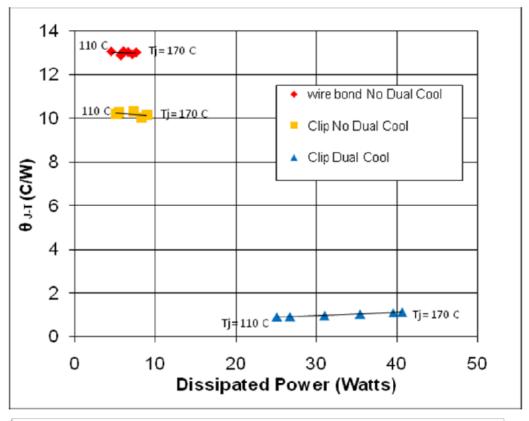

The thermal resistance and power dissipated was measured and compared to different constructions: a) a wire bond package b) a clip package with a 70% die coverage with a 10mm thick clip c) the same clip package but with dual cool technology. The results show a dramatic increase in the heat dissipated through the top of the package due to the decrease in the thermal resistance. As a result, the junction temperature is reduced during operation. The results presented are shown in Figure 3.8.

Figure 3.7: Construction of a dual cool device.[27]

Figure 3.8: *Top:* Thermal resistance junction-top vs power. *Bottom:* Thermal performance comparison for different packaging technologies.[27]

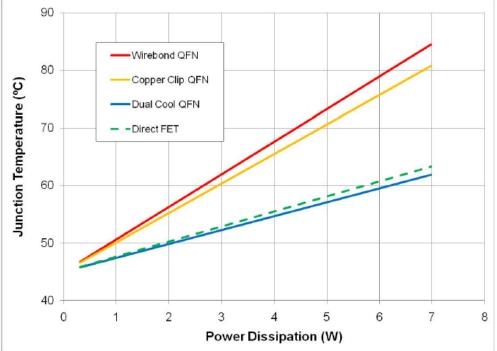

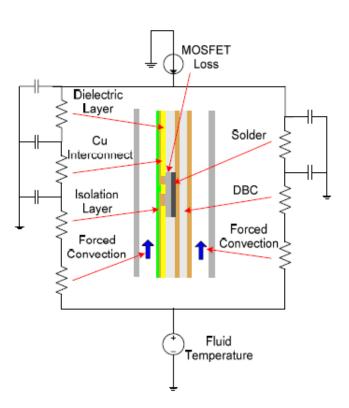

Charboneau et al. [28] demonstrate double-sided liquid cooling on a power semiconductor device. The CoolMOS power module shown in Figure 3.9 is packaged so that both sides of the module can be cooled by parallel forced water convection, as indicated by arrows.

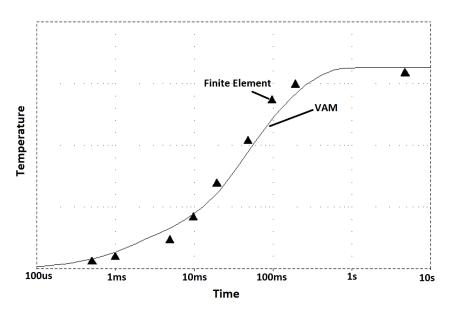

Modelling results were obtained for the packages cooled on a single side and on both sides, as well as experimental results for the package cooled on one side. The results obtained during device switch-on is shown in Figure 3.10. Comparing the modelling curves, it can be seen that the double sided cooling method suppresses the device temperature rise during the transient phase. The steady-state temperature achieved for the double-sided cooled device is less than that of the device cooled on a single-side.

47

Figure 3.9: *Top:* MOSFET based embedded power structure. *Bottom:* Electrothermal model for the structure with double-sided liquid cooling. The top MOSFET surface is protected by the Interconnection Isolation, which allows fluid flow over the top surface, as indicated int he bottom diagram. This provides an additional thermal path for heat flow to ambient. [28]

Figure 3.10: The thermal response of the device during switch-on for different cooling techniques.[28]

#### 3.1.3 Thermal Transients

Despite the large volume of literature and research surrounding the electronics cooling industry, relatively little focuses on the thermal management of transients. Work done by Cader et al. [13] and Charboneau et al. [28] consider the transient response of the devices, however on a relatively large time-scale. Thermal designs for shorter transient, in the order of magnitude of milli-seconds rather than seconds, are not as widely considered.

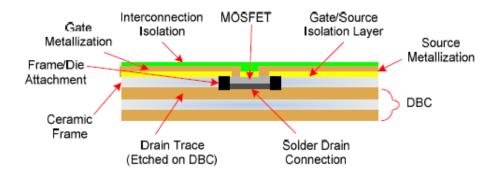

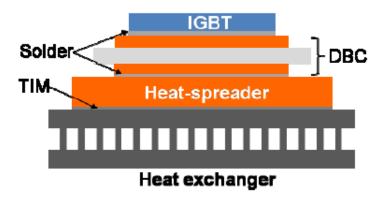

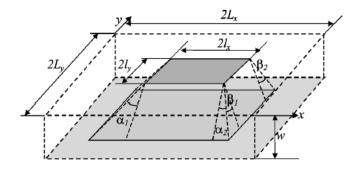

Ngo et al. [29] investigate the geometry of the heat spreader and heat transfer coefficient of the heat exchanger on both steady-state and transient temperature. The geometry examined is shown in Figure 3.11. They state that during a thermal transient, the heat spreader works as a thermal capacitance to store thermal energy, which reduces the peak temperature in the module. However, a large heat spreader does not necessarily result in a better transient thermal performance.

Figure 3.11: Structure for conventional power module with heat exchanger.[29]

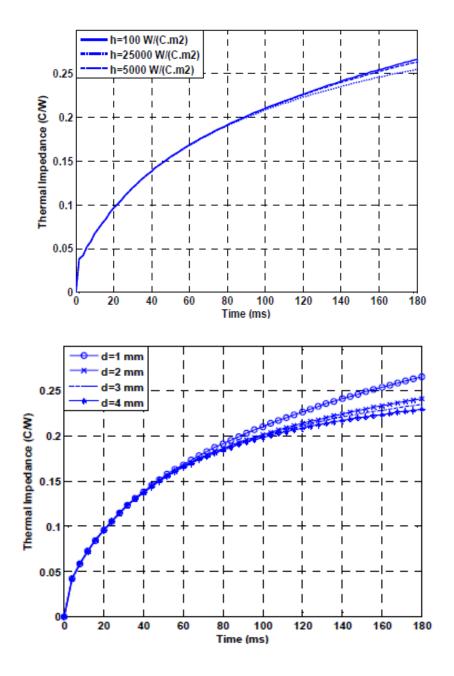

Results are obtained from thermal modelling using a finite element analysis package. The thermal impedance is calculated during a transient when different heat spreader thicknesses are used, and also when different heat transfer coefficients are modelled in the heat exchanger.

Figure 3.12 shows that for transients less than 50ms, the heat transfer coefficient does not affect the thermal impedance. Beyond 50ms, a large change to the heat transfer

coefficient has only a limited effect on the thermal impedance. This is similar for the thickness of the heat spreader.

Figure 3.12: Variation in thermal impedance during a pulse: Top: for different heat transfer coefficients in the heat exchanger and Bottom: for different heat spreader thicknesses (d).[29]

A simpler design procedure is presented to achieve the minimum temperature rise during the pulse, for which the time constant,  $\tau$ , of the module must be greater than

the pulse length. For any given pulse length, the time constant can be calculated using eqs.(3.1) and (3.2). This allows the thickness of the heat spreader to be calculated based on the table in Figure 3.13. For transients of 120ms or greater, a 3mm heat spreader is preferred, as increasing the thickness beyond 3mm cannot improve the thermal impedance further, as seen in Figure 3.12.

$$\tau_i = R_i C_i = \frac{d_i}{k_i A_i} \rho_i c_{pi} d_i A_i = \frac{d_i^2 \rho_i c_{pi}}{k_i}$$

(3.1)

where d is the layer thickness.

$$\tau = \sum \tau_i \tag{3.2}$$

# CALCULATED TIME CONSTANT FOR EACH LAYER IN THE POWER MODULE

|                  | IGBT   | Solder  | DBC     | Heat-spreader              |

|------------------|--------|---------|---------|----------------------------|

| Time<br>Constant | 0.5 ms | 0.28 ms | 39.4 ms | $d^2 \cdot 8.6 \text{ ms}$ |

<sup>\*</sup>d is the thickness of the heat-spreader in mm

Figure 3.13: A table of the calculated time-constant for each layer.[29]

# 3.2 Modelling the Thermal Response of Devices

Accurate predictions of the temperature response of power semiconductor devices is important for the purposes of design. Being able to model the thermal response of different geometry configurations allows optimum designs to be achieved without the timely and costly procedure of testing each configuration experimentally. Modelling small variations to the design of the device structure allows the sensitivity of design changes to be analysed and an optimum device design to be derived.

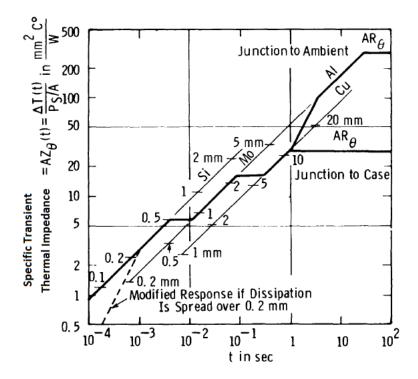

# 3.2.1 Analytical Approaches

Early attempts at modelling the temperature rise in a semiconductor device during a thermal transient took a mathematical analytical approach. The computational power required to perform large series of equations was rare and experimental technology for measuring device temperatures at high frequencies either was not available or was very expensive.