# Massively-Parallel and Concurrent SVM Architectures

P.B.A. Phear, B.E. (Hons.)

Thesis submitted to the University of Nottingham for the degree of Master of Philosophy

March 2018

## Abstract

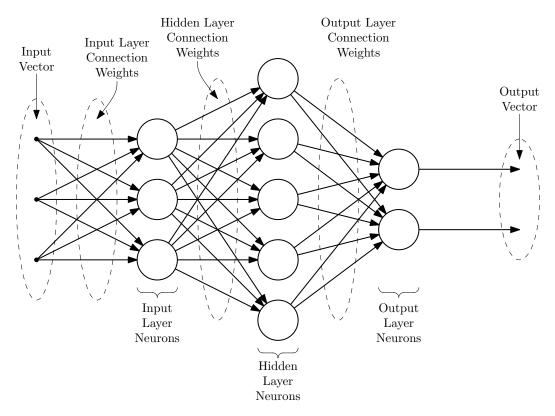

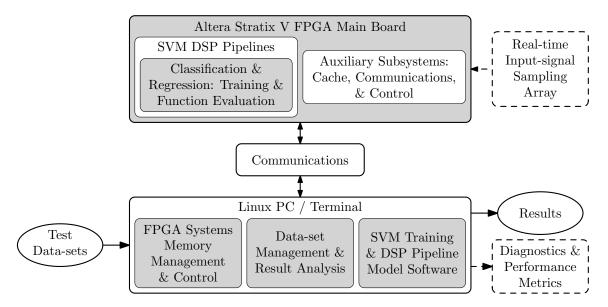

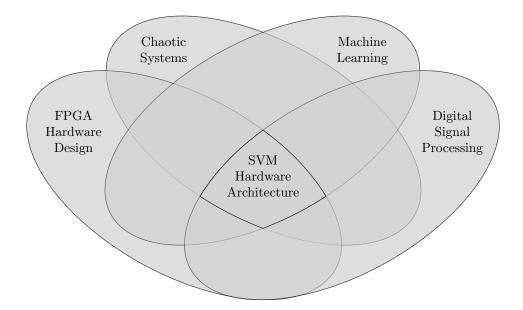

This work presents several Support Vector Machine (SVM) architectures developed by the Author with the intent of exploiting the inherent parallel structures and potentialconcurrency underpinning the SVM's mathematical operation. Two SVM training subsystem prototypes are presented - a brute-force search classification training architecture, and, Artificial Neural Network (ANN)-mapped optimisation architectures for both SVM classification training and SVM regression training. This work also proposes and prototypes a set of parallelised SVM Digital Signal Processor (DSP) pipeline architectures. The parallelised SVM DSP pipeline architectures have been modelled in C and implemented in VHDL for the synthesis and fitting on an Altera Stratix V FPGA. Each system presented in this work has been applied to a problem domain application appropriate to the SVM system's architectural limitations - including the novel application of the SVM as a chaotic and non-linear system parameter-identification tool.

The SVM brute-force search classification training architecture has been modelled for datasets of 2 dimensions and composed of linear and non-linear problems requiring only 4 support vectors by utilising the linear kernel and the polynomial kernel respectively. The system has been implemented in Matlab and non-exhaustively verified using the holdout method with a trivial linearly separable classification problem dataset and a trivial nonlinear XOR classification problem dataset. While the architecture was a feasible design for software-based implementations targeting 2-dimensional datasets the architectural complexity and unmanageable number of parallelisable operations introduced by increasing data-dimensionality and the number of support vectors subsequently resulted in the Author pursuing different parallelised-architecture strategies.

Two distinct ANN-mapped optimisation strategies developed and proposed for SVM classification training and SVM regression training have been modelled in Matlab; the architectures have been designed such that any dimensionality dataset can be applied by configuring the appropriate dimensionality and support vector parameters. Through Monte-Carlo testing using the datasets examined in this work the gain parameters inherent in the architectural design of the systems were found to be difficult to tune, and, system convergence to acceptable sets of training support vectors were unachieved. The ANN-mapped optimisation strategies were thus deemed inappropriate for SVM training with the applied datasets without more design effort and architectural modification work.

The parallelised SVM DSP pipeline architecture prototypes data-set dimensionality, support vector set counts, and latency ranges follow. In each case the Field Programmable Gate Array (FPGA) pipeline prototype latency unsurprisingly outclassed the corresponding C-software model execution times by at least 3 orders of magnitude. The SVM classification training DSP pipeline FPGA prototypes are compatible with data-sets spanning 2 to 8 dimensions, support vector sets of up to 16 support vectors, and have a pipeline latency range spanning from a minimum of 0.18 microseconds to a maximum of 0.28 microseconds. The SVM classification function evaluation DSP pipeline FPGA prototypes are compatible with data-sets spanning 2 to 8 dimensions, support vector sets of up to 32 support vectors, and have a pipeline latency range spanning from a minimum of 0.16 microseconds to a maximum of 0.24 microseconds. The SVM regression training DSP pipeline FPGA prototypes are compatible with data-sets spanning 2 to 8 dimensions, support vector sets of up to 16 support vectors, and have a pipeline latency range spanning from a minimum of 0.20 microseconds to a maximum of 0.30 microseconds. The SVM regression function evaluation DSP pipeline FPGA prototypes are compatible with data-sets spanning 2 to 8 dimensions, support vector sets of up to 16 support vectors, and have a pipeline latency range spanning from a minimum of 0.20 microseconds to a maximum of 0.30 microseconds.

Finally, utilising LIBSVM training and the parallelised SVM DSP pipeline function evaluation architecture prototypes, SVM classification and SVM regression was successfully applied to Rajkumar's oil and gas pipeline fault detection and failure system legacy dataset yielding excellent results. Also utilising LIBSVM training, and, the parallelised SVM DSP pipeline function evaluation architecture prototypes, both SVM classification and SVM regression was applied to several chaotic systems as a feasibility study into the application of the SVM machine learning paradigm for chaotic and non-linear dynamical system parameter-identification. SVM classification was applied to the Lorenz Attractor and an ANN-based chaotic oscillator to a reasonably acceptable degree of success. SVM classification was applied to the Mackey-Glass attractor yielding poor results. SVM regression was applied Lorenz Attractor and an ANN-based chaotic oscillator yielding average but encouraging results. SVM regression was applied to the Mackey-Glass attractor yielding poor results.

# Contents

| Ab  | stra | act                                                                                                                                                        | i   |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Co  | nter | its                                                                                                                                                        | ii  |

| Pre | efac | e                                                                                                                                                          | vi  |

|     | 0.1  | Supporting Publications                                                                                                                                    | vi  |

|     | 0.2  | List of Figures                                                                                                                                            | vi  |

|     | 0.3  | List of Tables                                                                                                                                             | ii  |

|     | 0.4  | List of Algorithm and Code Listings                                                                                                                        | v   |

| Glo | ossa | ry xv                                                                                                                                                      | ii  |

|     | 0.5  | Notation                                                                                                                                                   | ii  |

|     | 0.6  | Acronyms and Abbreviations                                                                                                                                 | iii |

| 1   | Intr | roduction                                                                                                                                                  | 1   |

|     | 1.1  | Problem Statement                                                                                                                                          | 8   |

|     | 1.2  | Research Objectives                                                                                                                                        | 8   |

|     | 1.3  | System Overview                                                                                                                                            | 9   |

|     | 1.4  | Research Scope                                                                                                                                             | 9   |

|     | 1.5  | Subject Area Contributions                                                                                                                                 | 0   |

|     | 1.6  | Organisation 1                                                                                                                                             | 0   |

| 2   | Pre  | liminaries 1                                                                                                                                               | 2   |

|     | 2.1  | Linear Algebra                                                                                                                                             | 2   |

|     |      | 2.1.1 Vectors and Matrices                                                                                                                                 | 2   |

|     |      | 2.1.2 Vector Spaces $\ldots \ldots \ldots$ | 3   |

|     |      | 2.1.3 Lines, Planes, and Hyperplanes                                                                                                                       | 4   |

|     | 2.2  | Optimisation Problems                                                                                                                                      | .6  |

|     | 2.3  | Taylor Series    1                                                                                                                                         | 7   |

|     | 2.4  | State-Space Methods                                                                                                                                        | 7   |

| 3   | Lite | erature Review 1                                                                                                                                           | 9   |

|     | 3.1  | Machine Learning with Support Vector Machines                                                                                                              | 9   |

|     |      | 3.1.1 Maximum-Margin Classifiers and SVMs                                                                                                                  | 9   |

|     |      | 3.1.1.1 Maximum-Margin Classifiers                                                                                                                         | 9   |

|   |                | 3.1.1.2 Su           | pport Vector Machine Classifiers                                                                           |

|---|----------------|----------------------|------------------------------------------------------------------------------------------------------------|

|   |                | 3.1.1.3 Sta          | atistical Learning Theory                                                                                  |

|   |                | 3.1.1.4 SV           | M Training and Optimisation Techniques                                                                     |

|   |                | 3.1.1.5 M            | ılti-class SVM Classifiers                                                                                 |

|   |                | 3.1.1.6 Re           | gression and Prediction with SVMs                                                                          |

|   |                | 3.1.2 Unsupervise    | d Learning $\ldots \ldots 43$ |

|   |                | 3.1.2.1 Le           | gacy SVM System                                                                                            |

|   |                | 3.1.2.2 k-l          | Means Clustering                                                                                           |

|   |                | 3.1.3 SVM Hardv      | vare Implementations                                                                                       |

|   | 3.2            |                      | Yield Programmable Gate Arrays       46                                                                    |

|   |                | 0 0                  | ammable Gate Array Logic                                                                                   |

|   |                |                      | the Integrated Circuit Market                                                                              |

|   | 3.3            |                      | essing $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $50$                                          |

|   |                |                      | SP Fundamentals                                                                                            |

|   |                |                      | chines and Systolic Signal Processing                                                                      |

|   |                |                      | DSP Platform                                                                                               |

|   | 3.4            |                      | ear Systems                                                                                                |

|   | 0.1            |                      | and Quantification of Chaos                                                                                |

|   |                | •                    | illators $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $54$                      |

|   |                |                      | Embedding and State-space Reconstruction 57                                                                |

|   |                | State space          |                                                                                                            |

| 4 | $\mathbf{SVI}$ | A System Archite     | ctures and Scientific Method 60                                                                            |

|   | 4.1            | SVM Training Stra    | tegies                                                                                                     |

|   |                | 4.1.1 Brute-force    | SVM Training                                                                                               |

|   |                | 4.1.2 Combined H     | Exterior Penalty and Barrier Function Optimisation 68                                                      |

|   |                | 4.1.3 Augmented      | Lagrange Multiplier Optimisation                                                                           |

|   | 4.2            | SVM Test-Rig Syst    | em Hardware Architecture                                                                                   |

|   |                | 4.2.1 FPGA Plat      | Form and Implementation Considerations                                                                     |

|   |                | 4.2.2 Design Meth    | nodology Considerations                                                                                    |

|   |                | 4.2.3 FPGA Deve      | lopment Platform Considerations                                                                            |

|   |                | 4.2.4 Ancillary So   | ftware Tools                                                                                               |

|   |                | 4.2.5 System Des     | gn Considerations                                                                                          |

|   |                | 4.2.6 SVM Test-F     | tig Design and Implementation    89                                                                        |

|   | 4.3            | SVM DSP Pipeline     | s                                                                                                          |

|   | 4.4            | Scientific Methodol  | ogies                                                                                                      |

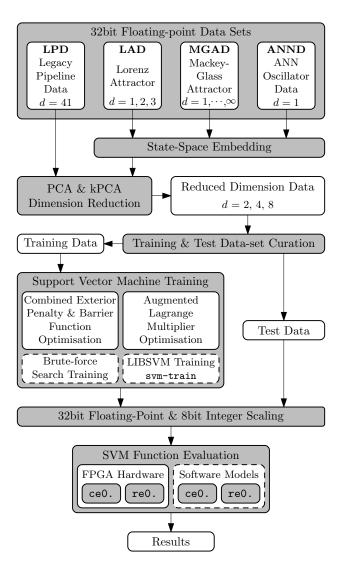

|   |                | 4.4.1 Data-sets an   | d Machine Learning Experimental Overview 108                                                               |

|   |                |                      | ccessing and Application of SVM Systems 112                                                                |

|   |                |                      | gacy Pipeline Data Methodology                                                                             |

|   |                |                      | aotic Systems Data Methodology                                                                             |

|   |                |                      |                                                                                                            |

| 5 | Res            |                      | 116                                                                                                        |

|   | 5.1            |                      |                                                                                                            |

|   | 5.2            | Electrical Results . |                                                                                                            |

|    | 5.3   | Machi   | ne Learni  | ing Results                    | . 142 |

|----|-------|---------|------------|--------------------------------|-------|

|    |       | 5.3.1   | SVM Cl     | lassification Results          | . 142 |

|    |       |         | 5.3.1.1    | C-LPD                          | . 142 |

|    |       |         | 5.3.1.2    | C-LAD                          | . 143 |

|    |       |         | 5.3.1.3    | C-MGAD                         | . 144 |

|    |       |         | 5.3.1.4    | C-ANND                         | . 144 |

|    |       | 5.3.2   | SVM Re     | egression Results              | . 144 |

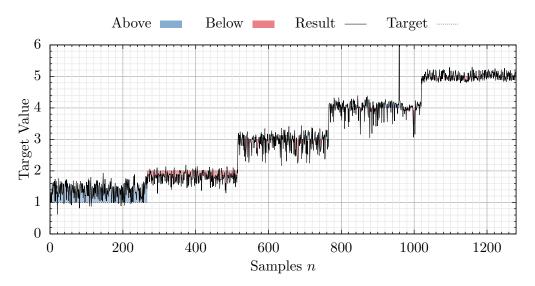

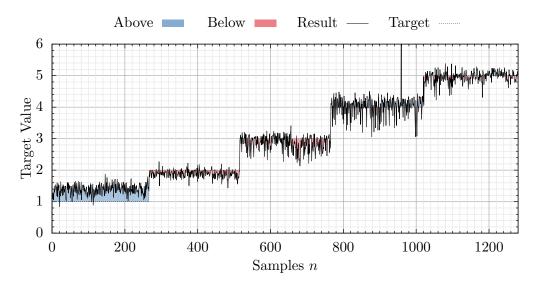

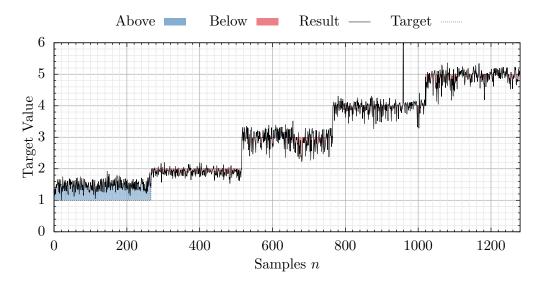

|    |       |         | 5.3.2.1    | R-LPD                          | . 145 |

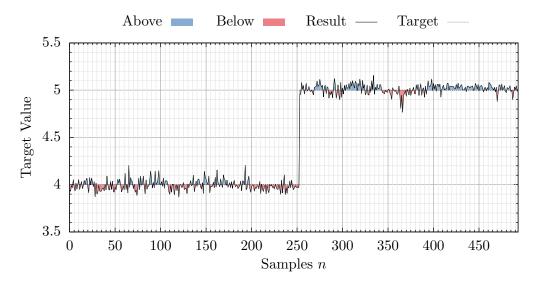

|    |       |         | 5.3.2.2    | R-LAD                          | . 148 |

|    |       |         | 5.3.2.3    | R-MGAD                         | . 150 |

|    |       |         | 5.3.2.4    | R-ANND                         | . 152 |

| 6  | Dise  | cussior | n          |                                | 155   |

| Ū  | 6.1   |         |            | ecture Training Discussion     |       |

|    | 6.2   |         |            | re and DSP Pipeline Discussion |       |

|    | 6.3   |         |            | nd Benchmarks Discussion       |       |

|    | 6.4   |         |            | lts Discussion                 |       |

|    | 6.5   |         |            | ing Results Discussion         |       |

| 7  | Con   | clusio  | n          |                                | 166   |

|    | 7.1   | Recon   | nmendatio  | ons and Future Work            | . 166 |

|    | 7.2   |         |            |                                |       |

| Aj | ppen  | dices   |            |                                | 169   |

|    | App   | endix A | <b>4</b> . |                                |       |

|    |       | SVM     | DSP Inst   | ruction Set                    | . 169 |

|    | App   |         |            | Pipeline Designs               |       |

|    |       |         |            | nented Pipeline Entities       |       |

| Re | efere | nces    |            |                                | 195   |

# Preface

#### 0.1 Supporting Publications

- R. K. Rajkumar, P. B. A. Phear, D. Isa, W. Y. Wan, and N. A. Akram, "Real-time pipeline monitoring system and method thereof," Malaysian Patent Application PI 2015704444, December 4, 2015.

- P. B. A. Phear, R. K. Rajkumar, and D. Isa, "Efficient non-iterative fixed-period SVM training architecture for FPGAs," in *Proc. of the 39th Annu. Conf. of the IEEE Industrial Electronics Society (IECON 2013)*, Vienna, Austria, November 2013.

#### 0.2 List of Figures

| 1.1 | Mankind's past, present, and possible future, illustrated as discrete evolu-                                                       |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

|     | tionary leaps forward, from left to right, in time                                                                                 | 2  |

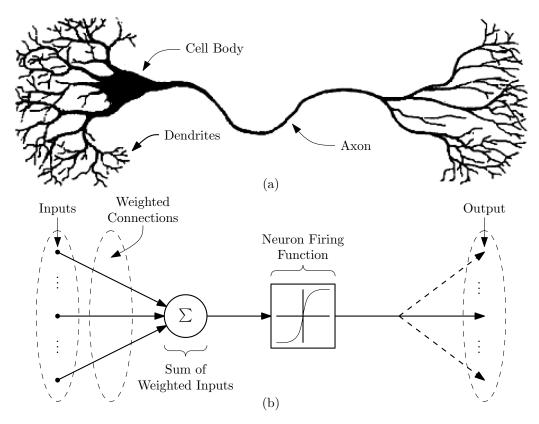

| 1.2 | The Perceptron was modelled on biological neuron function; (a) a biological                                                        |    |

|     | neuron structure and (b) Rosenblatt's artificial neuron structure                                                                  | 2  |

| 1.3 | Royal McBee LGP-30 vacuum-tube computer, as used by Edward Lorenz,                                                                 |    |

|     | complete with operator.                                                                                                            | 4  |

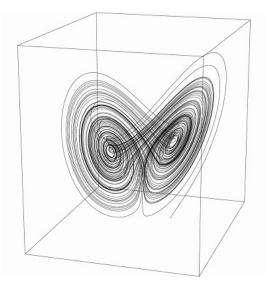

| 1.4 | A three-dimensional state-space or phase-space reconstruction of the Lorenz                                                        |    |

|     | Attractor                                                                                                                          | 5  |

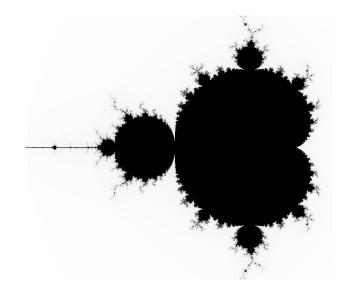

| 1.5 | The Mandelbrot Set fractal, the iteration of $z \to z^2 + c$ on every complex                                                      |    |

|     | number $c$ on the complex plane; $c$ belongs to the set, and hence is coloured                                                     |    |

|     | black, if the iterated result $z$ remains bounded, oscillates chaotically, or                                                      |    |

|     | does not tend to infinity                                                                                                          | 6  |

| 1.6 | An example of a Multilayer Perceptron                                                                                              | 7  |

| 1.7 | High-level block-diagram overview of the SVM Hardware Architecture and                                                             |    |

|     | Auxiliary subsystems and accompanying tools, models, and software                                                                  | 9  |

| 1.8 | Venn diagram illustrating the four subject areas covered in this work's                                                            |    |

|     | scope and its subsequent research contributions                                                                                    | 10 |

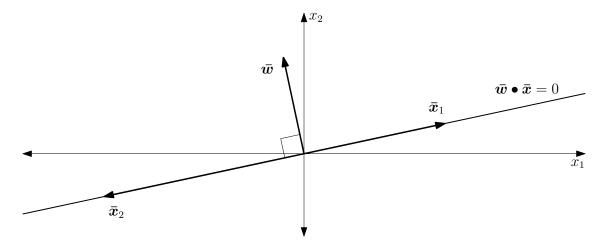

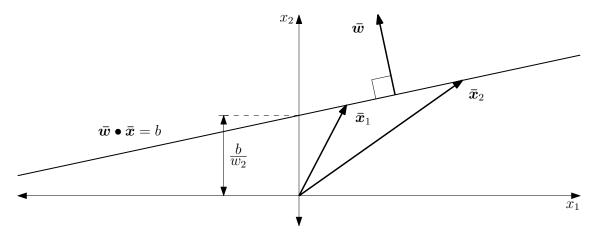

| 2.1 | Line in $\mathbb{R}^2$ expressed as a dot product, $\bar{\boldsymbol{w}} \bullet \bar{\boldsymbol{x}} = 0$ , the orthogonal normal |    |

| 2.1 | vector $\bar{w}$ , and two possible position vectors, $\bar{x_1}$ and $\bar{x_2}$ , of which both lie                              |    |

|     | on, and are orthogonal to, the line. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                  | 15 |

|     |                                                                                                                                    | 10 |

| 2.2  | Line in $\mathbb{R}^2$ expressed as a dot product, $\bar{\boldsymbol{w}} \bullet \bar{\boldsymbol{x}} = b$ , the orthogonal normal vector $\bar{\boldsymbol{w}}$ , and two possible position vectors, $\bar{\boldsymbol{x_1}}$ and $\bar{\boldsymbol{x_2}}$ , of which both are  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | points on the line. $\dots \dots \dots$                                                                                                                                          |

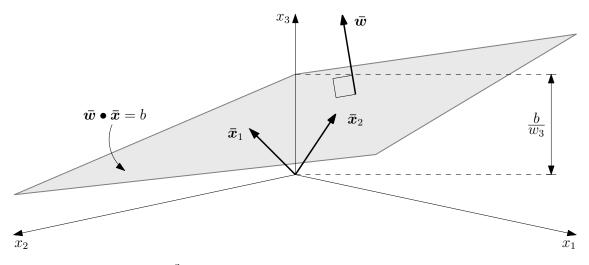

| 2.3  | Plane in $\mathbb{R}^3$ expressed as a dot product, $\bar{\boldsymbol{w}} \bullet \bar{\boldsymbol{x}} = b$ , the orthogonal normal vector $\bar{\boldsymbol{w}}$ , and two possible position vectors, $\bar{\boldsymbol{x_1}}$ and $\bar{\boldsymbol{x_2}}$ , of which both are |

|      | points on the plane.                                                                                                                                                                                                                                                             |

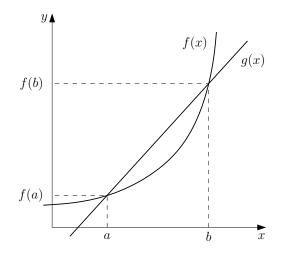

| 2.4  | The linear function $g(x)$ intersects the convex function $f(x)$ at points $(a, f(a))$ and $(b, f(b))$ .                                                                                                                                                                         |

|      |                                                                                                                                                                                                                                                                                  |

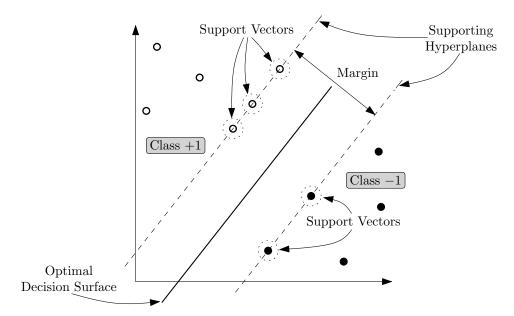

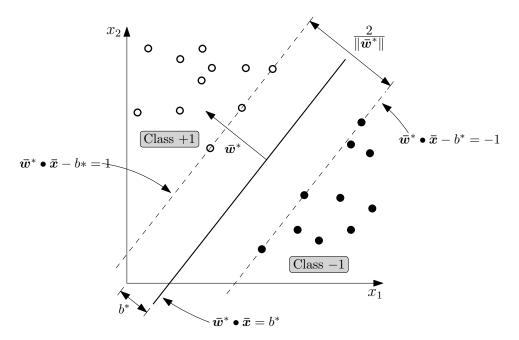

| 3.1  | Optimal decision surface with its two supporting hyperplanes separating two linearly separable classes.                                                                                                                                                                          |

| 3.2  | Maximum-Margin class separation example                                                                                                                                                                                                                                          |

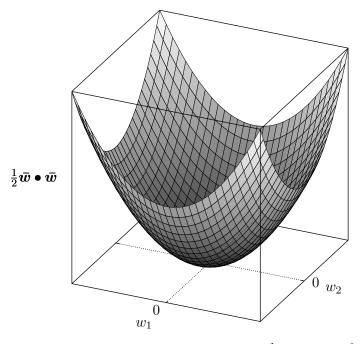

| 3.3  | Objective function $\frac{1}{2}\bar{\boldsymbol{w}} \bullet \bar{\boldsymbol{w}}$ in $\mathbb{R}^2$                                                                                                                                                                              |

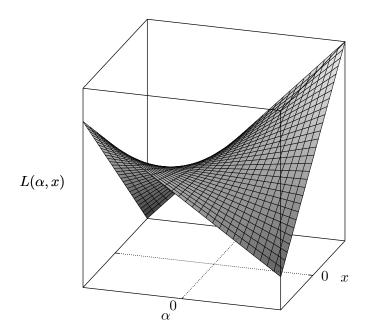

| 3.4  | Lagrangian objective function $L(\alpha, x) = \frac{1}{2}x^2 - \alpha(x-2)$ in $\mathbb{R}^2$                                                                                                                                                                                    |

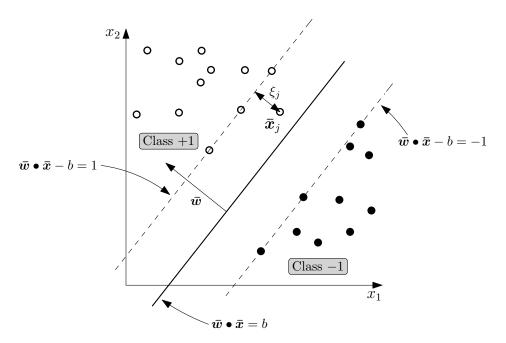

| 3.5  | Soft-Margin Classifier class separation example                                                                                                                                                                                                                                  |

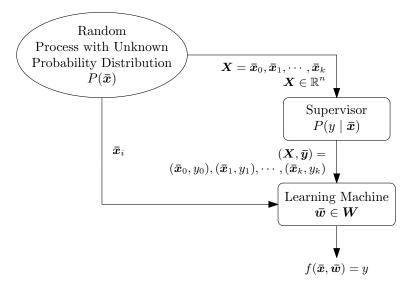

| 3.6  | Statistical Learning Theory: The model of learning from examples                                                                                                                                                                                                                 |

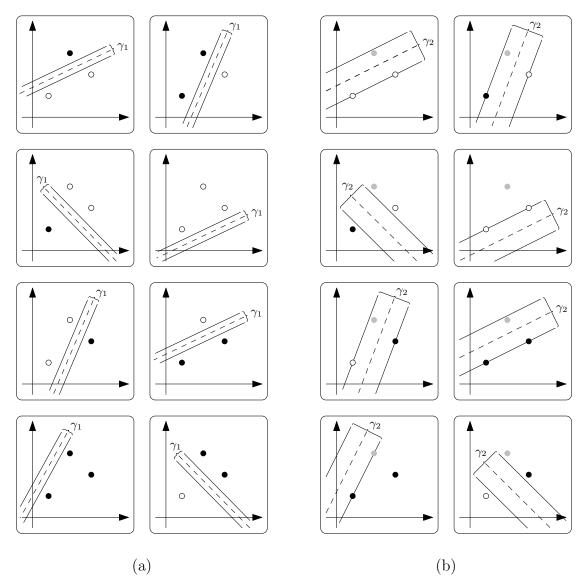

| 3.7  | Illustration of the VC-dimension $h$ of two classifiers $\hat{F}[\gamma_1]$ and $\hat{F}[\gamma_2]$ of                                                                                                                                                                           |

|      | decreasing complexity on an arbitrary data-set $D$ ; (a) classifier $\hat{F}[\gamma_1]$ with                                                                                                                                                                                     |

|      | margin $\gamma_1$ shatters $D$ , thus $h_{\gamma_1} = 3$ , and (b) classifier $\hat{F}[\gamma_2]$ with margin                                                                                                                                                                    |

|      | $\gamma_2$ shatters only two data points, thus $h_{\gamma_2} = 2$                                                                                                                                                                                                                |

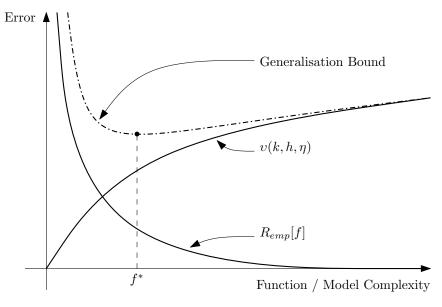

| 3.8  | Structural Risk Minimisation.                                                                                                                                                                                                                                                    |

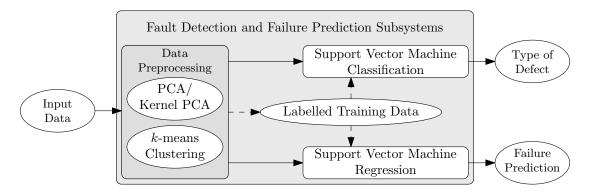

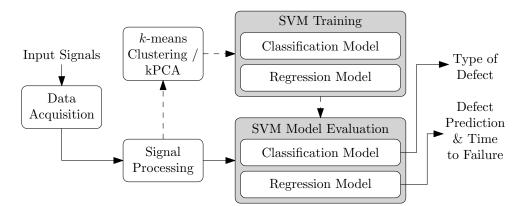

| 3.9  | System-level diagram of Rajkumar's oil and gas pipeline defect-monitoring                                                                                                                                                                                                        |

|      | and failure-prediction subsystems.                                                                                                                                                                                                                                               |

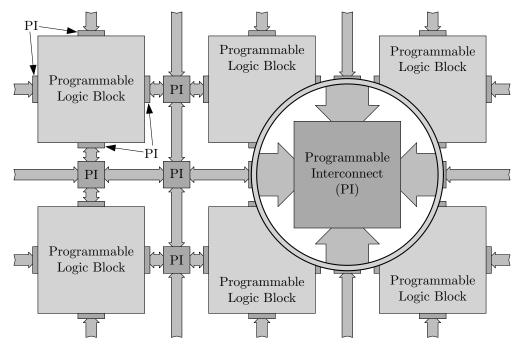

| 3.10 | Illustration of generic FPGA architecture, also referred to as fabric, with                                                                                                                                                                                                      |

|      | generic terminology, as viewed from above.                                                                                                                                                                                                                                       |

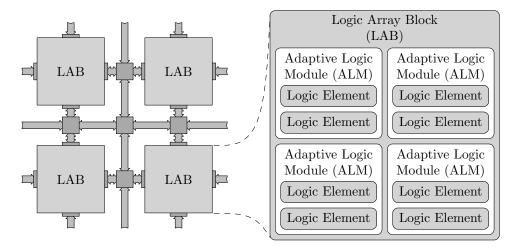

| 3.11 | Illustration of Altera FPGA architecture or fabric as viewed from above                                                                                                                                                                                                          |

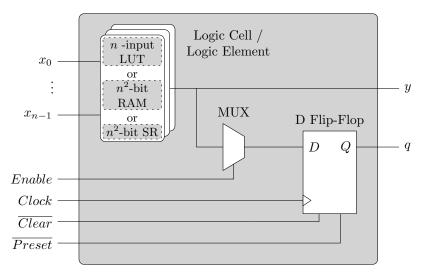

| 3.12 | Illustration of the generalised Altera Logic Element FPGA architectures as                                                                                                                                                                                                       |

|      | a quantum unit.                                                                                                                                                                                                                                                                  |

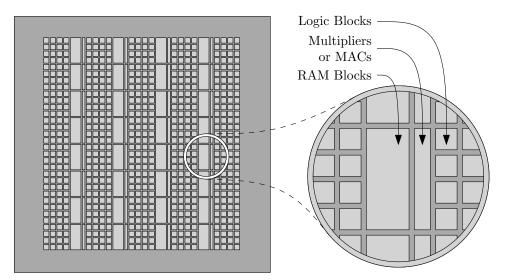

| 3.13 | A generic FPGA architecture with embedded RAM and multiplier or MAC                                                                                                                                                                                                              |

|      | instruction blocks arranged in columns amongst the programmable logic                                                                                                                                                                                                            |

|      | block fabric of the device.                                                                                                                                                                                                                                                      |

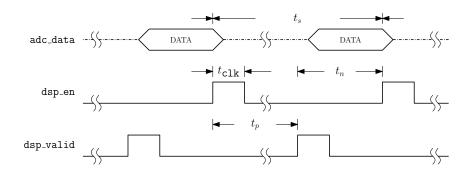

| 3.14 | DSP processing latency.                                                                                                                                                                                                                                                          |

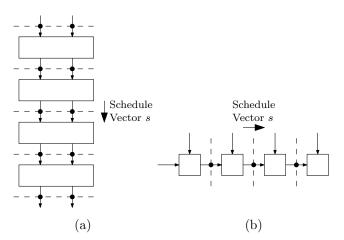

| 3.15 | Linear systolic array architectures; (a) column, and (b) row                                                                                                                                                                                                                     |

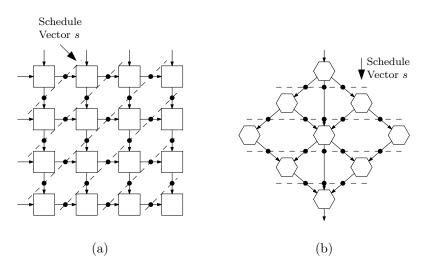

| 3.16 | Linear systolic array architectures; (a) rectangular, and (b) hexagonal                                                                                                                                                                                                          |

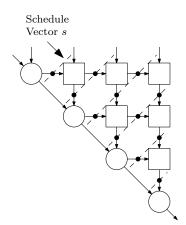

| 3.17 | Triangular QR systolic array architecture.                                                                                                                                                                                                                                       |

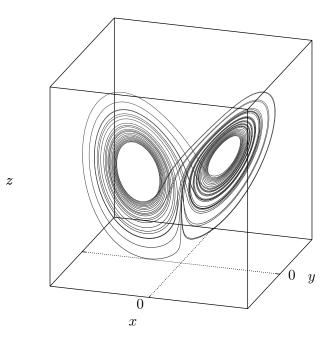

| 3.18 | State-space portrait of the Lorenz attractor for $R = 28$ , $P = 10$ , $B = 8/3$ ,                                                                                                                                                                                               |

|      | and some arbitrary initial conditions                                                                                                                                                                                                                                            |

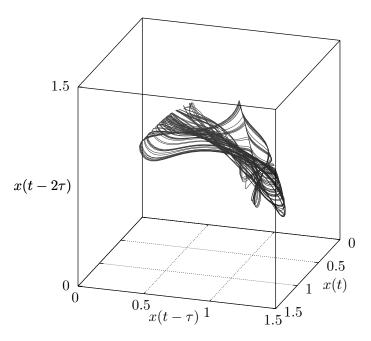

| 3.19 | State-space portrait of the Mackey-Glass attractor for $a = 0.2, b = 0.1,$                                                                                                                                                                                                       |

|      | $c = 10$ , and $\tau = 23$                                                                                                                                                                                                                                                       |

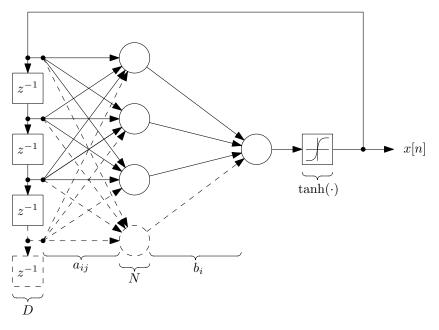

| 3.20 | Albers et-al ANN chaotic oscillator architecture.                                                                                                                                                                                                                                |

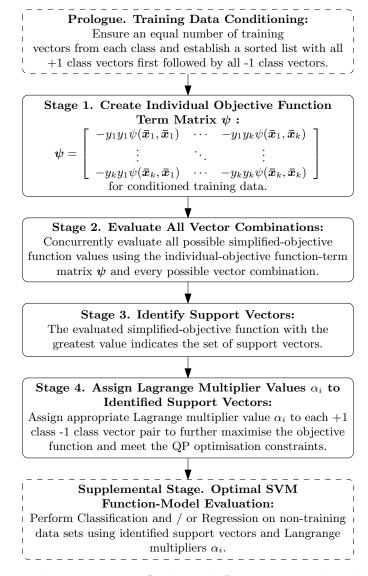

| 4.1  | The non-iterative fixed-period SVM training algorithm including supple-            |

|------|------------------------------------------------------------------------------------|

|      | mentary SVM optimal-function model evaluation stage for classification             |

|      | and / or regression                                                                |

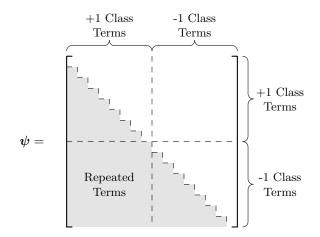

| 4.2  | Individual objective function term matrix $\psi$ illustrating the four class-      |

|      | combination quadrants, and when utilising an appropriate kernel, repeated          |

|      | terms that needn't be calculated                                                   |

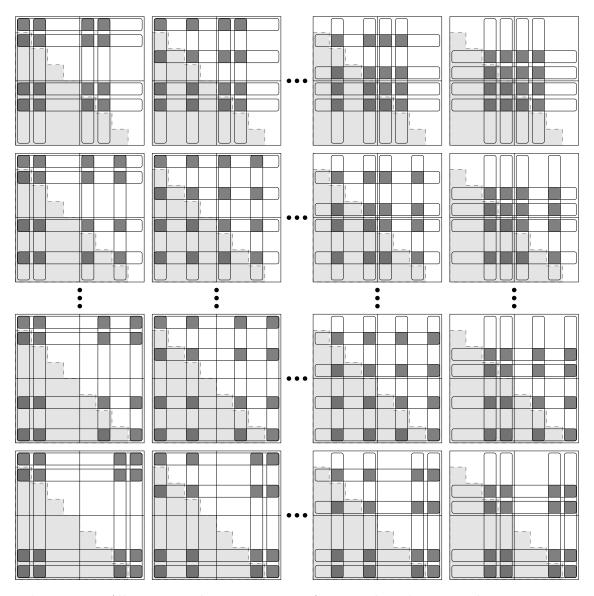

| 4.3  | All vector combination patterns for an eight 2-dimensional vector training         |

|      | set; the dark-grey boxes where each corresponding vector intersections illus-      |

|      | trates the terms to be summed to form one of the potential maximisations           |

|      | of the objective function                                                          |

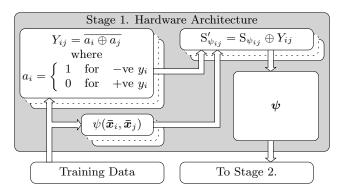

| 4.4  | Stage 1. hardware architecture overview                                            |

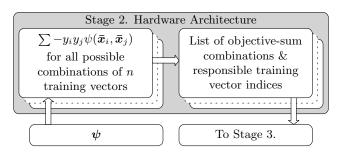

| 4.5  | Stage 2. hardware architecture overview                                            |

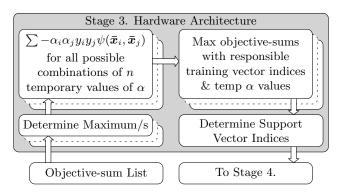

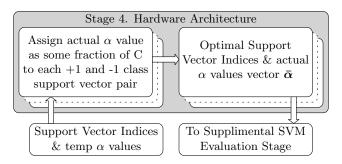

| 4.6  | Stage 3. hardware architecture overview                                            |

| 4.7  | Stage 4. hardware architecture overview                                            |

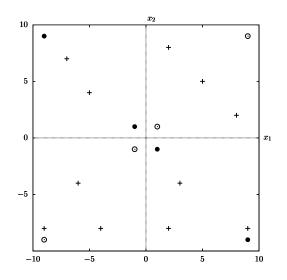

| 4.8  | Simple linearly-separable problem datasets; $+1$ class and $-1$ class training     |

|      | data are shown as circles and dots respectively, testing data is shown as          |

|      | crosses.                                                                           |

| 4.9  | XOR problem datasets; +1 class and -1 class training data are shown as             |

|      | circles and dots respectively, testing data is shown as crosses. $\ldots$ $\ldots$ |

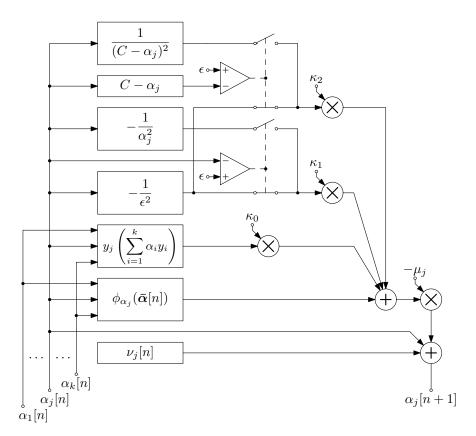

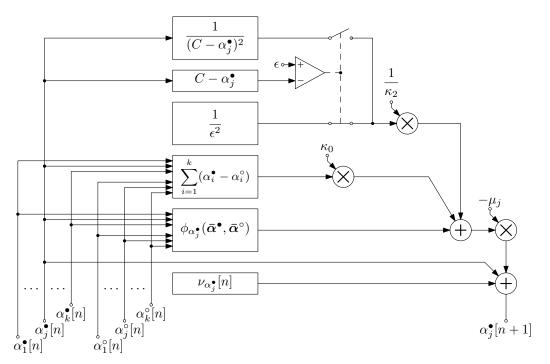

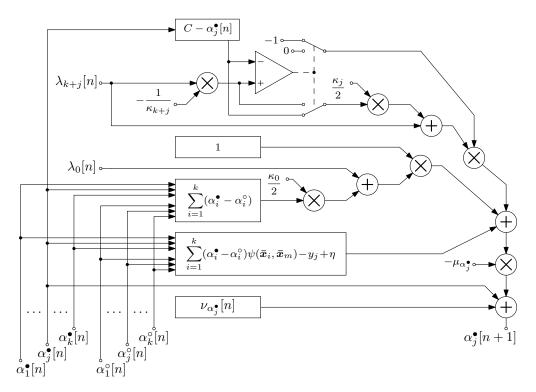

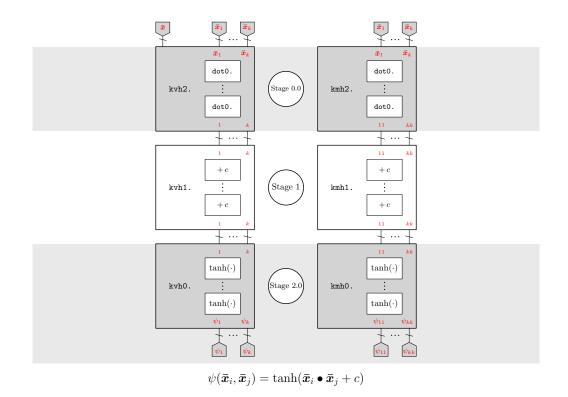

| 4.10 | Functional block-diagram of the ANN-mapped combined exterior penalty               |

|      | function and interior penalty / barrier function optimisation technique for        |

|      | SVM classification as defined in Eq. 4.18                                          |

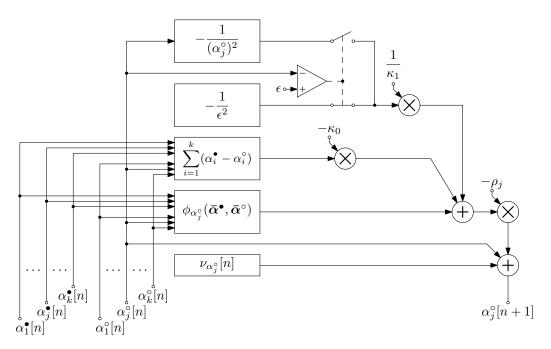

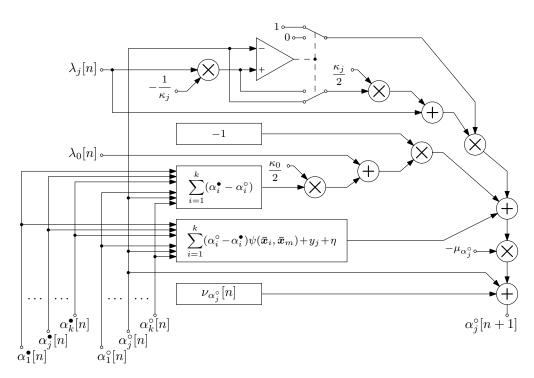

| 4.11 | Functional block-diagram of the ANN-mapped combined exterior penalty               |

|      | function and interior penalty / barrier function optimisation technique for        |

|      | SVM regression as defined in Eq. 4.35                                              |

| 4.12 | Functional block-diagram of the ANN-mapped combined exterior penalty               |

|      | function and interior penalty / barrier function optimisation technique for        |

|      | SVM regression as defined in Eq. 4.36                                              |

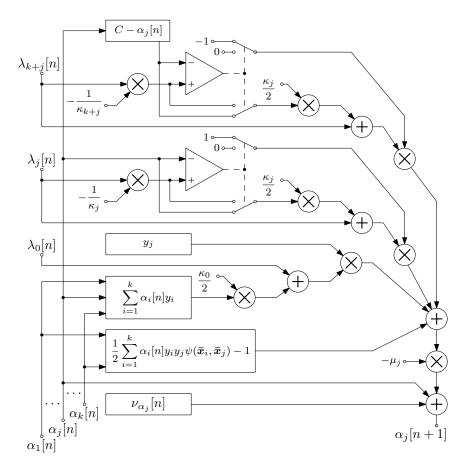

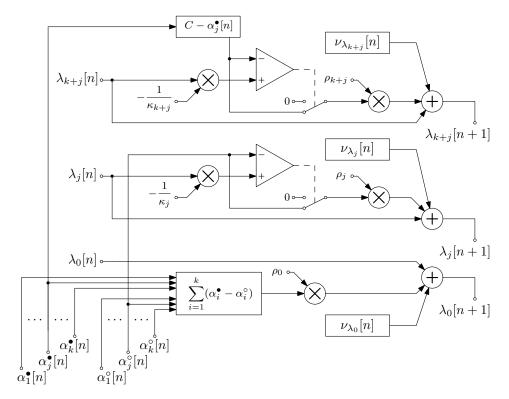

| 4.13 | Functional block-diagram of the ANN-mapped augmented Lagrange Mul-                 |

|      | tiplier optimisation technique as defined in Eq. 4.58                              |

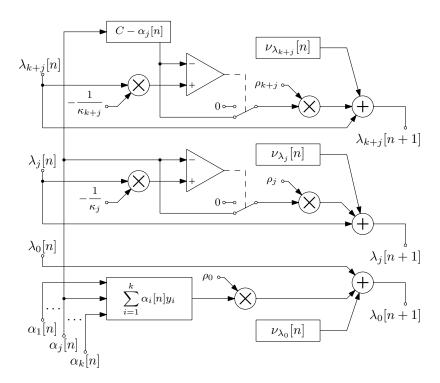

| 4.14 | Functional block-diagram of the ANN-mapped augmented Lagrange Mul-                 |

|      | tiplier optimisation technique as defined in Eq. 4.59, Eq. 4.60, and Eq. $$        |

|      | 4.61                                                                               |

| 4.15 | Functional block-diagram of the ANN-mapped augmented Lagrange Mul-                 |

|      | tiplier optimisation technique as defined in Eq. 4.86                              |

| 4.16 | Functional block-diagram of the ANN-mapped augmented Lagrange Mul-                 |

|      | tiplier optimisation technique as defined in Eq. 4.87                              |

| 4.17 | Functional block-diagram of the ANN-mapped augmented Lagrange Mul-                 |

|      | tiplier optimisation technique as defined in Eq. 4.88, Eq. 4.89, and Eq.           |

|      | 4.90                                                                               |

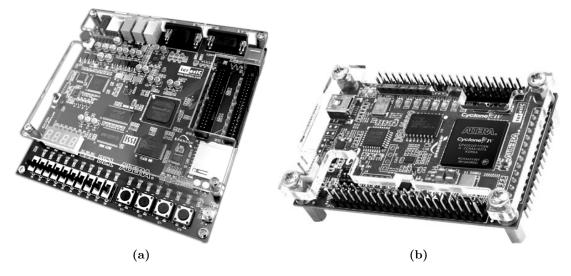

| 4.18 | Terasic Altera FPGA development boards; (a) the DE1 Cyclone II devel-              |

|      | opment board, and (b) the DE0-Nano Cyclone IV development board                    |

| 4.19 | Altera Stratix V DSP development Board                                                   | 87   |

|------|------------------------------------------------------------------------------------------|------|

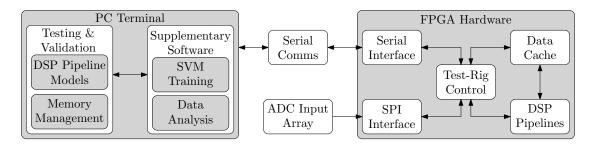

| 4.20 | Simplified data-flow model of Rajkumar's original work.                                  | 89   |

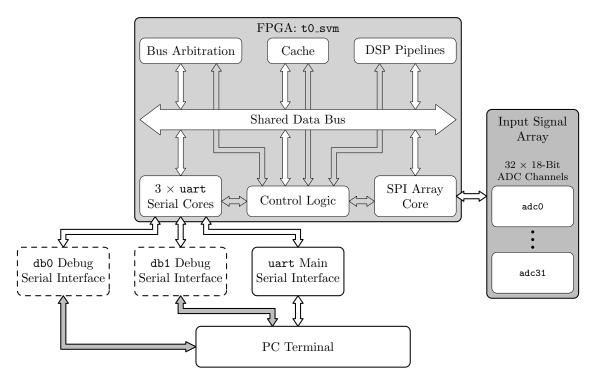

| 4.21 | Top-level block-diagram of the FPGA hardware test-rig system and sup-                    |      |

|      | plementary software subsystems.                                                          | 89   |

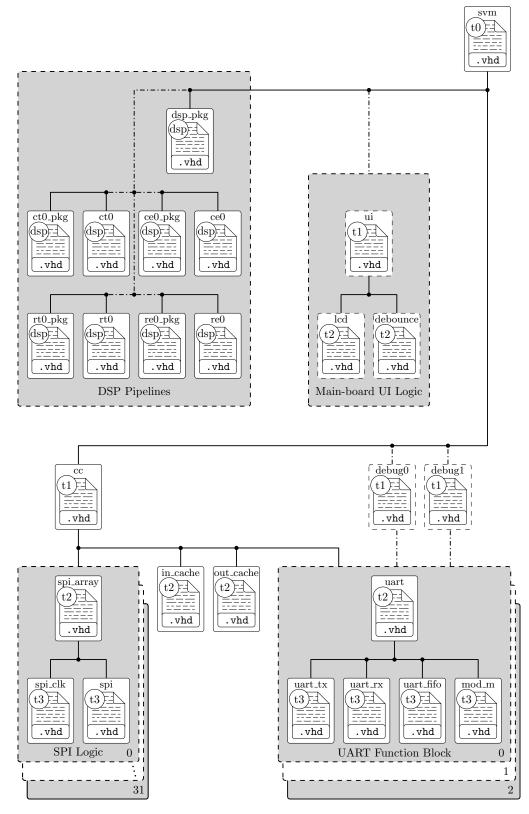

| 4.22 | Test-rig hardware system architectural overview.                                         | 90   |

| 4.23 | Test-rig system VHDL module dependency tree.                                             | 91   |

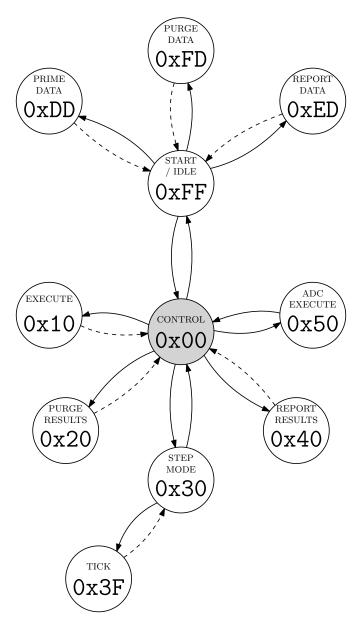

| 4.24 | Test-rig system command and control finite state machine                                 | 92   |

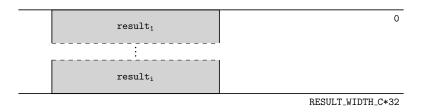

| 4.25 | Test-rig system serial input data cache map                                              | 93   |

| 4.26 | Test-rig system result cache map                                                         | 93   |

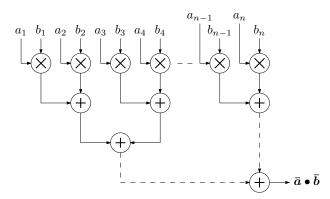

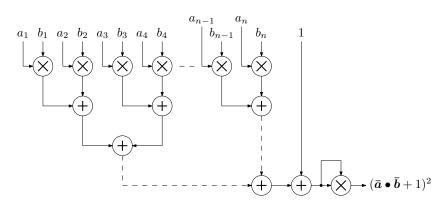

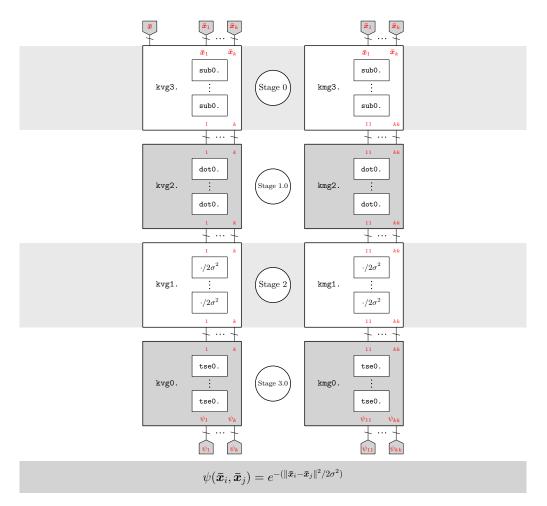

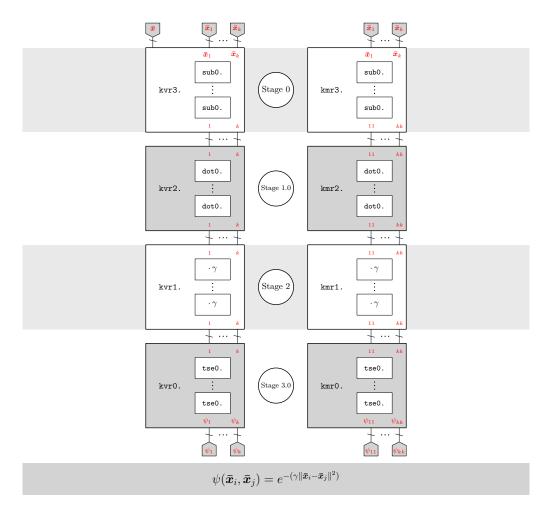

| 4.27 | General RTL architectural structure of the linear kernel evaluation operation            | . 96 |

| 4.28 | General RTL architectural structure of the polynomial kernel evaluation                  |      |

|      | operation                                                                                | 96   |

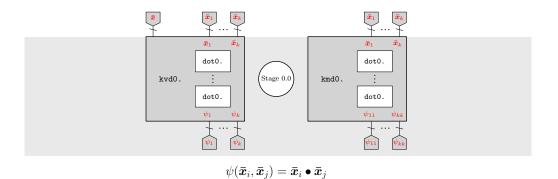

| 4.29 | Linear kernel pipeline                                                                   | 97   |

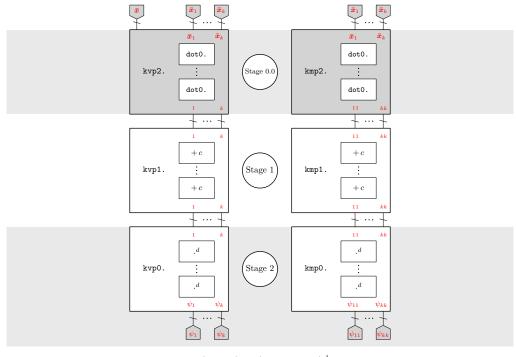

| 4.30 | Polynomial kernel pipeline.                                                              | 99   |

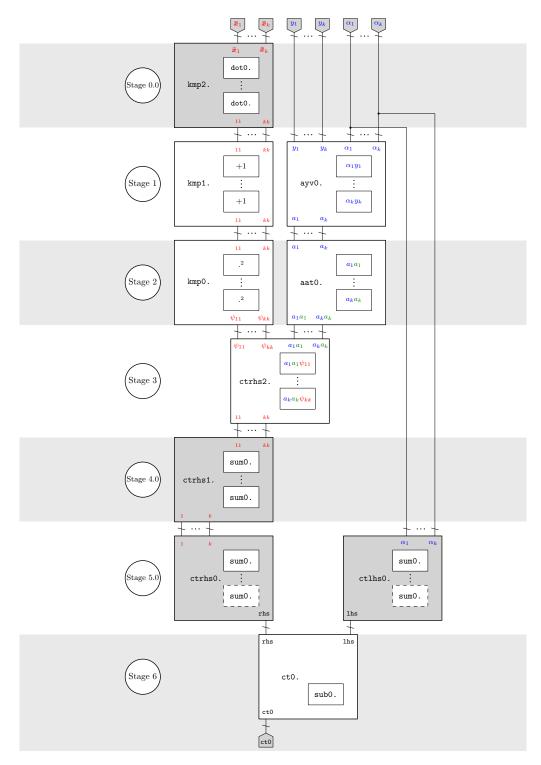

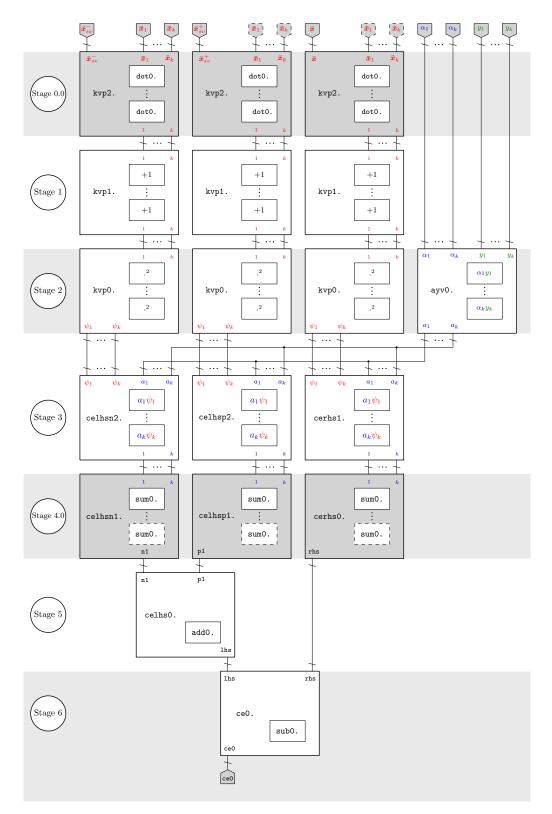

| 4.31 | ct0. Classification Training Pipeline.                                                   | 100  |

| 4.32 | ce0. Classification Evaluation Pipeline                                                  | 102  |

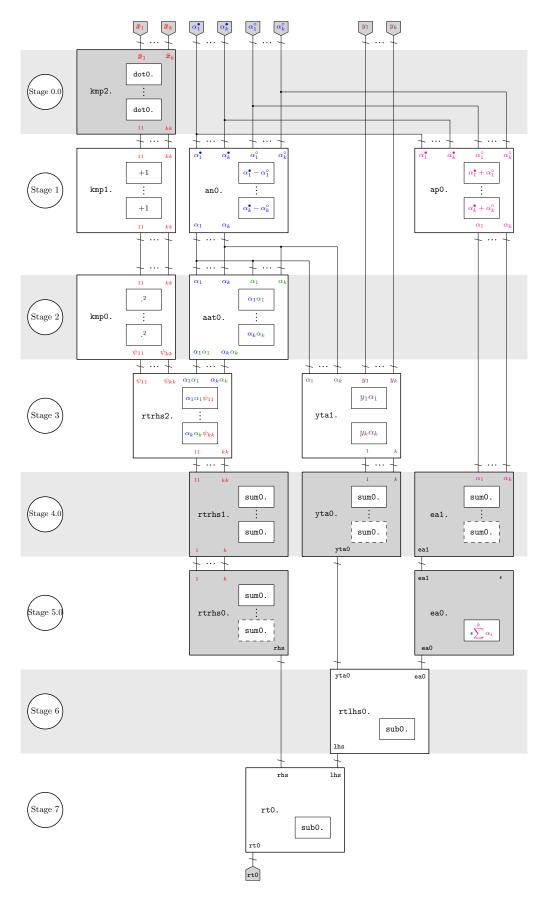

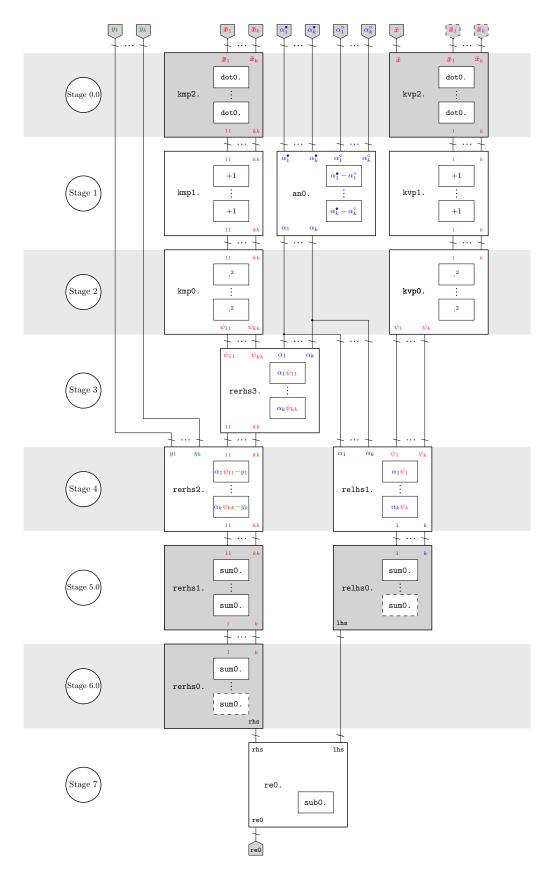

| 4.33 | rt0. Regression Training Pipeline                                                        | 104  |

| 4.34 | <b>re0.</b> Regression Evaluation Pipeline                                               | 106  |

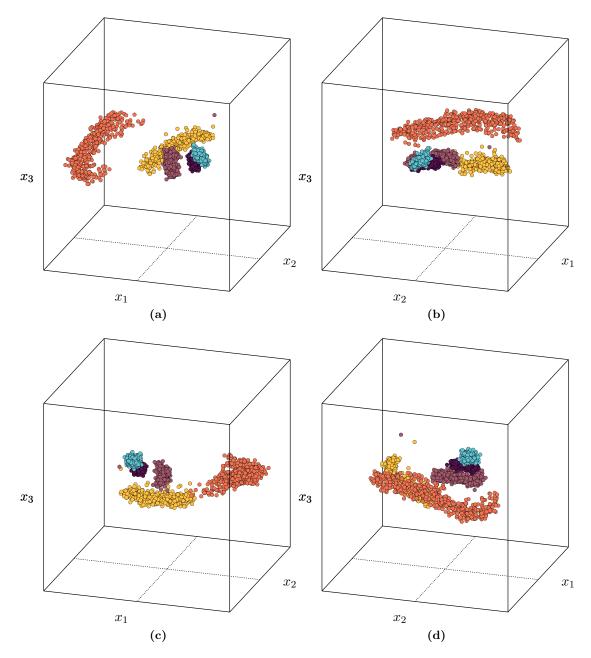

| 4.35 | Legacy pipeline 3-dimensional data-space rotated through 360 $^\circ$ at 90 $^\circ$ in- |      |

|      | crements                                                                                 | 109  |

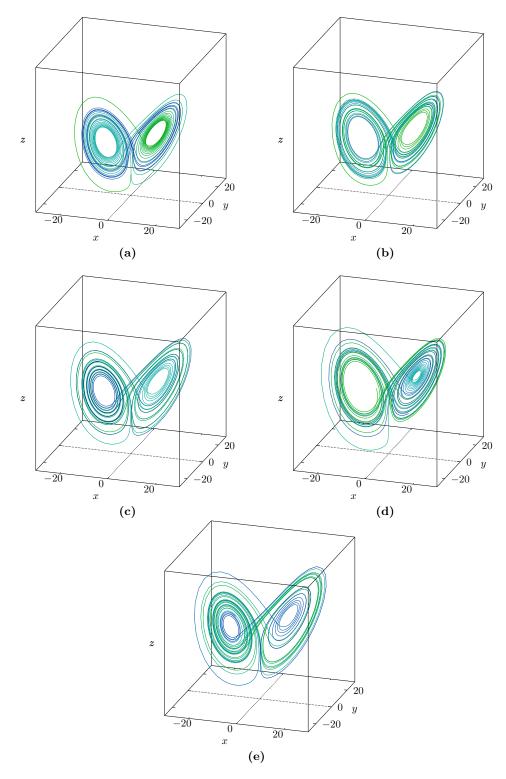

| 4.36 | Lorenz Attractor state-space response for system parameters $P = 10, B =$                |      |

|      | 8/3, and (a) $R = 25$ , with initial conditions $x(0) = 0.0$ , $y(0) = -0.1$ , and       |      |

|      | z(0) = 9.0, through to (e) $R = 33$ , with each previous system's final state            |      |

|      | as initial conditions. Each state-space evolution is shown as a transition               |      |

|      | from green to blue                                                                       | 110  |

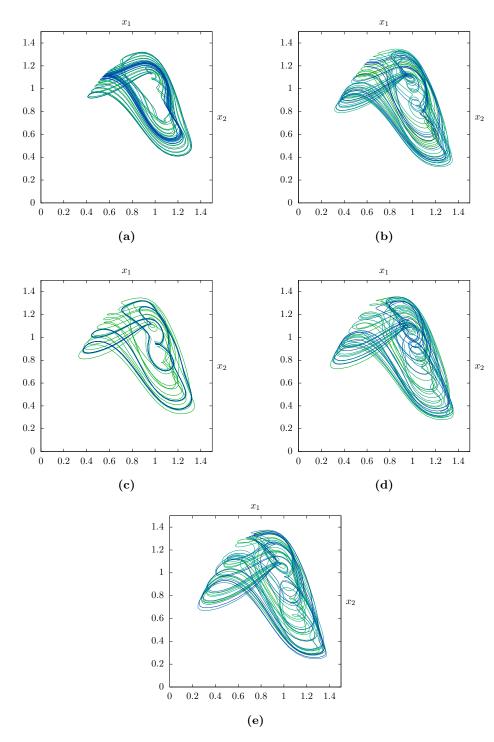

| 4.37 | Mackey-Glass Attractor 2-dimensional state-space response for system pa-                 |      |

|      | rameters $a = 0.2, b = 0.1, c = 10$ and (a) $\tau = 17$ , increased at increments of     |      |

|      | 2 through to (e) $\tau = 25$ . Each state-space evolution is shown as a transition       |      |

|      | from green to blue                                                                       | 111  |

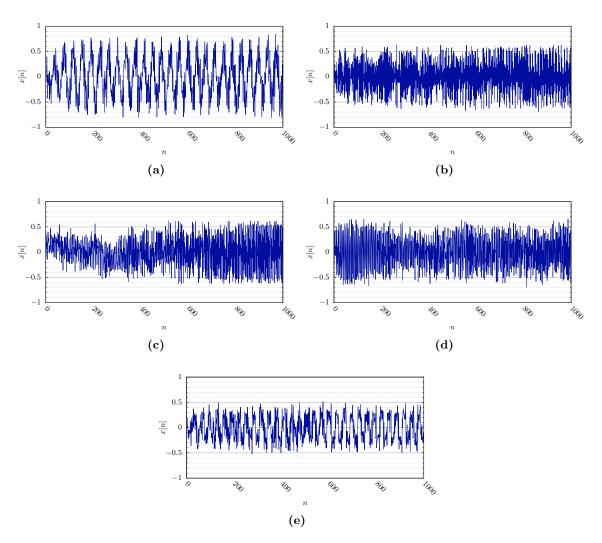

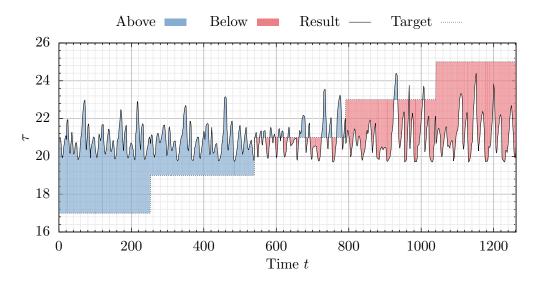

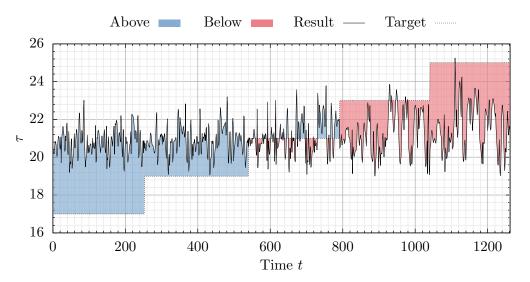

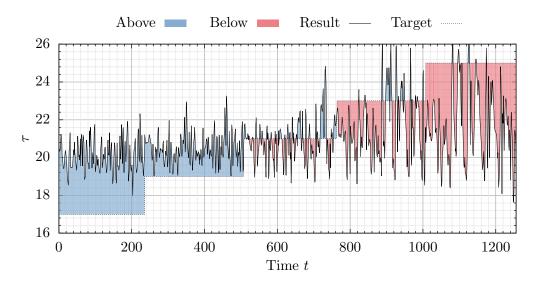

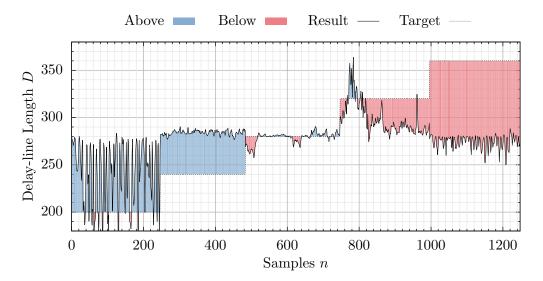

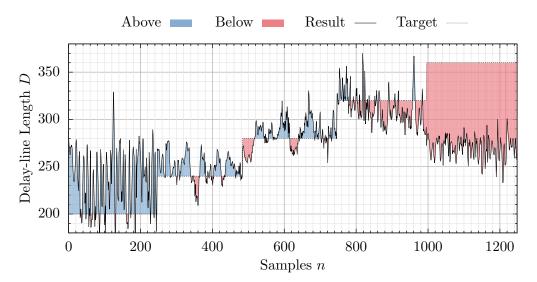

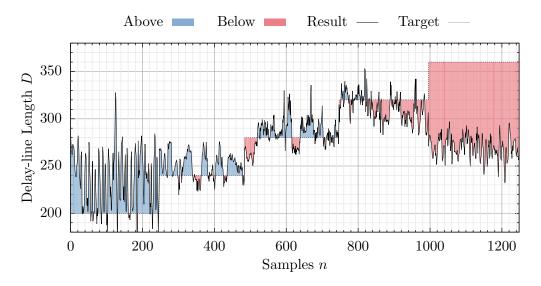

| 4.38 | ANN Chaotic Oscillator time-series with the number of neurons held con-                  |      |

|      | stant at $N = 10$ and the delay-line length increased at increments of 40                |      |

|      | from (a) $D = 200$ , through to (e) $D = 360$                                            | 112  |

| 4.39 | Experimental Data-set Processing Overview.                                               | 113  |

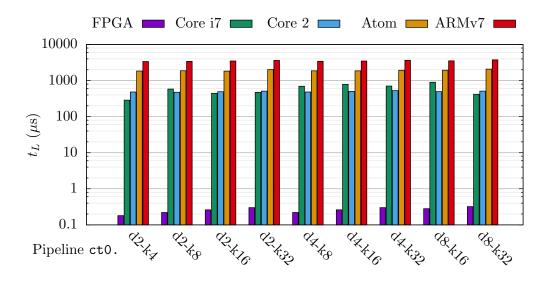

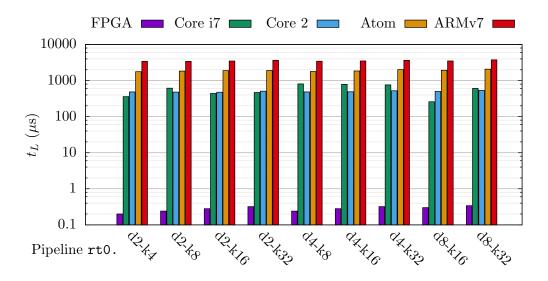

| 5.1  | Pipeline architecture ct0. FPGA hardware implementation and corre-                       |      |

|      | sponding software model latency / execution time $t_L$ performance metrics.              | 119  |

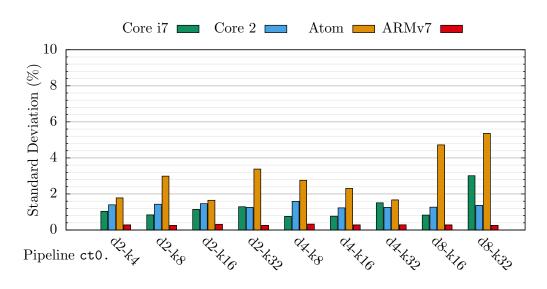

| 5.2  | Pipeline architecture ct0. software model mean execution time $t_L$ perfor-              |      |

|      | mance metric's standard deviation (%).                                                   | 120  |

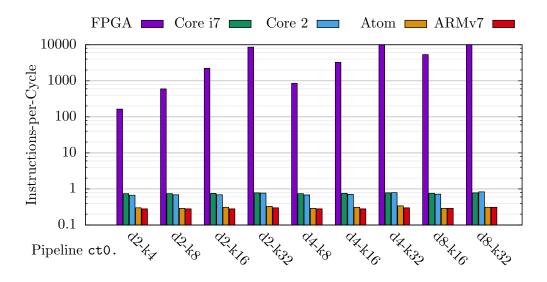

| 5.3  | Pipeline architecture ct0. FPGA hardware implementation and corre-                       |      |

|      | sponding software model instructions-per-cycle performance metrics                       | 121  |

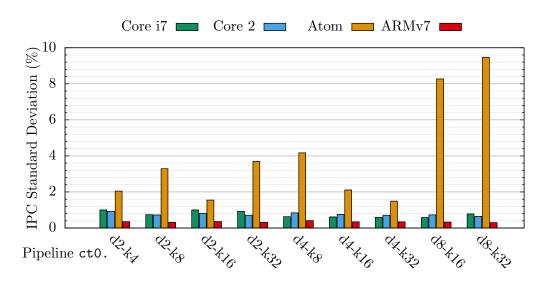

| 5.4  | Pipeline architecture ct0. software model mean instructions-per-cycle per-               |      |

|      | formance metric's standard deviation (%)                                                 | 122  |

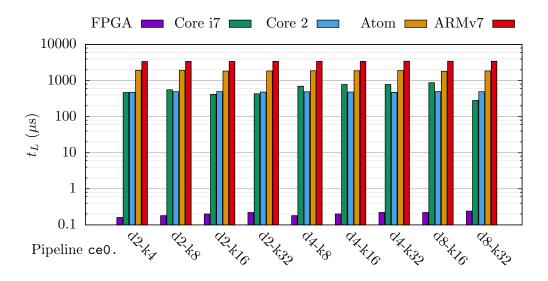

| 5 | .5  | Pipeline architecture ce0. FPGA hardware implementation and corre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 194 |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

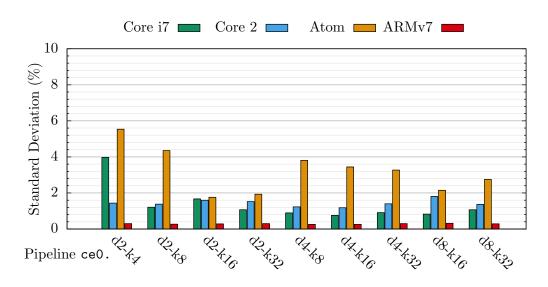

| 5 | .6  | sponding software model latency / execution time $t_L$ performance metrics.<br>Pipeline architecture ce0. software model mean execution time $t_L$ perfor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 124 |

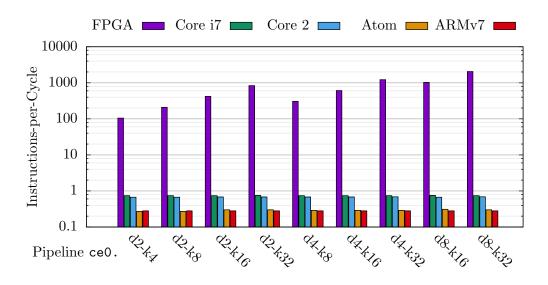

| 5 | .7  | mance metric's standard deviation (%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125 |

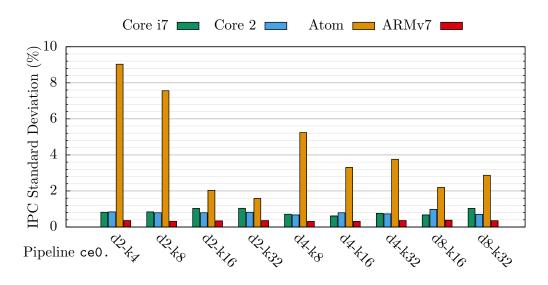

| 5 | .8  | sponding software model instructions-per-cycle performance metrics<br>Pipeline architecture ce0. software model mean instructions-per-cycle per-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 126 |

| 5 | .9  | formance metric's standard deviation (%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 127 |

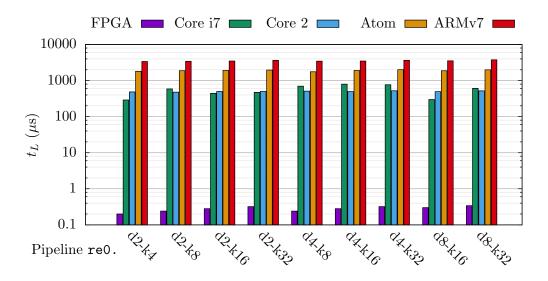

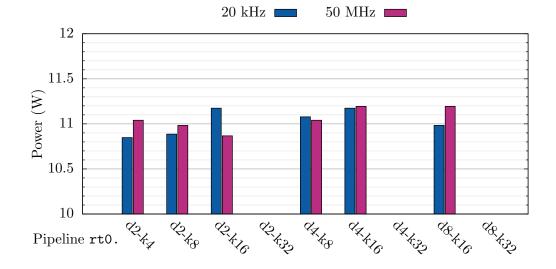

|   |     | sponding software model latency / execution time $t_L$ performance metrics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 129 |

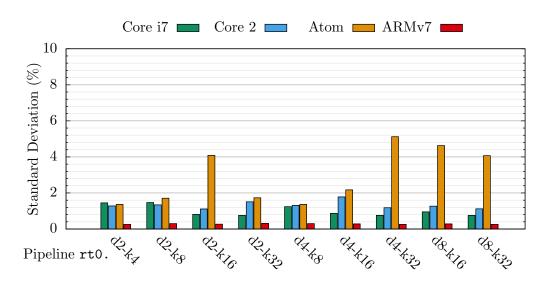

| 5 | .10 | Pipeline architecture rt0. software model mean execution time $t_L$ performance metric's standard deviation (%).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 130 |

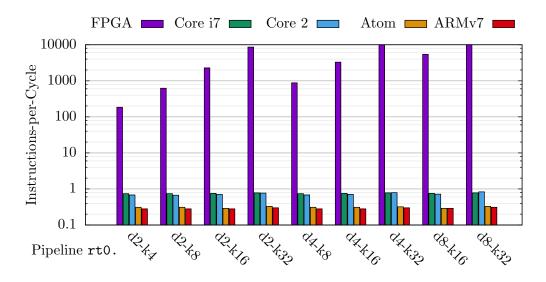

| 5 | .11 | Pipeline architecture rt0. FPGA hardware implementation and corre-<br>sponding software model instructions-per-cycle performance metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 131 |

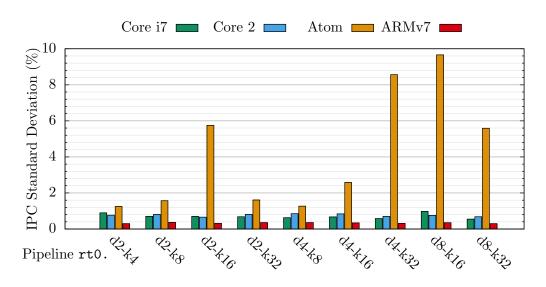

| 5 | .12 | $\label{eq:point} Pipeline \ architecture \ \texttt{rt0.} \ software \ model \ mean \ instructions-per-cycle \ per-cycle \ per-cycl$ |     |

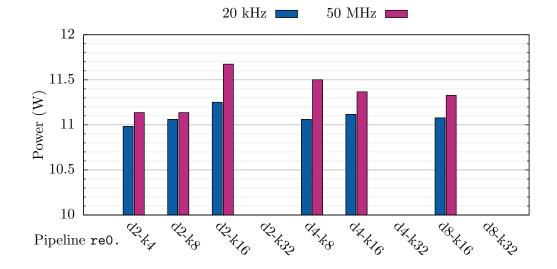

| 5 | .13 | formance metric's standard deviation (%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 132 |

| 5 | .14 | sponding software model latency / execution time $t_L$ performance metrics.<br>Pipeline architecture re0. software model mean execution time $t_L$ perfor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 134 |

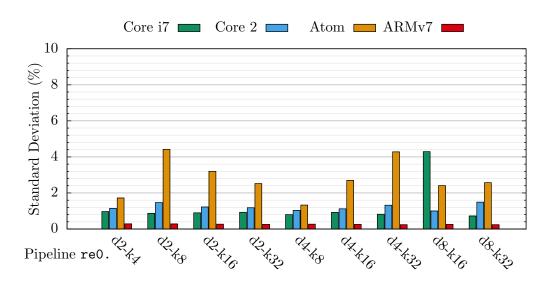

|   |     | mance metric's standard deviation (%). $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 135 |

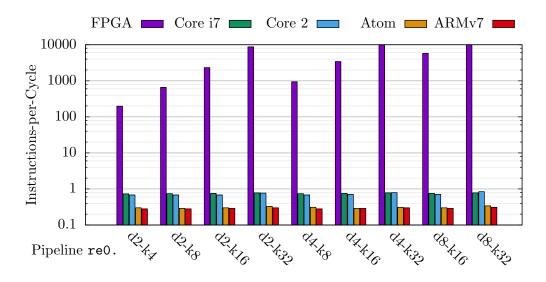

|   |     | Pipeline architecture re0. FPGA hardware implementation and corre-<br>sponding software model instructions-per-cycle performance metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 136 |

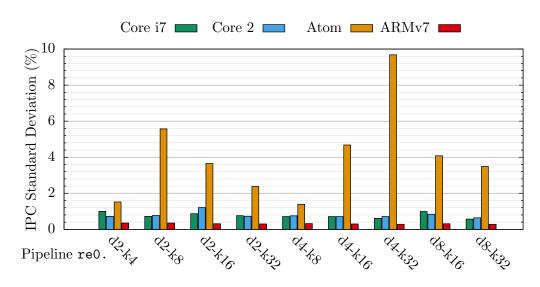

| 5 | .16 | Pipeline architecture <b>re0</b> . software model mean instructions-per-cycle per-<br>formance metric's standard deviation (%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 137 |

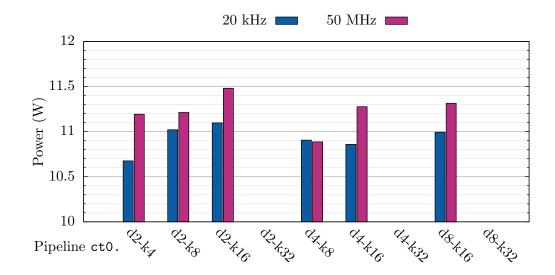

| 5 | .17 | Pipeline architecture ct0. average power consumption of each Altera<br>Stratix V GS 5SGSMD5 FPGA DSP development board implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| ٣ | 10  | with pipeline enable en rate of 20 kHz and 50 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 138 |

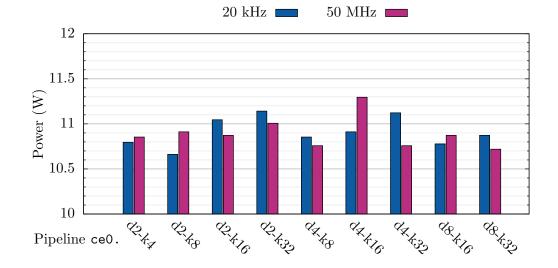

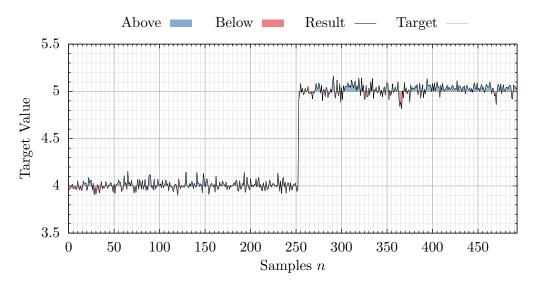

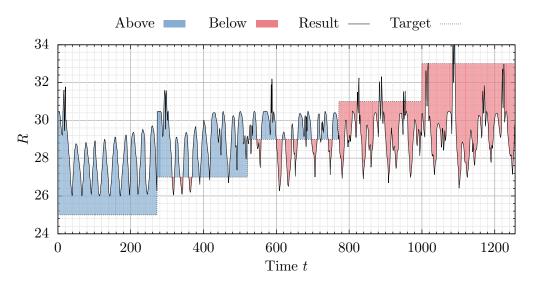

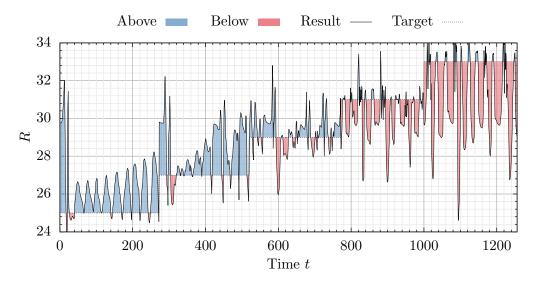

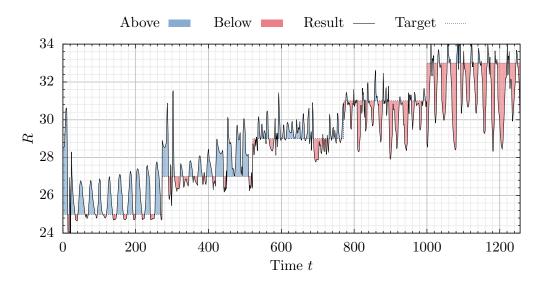

| 5 | .18 | Pipeline architecture ce0. average power consumption of each Altera<br>Stratix V GS 5SGSMD5 FPGA DSP development board implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |