### UNITED KINGDOM · CHINA · MALAYSIA

### **Department of Electrical and Electronic Engineering**

## A Multilevel Converter with a Floating Bridge for Open-Ended Winding Motor Drive Application

by

Shajjad Chowdhury B.Sc., M.Sc.

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

January 2017

То

My respected parents,

and

My beloved Wife, Pritha

### **Abstract**

In this thesis, a dual inverter topology is considered as an alternative to a multilevel converter for the control of high speed machines. Instead of feeding to one end of the stator with a single power converter, this topology feeds from both sides of the stator winding using two converters, thus achieving multilevel output voltage waveforms across the load. A large amount of published work in the area of open end winding power converter topologies are focused on symmetrical voltage sources. This published research recognises the advantages of the converter system in terms of increased reliability, improved power sharing capability and elimination of common mode voltages when compared to traditional single sided three phase converter solutions. However isolated DC supplies come with the price of additional components thus increase size, weight and losses of the converter system.

The aim of this project is, therefore, to investigate on reducing size, weight and losses of the open end winding motor drive by eliminating the need for isolated supply as well to achieve multilevel output voltage waveform. A traditional openend winding induction motor drive has been analysed in terms of weight and losses and it has been clearly identified that the isolation transformer not only increases the size and weight of a drive system but also includes additional losses.

A modified dual inverter system has then been proposed where one of the bridge inverters is floating, thus eliminated the need for isolated supplies. An asymmetric DC voltage sources ratio of 2:1 is utilised to achieve multilevel output voltage waveform across the load. The switching sequences are also analysed to identify the charging and discharging sequences to achieve control over floating capacitor voltage. This thesis describes the theoretical derivation of the modified converter model and algorithms as well as experimental results from an 11kW laboratory prototype.

### Thesis contribution

The work presented in this thesis has resulted in two conferences and three journal publications. The published papers are as listed:

- S. Chowdhury, P. W. Wheeler, C. Gerada, and C. Patel, "Model Predictive Control for a Dual Active Bridge Inverter with a Floating Bridge," *IEEE Transactions on Industrial Electronics*, vol. 63, pp. 5558-5568, 2016.

- S. Chowdhury, P. Wheeler, C. Patel, and C. Gerada, "A Multilevel Converter with a Floating Bridge for Open-ended Winding Motor Drive Applications," *IEEE Transactions on Industrial Electronics*, vol. 63, pp. 5366-5375, 2016.

- S. Chowdhury, P. Wheeler, C. Gerada, and C. Patel, "A dual two-level inverter with a single source for open end winding induction motor drive application," 17th European Conference on in Power Electronics and Applications (EPE'15 ECCE-Europe), 2015, 2015, pp. 1-9.

- S. Chowdhury, P. Wheeler, C. Gerada, and S. Lopez Arevalo, "A dual-inverter for an open end winding induction motor drive without an isolation transformer," IEEE Applied Power Electronics Conference and Exposition (APEC), 2015, pp. 283-289.

### Acknowledgement

I would like to express my deep appreciation and gratitude to my supervisors Prof. Pat. Wheeler and Prof. Chris Gerada for their encouragement, valuable advice and financial support throughout the progress of this work.

Thanks are also due to International Office and Department of Electrical and Electronic Engineering, the University of Nottingham for providing the financial support to cover my tuition fees for this research course.

I also wish to thank all my colleagues and friends in the Power Electronics, Control and Machine Group at the University of Nottingham for the support and valuable discussions. Among them, I would like to give special thanks to Dr. Saul Lopez and Dr. Chintan Patel for their help, and useful discussion.

I would also like to thank all of my friends for their help and support. Appreciation is extended to those who have made my research more interesting and enjoyable, there are too many to mention but particularly Attahir Aliyu, Emre Gurpinar, Maria Jankovic, Manjusha Vijayagopal, Savvas Papadopoulos and Bilal Arif.

Finally, I owe the greatest debt of gratitude to my family. I would like to thank my parents and my sisters for a lifetime of support, encouragement, and education. I am also thankful to my parent-in-laws and brother-in-law for their love, encouragement and support.

Last, but certainly not the least, I would like to thank my wife Pritha for her endless love and support.

| Co                          | ntents                                                                                   | Page No                         |

|-----------------------------|------------------------------------------------------------------------------------------|---------------------------------|

| List<br>Ack<br>List<br>List | stract t of publications knowledgement t of symbols and acronyms t of table t of figures | ii<br>ivi<br>viii<br>xii<br>xiv |

| Cha                         | apter 1: Background and Motivation                                                       | 1                               |

| 1.1                         | Background                                                                               | 1                               |

|                             | Objectives of the project                                                                | 4                               |

|                             | Thesis structure                                                                         | 5                               |

| 1.4                         | Conclusion                                                                               | 7                               |

| Cha                         | apter 2: Multilevel Voltage Source Converters                                            | 8                               |

| 2.1                         | Multilevel converter topologies                                                          | 9                               |

|                             | 2.1.1 Diode clamped converter                                                            | 10                              |

|                             | 2.1.2 Flying capacitor converter                                                         | 14                              |

|                             | 2.1.3 Cascaded converters                                                                | 16                              |

|                             | 2.1.4 Modular multilevel converter                                                       | 18                              |

| 2.2                         | 2.1.5 Hybrid converters  Modulation strategies                                           | 19<br>20                        |

| 2.2                         | Modulation strategies 2.2.1 Carrier based modulation                                     | 20                              |

|                             | 2.2.1.1 Third harmonic injection PWM                                                     | 23                              |

|                             | 2.2.1.2 Phase shifted PWM                                                                | 23                              |

|                             | 2.2.1.2 Thuse shifted T WM  2.2.1.3 Level shifted PWM                                    | 24                              |

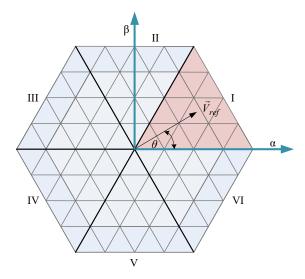

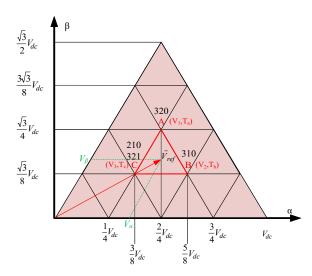

|                             | 2.2.2 Space vector modulation                                                            | 26                              |

|                             | 2.2.2.1 Space vector and switching states                                                | 27                              |

|                             | 2.2.2.2 Dwell time calculation                                                           | 29                              |

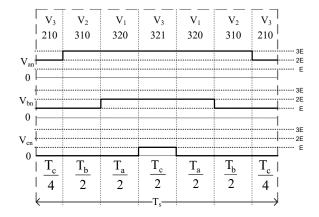

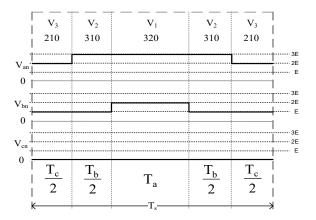

|                             | 2.2.2.3 Switching sequence design                                                        | 31                              |

| 2.3                         | Model predictive control for multilevel converters                                       | 32                              |

| 2.4                         | Conclusion                                                                               | 37                              |

| Cha                         | apter 3: Dual Two-Level Inverter                                                         | 38                              |

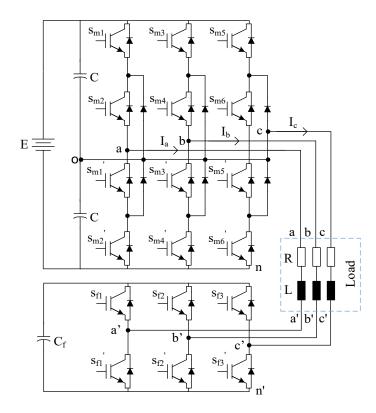

| 3.1                         | Topology description                                                                     | 38                              |

|                             | Applications of dual inverter                                                            | 39                              |

|                             | Analysis of the system                                                                   | 40                              |

|                             | Dual inverter with asymmetric voltage sources                                            | 43                              |

| 3.5                         | Modulation strategies                                                                    | 45                              |

|                             | 3.5.1 Carrier based modulation                                                           | 45                              |

| 2.0                         | 3.5.2 Space vector modulation                                                            | 47                              |

| 3.6                         | Control strategies for dual inverter                                                     | 51                              |

|                             | 3.6.1 Dual inverter to eliminate common mode voltage                                     | 51                              |

|                             | 3.6.2 Dual inverter with power sharing capability                                        | 52                              |

|     | 3.6.3 Dual inverter with one bridge floating                                                         | 53       |

|-----|------------------------------------------------------------------------------------------------------|----------|

|     | 3.6.4 Dual inverter with asymmetric sources                                                          | 54       |

| 3.7 | Advantages and disadvantages of dual inverter system                                                 | 55       |

| 3.8 | Conclusion                                                                                           | 56       |

| Ch  | apter 4: Open End Winding Induction Motor Drive                                                      | 57       |

| 4.1 | Induction machine                                                                                    | 57       |

|     | 4.1.1 Modelling of three phase induction motor                                                       | 58       |

|     | 4.1.2 Induction machine model incorporating space harmonics                                          | 62       |

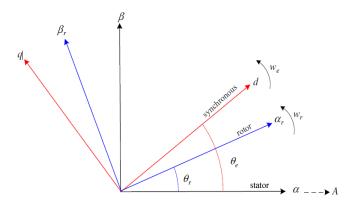

| 4.2 | Transformation of IM model into a common reference frame                                             | 64       |

| 4.3 | Loss calculation for open end winding IM drive                                                       | 67       |

|     | 4.3.1 Loss estimation of the converter system                                                        | 69       |

|     | 4.3.2 Loss calculation of induction motor                                                            | 70       |

|     | 4.3.3 Design and losses of isolation transformer                                                     | 73       |

|     | Reduction of losses, size and weight of OEW-IM drive                                                 | 75       |

| 4.5 | Conclusion                                                                                           | 76       |

| Ch  | apter 5: Analysis of Dual Inverter with one Bridge Floating                                          | 77       |

|     |                                                                                                      |          |

| 5.1 | Analysis of the proposed system                                                                      | 78       |

|     | 5.1.1 Floating capacitor voltage control                                                             | 78       |

|     | <ul><li>5.1.2 SVM to control the floating capacitor voltage</li><li>5.1.3 Dead-time effect</li></ul> | 83<br>84 |

|     |                                                                                                      | 86       |

|     | 5.1.4 Avoiding voltage spike during dead-time interval                                               | 80<br>90 |

| 5 2 | 5.1.5 Common mode voltage reduction                                                                  | 90       |

|     | Loss comparison Simulation results                                                                   | 92<br>95 |

|     | Conclusion                                                                                           | 107      |

| ~.  |                                                                                                      | 400      |

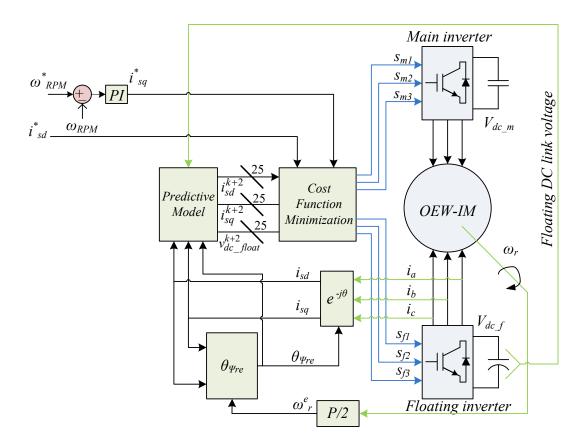

|     | apter 6: Predictive Control of Dual Inverter with one Bridge Floating                                | 108      |

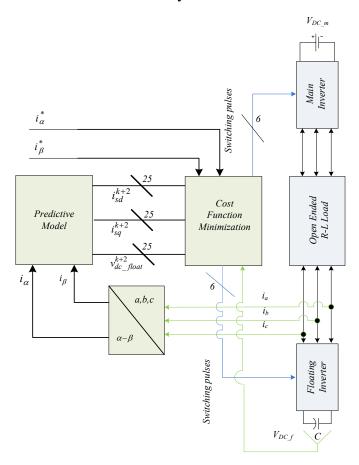

| 6.1 | Model predictive control                                                                             | 108      |

|     | 6.1.1 Modelling of the converter                                                                     | 109      |

|     | 6.1.2 Load modelling                                                                                 | 110      |

|     | 6.1.3 Simulation results                                                                             | 115      |

| 6.2 | Modulated model predictive control                                                                   | 122      |

|     | 6.2.1 Cost function and duty cycle calculation                                                       | 123      |

|     | 6.2.2 Simulation results                                                                             | 125      |

|     | Comparison of control dynamics                                                                       | 134      |

| 6.4 | Conclusion                                                                                           | 138      |

| Ch  | apter 7: Experimental Setup and Results                                                              | 139      |

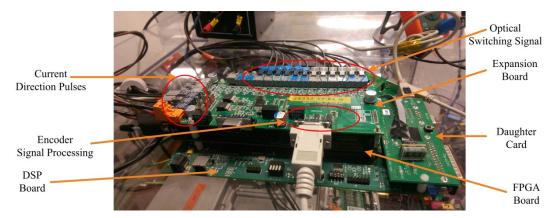

| 7.1 | Experimental setup                                                                                   | 140      |

|     | 7.1.1 Experimental converter                                                                         | 142      |

|     | 7.1.2 Voltage and current measurements                                                               | 143      |

|     |                                                                                                      |          |

| 7.1.3 Control boards                                                   | 143 |

|------------------------------------------------------------------------|-----|

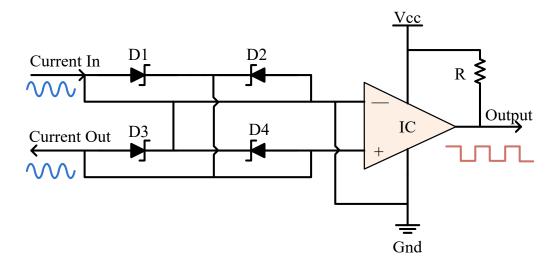

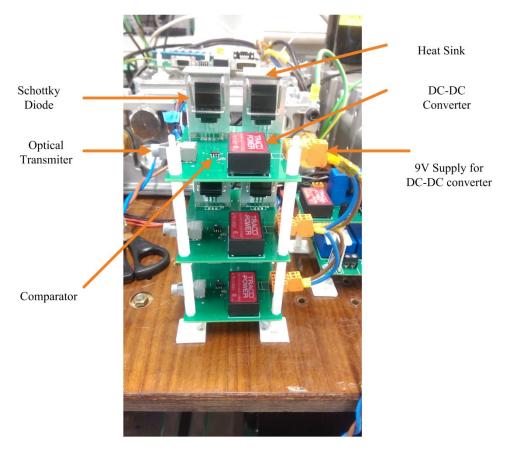

| 7.1.4 Current direction identification                                 | 144 |

| 7.1.5 Rotor speed measurement                                          | 145 |

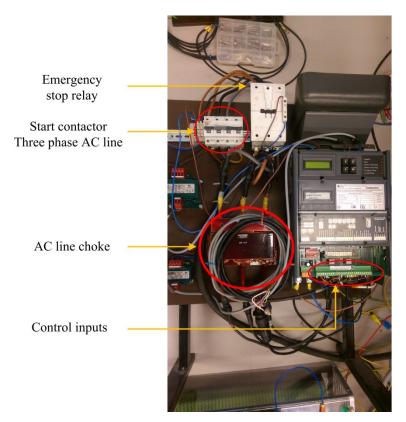

| 7.1.6 Industrial DC drive                                              | 146 |

| 7.2 Experimental results using a PI based controller                   | 146 |

| 7.3 Experimental results using predictive control                      | 158 |

| 7.4 Experimental results with modulated model predictive control       |     |

| 7.5 Comparison of control dynamics                                     | 166 |

| 7.6 Conclusion                                                         | 169 |

| Chapter 8: Conclusion and Future Work                                  | 171 |

| 8.1 Summary                                                            | 171 |

| 8.2 Future work suggestions                                            | 173 |

| 8.2.1 Increased modulation index                                       | 173 |

| 8.2.2 Implement MMPC algorithm for IM drive                            | 175 |

| Appendix A – Three Phase Isolation Transformer Design                  | 176 |

| Appendix B – Machine and Power Electronics Parameter for Loss          | 183 |

| Calculation                                                            |     |

| Appendix C – Coordinate Transformation                                 | 184 |

| Appendix D – Indirect Rotor Flux Oriented Control of Induction Machine | 186 |

| Appendix E – PI Controller Design                                      | 190 |

| Appendix F – Machine and Power Electronics Parameter for               | 194 |

| Simulation and Experimental Validation                                 |     |

| References                                                             | 195 |

### LIST OF SYMBOLS AND ACRONYMS

**Definitions**

### $S_{x}$ Switching state modulation index for carrier based modulation m $V_{m}$ Amplitude of the modulating signal $V_{cr}$ Amplitude of the carrier signal $V_{DC}$ DC link voltage Main inverters DC link voltage $V_{DC\ m}$ $V_{DC\ f}$ Floating inverters DC link voltage $V_{\alpha}$ , $V_{\beta}$ Fictitious two phase voltage after using Clarke's transformation $T_s$ Sampling time $T_a$ , $T_b$ , $T_c$ Duty cycle time modulation index for space vector modulation $m_a$ Current time instant k k+1Future time instant

Cost function for predictive control

Cost function for modulated model predictive control

$V_{abc\_s}$  Three phase stator voltage

$V_{abc\_r}$  Three phase rotor voltage

$i_{abc\_s}$  Three phase stator current

$i_{abc\ r}$  Three phase rotor current

$\Psi_{abc\_s}$  Three phase stator flux

$\Psi_{abc\_r}$  Three phase rotor flux

R Resistance

**Symbols**

g

G

L Inductance

$r_s$  Three phase stator resistance matrix

$r_r$  Three phase rotor resistance matrix

$R_s$  Stator per phase resistance

$R_r$  Rotor per phase resistance

*l*<sub>ls</sub> Stator per phase leakage inductance

$l_{lr}$  Rotor per phase leakage inductance

$l_{sr}$  Stator to rotor mutual inductance

$l_m$  Magnetising inductance

$\theta_r$  Rotor angular position

$T_e$  Electromagnetic torque

P pole pair

$\omega_r$  Rotor speed in rad/sec

$\omega_{rpm}$  Rotor speed in rotation per minute

$B_m$  Frictional coefficient

$T_L$  Load torque

j Rotor inertia

$i_{abc\_r5}$  Three phase stator current for MMF distribution of 5<sup>th</sup>

harmonics

$i_{abc}$  r7 Three phase stator current for MMF distribution of  $7^{th}$

harmonics

$V_{ds}$ ,  $V_{as}$ ,  $V_{os}$  Stator voltages after rotational transformation is applied

$V_{dr}$ ,  $V_{qr}$ ,  $V_{or}$  Rotor voltages after rotational transformation is applied

$i_{ds}$ ,  $i_{qs}$ ,  $i_{os}$  Stator currents after rotational transformation is applied

$i_{dr}$ ,  $i_{qr}$ ,  $i_{or}$  Rotor currents after rotational transformation is applied

$\Psi_{ds}$ ,  $\Psi_{qs}$ ,  $\Psi_{os}$  Stator flux after rotational transformation is applied

$\Psi_{dr}$ ,  $\Psi_{qr}$ ,  $\Psi_{or}$  Rotor flux after rotational transformation is applied

$C_{v/f}$  v/f constant to achieve constant flux

$P_{iron}$  Iron loss

$k_h$  Hysteresis loss coefficient

$k_e$  eddy current loss coefficient

$k_u$  Window utilisation factor

f Fundamental frequency

$V_d$  Diode voltage drop

J Current density

$A_p$  Area product

$W_a$  Window utilisation factor

$A_c$  Iron area

B<sub>ac</sub> Maximum flux density

$K_g$  Core geometry

$A_t$  Surface area

$N_p$  Number of primary winding turn

$A_w$  Bare copper area

$\rho$  Resistivity

$I_{a,b,c}$  Three phase load currents

$V_{an,bn,cn}$  Main converter leg voltages

$V_{an',bn',cn'}$  Floating converter leg voltages

$V_{aa',bb',cc'}$  Voltages across the load

dt Dead time

$V_{nn'}$  Voltage across the isolated neutral points

$V_{\alpha,\beta}$  Voltages after using Clarke's (stationary) transformation

$i_{\alpha,\beta}$  Currents after using Clarke's (stationary) transformation

$i_{mrd}$  Magnetising current

$\omega_{sl}$  Slip speed

$\theta_{wr}$  Rotor flux angle

$S_{m1,m2,m3}$  Switching pulses for main inverter

$S_{f1,f2,f3}$  Switching pulses for floating inverter

$T_s$  Sampling time

$I_{dc\ f}$  Floating inverters DC link current

g Cost function for predictive control

G Cost function for modulated model predictive control

λ Weighting factor

$f_s$  Switching frequency

### **Abbreviations**

MLT Mean Length Turn

**SVM** Space Vector Modulation

IM Induction Machine

**FS-MPC** Finite Set – Model Predictive Control

MPC Model Predictive Control

MMPC Modulated Model Predictive Control

PI Proportional Integral

**DC** Direct Current

**AC** Alternating Current

**DSP** Digital Signal Processor

**FPGA** Field Programmable Gate Array

**THD** Total Harmonic Distortion

**POD** Phase Opposition Disposition

**APOD** Alternate Phase Opposition Disposition

**IGBT** Insulated Gate Bipolar Transistor

**PWM** Pulse Width Modulation

VSI Voltage Source Inverter

### General

\* When in superscript, denotes the reference value

[] Square brackets identify matrices

$\alpha$ - $\beta$  When in subscript, denotes transformation of three phase

symmetrical system into two phase system using Clarke's

transformation

*d-q* When in subscript, denotes transformation of three phase

symmetrical system into two phase system using rotational

transformation.

### **List of Tables**

|           |                                                                                                    | Page No |

|-----------|----------------------------------------------------------------------------------------------------|---------|

| Table 2.1 | Relationship between switching states and output voltage of five-level diode clamped converter.    | 12      |

| Table 2.2 | Relationship between switching states and output voltage of three-level T-NPC converter.           | 12      |

| Table 2.3 | Relationship between switching states and output voltage of three-level Active-NPC converter.      | 13      |

| Table 2.4 | Relationship between switching states and output voltage of five-level flying capacitor converter. | 15      |

| Table 2.5 | Relationship between switching states and output voltage of five-level cascade H-bridge converter. | 17      |

| Table 3.1 | Relationship between converter operation and reference zone.                                       | 47      |

| Table 3.2 | Subsector identification.                                                                          | 50      |

| Table 4.1 | Losses of the dual inverter system.                                                                | 70      |

| Table 4.2 | Induction motor parameter.                                                                         | 71      |

| Table 4.3 | Material used for loss calculation.                                                                | 72      |

| Table 4.4 | Losses in the stator of IM.                                                                        | 72      |

| Table 4.5 | Losses in the rotor of IM.                                                                         | 72      |

| Table 4.6 | Design parameter of isolation transformer.                                                         | 73      |

| Table 4.7 | Used material and losses for isolation transformer.                                                | 74      |

| Table 4.8 | Loss and weight comparison for IM drive components.                                                | 75      |

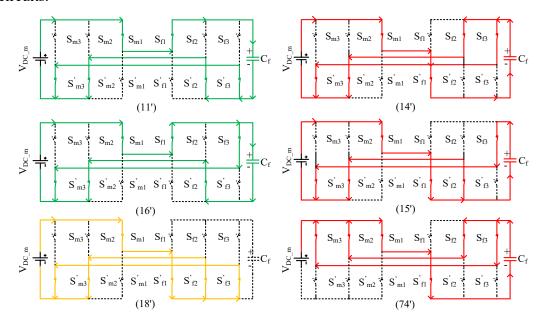

| Table 5.1 | Relation between switching number and switching states.                                            | 78      |

| Table 5.2 | Charging and discharging switching sequences.                                                      | 84      |

| Table 5.3 | Delay time depending on current direction.                                                         | 87      |

| Table 5.4 | Common mode voltage for all available switching combinations.                                      | 91      |

| Table 5.5 | Common mode voltage for redundant switching states.                                                | 91      |

| Table 5.6 | Device voltage rating comparison.                                                                  | 94      |

| Table 6.1 | THD comparison of Different current controllers for R-L load.                                      | 135     |

| Table 6.2 | THD comparison of Different current controllers for IM drive.                                      | 135     |

| Table 7.1 | THD comparison of Different current controllers for R-L load. | 166 |

|-----------|---------------------------------------------------------------|-----|

| Table 7.2 | THD comparison of Different current controllers for IM drive. | 166 |

## **List of Figures**

|             |                                                                                                                                                                 | Page No |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

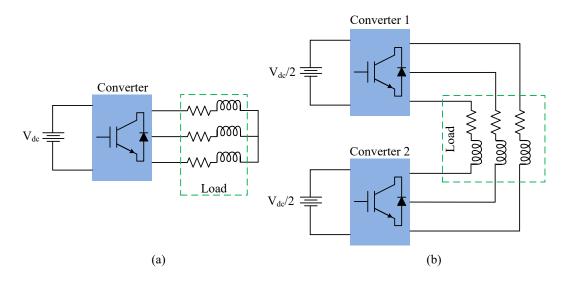

| Figure 1.1  | Converter topologies depending on supply techniques (a) single sided converter (b) dual converter.                                                              | 3       |

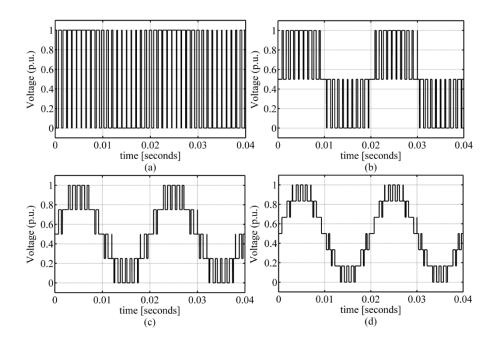

| Figure 2.1  | One phase leg of an inverter (a) two-level, (b) three-level and (c) n-level inverter.                                                                           | 8       |

| Figure 2.2  | Per-unit output pole voltage waveform of power converters (a) two level converter (b) three level converter (c) five level converter (d) seven level converter. | 9       |

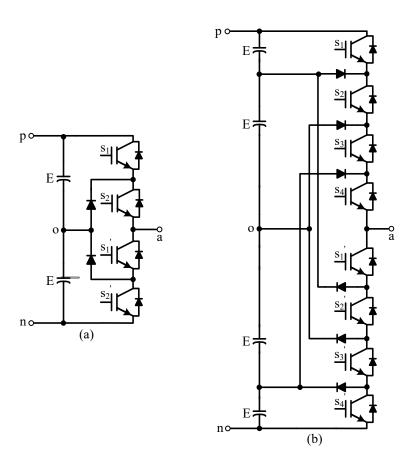

| Figure 2.3  | Single phase leg of diode clamped multi-level converter topology (a) three level converter (b) five level converter.                                            | 11      |

| Figure 2.4  | Three level T-type NPC converter.                                                                                                                               | 12      |

| Figure 2.5  | Three level active-NPC converter.                                                                                                                               | 13      |

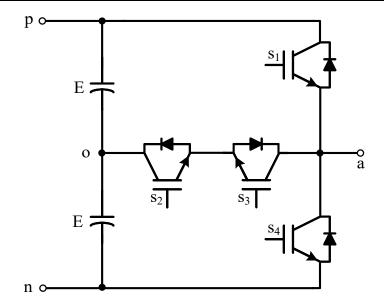

| Figure 2.6  | Single phase leg of flying capacitor multi-level converter topology (a) three level converter (b) five level converter.                                         | 14      |

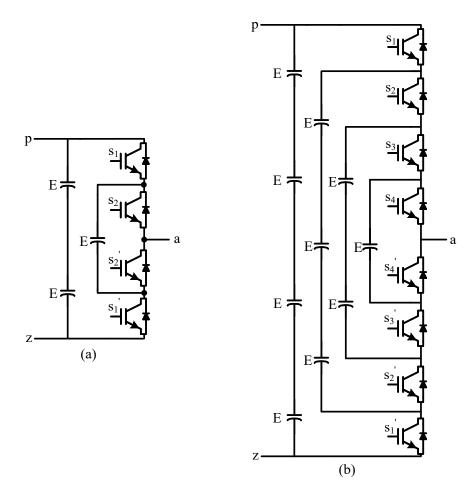

| Figure 2.7  | H-bridge converter topology (a) three-level full bridge converter (b) five-level cascade H-bridge converter.                                                    | 16      |

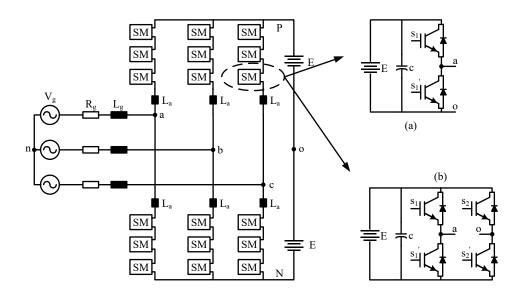

| Figure 2.8  | Cascade dual two level three phase inverter topology with equal DC link voltage ratio.                                                                          | 17      |

| Figure 2.9  | Modular multilevel converter topology (a) single modules with half bridge converters (b) single modules with full bridge converters.                            | 18      |

| Figure 2.10 | Hybrid nine-level converter topology, three-level NPC converter is series connected with three-level H-bridge converter.                                        | 19      |

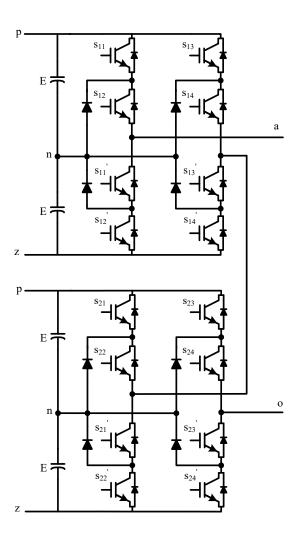

| Figure 2.11 | Hybrid nine-level converter topology, three-level NPC converter series connected with another three-level NPC converter.                                        | 20      |

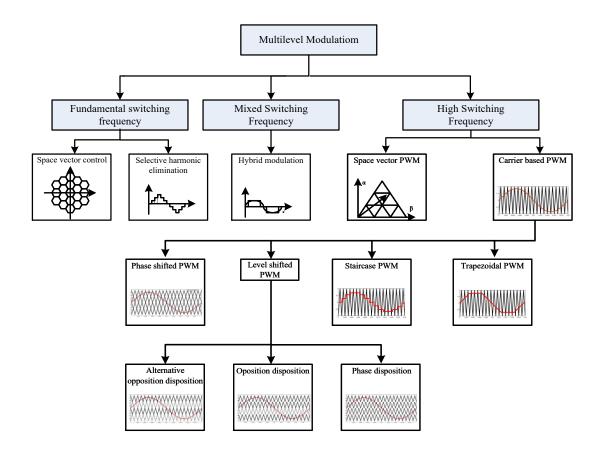

| Figure 2.12 | Classification of multilevel modulation technique.                                                                                                              | 21      |

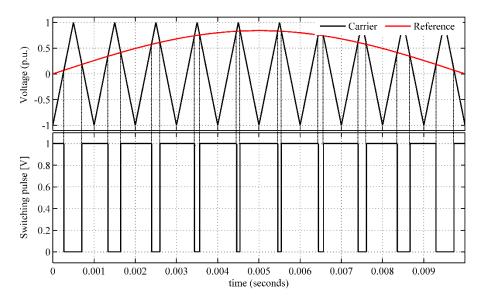

| Figure 2.13 | Carrier based modulation of two-level converter.                                                                                                                | 22      |

| Figure 2.14 | Third harmonic injection carrier based modulation of two-level converter.                                                                                       | 23      |

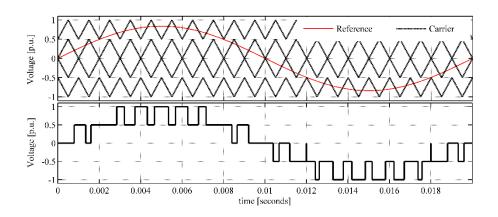

| Figure 2.15 | Phase shifted PWM for five-level converter.                                                                                                                     | 24      |

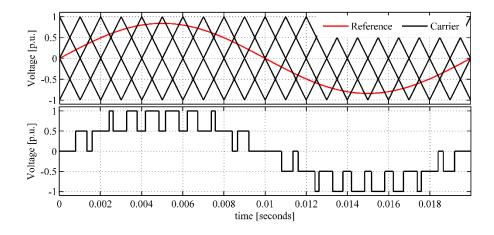

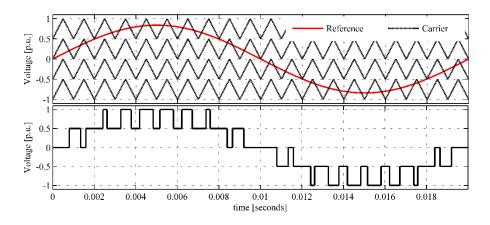

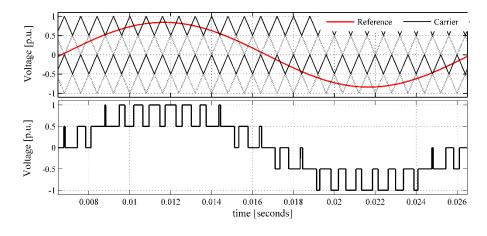

| Figure 2.16 | PD-PWM of five-level converter.                                                                                                                                 | 25      |

| Figure 2.17 | POD-PWM of five-level converter.                                                                                                                                | 25      |

| Figure 2.18 | APOD-PWM of five-level converter.                                                                                          | 25 |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----|

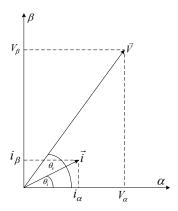

| Figure 2.19 | Voltage and current space vector in a two dimensional complex plane.                                                       | 27 |

| Figure 2.20 | A three-phase five-level diode clamped converter topology.                                                                 | 28 |

| Figure 2.21 | Space vector diagram of five-level converter.                                                                              | 28 |

| Figure 2.22 | Sector I of five-level converter.                                                                                          | 30 |

| Figure 2.23 | Seven segment switching sequence.                                                                                          | 31 |

| Figure 2.24 | Five segment (discontinuous) switching sequence.                                                                           | 31 |

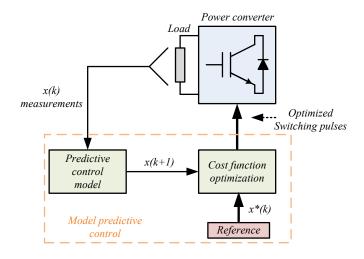

| Figure 2.25 | Block diagram of predictive control algorithm.                                                                             | 33 |

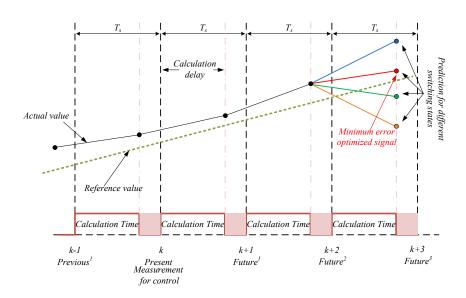

| Figure 2.26 | Sampling interval and switching state selection for predictive control.                                                    | 34 |

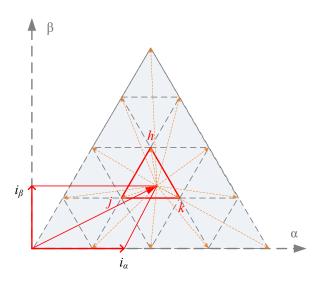

| Figure 2.27 | Current space vector diagram for MMPC algorithm.                                                                           | 35 |

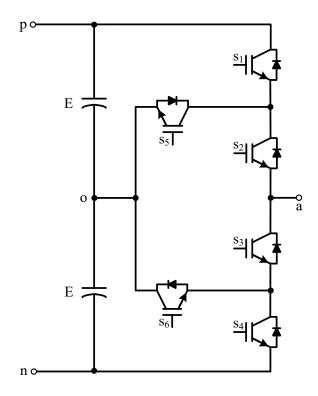

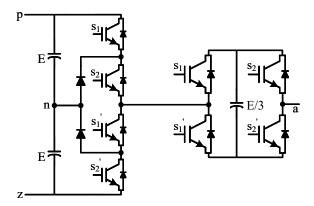

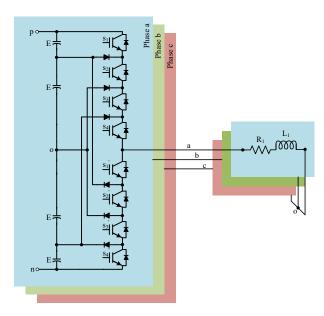

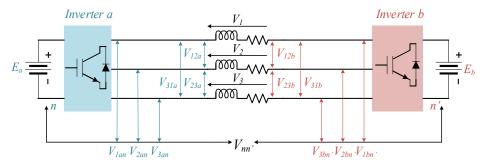

| Figure 3.1  | Dual two-level inverter with isolated sources.                                                                             | 38 |

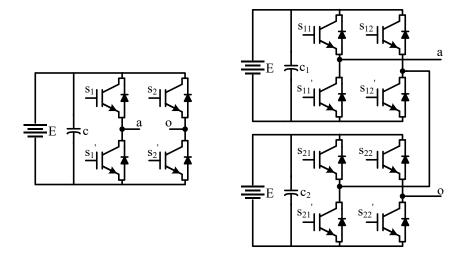

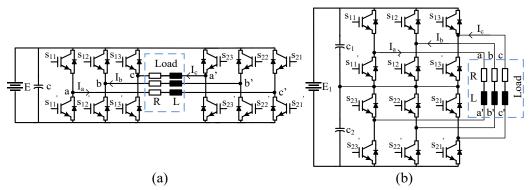

| Figure 3.2  | Dual two-level inverter with single source (a) parallel configuration (b) series configuration.                            | 39 |

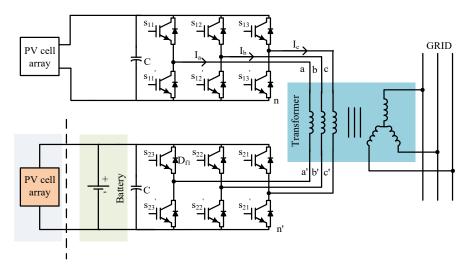

| Figure 3.3  | Dual inverter for PV applications.                                                                                         | 40 |

| Figure 3.4  | Dual inverter voltage states.                                                                                              | 41 |

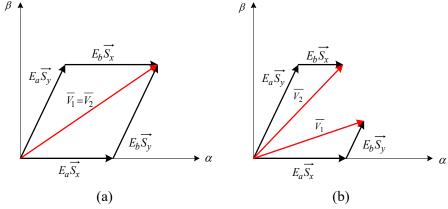

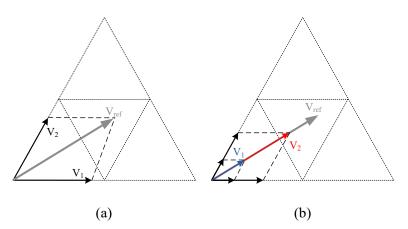

| Figure 3.5  | Voltage vector compositions (a) equal voltage sources (b) asymmetrical sources ratio of (2:1).                             | 44 |

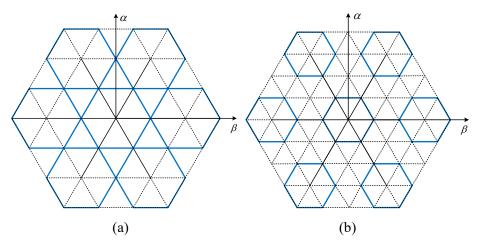

| Figure 3.6  | Space vector diagram of dual-two level inverter with asymmetric sources (a) sources ratio of 2:1 (b) sources ratio of 3:1. | 45 |

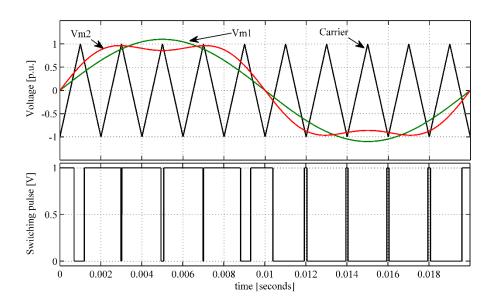

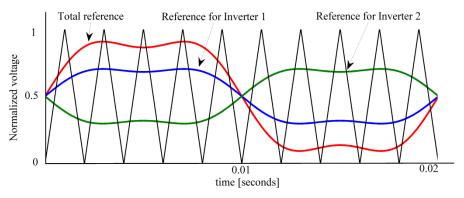

| Figure 3.7  | Carrier based modulation scheme where two references are used to modulate dual inverter with equal voltage sources.        | 45 |

| Figure 3.8  | Carrier based modulation scheme where two carrier signals are used to modulate dual inverter with equal voltage sources.   | 46 |

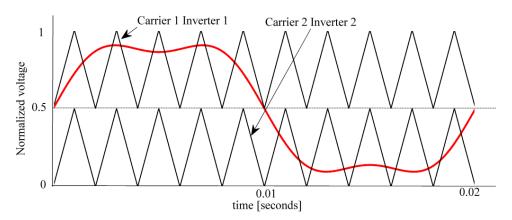

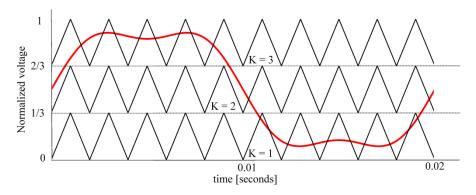

| Figure 3.9  | Carrier based modulation scheme where three references are used to modulate dual inverter with unequal voltage sources.    | 47 |

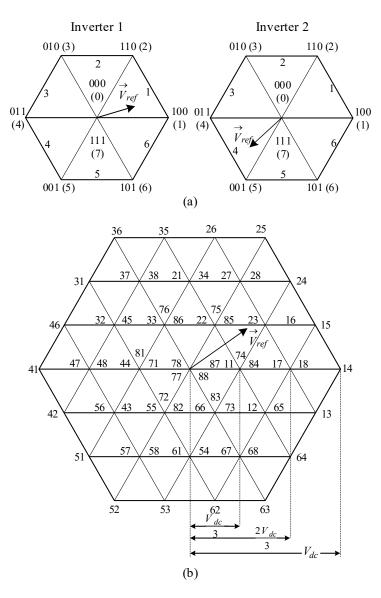

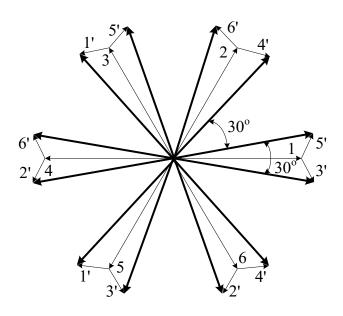

| Figure 3.10 | Space vector diagram of dual inverter with voltage ratio of 2:1 (a) individual inverters (b) dual inverter system.         | 48 |

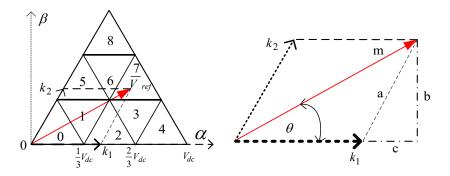

| Figure 3.11 | Subsector identification diagram.                                                                                          | 49 |

| Figure 3.12 | Seven segment switching sequence.                                                                                          | 50 |

|             |                                                                                                                            |    |

| Figure 3.13 | source ratio (b) dual inverter for common mode elimination.                                                    | 31 |

|-------------|----------------------------------------------------------------------------------------------------------------|----|

| Figure 3.14 | Vector diagram (a) traditional modulation (b) modified modulation to achieve power sharing.                    | 52 |

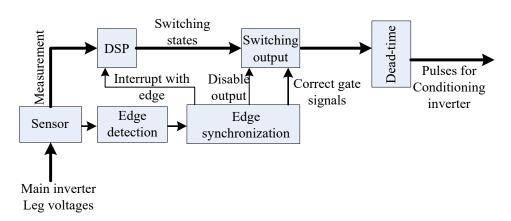

| Figure 3.15 | Hardware implementation block diagram of the conditioning inverter.                                            | 53 |

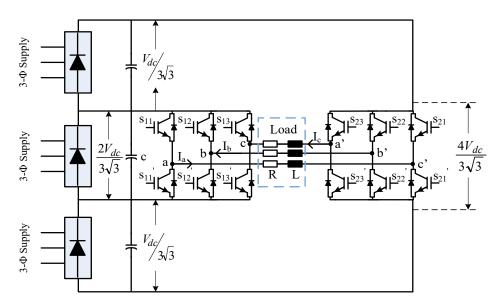

| Figure 3.16 | Dual inverter with asymmetric voltage sources with three DC sources.                                           | 54 |

| Figure 3.17 | Selected switching combinations of the vector positions for both the inverters for a voltage ratio of 1:0.366. | 55 |

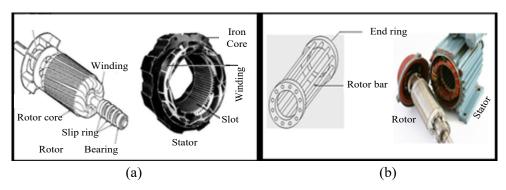

| Figure 4.1  | Rotor and stator construction (a) wound rotor induction motor (b) SCIM                                         | 57 |

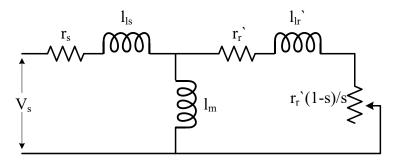

| Figure 4.2  | Equivalent circuit of squirrel cage induction motor.                                                           | 58 |

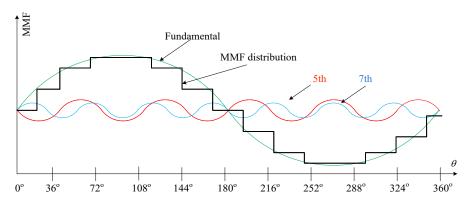

| Figure 4.3  | Ideal MMF distribution in the air gap.                                                                         | 62 |

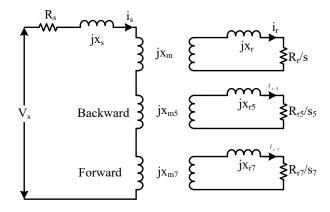

| Figure 4.4  | Conventional per-phase equivalent circuit (left) and modified equivalent circuit (right).                      | 63 |

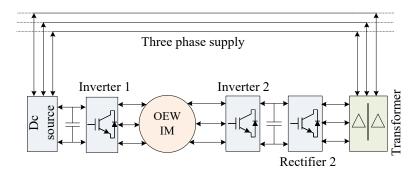

| Figure 4.5  | Open end winding IM drive with an isolation transformer.                                                       | 67 |

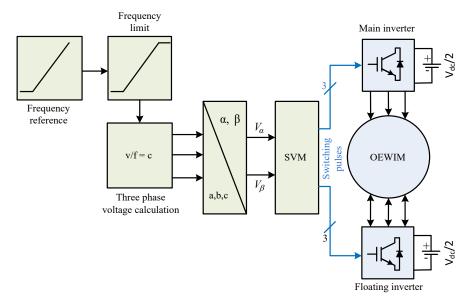

| Figure 4.6  | Block diagram of v/f controlled open end winding induction motor drive.                                        | 68 |

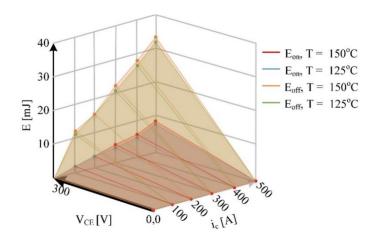

| Figure 4.7  | Switching loss profile for IGBT switch FF600R07ME4_B11.                                                        | 69 |

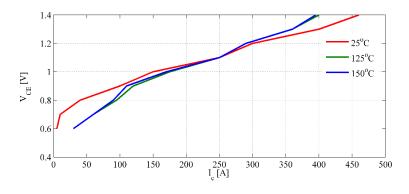

| Figure 4.8  | Conduction loss profile for IGBT switch FF600R07ME4_B11.                                                       | 69 |

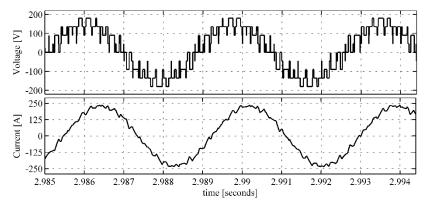

| Figure 4.9  | Phase voltage and current for the IM when the machine was fully loaded.                                        | 71 |

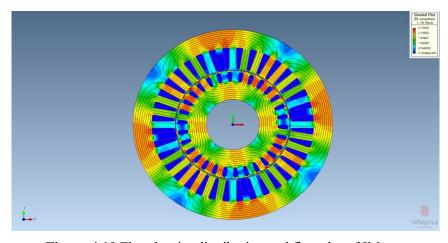

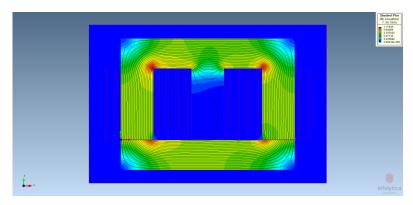

| Figure 4.10 | Flux density distribution and flux plot of IM.                                                                 | 72 |

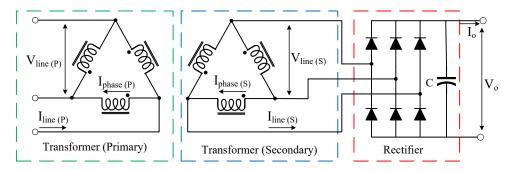

| Figure 4.11 | Three phase delta connected isolation transformer with a bridge rectifier.                                     | 73 |

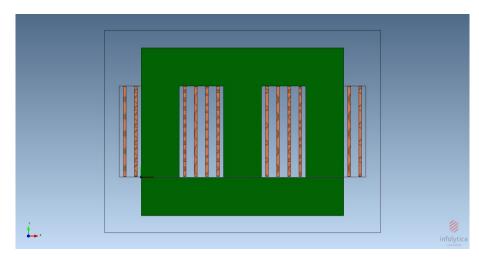

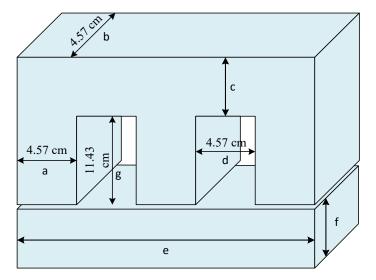

| Figure 4.12 | Isolation transformer designed in MagNet.                                                                      | 74 |

| Figure 4.13 | Flux function view of the transformer when it was loaded.                                                      | 75 |

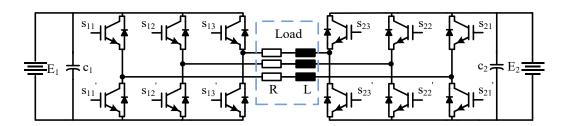

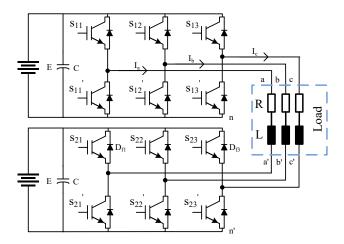

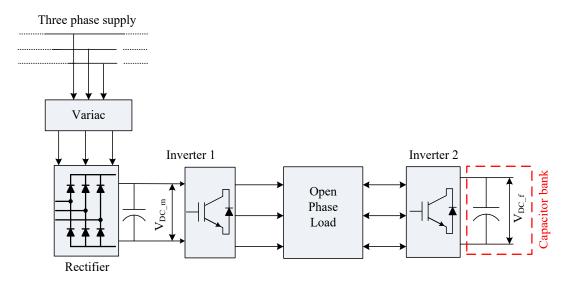

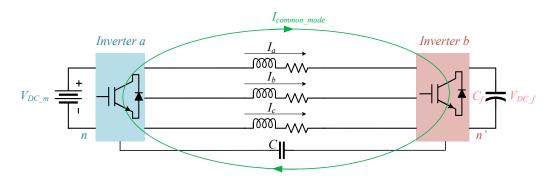

| Figure 5.1  | Block diagram of dual inverter with an open phase load.                                                        | 77 |

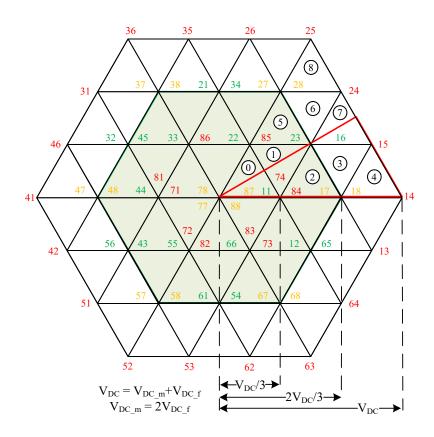

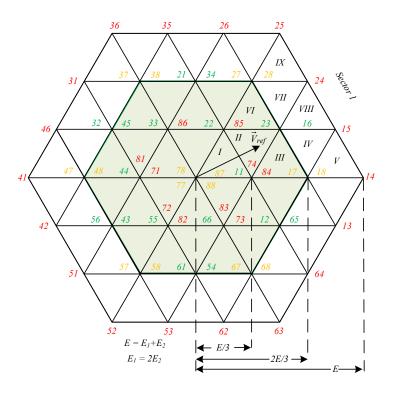

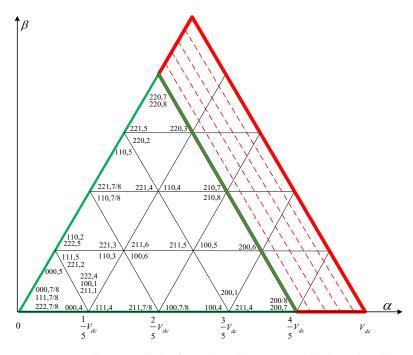

| Figure 5.2  | Space vector of dual two level inverter (source ratio 2:1).                                                    | 79 |

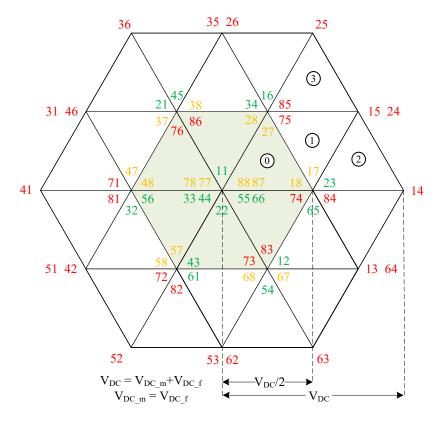

| Figure 5.3  | Space vector of dual two level inverter (source ratio 1:1).                                                    | 79 |

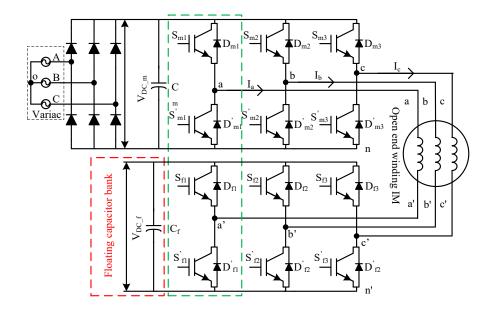

| Figure 5.4  | Power stage diagram of dual inverter with an open phase load.                                                                                                   | 80 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.5  | Current flow for different switching states.                                                                                                                    | 81 |

| Figure 5.6  | Circuit diagram of dual inverter when the switching state (11) is applied.                                                                                      | 82 |

| Figure 5.7  | Circuit diagram of dual inverter when the switching state (16) is applied.                                                                                      | 82 |

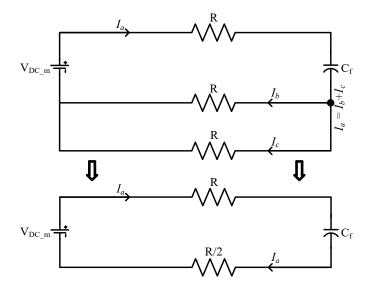

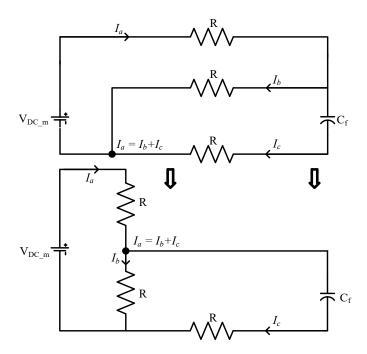

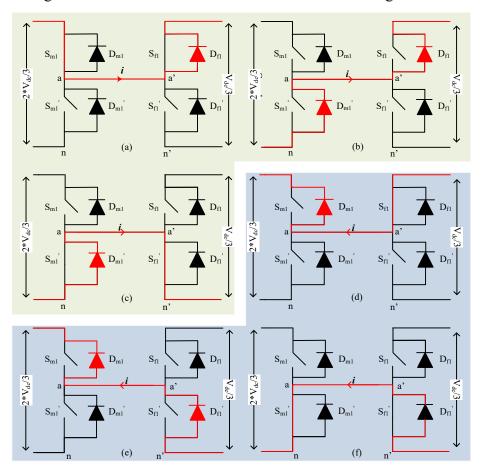

| Figure 5.8  | Dead-time effect for positive load current (a) current direction before dead-time (b) current direction during dead-time (c) current direction after dead-time. | 85 |

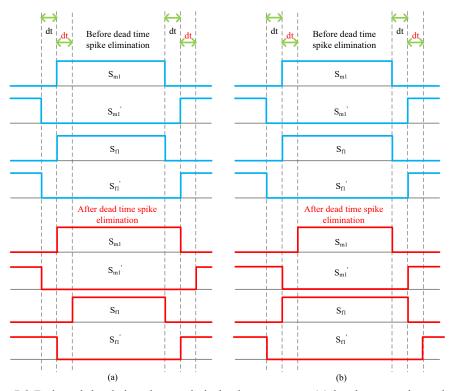

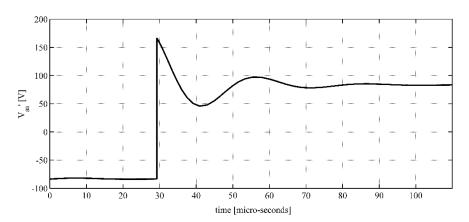

| Figure 5.9  | Delayed dead-time intervals in both converters (a) load current is positive (b) load current is negative.                                                       | 87 |

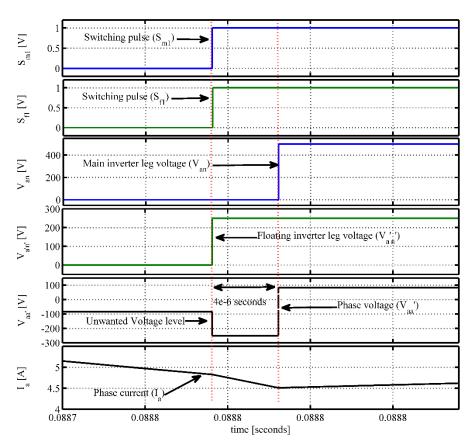

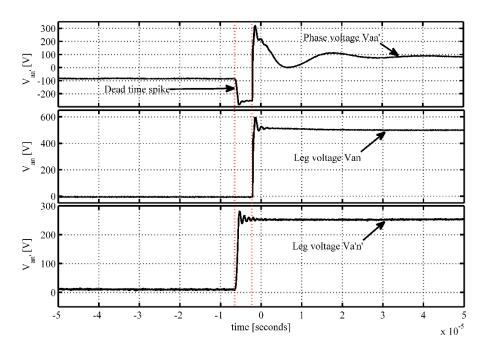

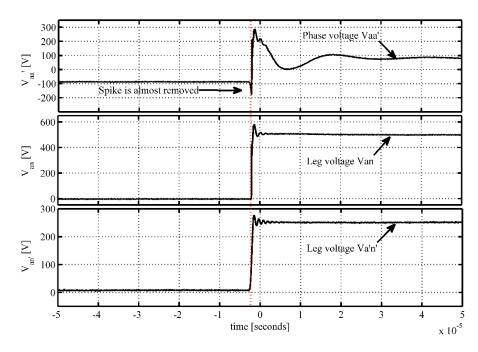

| Figure 5.10 | Switching pulses, leg voltages, phase voltage and current before dead-time elimination.                                                                         | 88 |

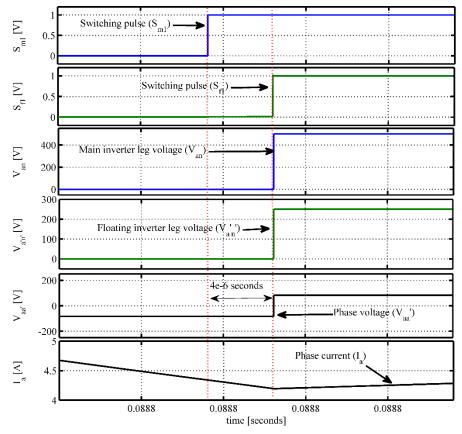

| Figure 5.11 | Switching pulses, leg voltages, phase voltage and current after dead-time elimination.                                                                          | 89 |

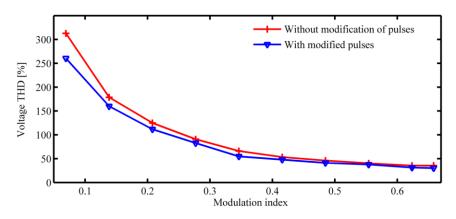

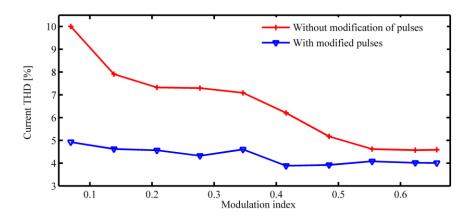

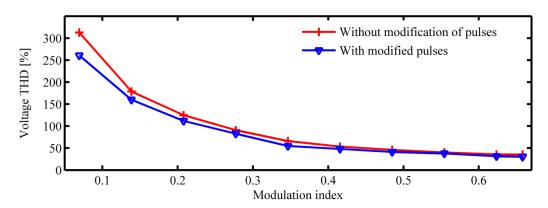

| Figure 5.12 | Voltage harmonic distortions with or without modification of output pulses.                                                                                     | 89 |

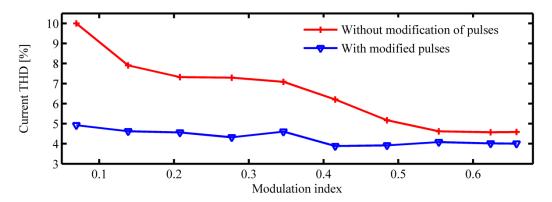

| Figure 5.13 | Current harmonic distortions with or without modification of output pulses.                                                                                     | 90 |

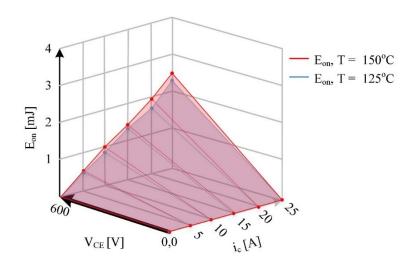

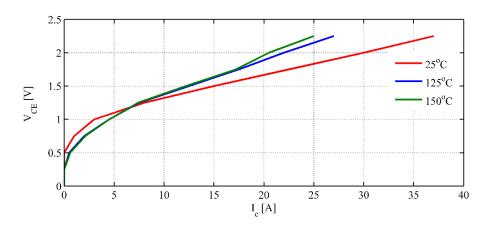

| Figure 5.14 | Turn-on switching loss profile for Infineon F12-25R12KT4G IGBT switches.                                                                                        | 93 |

| Figure 5.15 | Conduction loss profile for Infineon F12-25R12KT4G IGBT switches.                                                                                               | 93 |

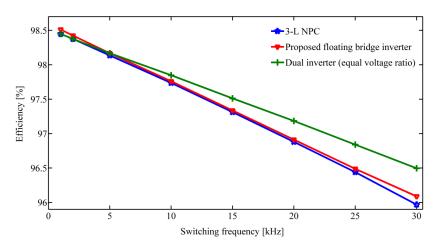

| Figure 5.16 | Loss comparison in different power converter topologies.                                                                                                        | 95 |

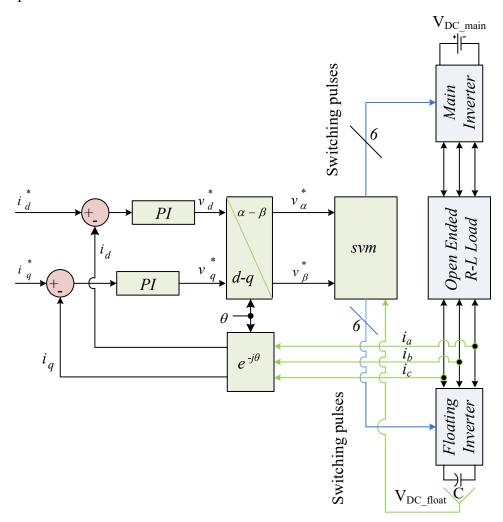

| Figure 5.17 | Block diagram of current controlled open phase R-L load.                                                                                                        | 96 |

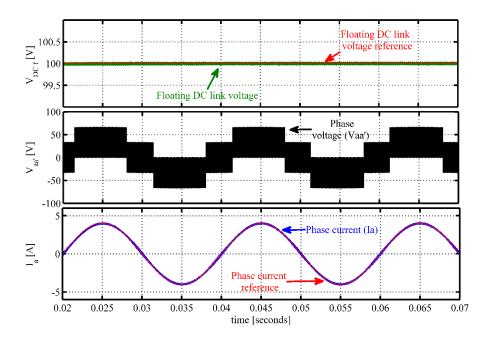

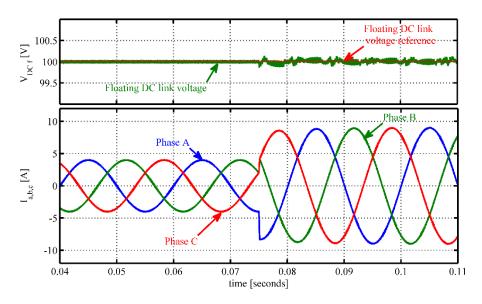

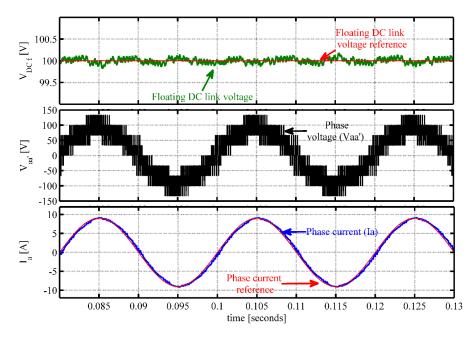

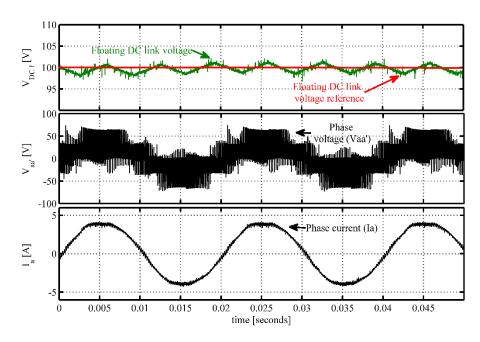

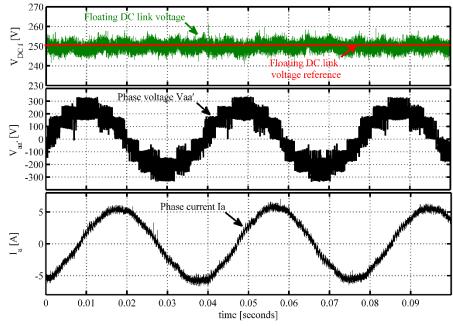

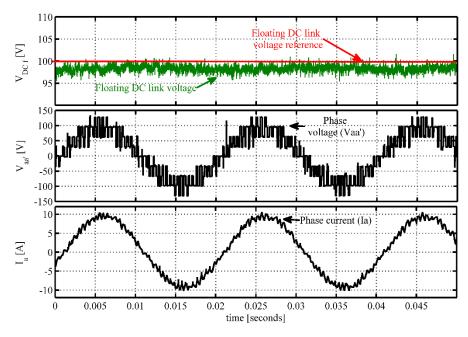

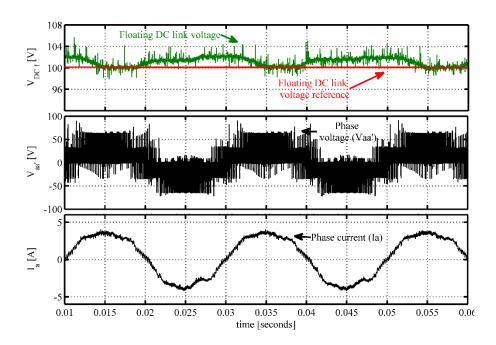

| Figure 5.18 | Floating DC link voltage, phase voltage and current for R-L load when the reference was set to 4 Amps.                                                          | 97 |

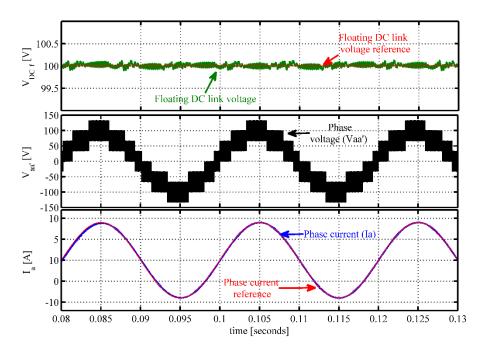

| Figure 5.19 | Floating DC link voltage, phase voltage and current for R-L when the reference was set to 9 Amps.                                                               | 98 |

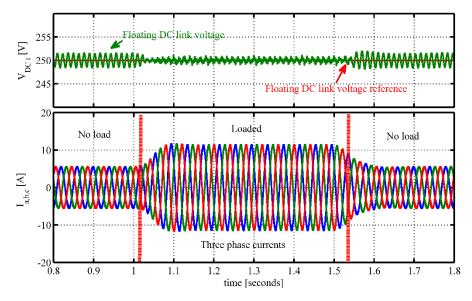

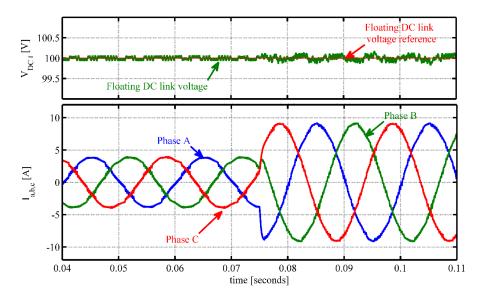

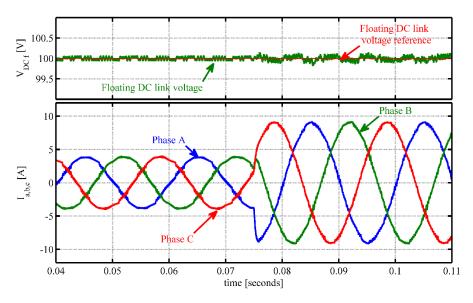

| Figure 5.20 | Step response of the controller (R-L load) from top to bottom: Floating DC link voltage, three phase currents.                                                  | 98 |

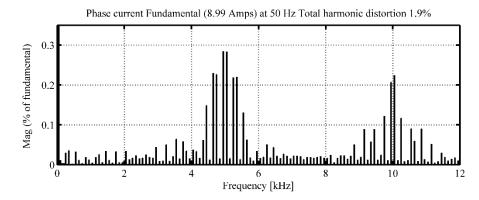

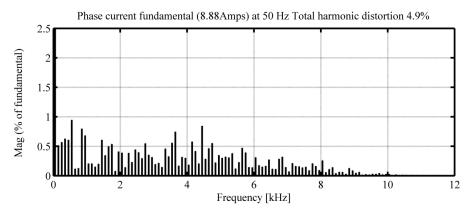

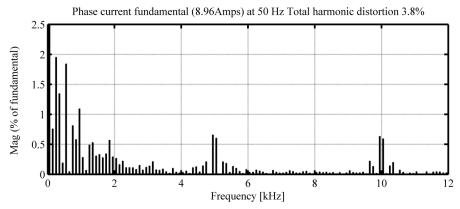

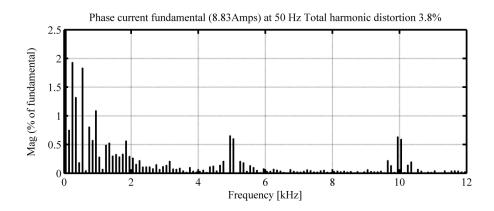

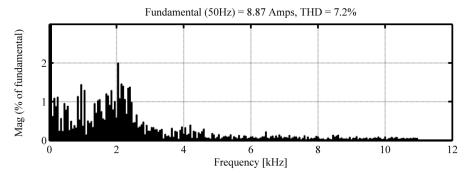

| Figure 5.21 | FFT of current when the converter was running at three level mode of operation.                                                                                 | 99 |

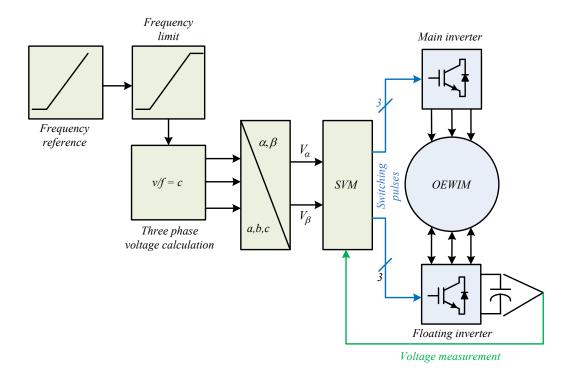

| Figure 5.22 | Block diagram of open loop v/f controlled induction motor drive.                                                               | 99  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

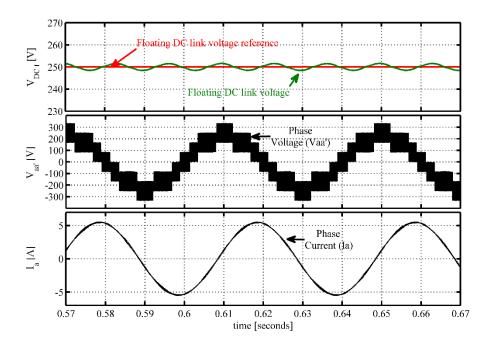

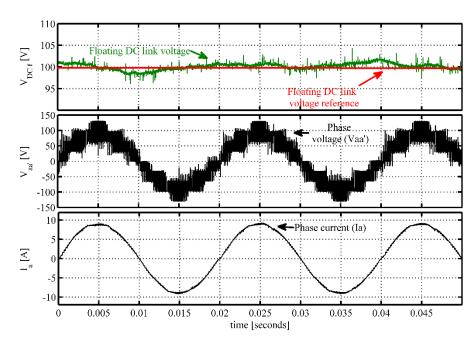

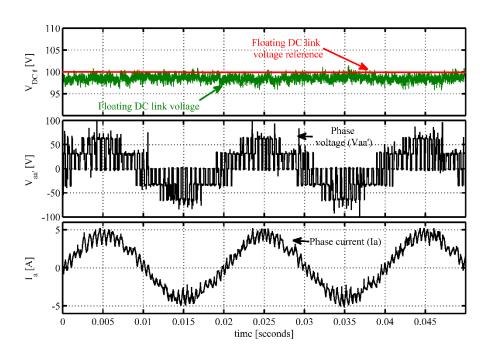

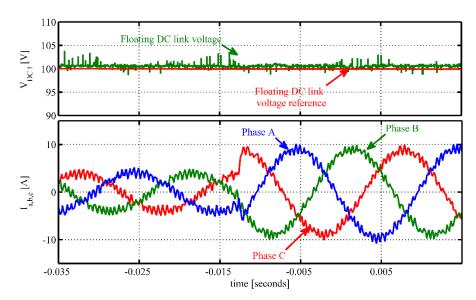

| Figure 5.23 | Floating DC link voltage, phase voltage and current for open loop $v/f$ IM drive when the reference frequency was set to 25Hz. | 100 |

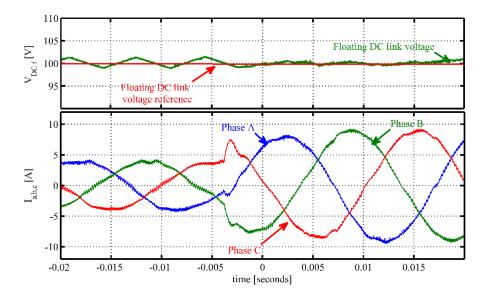

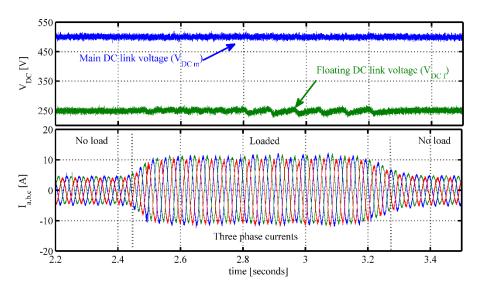

| Figure 5.24 | Floating DC link voltage and three phase currents for open loop $v/f$ IM drive when a load torque was applied to the machine.  | 100 |

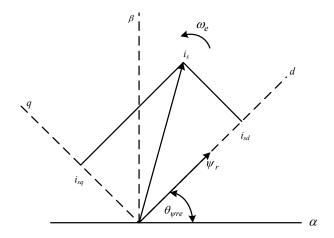

| Figure 5.25 | Phasor diagram of rotor flux orientation for IRFO based drives.                                                                | 102 |

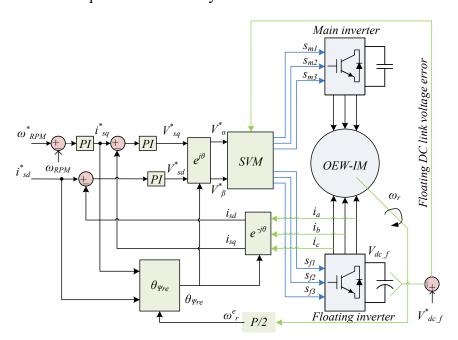

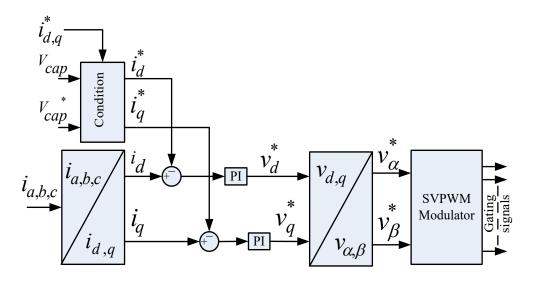

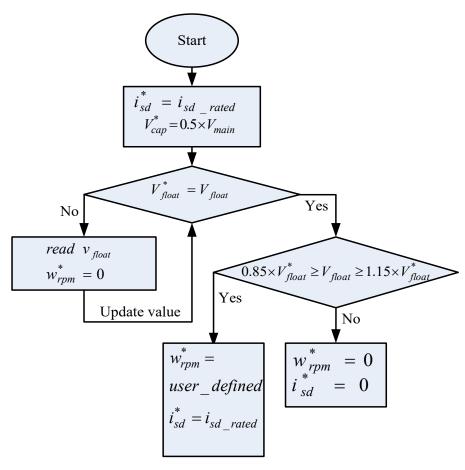

| Figure 5.26 | A block diagram of IRFO based OEWIM drive.                                                                                     | 104 |

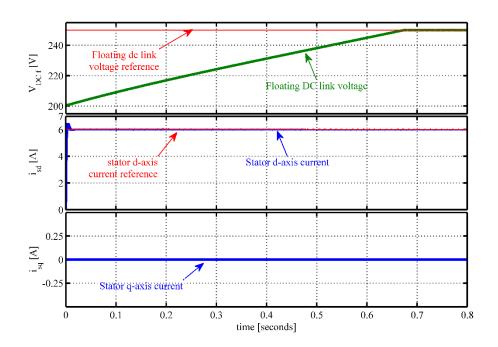

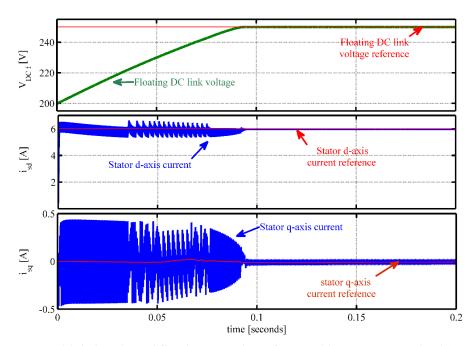

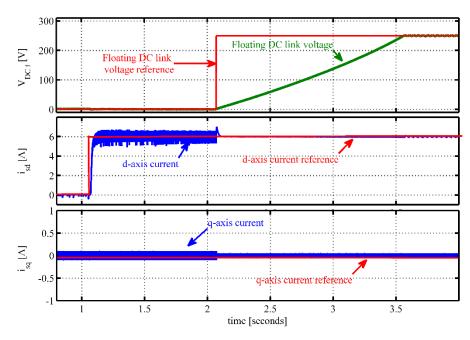

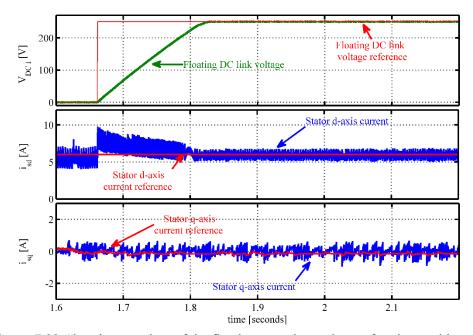

| Figure 5.27 | Initial charging of floating capacitor after machine was magnetised.                                                           | 105 |

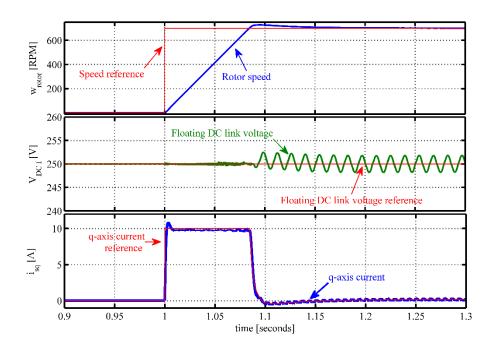

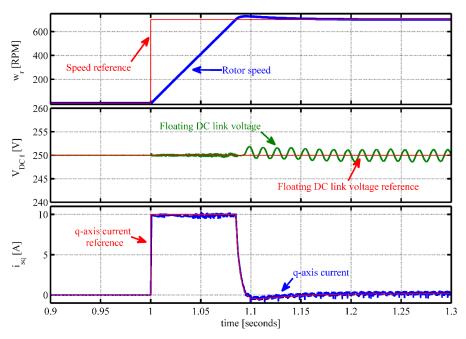

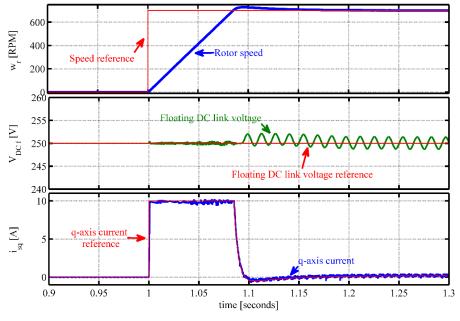

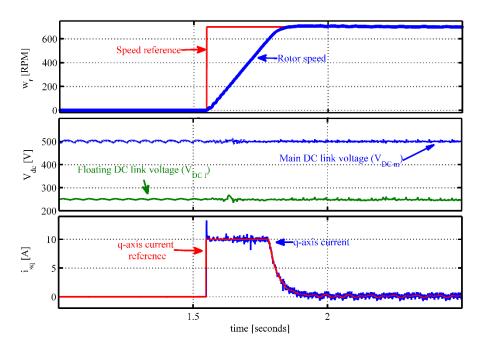

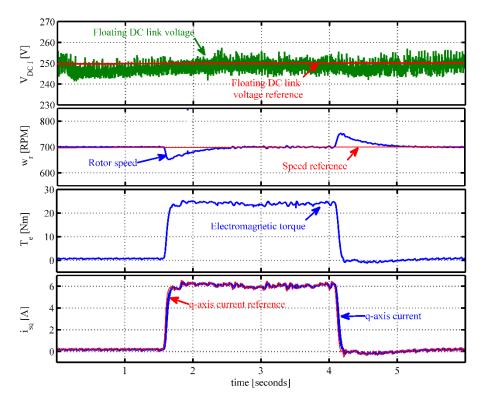

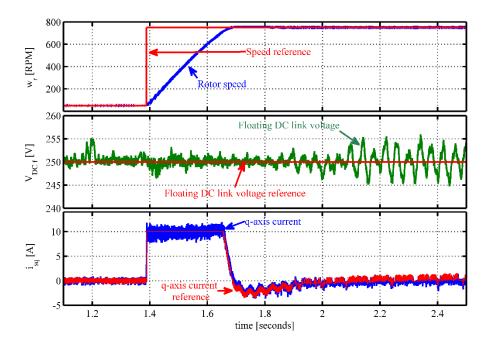

| Figure 5.28 | FOC response of no load speed to a step reference speed command.                                                               | 105 |

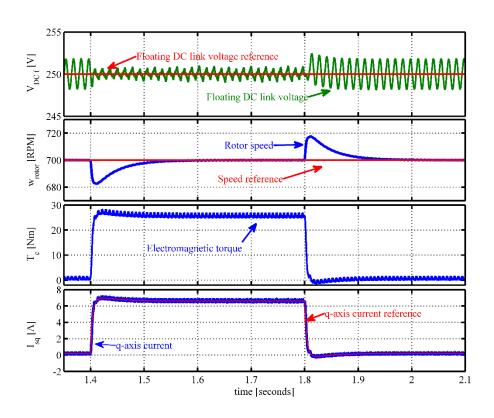

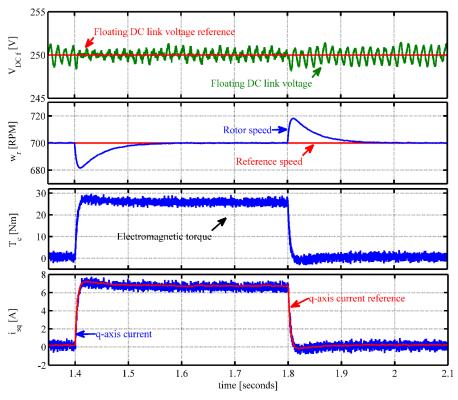

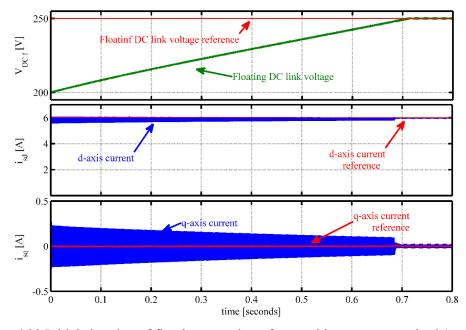

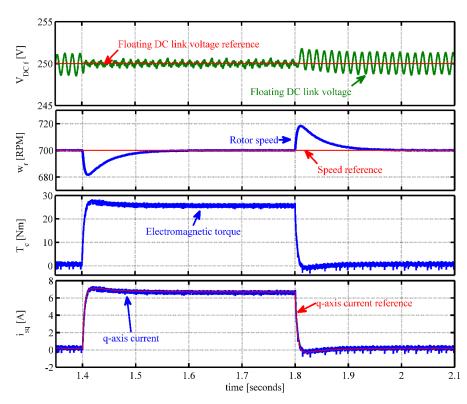

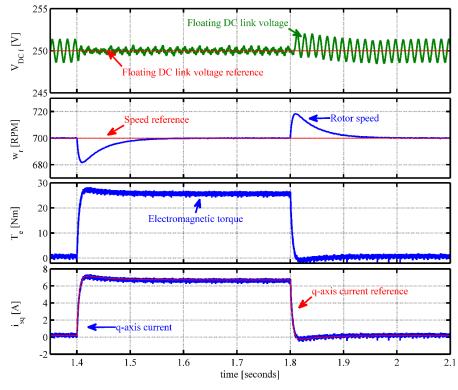

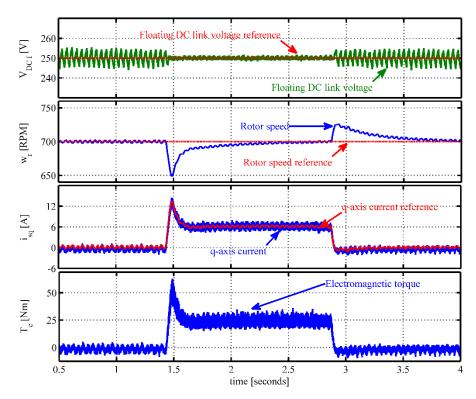

| Figure 5.29 | FOC response to a step load applied after the speed reaches steady-state.                                                      | 106 |

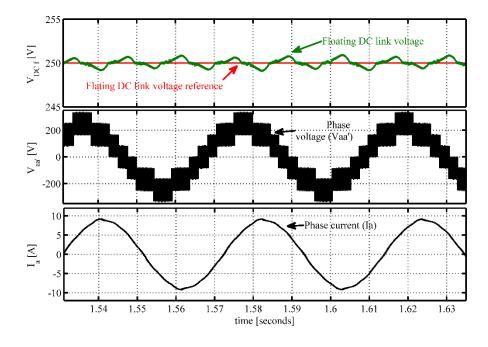

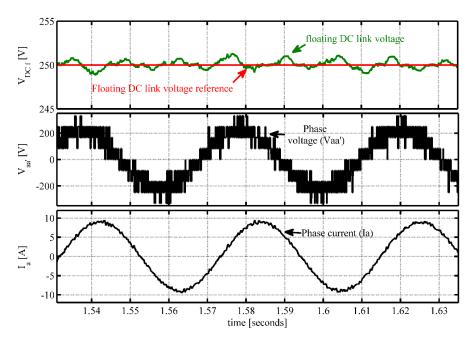

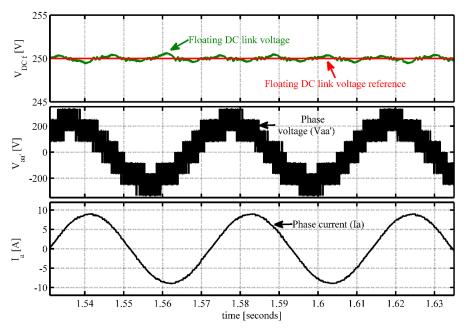

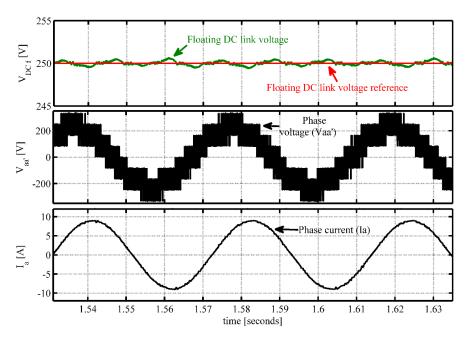

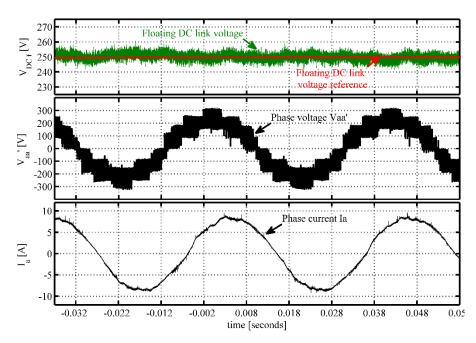

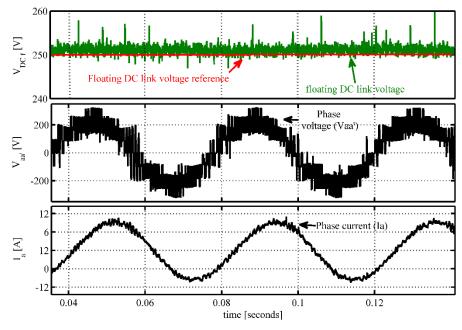

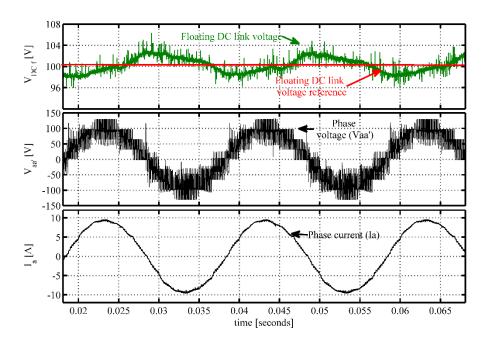

| Figure 5.30 | Floating DC link voltage, phase voltage $(V_{aa})$ and phase current $(I_a)$ when the machine was loaded.                      | 106 |

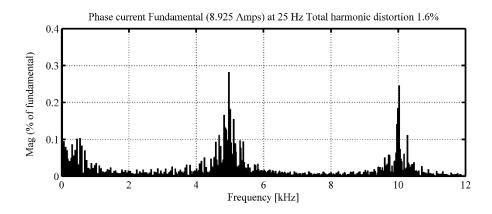

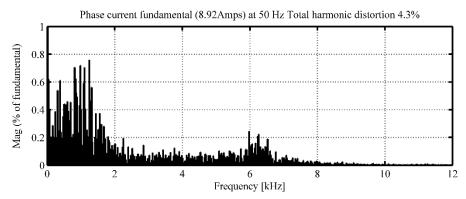

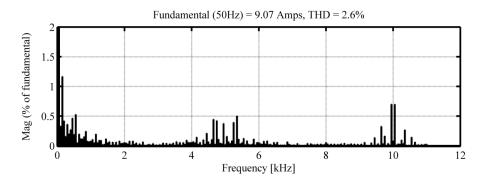

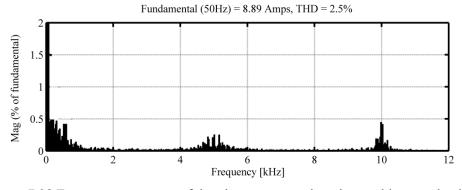

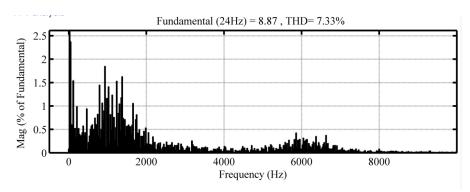

| Figure 5.31 | FFT of phase current when the machine was loaded.                                                                              | 107 |

| Figure 6.1  | Block diagram of predictive current controlled open phase R-L load.                                                            | 116 |

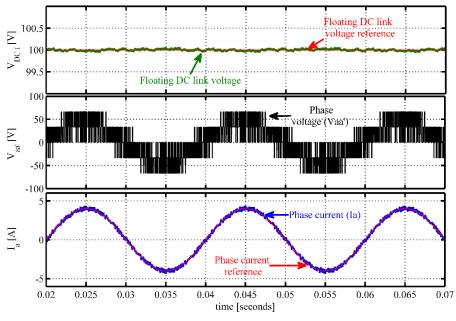

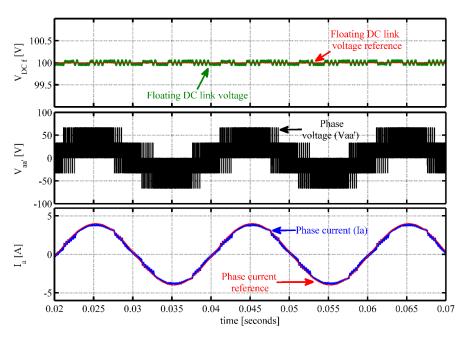

| Figure 6.2  | Floating DC link voltage, phase voltage and current for R-L load when the reference was set to 4 Amps.                         | 116 |

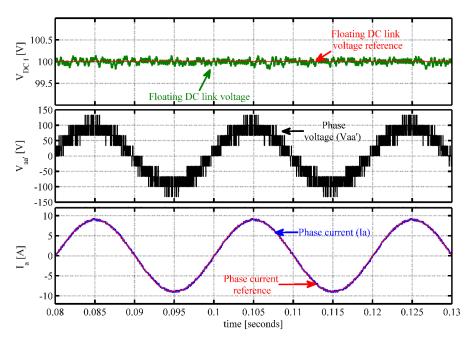

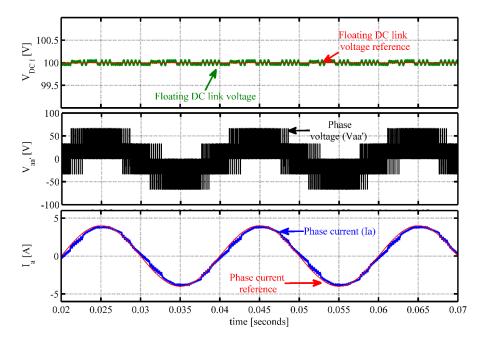

| Figure 6.3  | Floating DC link voltage, phase voltage and current for R-L load when the reference was set to 9 Amps.                         | 117 |

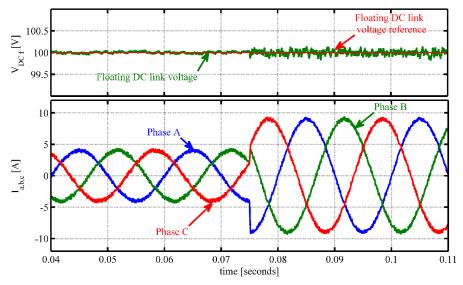

| Figure 6.4  | Step response of the controller (R-L load) from top to bottom: Floating DC link voltage, three phase currents.                 | 117 |

| Figure 6.5  | FFT of phase current when the when the converter was operating at three-level mode.                                            | 118 |

| Figure 6.6  | Block diagram of induction motor drive using predictive current control of dual two-level inverter with one bridge floating.   | 118 |

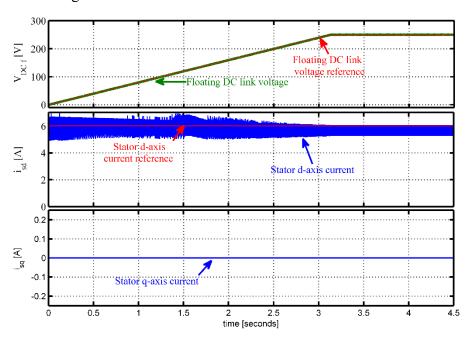

| Figure 6.7  | Initial charging of floating capacitor after machine was magnetised.                                                           | 119 |

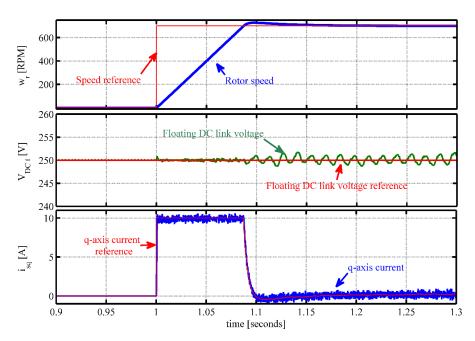

| Figure 6.8  | Predictive control response of no load speed to a step reference speed command.                                                | 120 |

| Figure 6.9  | MPC response to a step load applied after the speed reaches steady-state.                                                      | 120 |

|             |                                                                                                                                |     |

| Figure 6.10 | MPC response to a step load applied after the speed reaches steady-state.                                                                           | 121 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.11 | FT of phase current when the when the machine was loaded.                                                                                           | 121 |

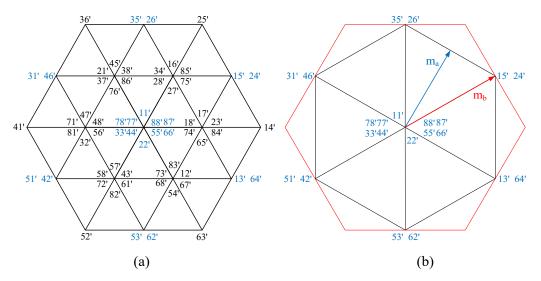

| Figure 6.12 | Space vector diagram of the proposed system.                                                                                                        | 123 |

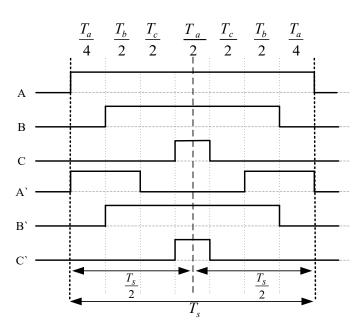

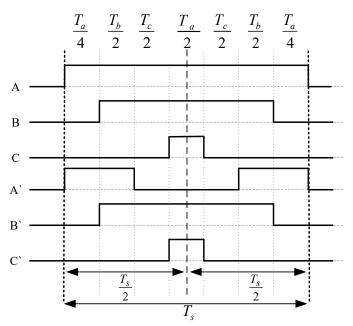

| Figure 6.13 | Seven segment switching sequence for MMPC algorithm.                                                                                                | 125 |

| Figure 6.14 | Floating DC link voltage, phase voltage and current for R-L load when the reference was set to 4 Amps (capacitor control in cost function).         | 126 |

| Figure 6.15 | Floating DC link voltage, phase voltage and current for R-L load when the reference was set to 4 Amps (capacitor control in modulation).            | 126 |

| Figure 6.16 | Floating DC link voltage, phase voltage and current for R-L load when the reference was set to 9 Amps (capacitor control in cost function).         | 127 |

| Figure 6.17 | Floating DC link voltage, phase voltage and current for R-L load when the reference was set to 9 Amps (capacitor control in modulation).            | 127 |

| Figure 6.18 | Step response of the controller (R-L load) from top to bottom: Floating DC link voltage, three phase currents (capacitor control in cost function). | 128 |

| Figure 6.19 | Step response of the controller (R-L load) from top to bottom: Floating DC link voltage, three phase currents (capacitor control in modulation).    | 128 |

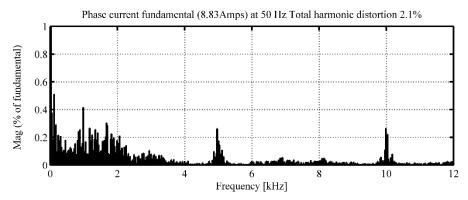

| Figure 6.20 | FFT of phase current when 9Amps current was demanded from the system (capacitor charging in cost function)                                          | 129 |

| Figure 6.21 | FFT of phase current when 9Amps current was demanded from the system (capacitor charging in modulation scheme).                                     | 129 |

| Figure 6.22 | Initial charging of floating capacitor after machine was magnetised (capacitor control in cost-function).                                           | 130 |

| Figure 6.23 | Initial charging of floating capacitor after machine was magnetised (capacitor control in modulation).                                              | 130 |

| Figure 6.24 | FOC response of no load speed to a step reference speed command (capacitor control in cost-function).                                               | 131 |

| Figure 6.25 | FOC response of no load speed to a step reference speed command (capacitor control in modulation).                                                  | 131 |

| reaches steady-state (capacitor control in cost function).                                                                                       | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FOC response to a step load applied after the speed reaches steady-state (capacitor control in modulation).                                      | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

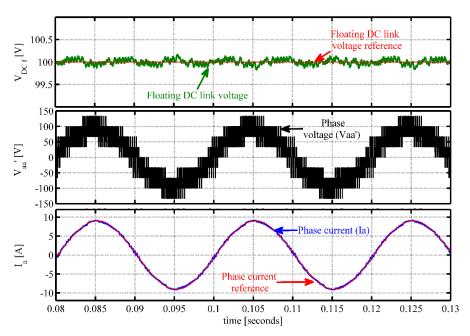

| Floating DC link voltage, phase voltage and current when the machine was loaded (capacitor control in cost-function).                            | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Floating DC link voltage, phase voltage and current when the machine was loaded (Capacitor control in modulation).                               | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

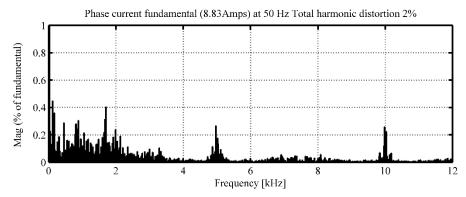

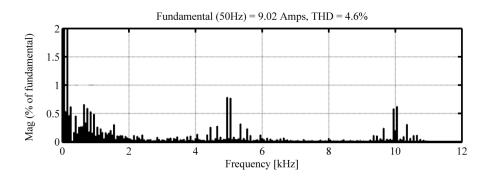

| FFT of phase current when the machine was loaded (cap-charge in cost function).                                                                  | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FFT of phase current when the machine was loaded (cap-charge in modulation).                                                                     | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

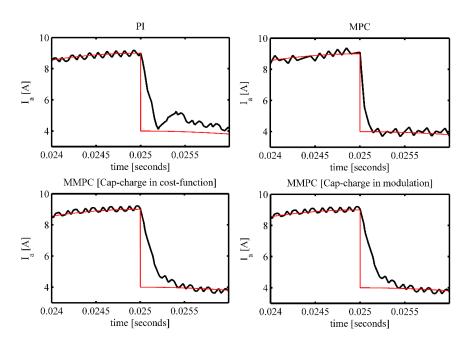

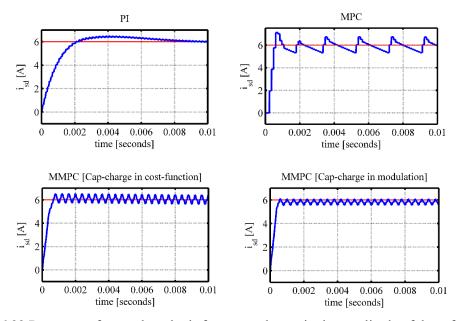

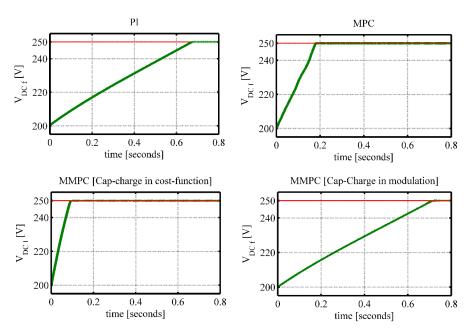

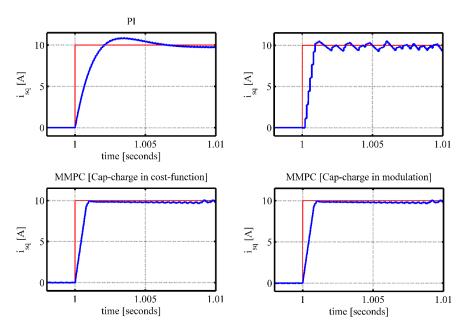

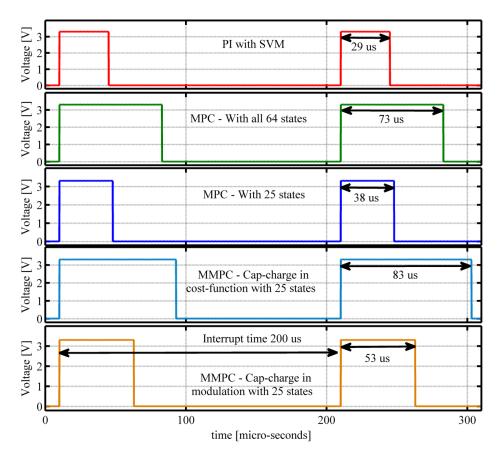

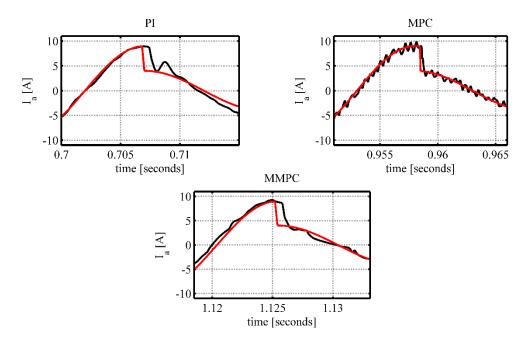

| Response of control methods for a step change in the amplitude of the reference current for R-L load.                                            | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

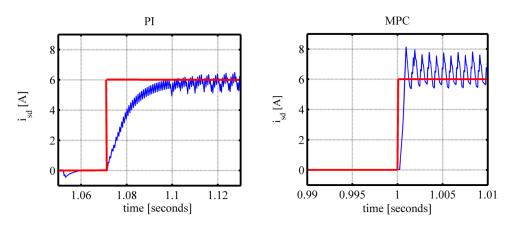

| Response of control methods for a step change in the amplitude of the reference flux producing current $(i^*_{sd})$ for induction motor drive.   | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

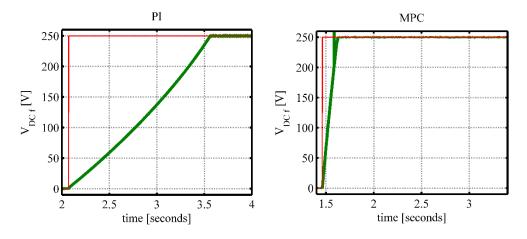

| Response of control methods for a step change in the amplitude of the reference floating DC link voltage for induction motor drive.              | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

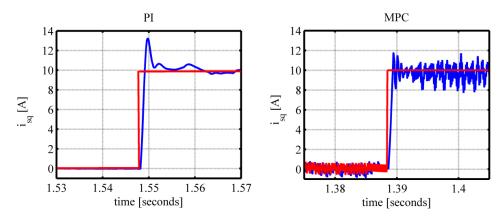

| Response of control methods for a step change in the amplitude of the reference torque producing current $(i_{sq}^*)$ for induction motor drive. | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

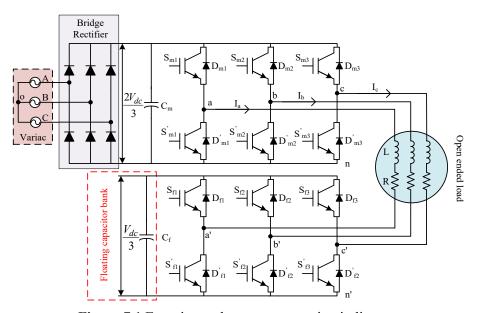

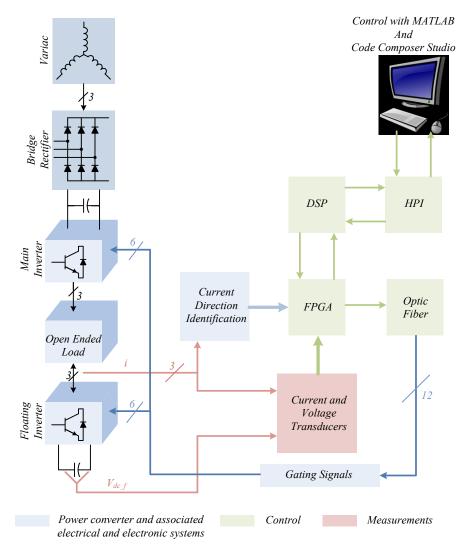

| Experimental arrangements circuit diagram.                                                                                                       | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Block diagram of control implementation.                                                                                                         | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

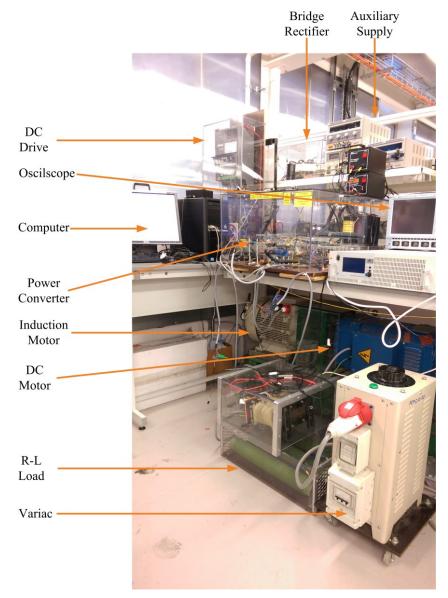

| Experimental setup.                                                                                                                              | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

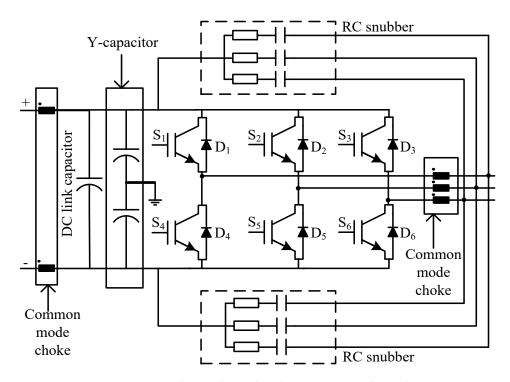

| Experimental two-level converter configuration.                                                                                                  | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

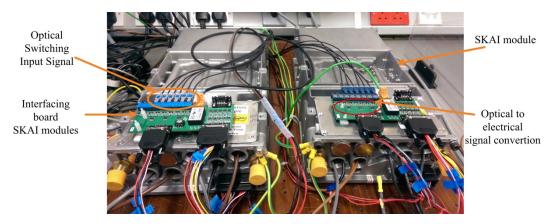

| SKAI module and interfacing board.                                                                                                               | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Control platforms.                                                                                                                               | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Circuit diagram of current direction identification circuit.                                                                                     | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Current direction detection circuits.                                                                                                            | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |