# Development of Phase Change Memory Cell Electrical Circuit Model for Non-volatile Multistate Memory Device

Nemat Hassan Ahmed ElHassan, BSc.

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

#### **Abstract**

Phase change memory (PCM) is an emerging non-volatile memory technology that demonstrates promising performance characteristics. The presented research aims to study the feasibility of using resistive non-volatile PCM in embedded memory applications, and in bridging the performance gap in traditional memory hierarchy between volatile and non-volatile memories.

The research studies the operation dynamics of PCM, including its electrical, thermal and physical properties; in order to determine its behaviour. A PCM cell circuit model is designed and simulated with the aid of SPICE tools (LTSPICE IV). The first step in the modelling process was to design a single-level PCM (SLPCM) cell circuit model that stores a single bit of data. To design the PCM circuit model; crystallization theory and heat transfer equation were utilized. The developed electrical circuit model evaluates the physical transformations that a PCM cell undergoes in response to an input pulse. Furthermore, the developed model accurately simulated the temperature profile, the crystalline fraction, and the resistance of the cell as a function of the programming pulse.

The circuit model is then upgraded into a multilevel phase change memory (MLPCM) cell circuit model. The upgraded MLPCM circuit model stores two bits of data, and incorporates resistance drift with time. The multiple resistance levels were achieved by controlling the programming pulse width in the range of 10ns to 200ns. Additionally, the drift behaviour was precisely evaluated; by using statistical data of drift exponents, and evaluating the exact drift duration.

Moreover, the simulation results for the designed SLPCM and MLPCM cell models were found to be in close agreement with experimental data. The simulated I-

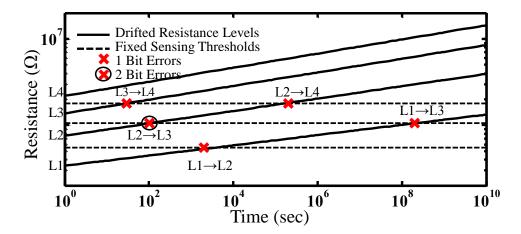

V characteristics for both SLPCM and MLPCM mimicked the experimentally produced I-V curves. Furthermore, the simulated drift resistance levels matched the experimental data for drift durations up to  $10^3$  seconds; which is the available experimental data duration in technical literature. Furthermore, the simulation results of MLPCM showed that the deviation between the programmed and drifted resistance can reach  $6x10^6\Omega$  in less than  $10^{10}$  seconds. This resistance deviation leads to reading failures in less than 100 seconds after programming, if standard fixed sensing thresholds method was used.

Therefore, to overcome drift reliability issues, and retain the density advantage offered by multilevel operation; a time-aware sensing scheme is developed. The designed sensing scheme compensates for the drift caused resistance deviation; by using statistical data of drift coefficients to forecast adaptive sensing thresholds. The simulation results showed that the use of adaptive time-aware sensing thresholds completely eliminated drift reliability issues and read errors.

Furthermore, PCM based nanocrossbar memory structure performance in terms of delay and energy consumption is studied in simulation environment. The nanocrossbar is constructed with a grid of connecting wires; and the designed PCM cell circuit model is used as memory element and placed at junction points of the grid. Then the effect of connecting nanowires resistance in PCM nanocrossbar performance is studied in passive crossbars. The resistance of a connecting wire segment was evaluated with physical formulas that calculate nanoscaled conductors' resistance. Then a resistor that is equivalent to each wire segment resistance is placed in the tested crossbar structure.

Simulation results showed that due to connecting wires resistance; the PCM cells are not truly biased to programming voltage and ground. This leads to 40% deviation

in the programed low resistive state from the targeted levels. Thus, affecting PCM reliability and decreasing the high to low resistance ratio by 90%.

Therefore, programming and architectural solutions to wire resistance related reliability issue are presented. Where dissipated power across wire resistance is compensated for; by controlling programming pulse duration. The programming solution retained reliability however; it increased programming energy consumption and delay by an average of 40pJ and 60ns respectively per operation.

Additionally, the effects of leakage energy in PCM based nanocrossbars were studied in simulation environment. Then, a structural solution was developed and designed. In the designed structure; leakage sneak paths are eliminated by introducing individual word lines to each memory element. This method led to 30% reduction in reading delay, and consumed only about sixth the leakage energy consumed by the standard structure.

Moreover, a sensing scheme that aims to reduce energy consumption in PCM based nanocrossbars during reading process was explored. The sensing method is developed using AC current in contrast to the standard DC current reading circuits. In the designed sensing circuit, a low pass filter is utilized. Accordingly, the filter attenuation of the applied AC reading signal indicates the stored state. The proposed circuit design of the AC sensing scheme was constructed and studied in simulation environment. Simulation results showed that AC sensing has reduced reading energy consumption by over 50%; compared to standard DC sensing scheme.

Furthermore, the use of SLPCM and MLPCM in memory applications as crossbar memory elements, and in logic applications i.e. PCM based LUTs was explored and tested in simulation environment. The PCM performance in crossbar memory was then compared to current Static Random Access Memory (SRAM)

technology and against one of the main emerging resistive non-volatile memory technologies i.e. Memristors.

Simulation results showed that programming and reading energy consumption of PCM based crossbars were five orders of magnitude more than SRAM based crossbars. And reading delay of SRAM based crossbars was only 38% of reading delay of PCM based counterparts. However, PCM cells occupies less than 60% of the area required by SRAM and can store multiple bit in a single cell.

Moreover, Memristor based nanocrossbars outperformed PCM based ones; in terms of delay and energy consumption. With PCM consuming 2 orders of magnitude more energy during programming and reading. PCM also required 10 times the programming delay. However, PCM crossbars offered higher switching resistance range i.e.  $170k\Omega$  compared to the  $20k\Omega$  offered by memristors; which support PCM multibit storage capability and higher density.

### Acknowledgment

Thank God for all his blessings. My guidance comes from him. In him I trust and unto him I turn.

My sincere thanks go to Dr. Nandha Kumar, my supervisor for his patience, motivation, and guidance that helped me in all the time of research and writing of this thesis. My deep gratitude goes to my advisor Prof. Haider Abbas, for his continuous support and giving me the opportunity to peruse my Ph.D. study.

Thanks to my dear parents Hassan Ahmed ElHassan & Zubaida Mohammed Ali for being my biggest supporters and critics, and standing by me through my life.

Their unlimited love gave me strength and determination.

Finally, I would like to thank everyone who helped and supported me throughout my research.

#### **List of Publications**

#### **Conference Proceedings**

- Nemat H. El-Hassan, T. Nandha Kumar, and Haider Abbas F. Almurib, "Improved SPICE Model for Phase Change Memory Cell", *IEEE 5th International Conference on Intelligent and Advanced Systems ICIAS*, Kuala Lumpur, Malaysia, June 2014. (*Shortlisted for the Best Presenter Award*)

DOI: 10.1109/ICIAS.2014.6869529)

- Ong Ming Hong, Nemat H. El-Hassan, T. Nandha Kumar, and Haider Abbas F. Almurib, "A Novel Emulator Design for Phase Change Memory", IEEE 2nd International Conference on Electronic Design, Penang, Malaysia, August 2014. DOI: 10.1109/ICED.2014.7015779

- Nemat H. El-Hassan, T. Nandha Kumar, and Haider Abbas F. Almurib, "Multilevel Phase Change Memory Cell Model", *IEEE Asia Pacific Conference on Circuits and Systems*, Okinawa, Japan, November 2014. DOI: 10.1109/APCCAS.2014.7032822

- Patrick W. C. Ho, Nemat H. El-Hassan, T. Nandha Kumar, and Haider Abbas F. Almurib, "PCM and Memristor Based Nanocrossbars," *IEEE International Conference on Nanotechnology, Rome, Italy*, July, 2015. DOI: 10.1109/NANO.2015.7388636

- Nemat H. El-Hassan, M. R. Ahmed Shahad, T. Nandha Kumar, and Haider Abbas F. Almurib, "AC Sense Circuit for Memristor Based Memory Crossbar", *IEEE student conference on research and development, Kuala Lumpur*, Malaysia, December 2015. DOI: 10.1109/SCORED.2015.7449367

- 6. **Nemat H. El-Hassan**, T. Nandha Kumar, and Haider Abbas F. Almurib, "Performance study of Phase Change Memory in Different Crossbar Architectures," *The International Nanotech and Nanoscience Conference and Exhibition*, Paris, June 2015.

#### **Refereed Journals**

- 1. Nemat H. El-Hassan, T. Nandha Kumar, and Haider Abbas F. Almurib, "Time-Aware Multilevel Phase Change Memory Cell", Elsevier Microelectronic Journal, Vol. 56, 74–80, October 2016. pp. http://dx.doi.org/10.1016/j.mejo.2016.08.007

- Nemat H. El-Hassan, T. Nandha Kumar, and Haider Abbas F. Almurib, "Wire Resistance Effect in PCM Based Nanocrossbar Array," *IET Journal of Engineering*, 2016. DOI: 10.1049/joe.2016.0212

- Nemat H. El-Hassan, Ong Ming Hong, T. Nandha Kumar, and Haider Abbas F. Almurib, "Phase Change Memory Cell Emulator Circuit Design", *Elsevier Microelectronic Journal*, 2016.

## **Table of Contents**

| Abstract      |                                      | I    |

|---------------|--------------------------------------|------|

| Acknowledg    | gment                                | V    |

| List of Publ  | ications                             | VI   |

| Table of Co   | ntents                               | VIII |

| List of Figur | res                                  | XI   |

| List of Table | es                                   | XVI  |

| Glossary      |                                      | I    |

| CHAPTER       | 1                                    | 2    |

|               |                                      | 2    |

| Introduct     | on<br>ackground                      | 2    |

|               | ims                                  | 5    |

|               | bjectives                            | 5    |

|               | ontribution of the research          | 6    |

|               | nesis outline                        | 7    |

| CHAPTER       |                                      | 10   |

| Prelimina     | uries                                |      |

| 2.1 O         | verview                              | 10   |

| 2.2 M         | emory Performance Characteristics    | 10   |

| 2.3 Tı        | raditional memory hierarchy          | 12   |

| 2.3.1         | SRAM                                 | 13   |

| 2.3.2         | DRAM                                 | 13   |

| 2.3.3         | Flash memory                         | 13   |

| 2.4 Eı        | merging resistive NVM                | 15   |

| 2.4.1         | Resistive RAM (ReRAM) "Memristor"    | 16   |

| 2.4.2         | Phase change memory (PCM)            | 16   |

| 2.4.3         | Magnetic Tunnel Junction (MTJ)       | 17   |

| 2.4.4         | Emerging NVMs performance comparison | 18   |

| 2.5 PC        | CM characteristics                   | 19   |

| 2.5.1         | Materials                            | 19   |

| 2.5.2         | Operating principles of PCM          | 21   |

| 2.5.3      | Crystallization of PCM                         | 30 |

|------------|------------------------------------------------|----|

| 2.5.4      | PCM device optimization                        | 37 |

| 2.5.5      | Reliability issues of PCM                      | 40 |

| 2.6 Su     | mmary                                          | 42 |

| CHAPTER    | 3                                              | 44 |

| Literature | Review                                         |    |

| 3.1 Ov     | erview                                         | 44 |

| 3.2 PC     | M modelling review                             | 44 |

| 3.2.1      | SLPCM modelling in literature                  | 46 |

| 3.2.2      | MLPCM modelling in literature                  | 47 |

| 3.3 Dri    | ift phenomenon in amorphous phase              | 49 |

| 3.3.1      | Drift origins                                  | 49 |

| 3.3.2      | Drift mitigation in literature                 | 51 |

| 3.4 Cro    | ossbars                                        | 52 |

| 3.4.1      | Performance issues in crossbars                | 54 |

| 3.4.2      | Connecting wires resistance                    | 54 |

| 3.4.3      | Leakage currents                               | 57 |

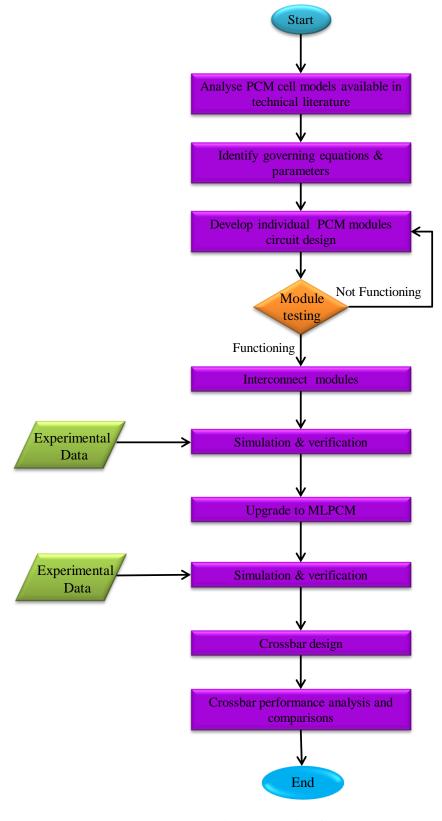

| 3.5 Me     | ethodology                                     | 60 |

| 3.5.1      | PCM cell and memory crossbar design flow chart | 60 |

| 3.5.2      | Design process                                 | 61 |

| 3.5.3      | Testing and verification                       | 61 |

| 3.6 Su     | mmary                                          | 62 |

| CHAPTER    | 4                                              | 65 |

| PCM Elec   | trical Circuit Modelling                       |    |

| 4.1 Ov     | erview                                         | 65 |

| 4.2 PC     | M cell model design                            | 65 |

| 4.2.1      | SLPCM cell model description                   | 68 |

| 4.2.2      | MLPCM cell model upgrade                       | 75 |

| 4.3 Sir    | nulation results                               | 77 |

| 4.3.1      | SLPCM simulation results and discussion        | 77 |

| 4.3.2      | MLPCM simulation results and discussion        | 88 |

| 4.4 Dri    | ift mitigation by time-aware sensing           | 93 |

| 4.4.1      | Proposed time-aware sensing                    | 94 |

| 4.4.2      | Time-aware sensing implementation              | 96 |

| 4.4.3      | Simulation results                             | 97 |

| 4.5    | Summary                                                 | 99  |

|--------|---------------------------------------------------------|-----|

| CHAPT  | ER 5                                                    | 102 |

| PCM I  | Based Memory Crossbars                                  |     |

| 5.1    | Overview                                                | 102 |

| 5.2    | Nanocrossbar connecting wires modelling                 | 102 |

| 5.2.   | 1 Connecting wires resistance R <sub>W</sub> evaluation | 104 |

| 5.2.   | 2 Nanocrossbar equivalent circuit                       | 104 |

| 5.2.   | 3 Simulation results and discussion                     | 106 |

| 5.3    | Wire resistance effects mitigation                      | 112 |

| 5.3.   | 1 Programming Solution                                  | 112 |

| 5.3.   | 2 Structural solution                                   | 113 |

| 5.4    | Leakage effects mitigation                              | 115 |

| 5.4.   | 1 Structural solution                                   | 115 |

| 5.4.   | 2 AC sensing                                            | 122 |

| 5.5    | Summary                                                 | 126 |

| CHAPT  | ER 6                                                    | 129 |

| SLPC   | M and MLPCM in Memory and Logic Applications            |     |

| 6.1    | Overview                                                | 129 |

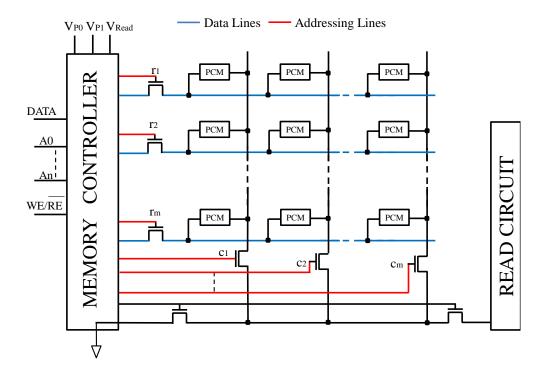

| 6.2    | SLPCM and MLPCM based memory crossbar architecture      | 129 |

| 6.2.   | 1 Memory controller                                     | 130 |

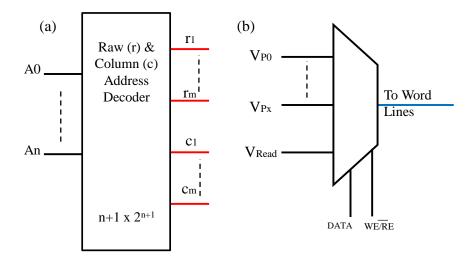

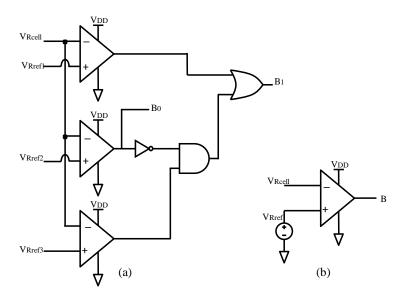

| 6.2.   | 2 Read circuit                                          | 132 |

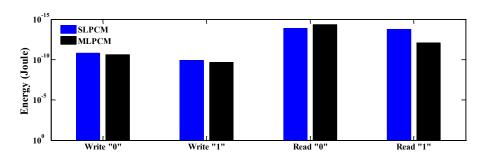

| 6.2.   | 3 Simulation results and discussion                     | 133 |

| 6.3    | MLPCM based LUT                                         | 141 |

| 6.3.   | 1 LUT half adder configuration                          | 142 |

| 6.3.   | 2 Simulation results and discussion                     | 143 |

| 6.4    | PCM, Memristor and SRAM Performance comparison          | 144 |

| 6.4.   | 1 Comparison test structure                             | 145 |

| 6.4.   | 2 Simulation results and discussion                     | 147 |

| 6.5    | Summary                                                 | 151 |

| CHAPT  | ER 7                                                    | 154 |

| Concl  | usion and Future Work                                   |     |

| 7.1    | Conclusion                                              | 154 |

| 7.2    | Future work                                             | 156 |

| REFERE | INCES                                                   | 158 |

| APPENI | DICES                                                   | 170 |

# **List of Figures**

#### **CHAPTER 1**

| Figure 1.1:         | Cross section of PCM cell mushroom structure                        |    |  |

|---------------------|---------------------------------------------------------------------|----|--|

| CHAPTER 2           | 2                                                                   |    |  |

| Figure 2.1:         | Traditionalcomputer memory hierarchy [30]                           | 13 |  |

| Figure 2.2:         | Cross section of memristor cell structure                           | 16 |  |

| Figure 2.3:         | Cross section of PCM cell structure                                 | 17 |  |

| Figure 2.4:         | MRAM cell structure                                                 | 17 |  |

| Figure 2.5:         | Phase diagram of the Ge-Sb-Te ternary alloy system                  | 21 |  |

| Figure 2.6:         | Temperature dependence of the phase change process                  | 22 |  |

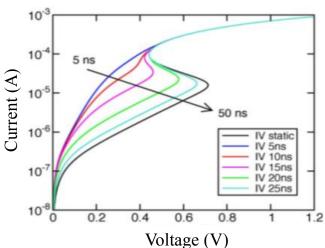

| Figure 2.7:         | I-V characteristics of PCM cell                                     | 22 |  |

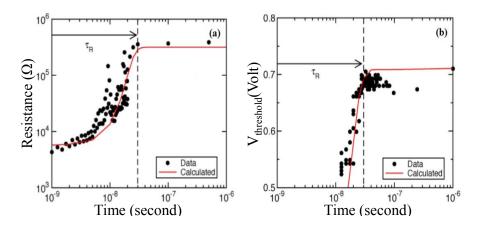

| Figure 2.8:         | Cell (a) resistance and (b) threshold voltage as a function of time |    |  |

|                     | after programming [48]                                              | 24 |  |

| Figure 2.9:         | Calculated I-V curves for PCM devices at increasing time after      |    |  |

|                     | reset, indicating the recovery dynamics[48]                         | 24 |  |

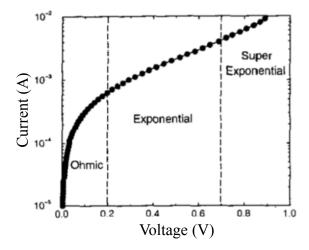

| Figure 2.10:        | Subthreshold I-V characteristic of amorphous phase [52]             | 26 |  |

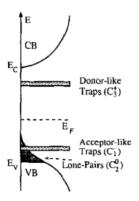

| Figure 2.11:        | Amorphous GST band model [52]                                       | 27 |  |

| Figure 2.12:        | Hot filament formation in amorphous GST                             | 28 |  |

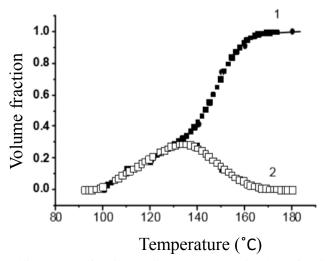

| <b>Figure 2.13:</b> | Crystalline volume fraction (Solid) and the nuclei volume           |    |  |

|                     | fraction as a function of temperature [65]                          | 31 |  |

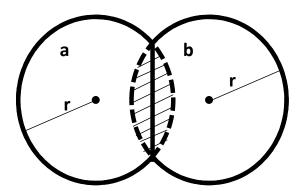

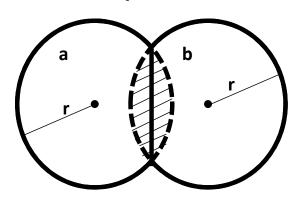

| Figure 2.14:        | Impingement influenced growing crystallite "solid line", and        |    |  |

|                     | impingement free extended volume "dotted line"                      | 33 |  |

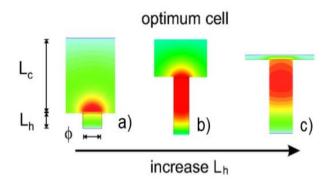

| Figure 2.15:        | Scaling optimization                                                | 39 |  |

| CHAPTER 3           | 3                                                                   |    |  |

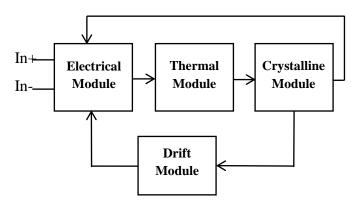

| Figure 3.1:         | PCM cell model block diagram.                                       | 45 |  |

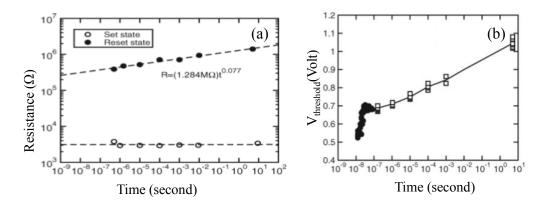

| Figure 3.2:         | Drift in amorphous phase (a) resistance, and (b) threshold          |    |  |

|                     | voltage (V <sub>threshold</sub> ) [49]                              | 49 |  |

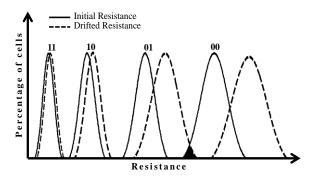

| Figure 3.3:         | Initial programmed and drifted resistance distribution at different |    |  |

|                     | PCM resistance levels.                                              | 51 |  |

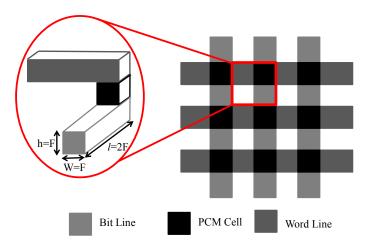

| Figure 3.4:         | Passive PCM based nanocrossbar structure, "inset" lateral view      |    |  |

|                     | of PCM cell in nanocrossbar.                                        | 53 |  |

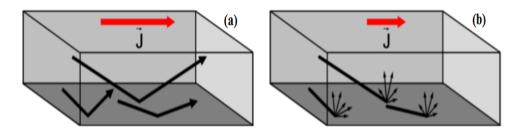

| Figure 3.5:                                                  | (a) Specular reflection of electrons at a conductor surfaces (b)                              |           |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|--|

| Diffuse reflection of electrons at a conductor surface [115] |                                                                                               |           |  |

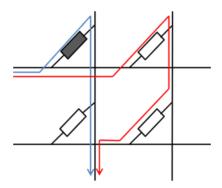

| Figure 3.6:                                                  | <b>6:</b> Leakage currents in standard crossbar architecture                                  |           |  |

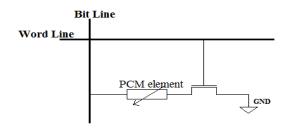

| Figure 3.7:                                                  | PCM element with access transistor 5                                                          |           |  |

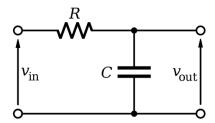

| Figure 3.8:                                                  | Low pass filter circuit 5                                                                     |           |  |

| Figure 3.9:                                                  | PCM cell circuit model design flow chart                                                      | 60        |  |

| CHAPTER 4                                                    | ı                                                                                             |           |  |

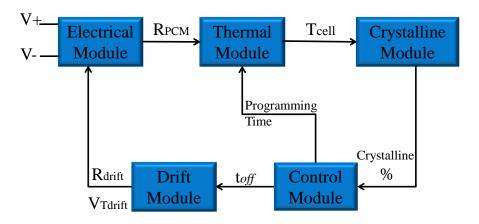

| Figure 4.1:                                                  | PCM cell model basic modules.                                                                 | 65        |  |

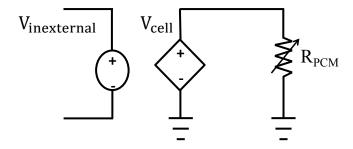

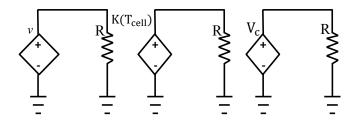

| Figure 4.2:                                                  | PCM cell resistance module equivalent circuit                                                 | 68        |  |

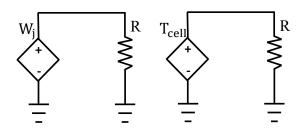

| Figure 4.3:                                                  | Temperature calculation module equivalent circuit                                             | <b>70</b> |  |

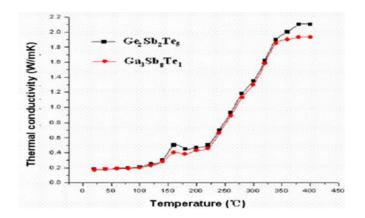

| Figure 4.4:                                                  | Thermal conductivity as a function of temperature [122]                                       | 71        |  |

| Figure 4.5:                                                  | Crystalline fraction module equivalent circuit                                                | 71        |  |

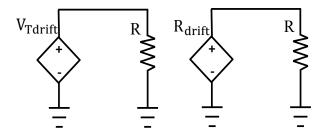

| Figure 4.6:                                                  | Drift module equivalent circuit                                                               | 72        |  |

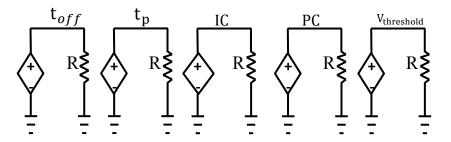

| Figure 4.7:                                                  | Control module equivalent circuit                                                             | 73        |  |

| Figure 4.8:                                                  | Average drift exponent as a function of the programmed                                        |           |  |

|                                                              | resistance level [100]                                                                        | 76        |  |

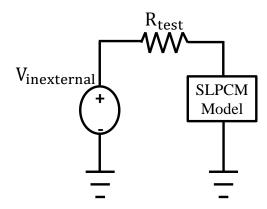

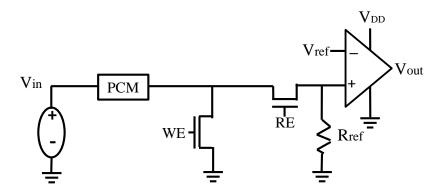

| Figure 4.9:                                                  | Test set for SLPCM cell model simulation                                                      | 77        |  |

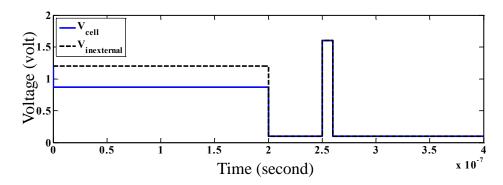

| <b>Figure 4.10:</b>                                          | Voltage across the cell $V_{\text{cell}}$ as a function of external input pulse               |           |  |

|                                                              | sequence V <sub>inexternal</sub>                                                              | <b>78</b> |  |

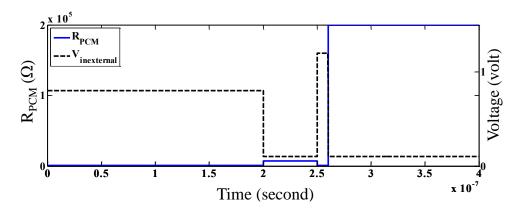

| Figure 4.11:                                                 | $R_{\text{PCM}}$ as a function of external input pulse sequence $V_{\text{inexternal}}$       | <b>79</b> |  |

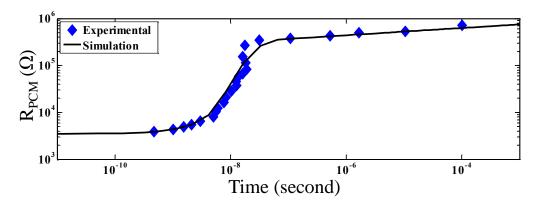

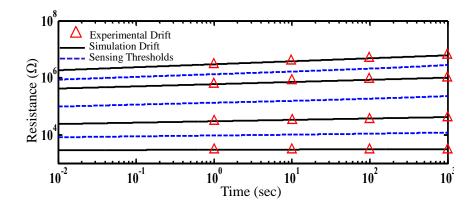

| <b>Figure 4.12:</b>                                          | Simulated and experimental [50] resistance as a function of time                              |           |  |

|                                                              | after programming.                                                                            | <b>79</b> |  |

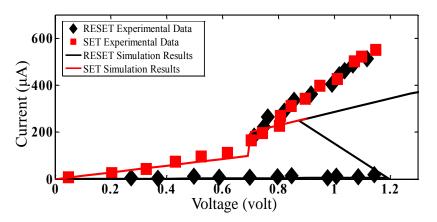

| <b>Figure 4.13:</b>                                          | Simulated and experimentally obtained [4] PCM cell I-V                                        |           |  |

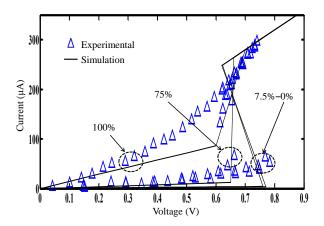

|                                                              | characteristics                                                                               | 80        |  |

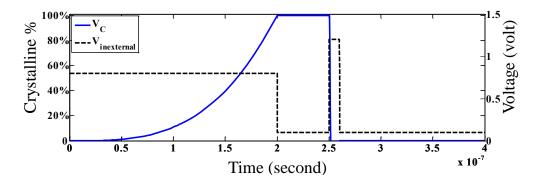

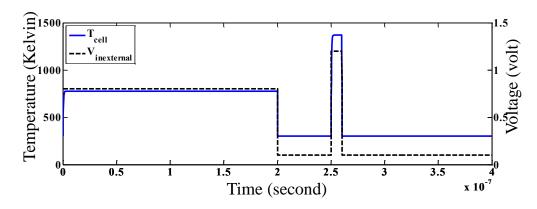

| <b>Figure 4.14:</b>                                          | $V_{\text{C}}$ as a function of external input pulse sequence $V_{\text{inexternal}}$         | 81        |  |

| <b>Figure 4.15:</b>                                          | $T_{\text{cell}}$ as a function of external input pulse sequence $V_{\text{inexternal}}$      | 81        |  |

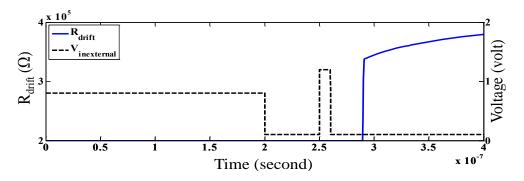

| <b>Figure 4.16:</b>                                          | $R_{\text{drift}}$ as a function of external input pulse sequence $V_{\text{inexternal}}$     | 82        |  |

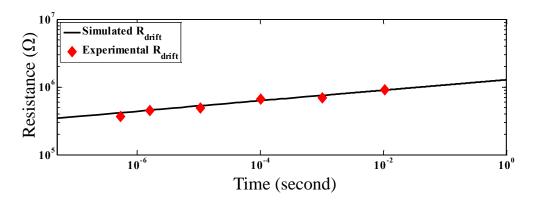

| <b>Figure 4.17:</b>                                          | Simulation and Experimentally [4] obtained $R_{\text{drift}}$ for extended                    |           |  |

|                                                              | drifting time $t_{off}$                                                                       | 82        |  |

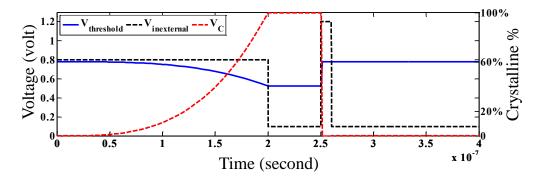

| <b>Figure 4.18:</b>                                          | $V_{\text{threshold}}$ as a function of external input pulse sequence $V_{\text{inexternal}}$ | 83        |  |

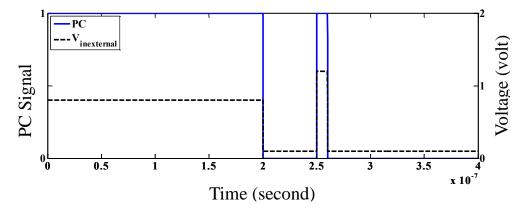

| <b>Figure 4.19:</b>                                          | PC signal corresponding to external input $V_{\text{inexternal}}$                             | 84        |  |

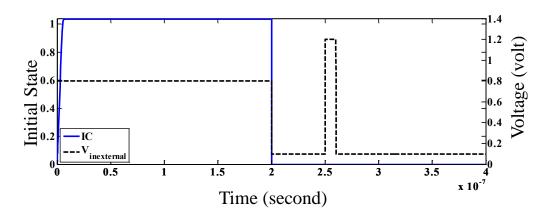

| <b>Figure 4.20:</b>                                          | IC signal corresponding to external input $V_{\text{inexternal}}$                             | 84        |  |

| <b>Figure 4.21:</b>                                          | Simulation result of t <sub>P</sub> evaluation in accordance to applied                       |           |  |

|                                                              | Vinexternal                                                                                   | 85        |  |

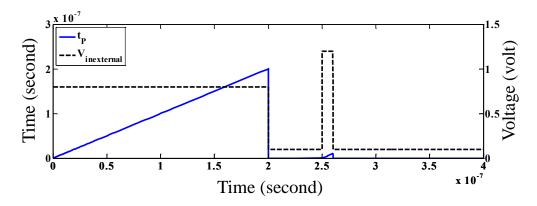

| <b>Figure 4.22:</b> | Simulation result for evaluation of $t_{\it off}$ in accordance to applied                |     |

|---------------------|-------------------------------------------------------------------------------------------|-----|

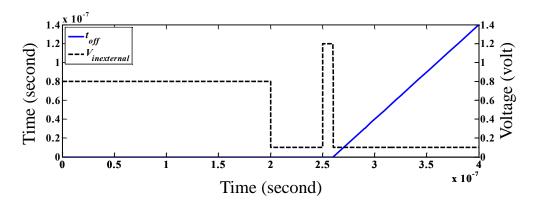

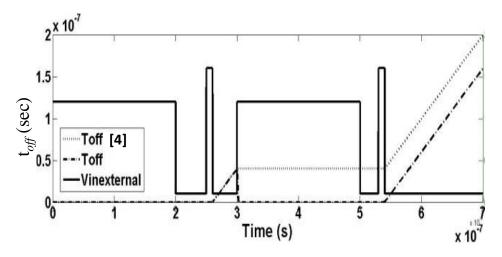

|                     | Vinexternal                                                                               | 86  |

| Figure 4.23:        | Comparison of toff evaluation in suggested model and previous                             |     |

|                     | PCM model                                                                                 | 86  |

| Figure 4.24:        | Standalone cell delay testing setup                                                       | 87  |

| Figure 4.25:        | Reading delay of a standalone cell simulation result                                      | 88  |

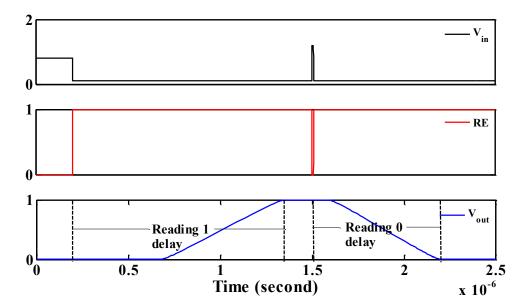

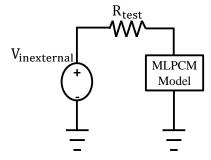

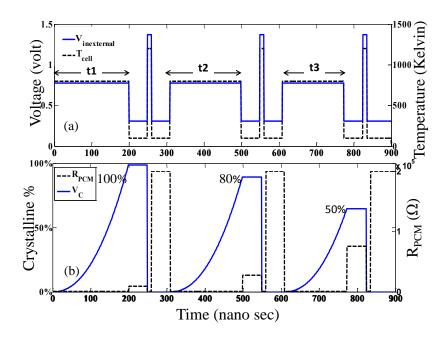

| <b>Figure 4.26:</b> | Test set for MLPCM cell model simulation                                                  | 88  |

| <b>Figure 4.27:</b> | (a) Temperature across the cell $T_{cell}$ , and (b) Crystalline fraction                 |     |

|                     | $V_C$ and cell resistance $R_{PCM}$ in response to external input Vin <sub>external</sub> | 90  |

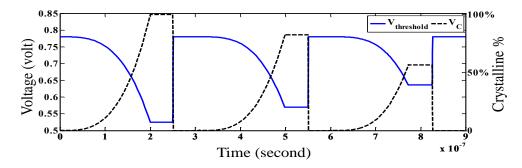

| Figure 4.28:        | Threshold voltage $V_{\text{threshold}}$ of corner and intermediate resistance            |     |

|                     | levels in accordance to $V_{\rm C}$                                                       | 91  |

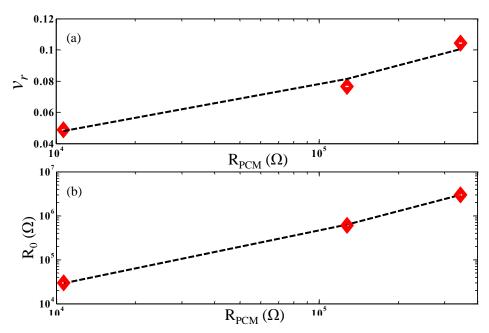

| Figure 4.29:        | (a) Drift exponent $v_r$ , and (b) Normalized resistance $R_0$ at $t_0=1$ sec             |     |

|                     | as a function of programmed $R_{\text{PCM}}$ "dotted line = simulation,                   |     |

|                     | points=experimental data [100]"                                                           | 91  |

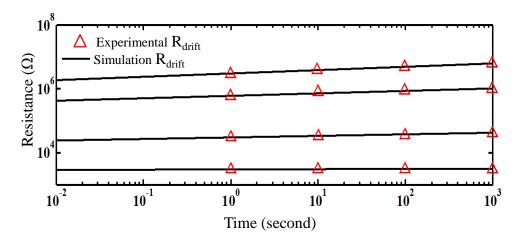

| Figure 4.30:        | Simulation and experimentally extracted [100] $R_{\text{drift}}$ at various               |     |

|                     | initial R <sub>PCM</sub> levels                                                           | 92  |

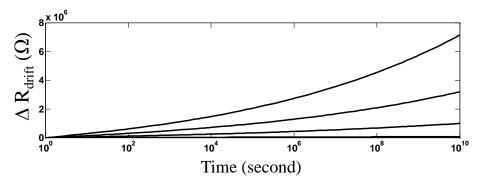

| Figure 4.31:        | Drift deviation from targeted resistance ( $\Delta R_{drift} = R_{drift}(t_{\it off})$ -  |     |

|                     | $R_{drift}(t_0))$                                                                         | 92  |

| Figure 4.32:        | Simulated and experimentally extracted [63] I-V characteristics at                        |     |

|                     | various R <sub>PCM</sub> levels                                                           | 93  |

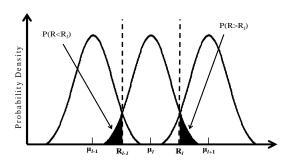

| Figure 4.33:        | Gaussian probability density function of resistance levels                                |     |

|                     | overlapping.                                                                              | 95  |

| Figure 4.34:        | 2-Bit MLPCM sensing circuit design, inset: truth table used to                            |     |

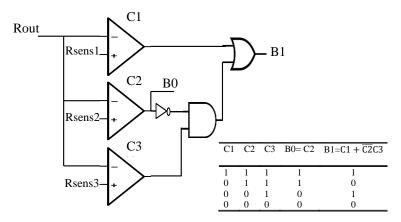

|                     | design the combinational circuit.                                                         | 96  |

| Figure 4.35:        | 2-Bit MLPCM sensing with fixed sensing threshold                                          | 98  |

| Figure 4.36:        | Simulation and experimental [100] resistance drift at various                             |     |

|                     | initial levels, and adaptive sensing thresholds.                                          | 99  |

| CHAPTER :           | 5                                                                                         |     |

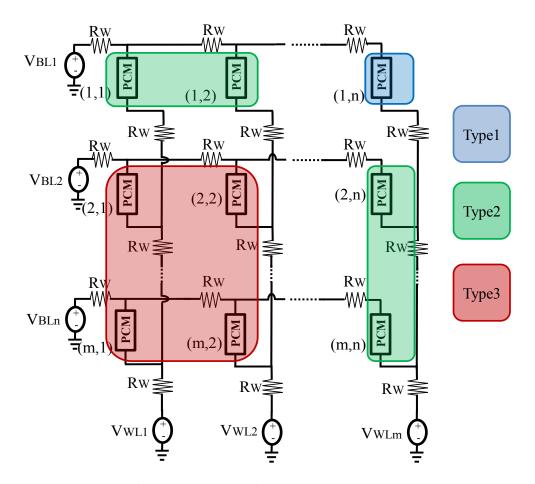

| Figure 5.1:         | PCM based nanocrossbar test structure                                                     | 103 |

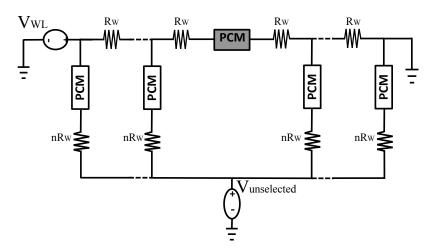

| Figure 5.2:         | Equivalent circuit for passive crossbar structure when targeting                          |     |

|                     | corner mostly affected cell                                                               | 105 |

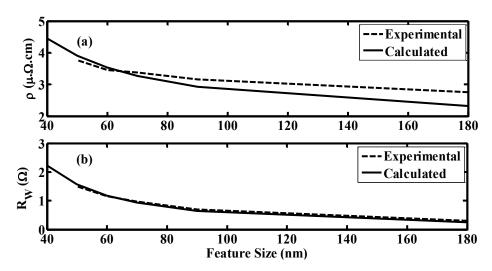

| Figure 5.3:         | Experimentally obtained and calculated connecting wire (a)                                |     |

|                     | electrical resistivity, and (b) resistance as a function of feature                       |     |

|                     | size                                                                                      | 107 |

| Figure 5.4:          | Programmed R <sub>crystalline</sub> deviation percentage from standalone cell |     |  |

|----------------------|-------------------------------------------------------------------------------|-----|--|

|                      | as a function of feature size (F) in 2x2 crossbar                             | 108 |  |

| Figure 5.5:          | Programmed crystalline resistance as a function of crossbar size 1            |     |  |

| Figure 5.6:          | Bitmap of programmed resistance in $k\Omega$ crossbar at the end of           |     |  |

|                      | 200ns programming pulse                                                       | 110 |  |

| Figure 5.7:          | Energy consumed during programming in ideal and realistic                     |     |  |

|                      | nanocrossbars                                                                 | 111 |  |

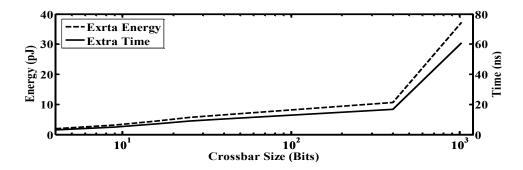

| Figure 5.8:          | Added programming duration and energy required to program to                  |     |  |

|                      | targeted R <sub>crystalline</sub> level                                       | 112 |  |

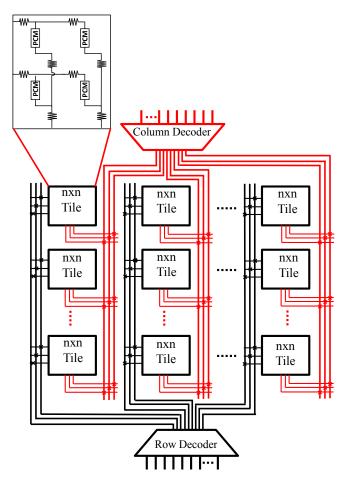

| Figure 5.9:          | Block segmented nanocrossbar structure                                        | 113 |  |

| Figure 5.10:         | Standard crossbar structure                                                   | 116 |  |

| Figure 5.11:         | Adapted new crossbar structure                                                | 118 |  |

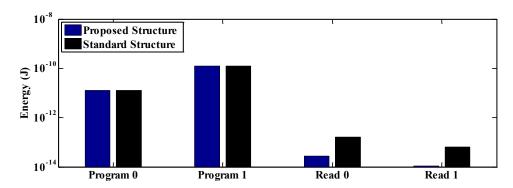

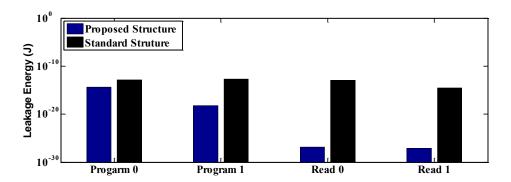

| Figure 5.12:         | Summary of simulation results of dissipated energy during                     |     |  |

|                      | reading and programming                                                       | 120 |  |

| <b>Figure 5.13:</b>  | Summary of simulation results of leaked energy during reading                 |     |  |

|                      | and programming.                                                              | 121 |  |

| Figure 5.14:         | AC sense circuit.                                                             | 123 |  |

| <b>Figure 5.15</b> : | The AC sense circuit reading input and signals at points A, B,                |     |  |

|                      | and C                                                                         | 125 |  |

| CHAPTER 6            | 5                                                                             |     |  |

| Figure 6.1:          | PCM based crossbar memory structure                                           | 130 |  |

| Figure 6.2:          | Memory controller's (a) Address decoder, and (b) Operation                    |     |  |

|                      | selector.                                                                     | 131 |  |

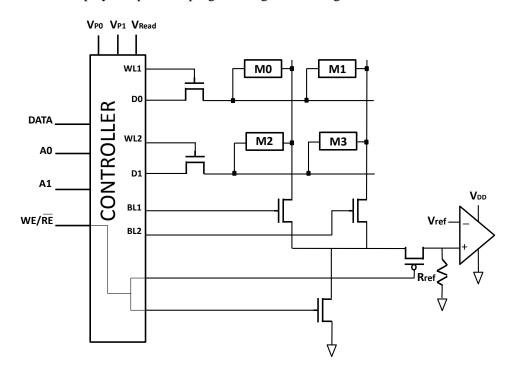

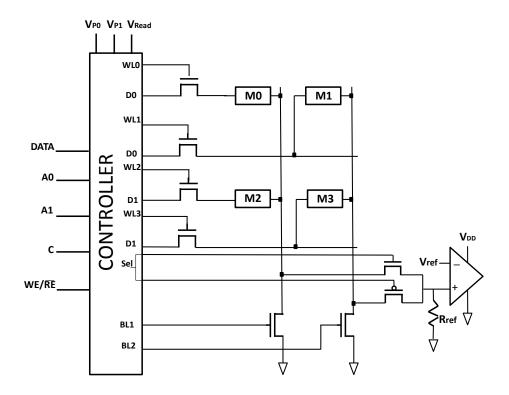

| Figure 6.3:          | Read Circuit Design for (a) MLPCM and (b) SLPCM cells                         | 133 |  |

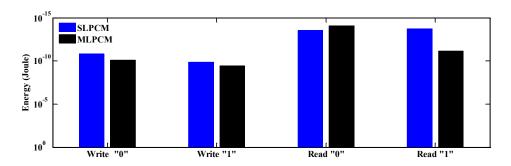

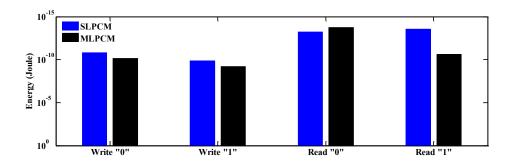

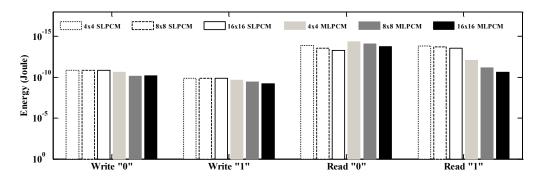

| Figure 6.4:          | 4x4 SLPCM and MLPCM based crossbars energy comparison                         | 134 |  |

| Figure 6.5:          | 8x8 SLPCM and MLPCM based crossbars energy comparison                         | 135 |  |

| Figure 6.6:          | 16x16 SLPCM and MLPCM based crossbars energy comparison                       | 136 |  |

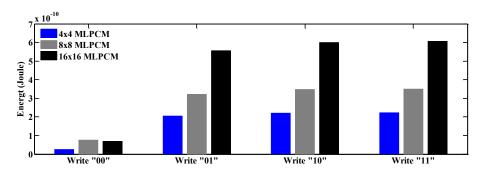

| Figure 6.7:          | MLPCM writing energy comparison                                               | 136 |  |

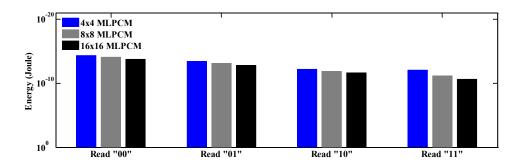

| Figure 6.8:          | MLPCM reading energy comparison                                               | 137 |  |

| Figure 6.9:          | SLPCM and MLPCM energy consumption                                            | 137 |  |

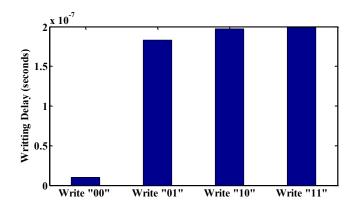

| Figure 6.10:         | Average writing delay for all programmable states                             | 139 |  |

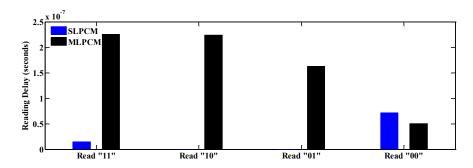

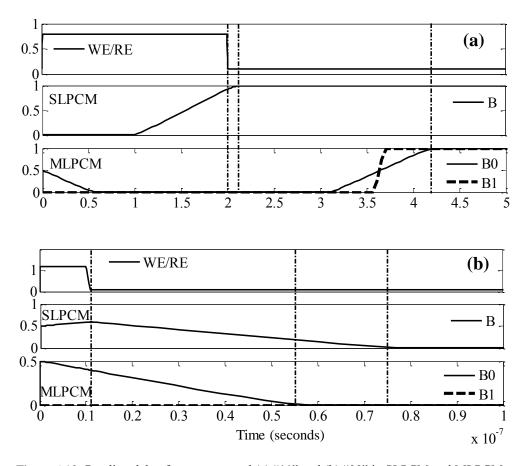

| Figure 6.11:         | Average reading delay for all programmable states                             | 139 |  |

| Figure 6.12:         | Reading delay for programmed (a) "11" and (b) "00" in SLPCM                   |     |  |

|                      | and MLPCM                                                                     | 140 |  |

| Figure 6 13.         | Measuring reading delay of all programmable states in MLPCM                   | 140 |  |

| Figure 6.14: | (a) 2 inputs MLPCM based LUT representation, (b) Half adder       |     |  |

|--------------|-------------------------------------------------------------------|-----|--|

|              | circuit, and (c) its Truth table.                                 | 142 |  |

| Figure 6.15: | Single and multibit reading failure with fixed sensing thresholds | 143 |  |

| Figure 6.16: | Schematic diagram of used crossbar architecture                   | 145 |  |

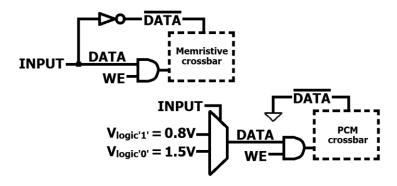

| Figure 6.17: | Write circuit of Memristor and PCM based crossbars.               | 146 |  |

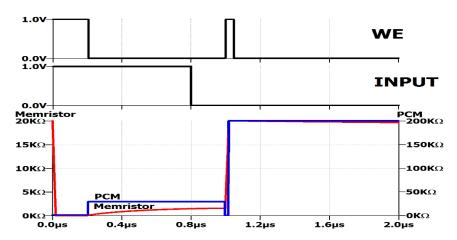

| Figure 6.18: | Programing delay and resistance levels of Memristor and PCM       |     |  |

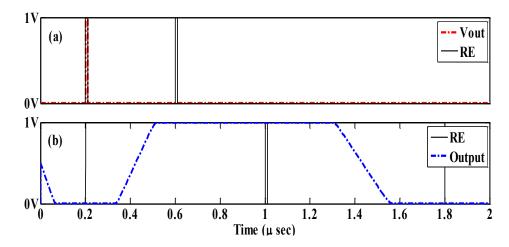

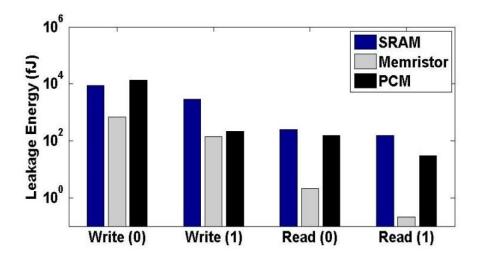

|              | based crossbars                                                   | 148 |  |

| Figure 6.19: | Simulation of Reading delay of (a) Memristive and (b) PCM         |     |  |

|              | based crossbars                                                   | 149 |  |

| Figure 6.20: | Leakage Energy in SRAM, Memristive, and PCM based                 |     |  |

|              | crossbars                                                         | 149 |  |

## **List of Tables**

#### **CHAPTER 2**

| <b>Table 2.1:</b> | Current memory hierarchy performance comparison [30]                   | 14  |

|-------------------|------------------------------------------------------------------------|-----|

| <b>Table 2.2:</b> | Emerging resistive NVM technologies performance comparison [31]        | 18  |

| CHAPTER           | 13                                                                     |     |

| Table 3.1:        | PCM cell model summary                                                 | 46  |

| <b>Table 3.2:</b> | MLPCM models summary                                                   | 48  |

| <b>Table 3.3:</b> | Ideal values for the mean free path of conductors [115]                | 55  |

| CHAPTER           | 4                                                                      |     |

| Table 4.1:        | Signals flow summary                                                   | 66  |

| <b>Table 4.2:</b> | The drift exponents and corresponding resistances and binary           | y   |

|                   | mapping                                                                | 89  |

| <b>Table 4.3:</b> | Mean values of resistance and drift exponent                           | 97  |

| CHAPTER           | 2.5                                                                    |     |

| <b>Table 5.1:</b> | Partial biasing scheme                                                 | 103 |

| <b>Table 5.2:</b> | Summary of parameters of equation (3-3) [116], [125]                   | 104 |

| <b>Table 5.3:</b> | Memory system optimization outline                                     | 114 |

| <b>Table 5.4:</b> | Truth table of standard structure controller unit ( $x = don't care$ ) | 117 |

| <b>Table 5.5:</b> | Truth table of novel structure controller unit ( $x = don't care$ )    | 119 |

| <b>Table 5.6:</b> | Delay and programmed level simulation results summary                  | 122 |

| <b>Table 5.7:</b> | AC Sense circuit performance comparison summary                        | 126 |

| CHAPTER           | 1.6                                                                    |     |

| <b>Table 6.1:</b> | Truth table of SLPCM Memory controller's operation selector unit       | 131 |

| <b>Table 6.2:</b> | Truth table of MLPCM Memory controller's operation selector unit       | 132 |

| <b>Table 6.3:</b> | MLPCM based LUT drifted outputs                                        | 144 |

| <b>Table 6.4:</b> | PCM, Memristor and SRAM based memory crossbars comparison              | n   |

|                   | summary                                                                | 151 |

#### Glossary

VM - Volatile Memory

NVM - Non-Volatile Memory

SCM - Storage Class Memory

CPU - Central Processing Unit

RAM - Random Access Memory

SRAM - Static Random Access Memory

DRAM - Dynamic Random Access Memory

CMOS - Complementary metal oxide semiconductor

ReRAM - Resistive Random Access Memory

PCM - Phase Change Memory

MRAM - Magnetic Random Access Memory

MTJ - Magnetic Tunnelling Junction

GST - Germanium Antimony Telluride (Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>)

PCRAM - Phase-change Random Access Memory

CBRAM - Conductive Bridge Random Access Memory

$V_{threshold}$  - Threshold voltage

OUM - Ovonic Unified Memory

FCC - Face Centered Cubic

JMAK - Johnson-Mehl-Avrami-Kolmogorov

R<sub>PCM</sub> - Cell resistance

$R_{drift} \hspace{1.5cm} - \hspace{0.5cm} Drifted \hspace{0.1cm} cell \hspace{0.1cm} resistance$

V<sub>Tdrift</sub> - Drifted cell threshold voltage

t<sub>off</sub> - Drift duration

VCR - Voltage controlled resistor

VCVS - Voltage Controlled Voltage Source

V<sub>C</sub> - Crystalline fraction

$R_{\text{crystalline}} \, / \, R_{\text{SET}} \qquad \quad \text{-} \quad \text{Crystalline state resistance}$

$R_{\text{amorphous}} \, / R_{\text{RESET}} \, / \, R_{\text{OFF}} \quad \text{-} \quad \text{Amorphous state resistance}$

R<sub>ON</sub> - Dynamic ON\_state resistance

$V_{cell}$  - Voltage across PCM cell

$T_{cell}$  - Temperature across PCM cell

$T_{cryt}$  - GST Crystallization temperature

$T_{melt} \hspace{1.5cm} \text{-} \hspace{0.5cm} \text{GST Melting temperature} \\$

$V_{Tmax}$  - Maximum threshold voltage

$V_{Tmin}$  - Minimum threshold voltage

opamp - operational amplifier

AC - Alternate Current

R<sub>W</sub> - Connecting wire segment electrical resistance

MSB - Most Significant Bit

LSB - Least Significant Bit

# **CHAPTER 1**

**INTRODUCTION**

#### 1.1 Background

The phase change memory (PCM) also known as the Ovonic Unified Memory (OUM) [1] was first proposed by Ovshinsky in the early 1960's; based on Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) chalcogenide alloy. In its early development, GST was implemented on rewritable optical CD/DVD disks. However, as PCM technology substantially advanced, it became possible to integrate GST in today's ICs where manufacturing costs have been considerably reduced [2].

The operation concept of PCM relies on the fact that the phase change material can exist in at least two phases and can undergo a thermally induced phase change. The phase change is typically from highly resistive phase to low resistive phase or vice versa. The high resistive state is a disordered amorphous phase with short range atomic order and low free electron density. The low resistive state is at crystalline phase, with long range atomic order and high free electron density. The resistance of the two phases is read to distinguish two different states equivalent to binary 1 and 0.

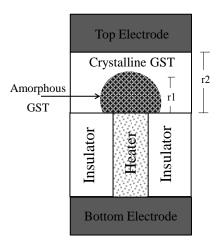

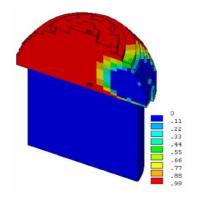

Figure 1.1: Cross section of PCM cell mushroom structure

The basic schematic cross section of PCM cell structure shown in Figure 1.1 is referred to as a mushroom cell. It is constituted of a thin film of chalcogenide material (GST in this work) with thickness of r2 in contact with a metallic heater; the

heater is surrounded by an insulator material. The programmable region referred to as active region in Figure 1.1 is the part that undergoes the phase change process which has the thickness of r1. The overall resistance of the cell is the series resistance of the bottom electrode, the heater, the phase change active region (GST layer) and the top electrode.

The PCM significance resides in its non-volatility among other properties that make it one of the most promising candidates for next generation mainstream Non-volatile Memory (NVM). PCM desirable properties include endurance, retention, and high density compared to other competing NVM technologies [3]–[8]. Furthermore, PCM properties make the technology a strong and desirable candidate in applications other than memories such as processors [9], space applications [10], and as electronic synaptic elements for building brain-like systems [11].

The high density offered by PCM is achieved by utilizing multilevel operation. In multilevel operation; each cell can be programmed to up to 2<sup>N</sup> resistance levels and store N bits; leading to lower cost [12], [13]operation is essential for PCM to fulfil its potential as replacement for Flash memory; and it enhances PCM competitiveness in the market [14]. However, experimental results suggest that resistance drift with time, thermal disturbance and noise [15] are critical reliability issues in multilevel [12], [13].

To assess the undesirable resistance drift effects from design perspective; an accurate predictive electrical circuit model of PCM cell is required. It is also needed to realize a straightforward and timely implementation of PCM in an integrated circuit IC [16]. Such model can help in mitigating the resulting reliability drawbacks in multilevel operation. The model can be used in design, testing and implementation of PCM applications. Several such Spice based simulation models are found in technical literature. These models demonstrate the basic characteristics and operational features of PCM. However, these models failed to simulate key aspects in

PCM operation; such as the impact of time and the stochastic nature of drift at different resistive levels.

Additionally to utilize the high density offered by PCM, it is placed in a crossbar structure. Crossbar memory arrays provide efficient means to facilitate large scale geometry which in turn enables ultra-high densities [17]. Crossbars are constructed of a mesh of intersecting conducting wires; with memory elements placed at each intersection point. Due to increasing demand for denser and faster memory devices; researchers have moved to replace standard SRAM based crossbars with non-volatile memory (NVM) devices based nanocrossbars [18], [19]. However, nanocrossbar structures have multiple performance issues. These issues lead to an increase in consumed energy and can affect the programming performance. Including leakage [17], [20], [21] stray capacitances caused by memory peripheral circuitry, thermal crosstalk [22], and connecting wire resistance [23], [24].

These nanocrossbar performance issues have been addressed in technical literature. A number of methods have been proposed in attempts to eliminate the leakage currents; yet most of the proposed techniques aimed to reduce the reliability issues caused by leakage and not the energy loss due to leakage currents. The leakage mitigation methods included partial biasing [3], crossbar architecture designs [4], and AC sensing [5] which was targeted towards Memristors.

Furthermore, connecting wire resistance at nanoscaled crossbars increases with decreasing dimensions. This resistance increase leads to additional voltage drop across the connecting wires. Which affects the final programmed state of the PCM cell since the power delivered to the cell is reduced. The effects of connecting wire resistances has been addressed in technical literature [23]–[28]. However, all the works were targeted at general NVM crossbars and not the particular case of PCM based nanocrossbars. Furthermore, these works have used less than accurate estimations that did not consider the nanoscale effect on connecting wires resistance.

#### **1.2** Aims

The general purpose of this research is to study, model, simulate and verify a realistic phase change memory (PCM) circuit model with the aid of Spice tools (LTSPICE). The model is expected to realistically simulate the temperature profile across the cell, calculate the crystalline fraction, measure the resistance of the cell and successfully generate the I-V characteristics of a PCM cell. The PCM cell model is designed with the purpose of understanding the PCM characteristics, study its failure modes, develop solutions, and evaluate the feasibility of PCM as a non-volatile random access memory technology for embedded memory applications.

The purpose of designing, testing, and verifying the PCM cell model against experimental data; is to use it as a building block to design and further test PCM performance in nanocrossbar memory arrays. The memory array performance is tested after designing and introducing the proper programming and read circuitry to the PCM crossbar structure. The aim of testing is to identify PCM array operational behaviour, determine its operational failures, their origins, and ways to avoid them in order to utilize PCM technology to its fullest potential and exploit multilevel storage property offered by PCM.

#### 1.3 Objectives

- Design and implement an accurate circuit model for single and multibit storing PCM cell using crystallization theory and heat transfer governing equations. Then verify the circuit model behaviour by comparing against experimental data.

- Accurately evaluate drift phenomenon based on statistical data, and evaluate its effect on reliability. Then develop a drift prediction and mitigation method.

- ❖ Use the designed PCM circuit model to test performance of PCM elements in memory crossbar structure. Including the effects of leakage currents and

- nanoscaled connecting wires resistance on energy dissipation and operation delay in crossbars.

- Develop an embedded memory and logic applications utilizing PCM properties, and the designed circuit model.

- Compare performance of PCM, SRAM, and NVM based crossbars in terms of programming and reading energy consumption, operation delay, and density.

#### 1.4 Contribution of the research

This work develops a PCM cell model that overcomes all accuracy issues demonstrated by previous PCM models in technical literature. The designed model evaluates drift phenomenon and accurately accounts for variability in drift exponents thus evaluating drift effects at multilevel operation mode. Based on that model a sensing scheme that overcomes the reliability issue arising from drift is developed. That scheme minimizes the area over head and programming complexity encountered in previously proposed drift solutions.

Furthermore, the designed PCM cell circuit model is used as a building block to evaluate PCM based memory crossbars performance, an area that is not thoroughly explored in technical literature. Additionally, there is no research in literature that has conducted detailed comparison between PCM and other memory technologies using the same crossbar architecture. In this work, SRAM, memristor and PCM based crossbars performance is compared in simulation environment using the exact same crossbar architecture; thus providing a fair comparison medium in which the performance characteristics of each memory technology are accurately calculated and advantages highlighted to be further utilized in more proper applications. Finally, this work studied the feasibility of using PCM in memory and logic applications and successfully implemented MLPCM based LUTs and embedded memory structures.

#### 1.5 Thesis outline

The layout of the rest of this thesis is as follows; Chapter 2 starts with an overview of current memory architecture and performance metrics used in evaluating memory performance. The most prominent emerging NVM technologies are briefly introduced. A detailed review of physical properties, operation concepts and reliability issues of PCM is presented. Chapter 3 is the chapter of literature review that highlights PCM behaviour governing equations, available PCM models, issues with PCM based crossbars, and how they are addressed in technical literature. The chapter also describes the methodology adopted in this work.

The designed PCM cell model is presented in Chapter 4 of this thesis. It describes in detail the circuit designs of the modules constituting the designed cell model, and the physical equations governing the model behaviour. It elaborates on the simulation patterns that are tested and compares the obtained results of simulations against experimental data. The work moves on to upgrade the single bit PCM cell design into multilevel PCM cell design. Moreover, the drift behaviour of amorphous and intermediate resistance levels of GST is simulated using experimental statistical data as reference. And a drift mitigation sensing method is presented.

Chapter 5 studies the performance issues facing memory crossbars in general and PCM based nanocrossbars in particular. Namely; connecting wire resistance energy consumption and energy dissipation due to leakage currents. Furthermore, the work elaborates on proposing solution to these performance drawbacks. The proposed solutions are designed and tested in simulation environment.

The use of PCM based nanocrossbar in memory and logic applications is presented in Chapter 6. Where both single and multibit storage using PCM based crossbars was explored. And a performance comparison in terms of delay, energy consumption and leakage energy in simulation environment is studied in detail. Additionally, the use of PCM memory cells in LUTs is explored. Then the

performance of PCM based memories is compared to currently used SRAMs and Memristors. Finally, this work is concluded in Chapter 7; with concluding remarks and proposed future work.

# **CHAPTER 2**

**PRELIMINARIES**

#### 2.1 Overview

In this chapter basic information that describe the current status of computer memory hierarchy are provided. The chapter starts in section 2.2 with main performance characteristics considered when evaluating a memory technology and structure. The current computer memory hierarchy and used memory technologies are explained in section 2.3. The most prominent emerging non-volatile memory technologies and their operation concepts are stated in section 2.4. Then a detailed description of PCM characteristics is provided in section 2.5.

#### 2.2 Memory Performance Characteristics

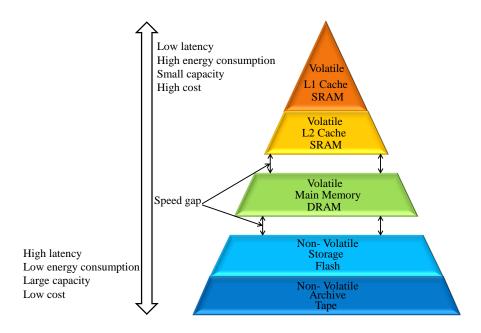

The memory is an essential and integral part of modern computer systems architecture, which is used to store both data and software programs, for it to be later used by the processor [29]. There are different categories and classifications of memory types; that are often used within a single system. The main electronic memories categories are Volatile Memories (VM) and Non-Volatile Memories (NVM). As the name indicates; volatile memories lose stored data when the system is powered off, in contrast to their non-volatile counterparts which retain stored data for extended periods of time after the system is powered [29], [30]. However the volatility is not the only defining characteristic of a memory type, as the memory hierarchy in the computer system shown in Figure 2.1 is constructed of several layers of memories. Each memory layer has specific properties i.e. performance indices in accordance to the requirements of that layer.

The performance metrics used to describe a memory type are listed and defined as following:

a) Retention Time: The period during which the memory retains data stored in it after the system is powered off.

- b) Read/Write energy: The energy required to read/write a single bit of data, it could be defined as the memory consumed per chip area.

- c) <u>Idle power:</u> The energy consumed by the memory when it's not used i.e. idle.

- d) Endurance: The number of program cycles that can be applied to the memory before the storage media becomes unreliable.

- e) Access time: The time interval between the read/write request and the availability of data.

- f) Read/Write latency: Time delay between the application of address and the availability of stable and accurate data on the data lines/memory cells.

- g) <u>Density (Capacity):</u> The volume of information (in bits) that the memory can store

- h) <u>Cell size:</u> The physical volume occupied by a single memory cell.

- Temperature range: The range of temperature at which the memory can operate reliably.

- j) <u>Multilevel operation:</u> The ability of a single memory cell to store more than a single bit of data.

It should be noted that a memory type does not possess all the desired performance characteristic; therefore trade-offs are made to support the main requirement of a specific system or memory type, e.g. some memories have longer retention times and higher capacities yet they require longer access times, while other memories trade the capacity for shorter access times [29]. Making the later suitable to be built in the processor; as it can keep up with its high operating speed; while the former is more suitable for external data storage system. Throughout this work read/write latency, read/write energy, and density will be the used metrics for performance comparison.

#### 2.3 Traditional memory hierarchy

The depiction of modern memory hierarchy in Figure 2.1 shows how memory performance metrics i.e. latency, energy consumption and capacity are traded off at each level depending on the system requirements. For example, short access time and latency are needed in level 1 cache memory; since it is integrated in the Central Processing Unit (CPU) chip and must work at processor's speed. However, slightly longer latency and access time, and higher capacity are the performance metrics exhibited by caches at level 2.

The main memory is used to store programmes and data when they are active and used by the processor. The main memory copies its contents from the non-volatile archive memory residing at the bottom of the memory hierarchy, and loses the contents once the system's power goes off. As the main memory acts as a link between the two ends of the memory hierarchy it possess intermediate characteristics as well in terms of latency, density and energy consumption. The latency increases as we go towards the base of the memory hierarchy pyramid as seen in Figure 2.1, and the capacity increases and energy consumption decreases at the cost of increased latency towards the base where the archival storage containing software programmes and stored data [30]. In the following the characteristics of Static Random Access Memory (SRAM) used in cache memory, Dynamic Random Access Memory (DRAM) used in Main memory, and the Flash memory used as storage memory are discussed.

Figure 2.1: Traditional computer memory hierarchy [30]

#### 2.3.1 **SRAM**

The SRAM is a high performance semiconductor memory constructed of six transistors. It is used for storing instructions in registers and caches of processors; due to its low latency as indicated in Figure 2.1. Thus SRAM low latency stated in Table 2.1, makes it suitable to provide data immediately to the CPU at its operating speed [30]. Yet despite the high speed, it requires larger area per cell due to the six CMOS transistors constructing it.

#### 2.3.2 **DRAM**

DRAM is a fast, power efficient semiconductor random access memory, with high endurance as indicated to in Table 2.1. DRAM is constructed of a single access transistor and a capacitor, and is used as main memory in computer systems. But since the main memory is separated from the CPU, an interface is required causing the DRAM energy consumption and delay to increase in comparison to SRAM [30], as seen in Table 2.1.

#### 2.3.3 Flash memory

Flash memory is a non-volatile, highly scalable, and inexpensive semiconductor memory technology that is used at storage level. Flash memories have longer latency

and less endurance compared to SRAM and DRAM as noted from Table 2.1, but its high density makes it suitable to be used as external storage [30], [31]. The core concept of the traditional memory hierarchy shown in Figure 2.1 has evolved from the fact that high performance directly correlates with extra cost [30]. Therefore, the expensive high performance memories use is confined to places where it is critical for overall system performance. Moreover, critical computing applications are becoming more data-centric than compute-centric [32], which means they require larger memory space than ever. This leads to two key issues with the current memory hierarchy; i.e. the speed gap between memory hierarchy levels, and the increased power consumption due to increased memory density [31].

Table 2.1: Current memory hierarchy performance comparison [30]

| Property          | SRAM            | DRAM                    | Flash                  |

|-------------------|-----------------|-------------------------|------------------------|

| Read energy       | -               | 0.8 J/GB                | 1.5 J/GB               |

|                   | $0.32 \mu W$    |                         |                        |

| Write energy      | [33]            | 1.2 J/GB                | 17.5 J/GB              |

|                   |                 |                         | 1-10                   |

| Idle power        | Cell leakage    | Refresh power~100 mW/GB | mW/GB                  |

| Endurance         | $10^{16}[32]$   | $10^{15}$               | $10^4 - 10^5$          |

| Retention [34]    | -               | 64 ms                   | >10 years              |

| Read latency      | 1.23ns [35]     | 20-50 ns                | ~25 µs                 |

|                   |                 | capacitor charging time |                        |

| Write latency     | 0.85ns [35]     | 20-50 ns                | ~500 µs                |

| Density           | -               | 1x                      | 4 x                    |

|                   |                 | 10uA capacitor charging |                        |

| Power consumption | 10.37 mW        | current                 | -                      |

| Cell size         | $>100F^{2}[36]$ | $6-8 F^{2} [36]$        | $10 \mathrm{F}^2 [34]$ |

| Temperature       |                 |                         |                        |

| range[34]         | -               | -40 − 85 °C             | -40 – 150 °C           |

| Multilevel        | N/A             | N/A                     | Available              |

From the issues faced by the traditional memory hierarchy, arose the need for a high-performance, high-density, and low-cost NVM technology; in order to improve overall system performance, and meet the demands of future storage server systems and consumer electronics market in terms of density and power. A class of memory that combines high speed and endurance of solid state memory such as SRAM, and archival memory low cost and high density, this class is called Storage Class Memory (SCM). SCM would bridge the speed gap in the memory hierarchy and solve the power consumption limitations [32]. Furthermore, having SCM will eliminate the need to store programs in non-volatile NAND then transferring them to volatile DRAM upon execution; by having the programs stored in non-volatile high speed SCM, hence providing high performance, low cost single chip solution [30].

#### 2.4 Emerging resistive NVM

Emerging resistive switching memory technologies that can overcome the issues of traditional memory hierarchy, replace flash memories, and be the technology for storage class memory, are widely studied in technical literature [19], [31], [32], [34], [37]–[39]. These emerging NVM technologies possess desired properties as they offer low power consumptions, high operating speeds, long data retention, and high scalability leading to high density as indicated in Table 2.2.

The operating concept of resistive switching memories relies on the fact that the equivalent resistance of the memory cell can be controlled by applying external potential, leading to either chemically, magnetically, or thermally induced change of the cell resistance. The memory cell therefore can be in at least two resistive states. The resistive state of the memory cell can then be used to store binary data, where the relatively high resistive state corresponds to binary zero, and the relatively low resistive state represents binary one. Resistive switching memories include but are not limited to; Magneto-resistive RAM (MRAM), Phase change RAM (PCRAM),

Conductive Bridge RAM (CBRAM), Bi-Stable organic memory, Ferroelectric RAM (FeRAM), and Memristors. In the following the most prominent of these resistive switching memory technologies are described.

#### 2.4.1 Resistive RAM (ReRAM) "Memristor"

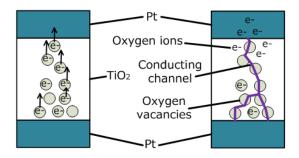

Memristor is a two terminal non-volatile resistive memory structure that changes its instantaneous resistance known as memristance. The memristance changes according to the amount and direction of applied programming pulse. Where applied current controls oxygen ions and the formation of oxygen vacancies that lines up to create a conducting channel thus lowering the resistance of the memristor cell. Reversing the direction of applied current causes the oxygen vacancies conducting channel to collapse leading to increased resistance [40] as depicted in Figure 2.2.

Figure 2.2: Cross section of memristor cell structure (high resistance "left", and low resistance "right")

#### 2.4.2 Phase change memory (PCM)

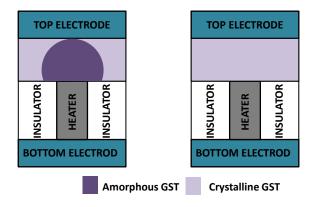

PCM also referred to as PCRAM is a two terminal memory structure that is a promising SCM candidate. The operation concept of PCM relies on the material's thermally induced phase change property; in which the material changes its atomic structure from highly disordered, highly resistive amorphous structure to ordered low resistive crystalline state. Typical phase change materials are chalcogenides, such as  $Ge_2Sb_2Te_5$  (GST) [30]. The phase change material layer is sandwiched between two electrodes as shown in Figure 2.3; and when current passes through the heater it

generates heat due to the Joule effect, this heat transfers to the phase change layer inducing the structure change [41].

Figure 2.3: Cross section of PCM cell structure (high resistance "left", and low resistance "right")

#### 2.4.3 Magnetic Tunnel Junction (MTJ)

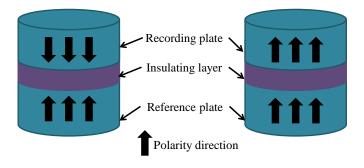

A traditional Ferro Electric Random Access Memory (FeRAM) cell is a two terminal structure that consists of two ferromagnetic plates separated by a thin insulating layer as illustrated in Figure 2.4. This structure is known as a Magnetic Tunnel Junction (MTJ). The lower plate is set to a fixed polarity, while the polarity of the upper plate is free and can be switched by controlling the applied programming pulse. The electrical resistance of the memory cell changes depending on whether or not the polarity is aligned between the two plates [19]. If the magnetic polarization of the two layers is aligned, the resistance through the MTJ is low relative to the resistance when they are misaligned [30].

Figure 2.4: MRAM cell structure (high resistance "left", and low resistance "right")

## 2.4.4 Emerging NVMs performance comparison

The above discussed emerging resistive NVM share the storage mechanism concept i.e. resistive storage concept, which leads to non-volatility, in contrast to charge storage in volatile transistor based Random Access Memories (RAM). However resistive NVM technologies demonstrate different performance characteristics which are outlined in Table 2.2.

Table 2.2: Emerging resistive NVM technologies performance comparison [31]

| Performance index | PCM                                | FeRAM                 | ReRAM               |

|-------------------|------------------------------------|-----------------------|---------------------|

| Cell size         | 4- 19 F <sup>2</sup>               | 15- 35 F <sup>2</sup> | 6-10 F <sup>2</sup> |

| Operation voltage | 1.5 – 1.8 V                        | 1.8V                  | 3.3 – 6.5 V         |

| Write current     | 10 <sup>-4</sup> A                 | 10 <sup>-6</sup> A    | 10 <sup>-4</sup> A  |

| Write latency     | 100ns                              | <10ns                 | 50ns                |

| Read latency      | <5ns                               | <5ns                  | <5ns                |

| Retention         | >10 years                          | >10 years             | >10 years           |

| Endurance         | 10 <sup>9</sup> - 10 <sup>12</sup> | $10^{13}$             | $10^{6}$            |

As noted from Table 2.2, PCRAM shows better performance in comparison to ReRAM in all performance metrics excluding write latency. It is due to the fact that in PCRAM, the resistive change depends on thermally induced structural change in the material used. This requires longer delay compared to magnetic and chemical changes in FeRAM and ReRAM respectively. Furthermore, looking at PCM performance characteristics from Table 2.2 and comparing it to traditional memory structures i.e. SRAM, DRAM, and Flash memory from Table 2.1, it is noted that PCM shows superior performance characteristics. PCM performance surpasses Flash memory in all performance metrics, and only lags in comparison to DRAM and

SRAM in terms of writing latency; an issue that is addressed in technical research. Moreover, when comparing the PCM specifications to the targeted specification of storage class memory listed in [32], it is noted that it fulfils the requirements making it a strong candidate to fill in as the technology for storage class memory.

## 2.5 PCM characteristics

#### 2.5.1 Materials

PCM technology relies on the phase change process displayed by chalcogenide materials; which are chemical compounds consisting of at least one chalcogen element, i.e. sulphur (S), selenium (Se), or tellurium (Te), in combination with other elements. In this research the focus is on germanium antimony telluride (Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>) referred to as GST.

Most phase-change materials are chalcogenides, containing at least one element from group VI of the periodic table. This due to the fact that group VI elements form pre-dominantly twofold-coordinated covalent chemical bonds that can produce linear, tangled, polymer like clusters in the melt. These clusters lead to an increase the viscosity of the liquid, inhibiting the atomic motion necessary for crystallization [42]; thus preventing the amorphous phase from spontaneously crystalizing, a necessary feature in using PCM as resistive storage system.

GST is the most commonly used and most widely studied phase change material, due to its more established previous application in optical storage systems. Yet it should be noted that the properties required in materials used in optical storage differ from the properties required in resistive storage systems. Possessing desirable properties for optical storage does not necessary make the material suitable for resistive storage. For resistive storage applications, phase change materials are desired to have fast crystallization speeds to minimize programming delays, crystallization temperatures that are well above the operating medium temperature to

insure reliability, and relatively low melting temperature to minimize programming power consumption. A large R<sub>amorphous</sub>/R<sub>crystalline</sub> ratio is also desired to facilitate a reliable read process and permit multilevel operation in order to increase density. High cyclability, endurance, and CMOS compatibility are as well much desired properties in resistive storage phase change materials. With all these requirements in mind phase change materials are studied and their properties are evaluated to decide the most suitable materials for resistive non-volatile memory application [42].

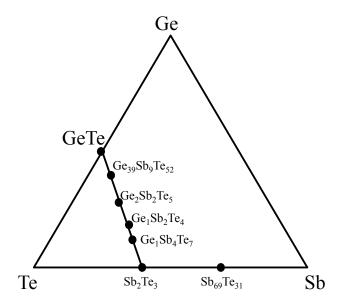

Experimental studies [43] showed that within the class of GeSbTe ternary alloys; compound materials along the pseudo-binary GeTe-Sb<sub>2</sub>Te<sub>3</sub> tie-line (e.g. Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, Ge<sub>1</sub>Sb<sub>2</sub>Te<sub>4</sub>, Ge<sub>1</sub>Sb<sub>4</sub>Te<sub>7</sub>), as shown in Figure 2.5, have fast crystallization properties. While GeSbTe materials demonstrated nucleation dominated crystallization process; silicon antimony telluride (SiSbTe) showed growth dominated crystallization making it faster in terms of programming delay. In addition SiSbTe demonstrates better data retention in comparison with GeSbTe. With archive lifetime of SiSbTe being about twice as long as that of GeSbTe [44].

Many other compounds have been developed, tested, analysed and further improved by doping, thus widening the array of materials that can be used as phase change materials in resistive memories. The developed materials include Ge-Te, AgSbSe2, Sb-Se, Ag-In-Sb-Te, and other Sb-Te variants. Along with a wide variety of dopants including elements of the 13th and 14th columns of the periodic table e.g. carbon (C), tin (Sn), indium (In), aluminium (Al), silicon (Si), germanium (Ge), nitrogen (N), and oxygen (O); because they enhance the operation characteristics, i.e. melting temperature, crystallizing temperature [42].

Figure 2.5: Phase diagram of the Ge-Sb-Te ternary alloy system

Adding dopants was experimentally studied [43], [45], [46], to evaluate the effect of adding nitrogen (N) and oxygen (O) on phase change properties. It was found that when adding oxygen to GeSbTe thin films, the oxygen acts as nucleation centre in crystallization process, minimizing the nucleation time in comparison to undoped GeSbTe films [45]. Moreover, it was noted that when doping Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> with nitrogen; the material endurance is improved as a result of increased activation energy [46]. Furthermore, different capping materials were tested [47], including silicon oxide (SiO<sub>2)</sub>, aluminium oxide (Al<sub>2</sub>O<sub>3</sub>), germanium oxide (GeO<sub>x</sub>), antimony oxide (SbO<sub>x</sub>), titanium nitride (TiN) and Al. It was concluded that the use of SiO<sub>2</sub> and GeO<sub>x</sub> as capping materials accelerates the recrystallization rate of GeSbTe substantially and increases crystallization temperature.

# 2.5.2 Operating principles of PCM

Data storage in PCM depends on the thermally induced phase change property in Chalcogenides (GST in this work); the material can exist in at least two phases; highly resistive amorphous and low resistive crystalline, where the latter phase represent (one) and the former represent (zero) in binary system.

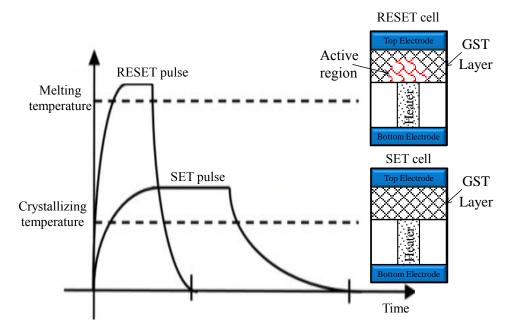

Figure 2.6: Temperature dependence of the phase change process

The material phase change from crystalline to amorphous is referred to as RESET process. During RESET process the PCM cell is heated by a current pulse above GST melting temperature (600°C) utilizing the Joule effect. The material is then rapidly quenched before it rearranges back to crystalline state, hence keeping it at a distorted amorphous phase. Similarly, the phase change from amorphous to crystalline is referred to as SET process. In the SET process the PCM cell is heated slightly above GST crystallization temperature (≈200°C) and well below its melting temperature as seen in Figure 2.6, for duration sufficient for the phase change material in active region to rearrange its atoms back to crystalline ordered state.

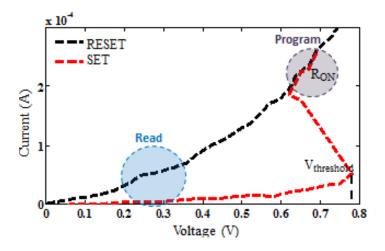

Figure 2.7: I-V characteristics of PCM cell

I-V characteristics shown in Figure 2.7 display the steady state response of a PCM cell. The steady state response gives an insight into the atomic transitions the PCM cell goes into when it is being programmed, i.e. SET from initial amorphous state into crystalline state, and RESET from initial crystalline state into amorphous state. After a RESET process the cell goes into a recovery stage before it reaches the final high resistance state. In the following the programming of PCM cells i.e. RESET and SET processes and the accompanying recovery transient are explained, along with the subthreshold regime and the characteristic snap back behaviour of PCM cell I-V characteristics as seen in Figure 2.7.

## 2.5.2.1 RESET process

When the material is initially crystalline as seen in crystalline curve in Figure 2.7, its resistance is relatively small and the current passing through the cell leads the temperature increase due to Joule effect. To programme the cell into the amorphous state i.e. to RESET the cell, a high steep programming current pulse is applied; causing an excessive presence of charge carriers. This creates a highly conductive dynamic ON state with even lower resistance (R<sub>ON</sub>) as shown in Figure 2.7. This allows sufficient current to heat the cell above melting temperature and program the cell.

## 2.5.2.2 Recovery behaviour

It is noted from experimental results in technical literature [48], [49] that when a PCM cell is RESET i.e. programmed into amorphous highly resistive state, it does not immediately reach the targeted resistance level after programming. Rather a transient resistance that is lower than the targeted value appears directly after programming. The cell resistance then exponentially increases to reach the targeted resistance as seen in Figure 2.8. This transient behaviour is referred to as the recovery behaviour, and it was experimentally calculated in [48] by measuring the I-V characteristics at several points in time after programming as depicted in Figure 2.9. The corresponding cell resistance and threshold voltage are extracted from the

captured recovery behaviour. The experimentally observed recovery time for the cell's resistance to increase from  $R_{ON}$  (typically few  $K\Omega$ ) up to the targeted amorphous resistance was found to be about 30ns [48]–[50].

Figure 2.8: Cell (a) resistance and (b) threshold voltage as a function of time after programming [48]

Figure 2.9: Calculated I–V curves for PCM devices at increasing time after reset, indicating the recovery dynamics[48]

The recovery behaviour is explained by the substantial concentration of excited carriers that are still at high energy states and elevated temperature within the cell immediately after programming. Thus resulting in lowered resistance, which gradually increase during the electronic relaxation time of carriers relaxing to low energy states, and the thermalization time needed for the excess thermal energy to diffuse [48], [50].

The impact of the recovery effect on device operation is significant in terms of reading speed [48], [51], as equilibrium must take place before reading can be carried out; in order to read accurate data. And if reading bias is applied before the equilibrium is achieved i.e. when the threshold voltage is substantially smaller; unintended programming may take place. Furthermore, read failures may occur due to lowered cell resistance, therefore the recovery time should be considered as the minimum waiting time after programming, to perform reading process.

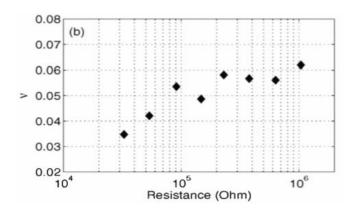

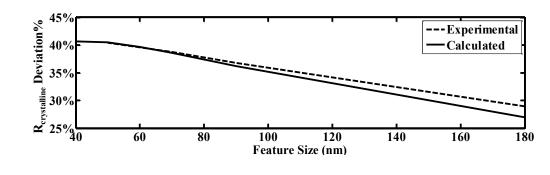

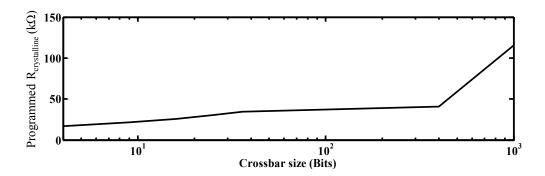

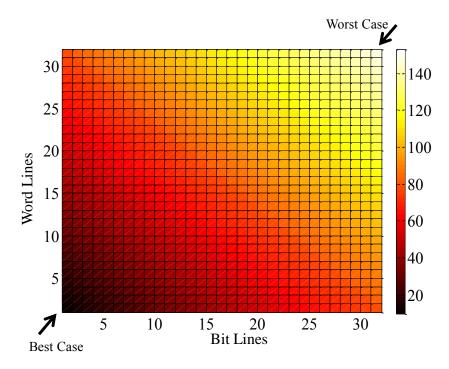

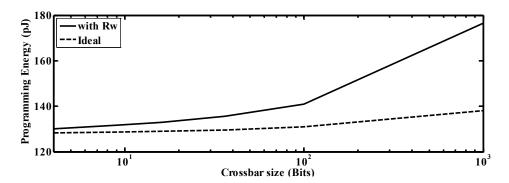

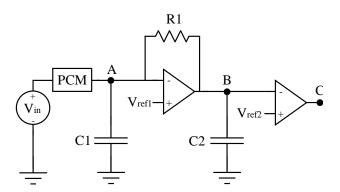

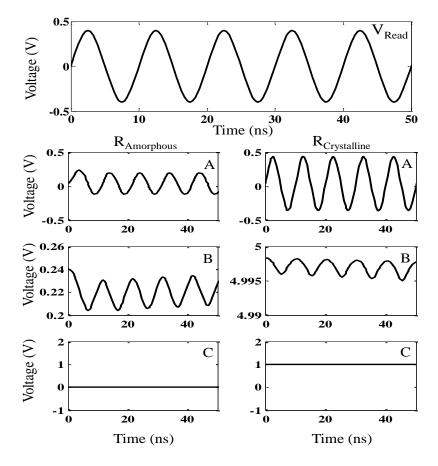

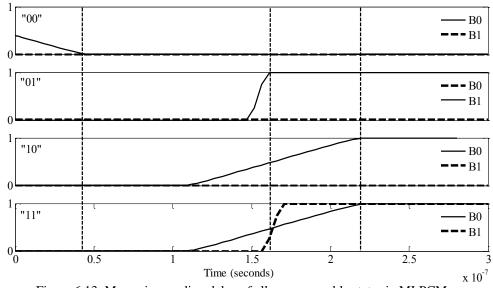

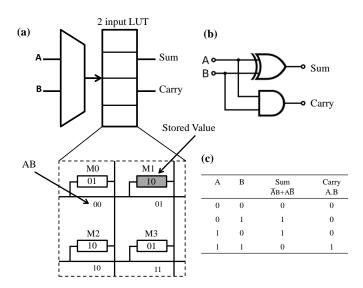

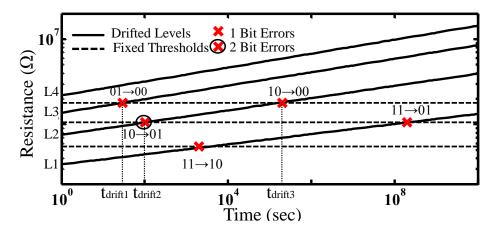

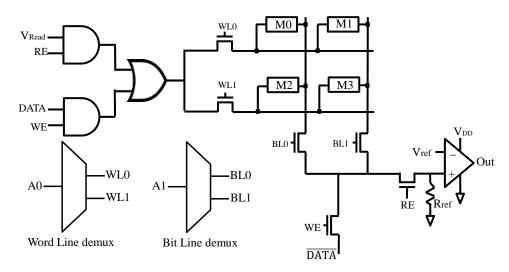

## 2.5.2.3 SET process