# Impact of Silicon Carbide Device Technologies on Matrix Converter Design and Performance

Saeed Safari, BSc, MSc

UNITED KINGDOM · CHINA · MALAYSIA

Submitted to the University of Nottingham for the degree of Doctor of Philosophy, August, 2014.

#### Abstract

The development of high power density power converters has become an important topic in power electronics because of increasing demand in transportation applications including marine, aviation and vehicle system. The possibility for greater power densities due to absence of a DC link is made matrix converter topologies more attractive for these applications. Additionally, with the emerging SiC device technology, the operating switching frequency and temperature of the converter can be potentially increased. The extended switching frequency and temperature range provide opportunities to further improve the power density of the power converters.

The aim of this thesis is to understand how SiC devices are different from the conventional Si devices and the effect these differences have on the design and performance of a matrix converter. Specific gate drive circuits are designed and implemented to fully utilize the high speed switching capabilities of these emerging semiconductor devices. A method to evaluate the conduction and switching losses and performance of Si and SiC power devices in the matrix converter circuit is developed. The developed method is used to compare power losses of matrix converters designed with different Si and SiC devices for a range of operating temperatures and switching frequencies. A design procedure for matrix converter input filters is proposed to fulfil power quality standard requirements and maximize the filter power density. The impact of the switching frequency on the input filter volume has also been considered in this work. The output waveform distortion due to commutation time in high switching frequency SiC matrix converters is also investigated and a three-step current commutation strategy is used to minimize the problem. Finally the influence of parasitic inductance on the behaviour of SiC power MOSFET matrix converters is investigated to highlight the challenges of high speed power devices.

### Acknowledgement

I would specially like to thank to the University of Nottingham for awarding me the Dean of Engineering Research Scholarship under its world class Power Electronics, Machine and Control (PEMC) group of the Department of Electrical and Electronic Engineering.

I would also like to thank my supervisors Prof. Pat Wheeler and Dr. Alberto Castellazzi for their support over the course of this project.

I would like to thank Dr. Andrew Cross and Dr. Christian Klumpner for sparing their time to examine me on the work in this thesis and for your brilliant comments and suggestions.

I would like to present my sincere thankfulness to my dear father Jafar Safari and my dear mother Tayebeh Khoshnoodi for their great role in my life and their unwavering support in the pursuit of my interests.

Last but not least, I would like to express my gratitude to my wife, Elaheh Arjmand, for her patience and tolerance over the last four years. Viyana Safari, my dear daughter, your innocent and warm smiles, and the times we shared together kept me going during this study and I am more than grateful to have you around.

# Contents

| Cha | apto | er 1 Introduction                                       | 1   |

|-----|------|---------------------------------------------------------|-----|

| 1.1 | Intr | oduction                                                | 1   |

| 1.2 | Ν    | Aatrix Converter Technology                             | 2   |

| 1.3 | R    | Research Motivation                                     | 4   |

| 1.4 | Res  | earch Objectives                                        | 6   |

| 1.5 | The  | esis Outline                                            | 7   |

| Cha | apto | er 2 Power Semiconductor Devices                        | 9   |

| 2.1 | Sili | con and Silicon Carbide                                 | 10  |

| 2.2 | Sui  | table Devices for AC/AC Converters                      | .11 |

| 2.3 | Si I | GBT                                                     | .12 |

| 2.4 | SiC  | Diode                                                   | .14 |

| 2.5 | SiC  | Power MOSFET                                            | .14 |

| 2.5 | .1   | Device Structure and Properties of SiC Power MOSFET     | 15  |

| 2.5 | .2   | Operation and Driving of SiC MOSFET                     | .17 |

| 2.6 | SiC  | JFET                                                    | 18  |

| 2.6 | .1   | Device Structure and Properties of SiC JFET             | 18  |

| 2.6 | .2   | Operation and Driving of SiC JFETs                      | 20  |

| 2.7 | SiC  | BJT                                                     | .23 |

| 2.7 | .1   | Device Structure and Properties of SiC BJT              | .24 |

| 2.7 | .2   | Operation and Driving of SiC BJT                        | .25 |

| 2.8 | Sun  | nmary                                                   | .27 |

| Cha | apto | er 3 The Matrix Converter Concept                       | .29 |

| 3.1 | Ma   | trix Converter Topology                                 | .30 |

| 3.2 | Spa  | ce Vector Modulation for Matrix Converters              | .33 |

| 3.3 | Bid  | irectional Switch Structures                            | .44 |

| 3.3 | .1   | Diode Bridge Embedded Bidirectional Switch              | .44 |

| 3.3 | .2   | Anti-series IGBT with Antiparallel Diode Configurations | .45 |

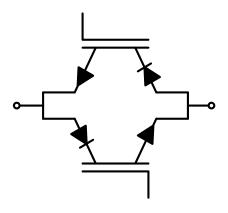

| 3.3 | .3 Antiparallel RB-IGBTs                                  | 46          |

|-----|-----------------------------------------------------------|-------------|

| 3.4 | Commutation Strategies                                    | 47          |

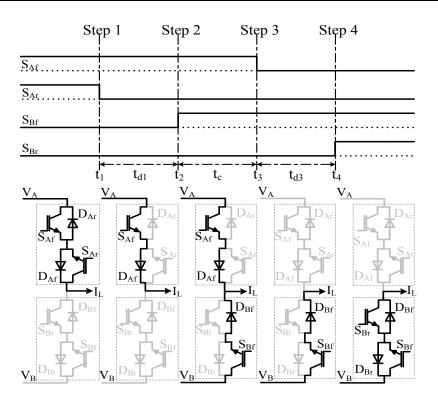

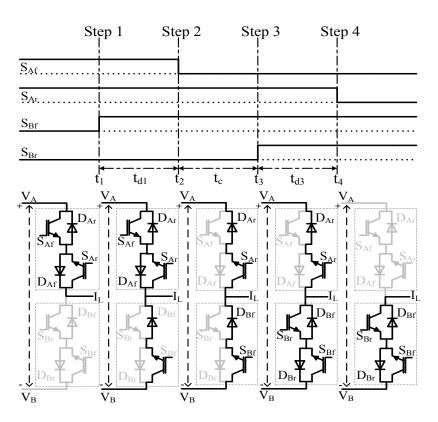

| 3.4 | .1 Four-Step Commutation Based on Output Current Direct   | ion48       |

| 3.4 | .2 Four-Step Commutation Based on the Sign of the Input l | ine-to-line |

|     | Voltage                                                   | 53          |

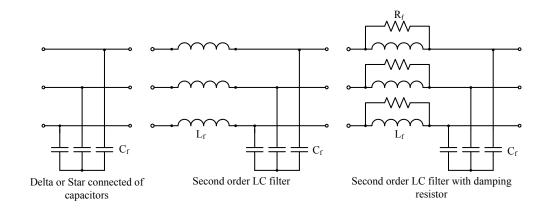

| 3.5 | Input Filter                                              | 55          |

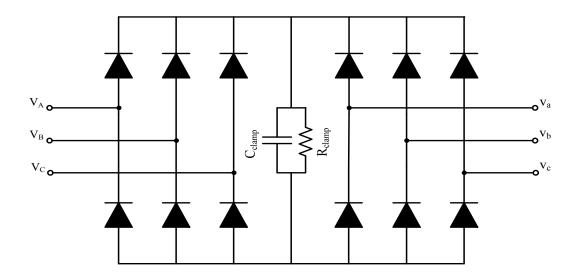

| 3.6 | Clamp Circuit                                             | 56          |

| 3.7 | Simulation Results                                        | 59          |

| 3.8 | Summary                                                   | 63          |

| Cha | apter 4 Hardware Prototype                                |             |

|     | Implementation                                            | 66          |

| 4.1 | Matrix Converter Power Circuit                            | 67          |

| 4.1 | .1 High Current, High Voltage Conduction Areas            | 69          |

| 2   | 4.1.1.1 High Voltage Implications                         | 70          |

| 2   | 4.1.1.2 High Current Implications                         | 70          |

| 4.1 | .2 Low Voltage Measurement Signal                         | 71          |

| 4.2 | Drive Circuit                                             | 72          |

| 4.2 | .1 Si IGBT Gate Drive                                     | 74          |

| 4.2 | .2 SiC MOSFET Gate Drive                                  | 75          |

| 4.2 | .3 Normally-off SiC JFET Gate Drive                       | 77          |

| 4.2 | .4 SiC BJT Base Drive                                     | 79          |

| 4.3 | Clamp Circuit                                             | 81          |

| 4.4 | Current Direction Detection Circuit                       |             |

| 4.5 | Measurement Circuit and Techniques                        |             |

| 4.6 | Control Board                                             |             |

| 4.6 | .1 Digital Signal Processor (DSP)                         |             |

| 4.6 | .2 Field Programmable Gate Array (FPGA)                   |             |

| 4.7 | Summary                                                   |             |

| Cha | apter 5 Power Losses Evaluation                           | 90          |

| 5.1 | Power Losses of the Si IGBT                               | 91          |

| 5.1 | .1 On-state Performance of the Si IGBT                    | 92          |

| 5.1 | .2 Dynamic Performance of the Si IGBT                     | 96          |

| 5.2                             | Power Losses of the SiC MOSFET                                                                                                                                                                                | 100                                                  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 5.2                             | 0.1 On-state Performance of the SiC MOSFET                                                                                                                                                                    | 100                                                  |

| 5.2                             | 2.2 Dynamic Performance of the SiC MOSFET                                                                                                                                                                     | 104                                                  |

| 5.3                             | Power Losses of the SiC JFET                                                                                                                                                                                  | 108                                                  |

| 5.3                             | On-state Performance of the SiC JFET                                                                                                                                                                          | 108                                                  |

| 5.3                             | Dynamic Characterization of the SiC JFET                                                                                                                                                                      | 111                                                  |

| 5.4                             | Power Losses of the SiC BJT                                                                                                                                                                                   | 115                                                  |

| 5.4                             | 1.1 Static Characterization of the SiC BJT                                                                                                                                                                    | 115                                                  |

| 5.4                             | .2 Dynamic Characterization of the SiC BJT                                                                                                                                                                    | 117                                                  |

| 5.5                             | Performance Comparison of the Selected Power Devices                                                                                                                                                          | 121                                                  |

| 5.6                             | Power Losses Evaluation of Matrix Converter                                                                                                                                                                   | 123                                                  |

| 5.6                             | D.1 Drive Losses                                                                                                                                                                                              | 124                                                  |

| 5.6                             | 6.2 Conduction Losses of Bidirectional Switch                                                                                                                                                                 | 126                                                  |

| 5.6                             | 5.3 Switching Losses                                                                                                                                                                                          | 128                                                  |

| 5.6                             | 6.4 Comparative Power Losses Analysis                                                                                                                                                                         | 133                                                  |

| 5.7                             | Summary                                                                                                                                                                                                       | 138                                                  |

| Cha                             | apter 6 Passive Components Minimization                                                                                                                                                                       | .140                                                 |

| 6.1                             | Power Quality Standards                                                                                                                                                                                       | 142                                                  |

| 6.2                             | Input Filter Topology                                                                                                                                                                                         | 143                                                  |

| 6.3                             | Calculation of Required Filter Attenuation                                                                                                                                                                    | 146                                                  |

| 6.4                             |                                                                                                                                                                                                               |                                                      |

| 6.5                             | Component Limits                                                                                                                                                                                              | 148                                                  |

| 0.0                             | Component Limits                                                                                                                                                                                              |                                                      |

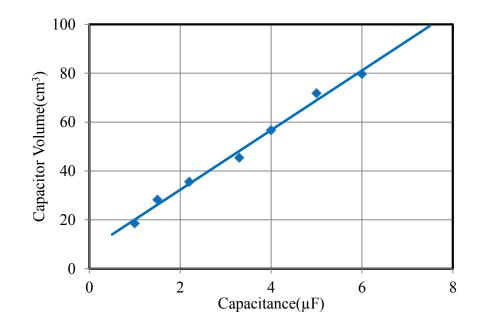

| 6.5                             | Volume Estimation of Filter Components                                                                                                                                                                        | 149                                                  |

|                                 | Volume Estimation of Filter Components         5.1       Capacitor                                                                                                                                            | 149<br>149                                           |

| 6.5                             | Volume Estimation of Filter Components         5.1       Capacitor                                                                                                                                            | 149<br>149<br>151                                    |

| 6.5<br>6.5                      | Volume Estimation of Filter Components         5.1       Capacitor         5.2       Inductor                                                                                                                 | 149<br>149<br>151<br>153                             |

| 6.5<br>6.5<br>6.6               | Volume Estimation of Filter Components         5.1       Capacitor         5.2       Inductor         Input Filter Design                                                                                     | 149<br>149<br>151<br>153<br>156                      |

| 6.5<br>6.5<br>6.6<br>6.7        | Volume Estimation of Filter Components         5.1       Capacitor         5.2       Inductor         Input Filter Design         Design Outcomes                                                             | 149<br>149<br>151<br>153<br>156<br>159               |

| 6.5<br>6.6<br>6.7<br>6.8<br>6.9 | Volume Estimation of Filter Components         5.1       Capacitor         5.2       Inductor         Input Filter Design         Design Outcomes         Simulation and Experimental Results                 | 149<br>149<br>151<br>153<br>156<br>159<br>163        |

| 6.5<br>6.6<br>6.7<br>6.8<br>6.9 | Volume Estimation of Filter Components         5.1       Capacitor         5.2       Inductor         Input Filter Design         Design Outcomes         Simulation and Experimental Results         Summary | 149<br>149<br>151<br>153<br>156<br>159<br>163<br>164 |

| 7.1.2      | Enhance Waveform Quality Using Minimized Commu    |                  |

|------------|---------------------------------------------------|------------------|

| 7.1.3      | Experimental Results                              |                  |

| 7.2 Inf    | luence of Parasitic Inductance                    |                  |

| 7.2.1      | Analytical Modelling of SiC MOSFET Switching Char |                  |

|            | Due to Parasitic Inductance                       |                  |

| 7.2.1      | .1 Hard Turn-on Switching                         |                  |

| 7.2.1      | .2 Hard Turn-off Switching                        | 191              |

| 7.2.2      | Inductance Parasitic of PCB Trace                 | 195              |

| 7.2.3      | Experimental and Analytical Evaluation            | 197              |

| 7.3 Su     | mmary                                             |                  |

| Chapt      | er 8 Conclusion and Future Work                   | <b>x</b> 203     |

| 8.1 Co     | nclusions                                         |                  |

| 8.2 Fut    | ture Work                                         |                  |

| 8.3 Lis    | t of Publications                                 |                  |

| 8.3.1      | Journal Paper                                     |                  |

| 8.3.2      | Conference Papers                                 | 207              |

| Refere     | ences                                             |                  |

| Appen      | ndix A Lists of Acronyms and Sym                  | <b>1bols</b> 224 |

| List of Ac | ronyms                                            |                  |

| List of Sy | mbols                                             |                  |

|            | ndix B PCB Layers                                 |                  |

|            | idix C Switching Energy Calculation               |                  |

|            |                                                   |                  |

|            | Approach                                          |                  |

|            |                                                   |                  |

|            | FET                                               |                  |

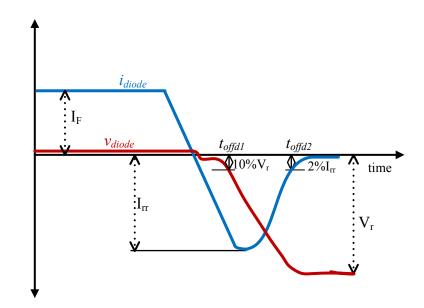

| Diode Tu   | rn-off Switching Energy                           | 239              |

# **List of Figures**

## Page

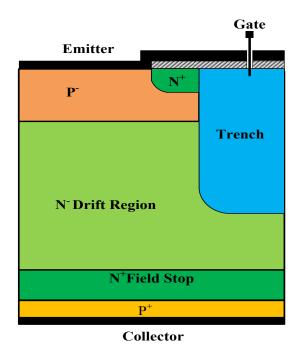

| Figure | 2.1:  | Schematic structure of T&FS IGBT13                                 |

|--------|-------|--------------------------------------------------------------------|

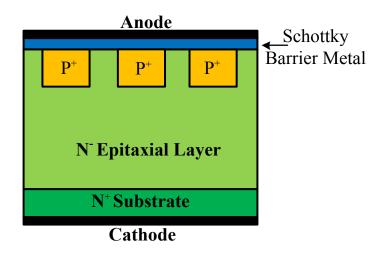

| Figure | 2.2:  | Schematic structure of JBS SiC diode14                             |

| Figure | 2.3:  | Schematic structure of SiC DMOSFET15                               |

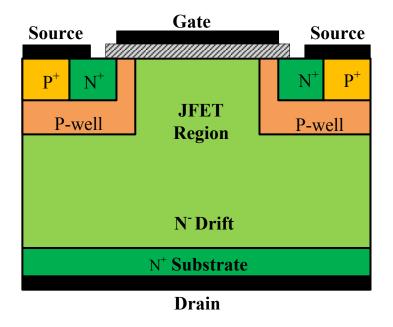

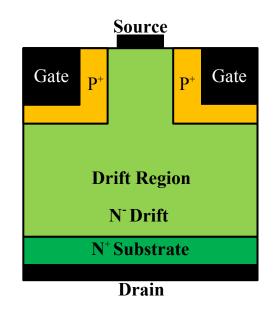

| Figure | 2.4:  | Schematic structure of SiC enhanced-mode vertical JFET19           |

| Figure | 2.5:  | Gate-source current of normally-off SiC JFET as a function of      |

|        |       | gate-source voltage                                                |

| Figure | 2.6:  | Simplified schematic diagram of the gate drive circuit for         |

|        |       | normally-off SiC JFET based on the charge pump circuit23           |

| Figure | 2.7:  | Schematic structure of SiC BJT                                     |

| Figure | 2.8:  | Simplified schematic diagram of base drive circuit for SiC BJT     |

|        |       |                                                                    |

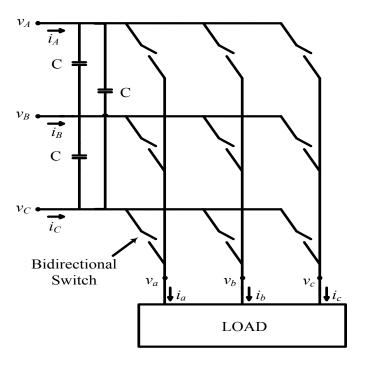

| Figure | 3.1:  | Basic 3×3 matrix converter circuit                                 |

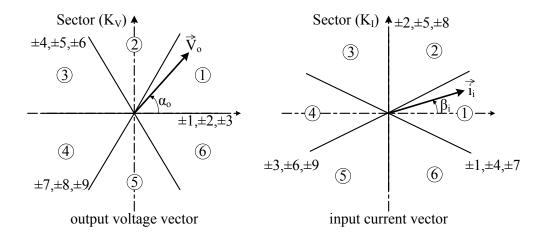

| Figure |       | Space vector of output voltage and input current generated by      |

| U      |       | the active configurations                                          |

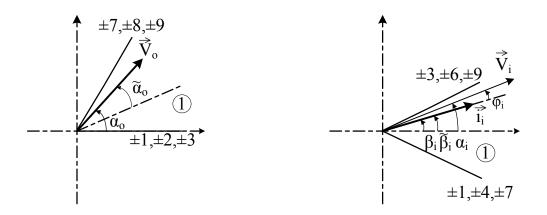

| Figure | 3.3:  | The synthesis of reference vectors in a given sector               |

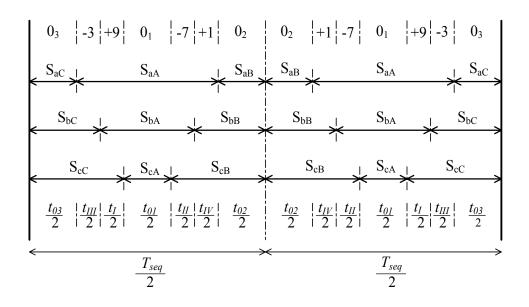

| Figure | 3.4:  | Double sided switching pattern of the space vector modulation      |

| -      |       | in a switching period T <sub>seq</sub>                             |

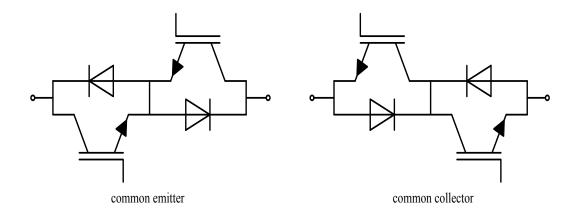

| Figure | 3.5:  | Diode bridge embedded bidirectional switch configuration45         |

| Figure | 3.6:  | Anti-series IGBT with antiparallel diode configurations45          |

| Figure | 3.7:  | RB-IGBT bidirectional switch configuration                         |

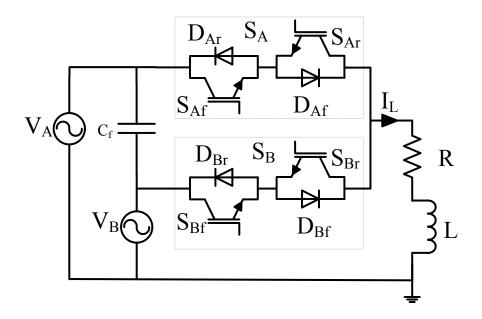

| Figure | 3.8:  | Two-phase to one-phase matrix converter                            |

| Figure | 3.9:  | Timing diagram and sequence of four-step current commutation       |

|        |       | when the output current is positive and constant                   |

| Figure | 3.10: | Timing diagram and sequence of four-step commutation based         |

|        |       | on input voltage magnitude when $VA-VB > 0$                        |

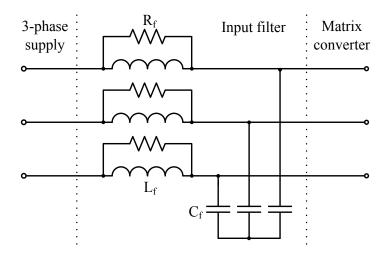

| Figure | 3.11: | Input filter configurations for matrix converter                   |

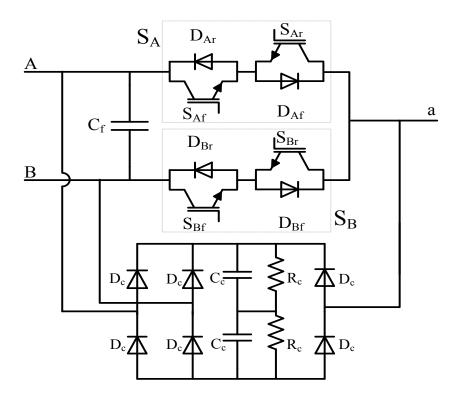

| Figure | 3.12: | Clamp circuit for the matrix converter                             |

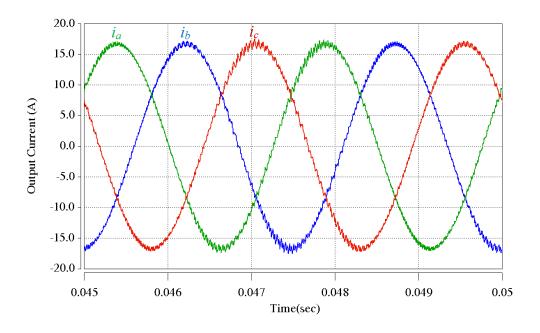

| Figure | 3.13: | The three-phase output currents of matrix converter when the       |

|        |       | switching frequency is 10 kHz61                                    |

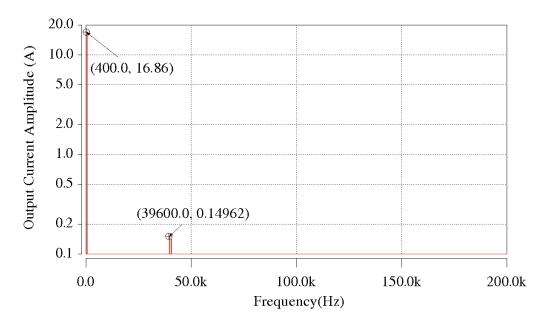

| Figure | 3.14: | Harmonic spectrum of matrix converter output current, $i_a$ , when |

|        |       | the switching frequency is 10 kHz61                                |

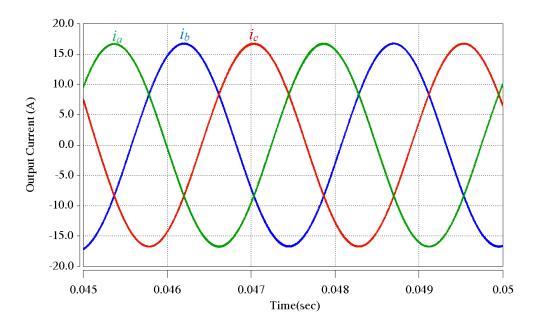

| Figure | 3.15: | The three-phase output currents of matrix converter when the       |

|        |       | switching frequency is 80 kHz62                                    |

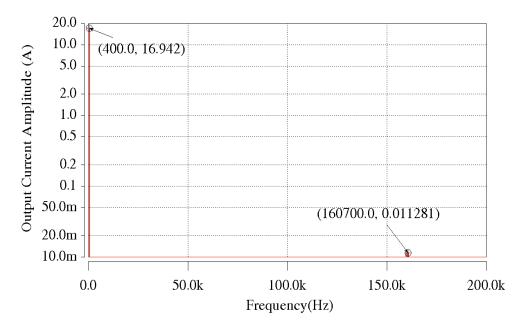

| Figure 3.16: | Harmonic spectrum of matrix converter output current, $i_a$ , when |

|--------------|--------------------------------------------------------------------|

|              | the switching frequency is 80 kHz                                  |

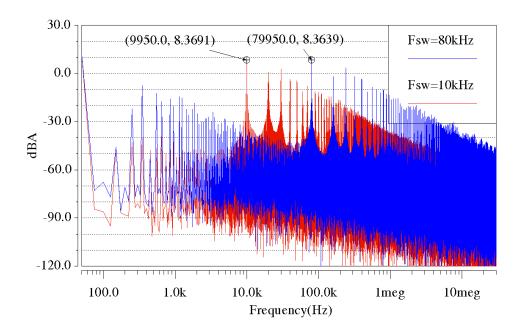

| Figure 3.17: | Spectrum of matrix converter unfiltered input current for          |

|              | different switching frequencies                                    |

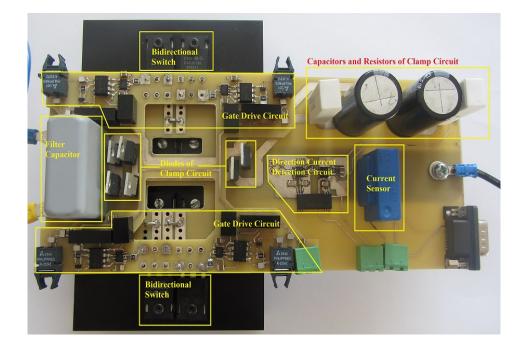

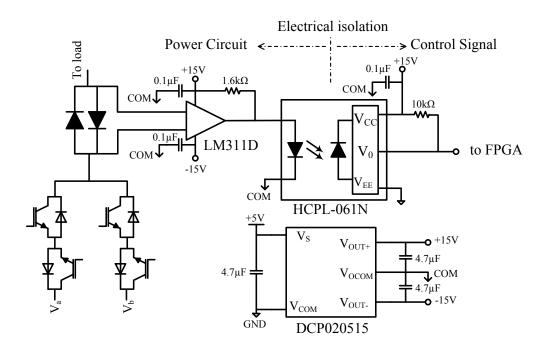

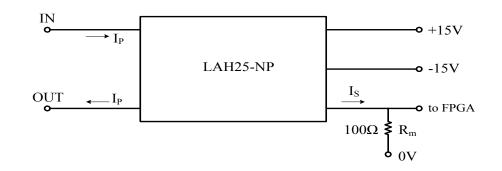

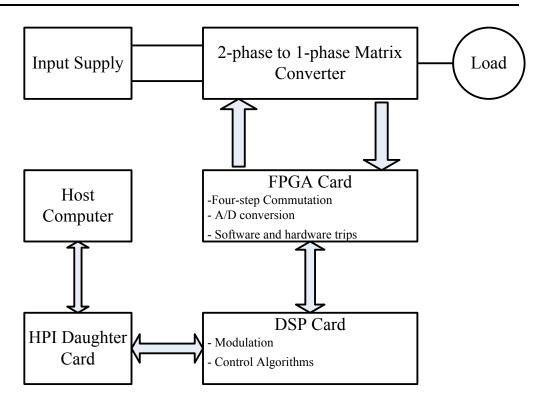

| Figure 4.1:  | Schematic diagram of experimental rig67                            |

| Figure 4.2:  | 2-phase to 1-phase matrix converter laboratory prototype68         |

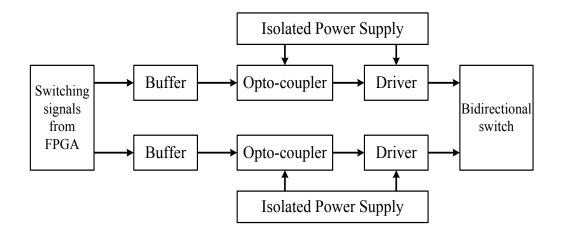

| Figure 4.3:  | A schematic diagram of the drive circuit for each bidirectional    |

|              | switch73                                                           |

| Figure 4.4:  | Schematic diagram of the gate drive circuit for the Si IGBT        |

|              | bidirectional switch74                                             |

| Figure 4.5:  | Schematic diagram of the gate drive circuit for the SiC            |

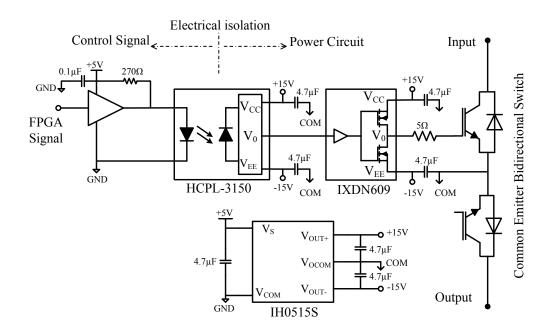

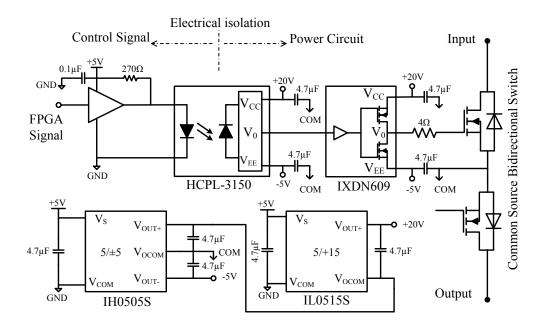

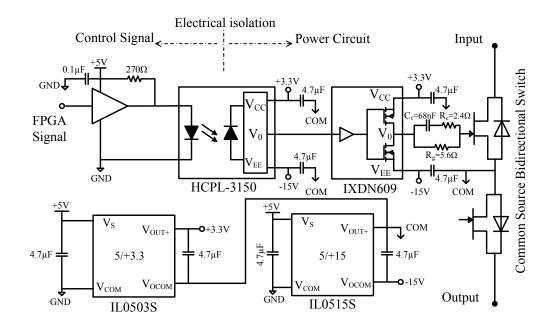

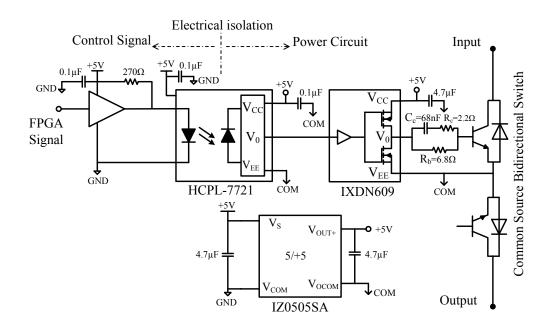

|              | MOSFET bidirectional switch76                                      |

| Figure 4.6:  | Schematic diagram of the gate drive circuit for the normally-off   |

|              | SiC JFET bidirectional switch79                                    |

| Figure 4.7:  | Schematic diagram of the gate drive circuit for the SiC BJT        |

|              | bidirectional switch                                               |

| Figure 4.8:  | Schematic diagram of the current direction detection circuit83     |

| Figure 4.9:  | Schematic diagram of the current measurement circuit               |

| Figure 4.10: | Diagram of overall matrix converter control implementation87       |

| Figure 5.1:  | The forward output characteristic of the IGBT92                    |

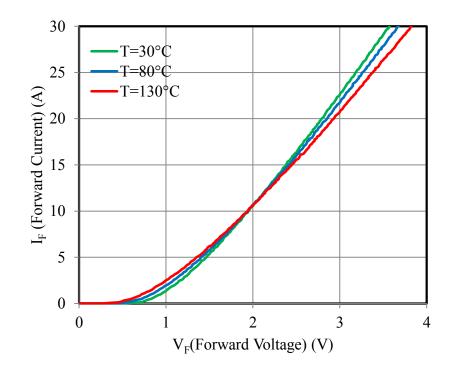

| Figure 5.2:  | The forward characteristic of the IGBT antiparallel diode93        |

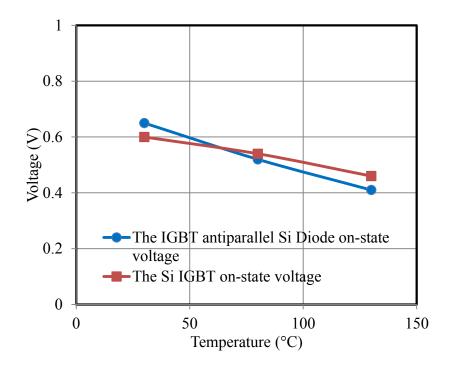

| Figure 5.3:  | The Si IGBT and its antiparallel diode on-state voltages for       |

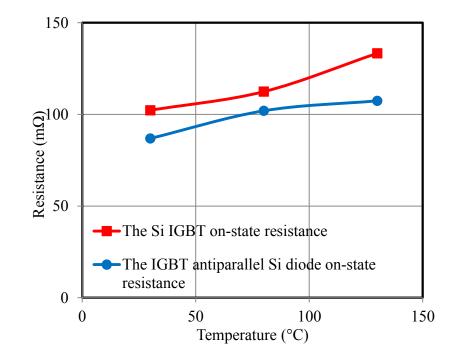

|              | different temperatures                                             |

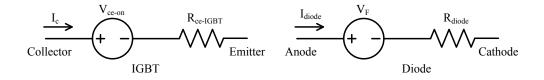

| Figure 5.4:  | The Si IGBT and its antiparallel diode on-state resistances for    |

|              | different temperatures95                                           |

| Figure 5.5:  | Electrical models of the IGBT and diode during conduction96        |

| Figure 5.6:  | Experimentally measured hard turn-on switching waveforms of        |

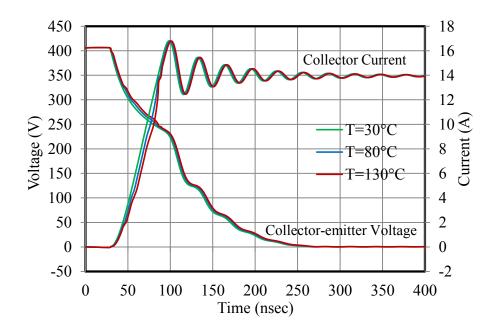

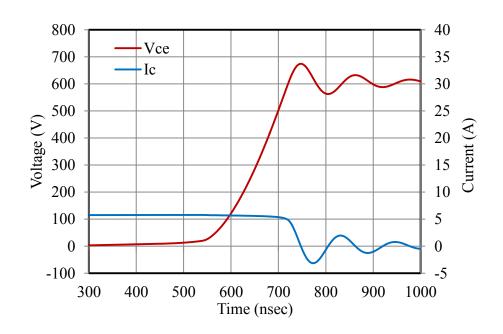

|              | Si IGBT in a bidirectional switch of the matrix converter97        |

| Figure 5.7:  |                                                                    |

|              | Si IGBT in bidirectional switch                                    |

| Figure 5.8:  | Switching energy losses of Si IGBT devices in different            |

|              | voltages, load currents and temperatures                           |

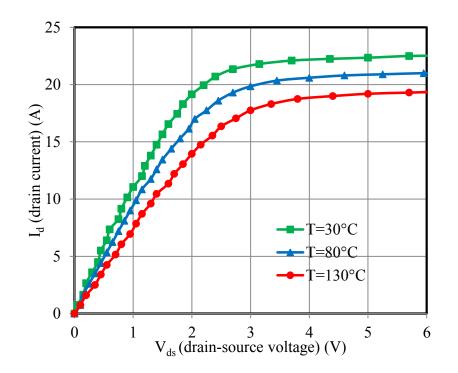

| Figure 5.9:  | The forward output characteristic of the SiC MOSFET at 25°C        |

|              |                                                                    |

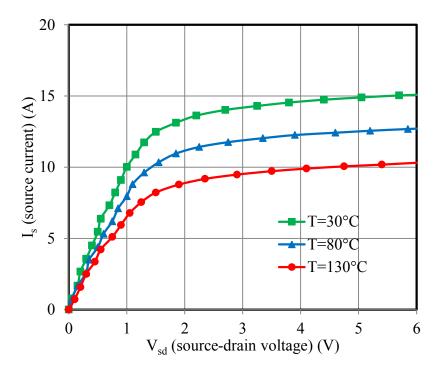

| Figure 5.10: | Reverse conduction characteristics of the SiC MOSFET at on         |

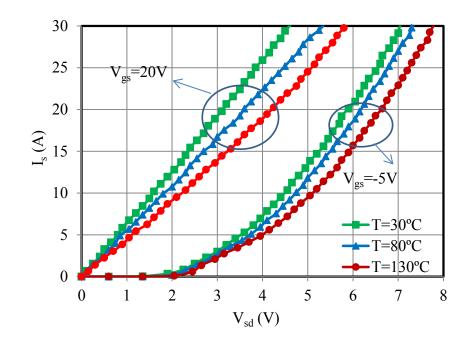

|              | and off gate-source voltage for different temperatures102          |

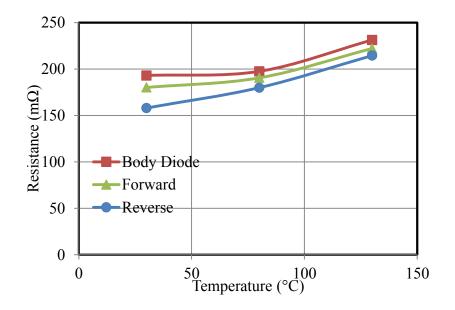

| Figure 5.11: | SiC MOSFET on-state resistance in forward and reverse              |

|              | conduction modes and on-state resistance of its body diode103      |

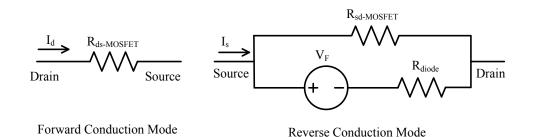

| Figure 5.12: | Electrical schematic of the SiC MOSFET model during forward        |

|              | and reverse conduction mode                                        |

| Figure 5.13: | Experimentally measured hard turn-on switching waveforms of        |

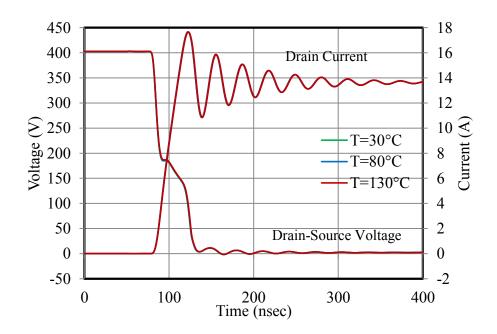

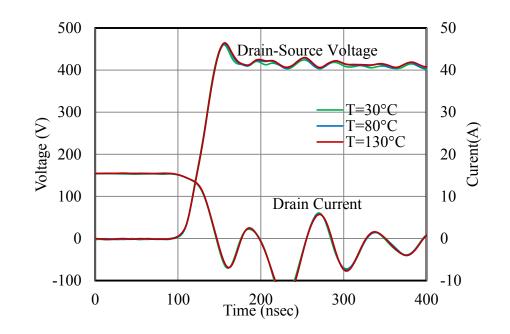

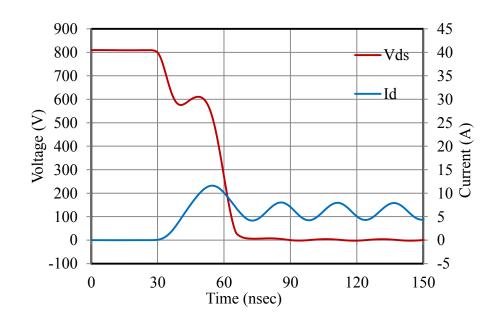

|              | SiC MOSFET in bidirectional switch105                              |

| Figure 5.14: | Experimentally measured hard turn-off switching waveforms of       |

|              | SiC MOSFET in bidirectional switch106                                     |

|--------------|---------------------------------------------------------------------------|

| Figure 5.15: | Switching energy losses of SiC MOSFET devices in different                |

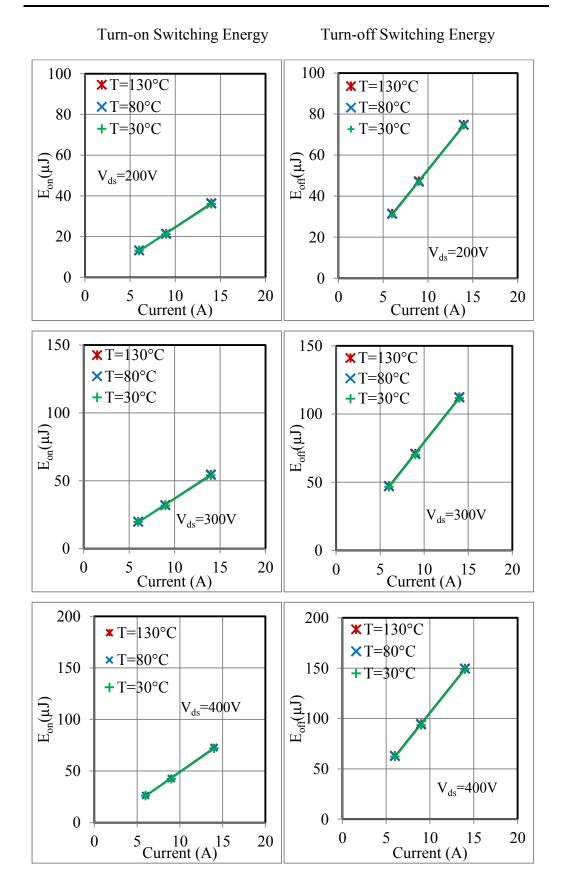

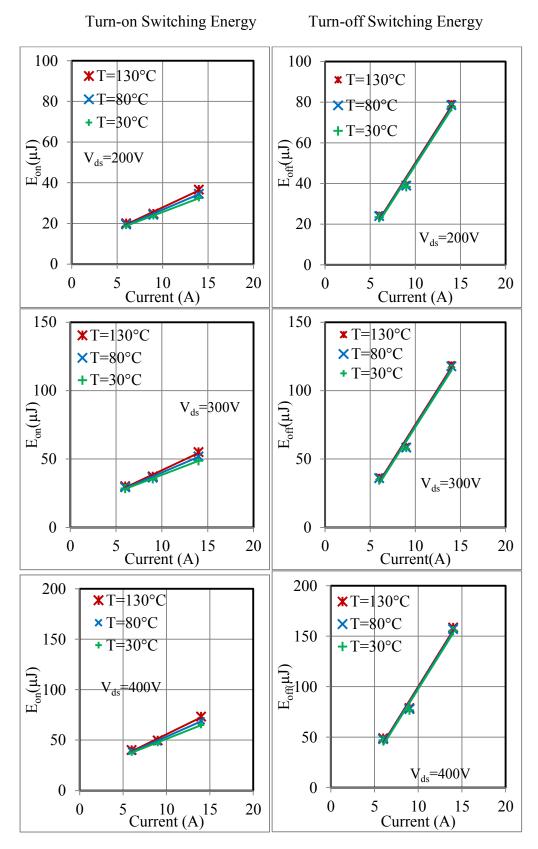

|              | voltages, load currents and temperatures107                               |

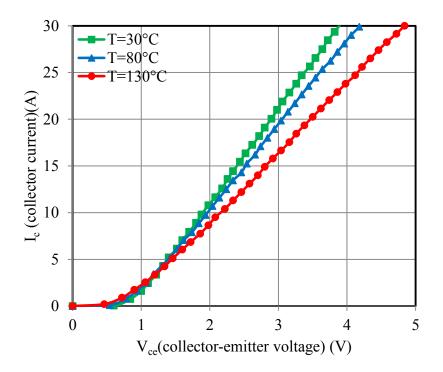

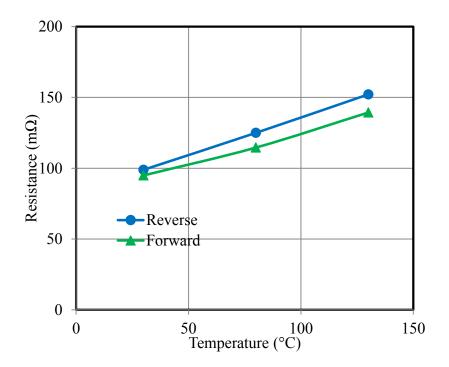

| Figure 5.16: | Forward output characteristics of SiC JFET for different                  |

|              | temperatures when gate-source voltage is 2.5V109                          |

| Figure 5.17: | Reverse conduction characteristics of SiC JFET for different              |

|              | temperatures when the gate-source voltage is 2.5V109                      |

| Figure 5.18: | Forward and reverse on-state resistance of the SiC JFET at                |

|              | different temperatures                                                    |

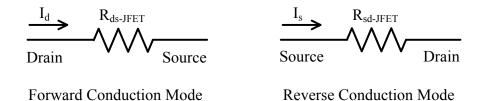

| Figure 5.19: | Electrical equivalent model of the normally-off SiC JFET in the           |

| -            | forward and reverse conduction modes                                      |

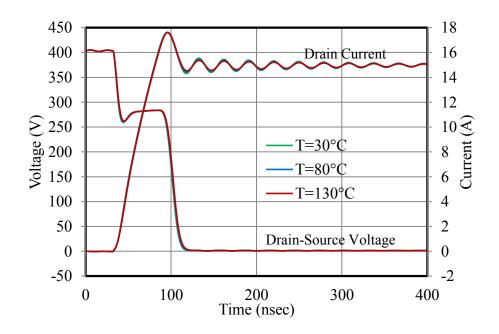

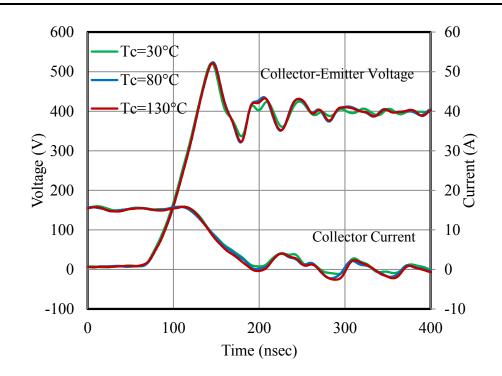

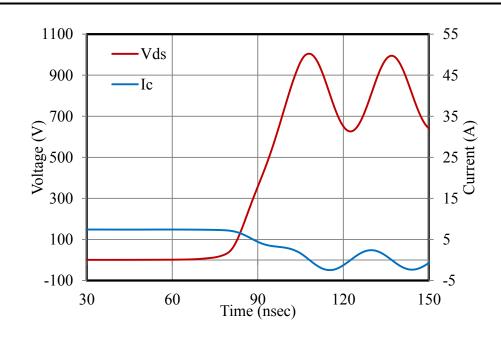

| Figure 5.20: | Measured hard turn-on switching waveforms of SiC JFET in                  |

| C            | bidirectional switch                                                      |

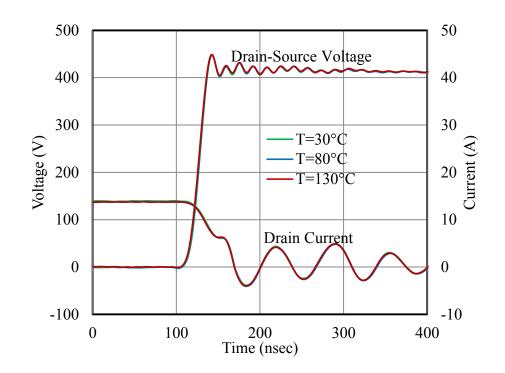

| Figure 5.21: | Measured hard turn-off switching waveforms of SiC JFET in                 |

| -            | bidirectional switch                                                      |

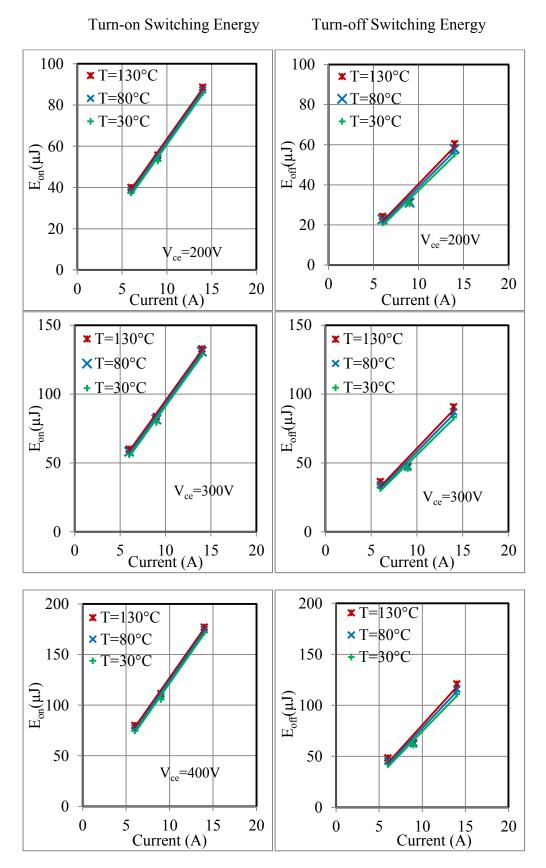

| Figure 5.22: | Switching energy losses of SiC JFET devices in different                  |

| C            | voltages, load currents and temperatures                                  |

| Figure 5.23: | Forward output characteristics of SiC BJT at different                    |

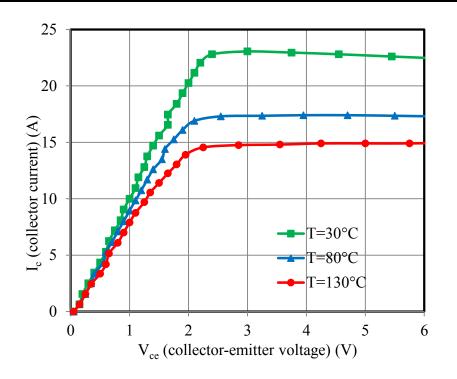

| e            | temperatures when the base current is 250mA                               |

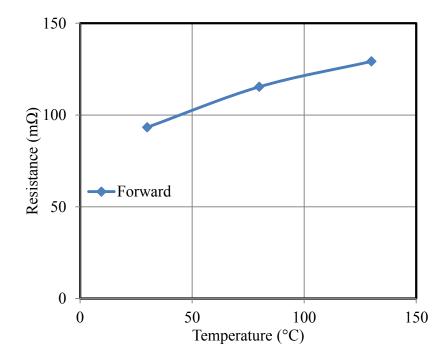

| Figure 5.24: | On-state resistances of the SiC BJT at different temperatures 116         |

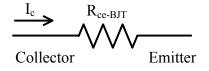

| Figure 5.25: | Schematic of electrical model of the SiC BJT during conduction            |

| C            | mode                                                                      |

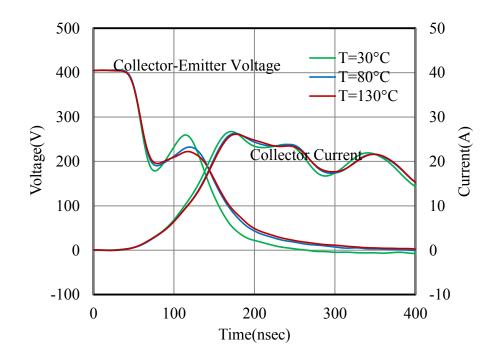

| Figure 5.26: | Measured hard turn-on switching waveforms of SiC BJT in                   |

| -            | bidirectional switch                                                      |

| Figure 5.27: | Measured hard turn-off switching waveforms of SiC BJT in                  |

| -            | bidirectional switch                                                      |

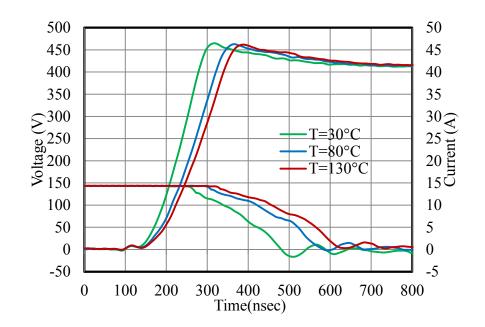

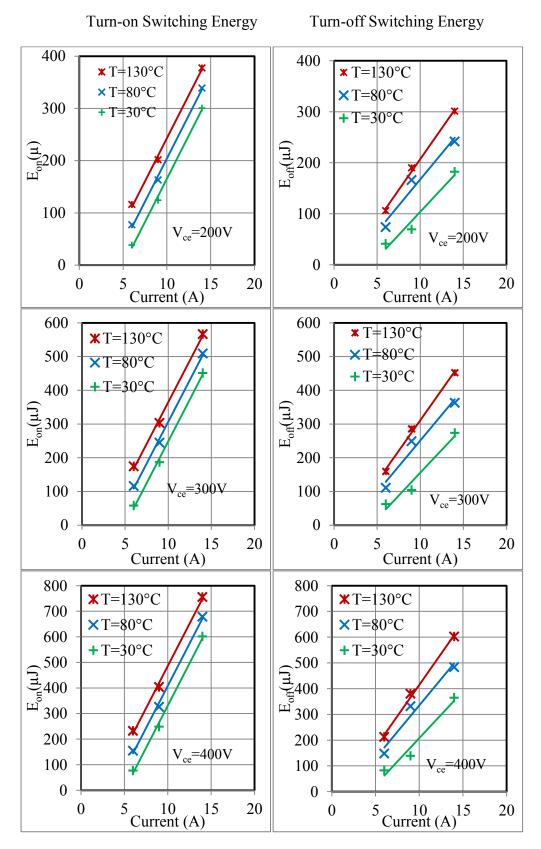

| Figure 5.28: | Switching energy losses of SiC BJT devices in different                   |

| -            | voltages, load currents and temperatures                                  |

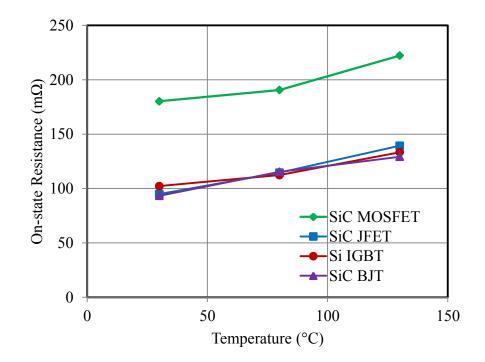

| Figure 5.29: | On-state resistance versus temperature for the different power            |

| -            | devices                                                                   |

| Figure 5.30: | Total switching energy versus current for different power                 |

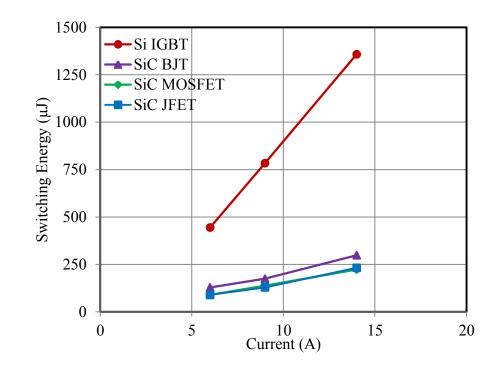

|              | devices at 400V and 130°C                                                 |

| Figure 5.31: | Schematic representation of switching function for switch S <sub>aA</sub> |

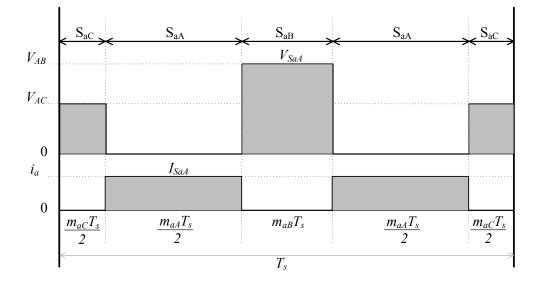

|              | with double sided space vector modulation131                              |

| Figure 5.32: | Drive, conduction and switching losses of Si and SiC power                |

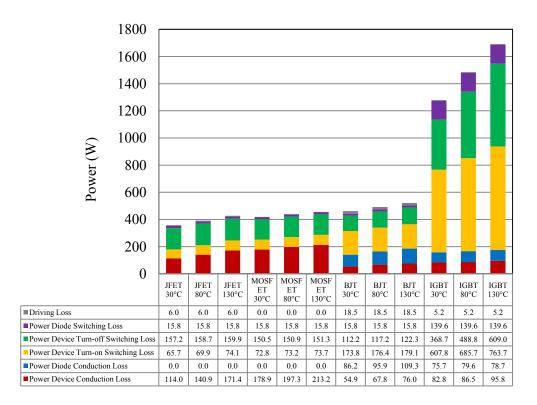

|              | devices for an 8.2 kW three phase matrix converter when                   |

|              | switching frequency is 80 kHz at different temperatures134                |

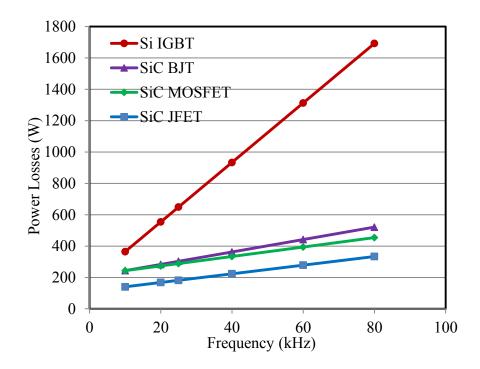

| Figure 5.33: | Variation of calculated matrix converter losses with switching            |

|              | frequency at rated load and temperature of 130 °C for various             |

|              | devices                                                                   |

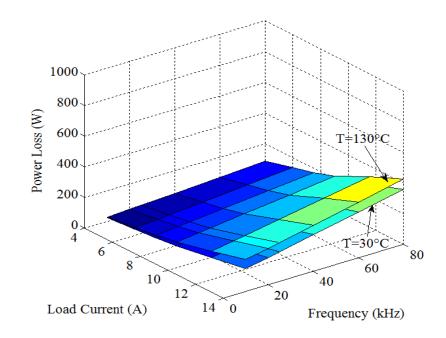

| Figure 5.34: | SiC JFET matrix converter power losses surface                            |

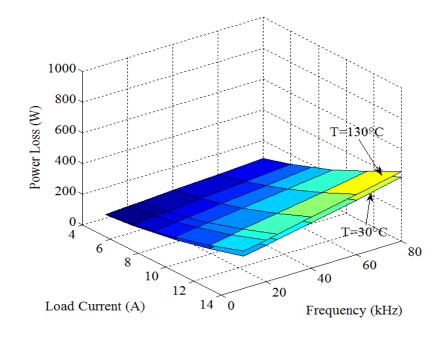

| Figure 5.35: | SiC MOSFET matrix converter power losses surface                          |

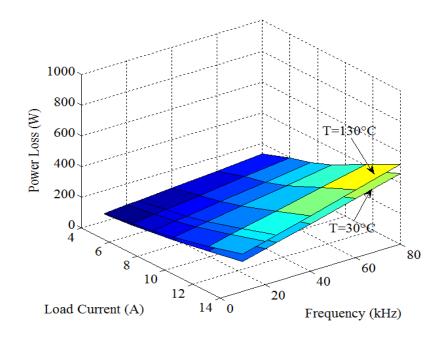

| Figure 5.36: | SiC BJT matrix converter power losses surface                             |

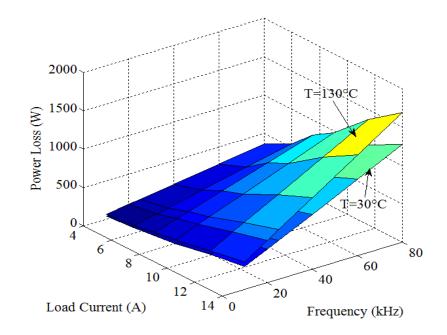

| Figure 5.37: | Si IGBT matrix converter power losses surface                         |

|--------------|-----------------------------------------------------------------------|

| Figure 6.1:  | LC filter with parallel damping resistor                              |

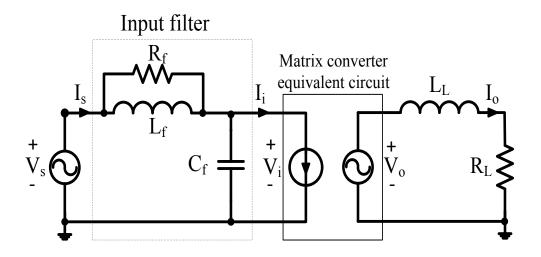

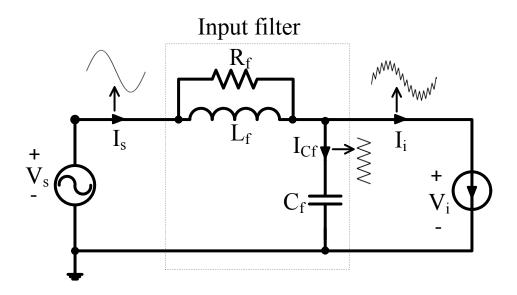

| Figure 6.2:  | Single-phase equivalent circuit of the matrix converter               |

| Figure 6.3:  | Idealized current waveforms for each filter component                 |

| Figure 6.4:  | Volume versus capacitance of 440V polypropylene film                  |

| U            | capacitors from EPCOS                                                 |

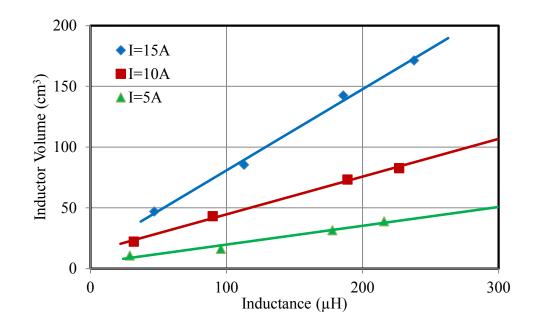

| Figure 6.5:  | Volume versus inductance for toroidal inductors based on the          |

| U            | MPP core material for a range of current ratings                      |

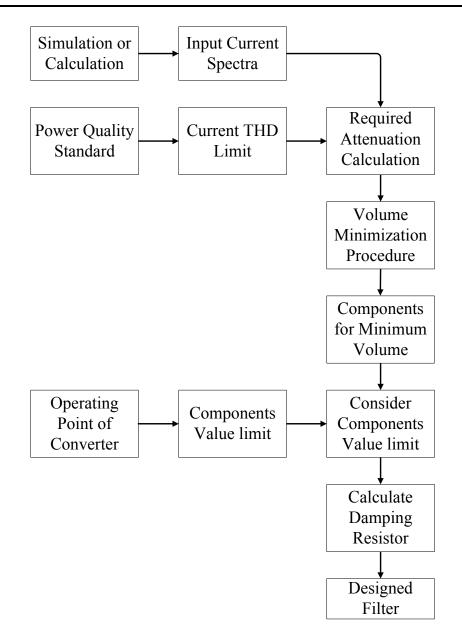

| Figure 6.6:  | Flowchart showing the input filter design procedure155                |

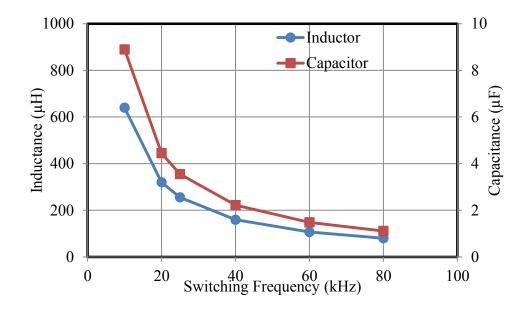

| Figure 6.7:  | Inductor and capacitor values versus switching frequency for the      |

| C            | considered input filter design                                        |

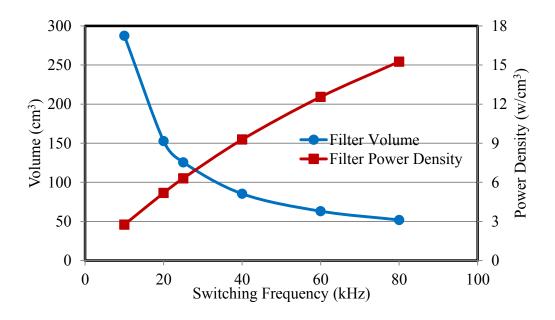

| Figure 6.8:  | Volume and power density of input filter versus switching             |

| C            | frequency for an 800W 2-phase to 1-phase matrix converter.158         |

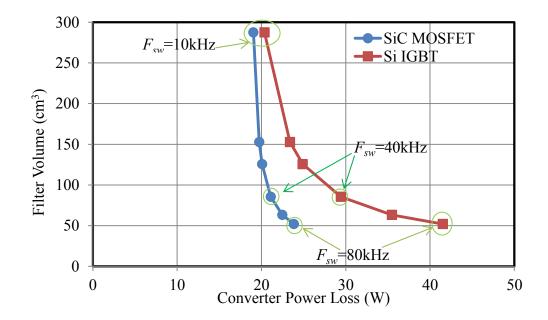

| Figure 6.9:  | Input filter volume versus converter losses for a range of            |

| C            | switching frequencies corresponding for 2-phase to 1-phase            |

|              | matrix converter                                                      |

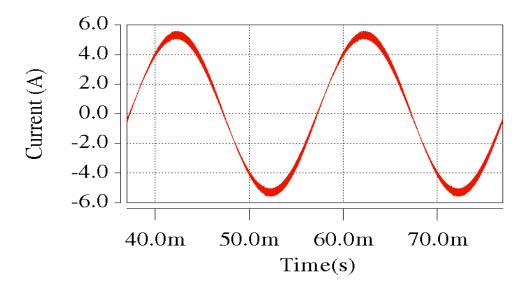

| Figure 6.10: | Simulated supply current waveform of the selected filter160           |

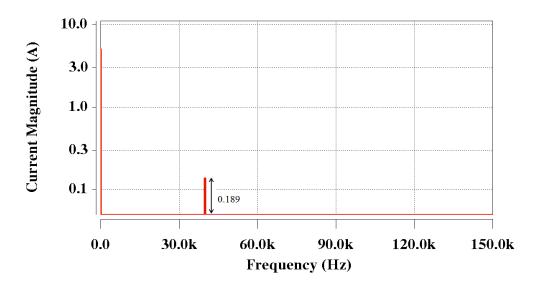

| Figure 6.11: | Spectrum of simulated filtered input current for the selected         |

| -            | filter                                                                |

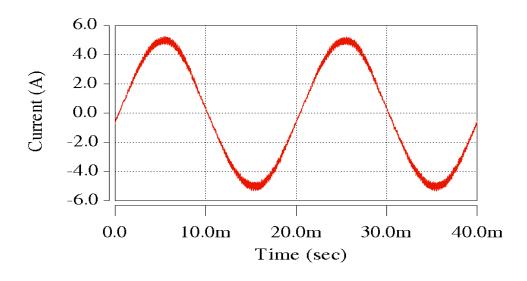

| Figure 6.12: | Measured input current waveform of matrix converter input             |

| -            | filter                                                                |

| Figure 6.13: | Spectrum of measured filtered input current of matrix converter       |

| -            | for the selected filter                                               |

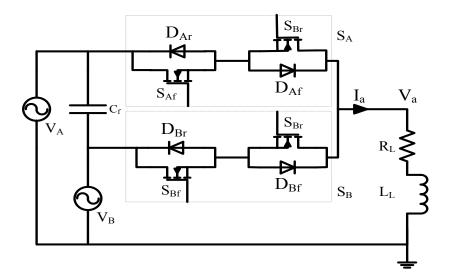

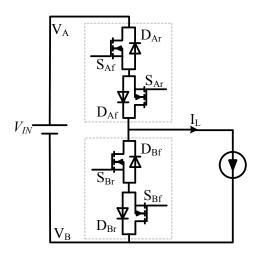

| Figure 7.1:  | Schematic of two bidirectional switch                                 |

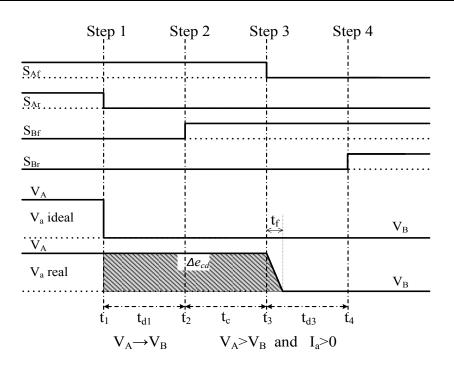

| Figure 7.2:  | Four-step current base commutation sequence from phase A to           |

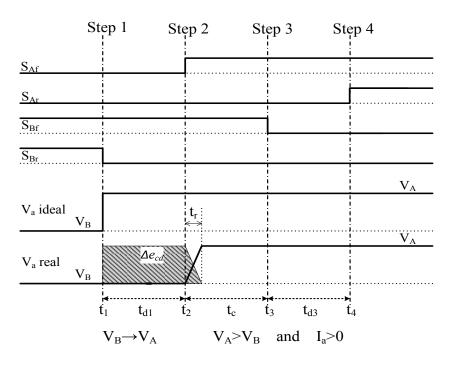

| 8            | phase B for positive output current ( $I_a > 0$ ) and $V_A > V_B$ 168 |

| Figure 7.3:  | Four-step current base commutation sequence from phase B to           |

| 8            | phase A for positive output current ( $I_a > 0$ ) and $V_A > V_B$ 168 |

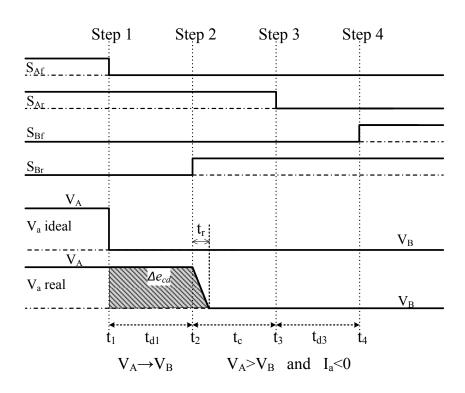

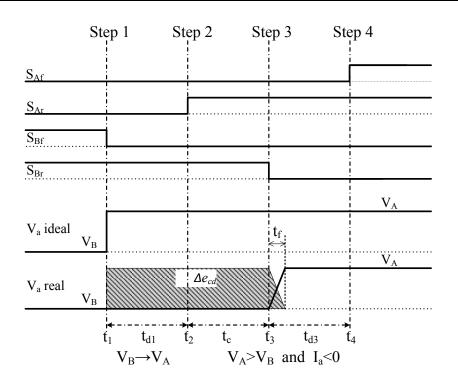

| Figure 7.4:  | Four-step current base commutation sequence from phase A to           |

| - 8          | phase B for negative output current ( $I_a < 0$ ) and $V_A > V_B$ 170 |

| Figure 7.5:  | Four-step current base commutation sequence from phase B to           |

| 8            | phase A for negative output current ( $I_a < 0$ ) and $V_A > V_B$ 171 |

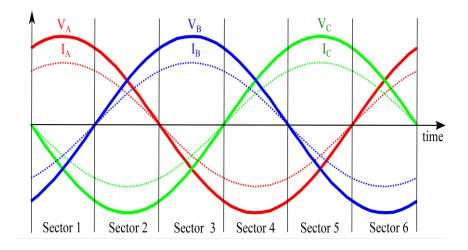

| Figure 7.6:  | The input voltage sectors in matrix converter                         |

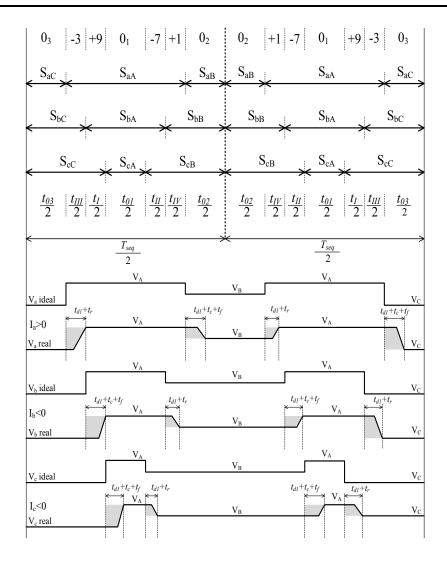

| Figure 7.7:  | The double-sided switching pattern of SVM in input sector 1 in        |

| e            | a PWM period                                                          |

| Figure 7.8:  | Output voltage of matrix converter due to commutation time            |

| e            | effect                                                                |

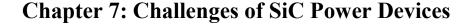

| Figure 7.9:  | Three-step current commutation strategy                               |

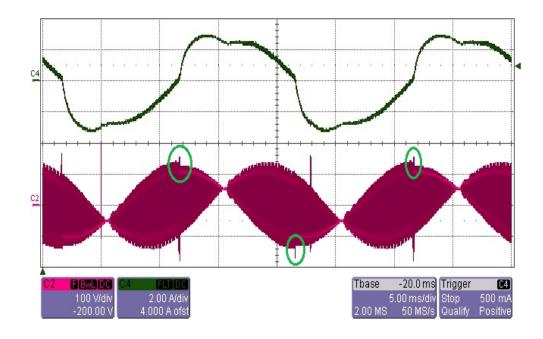

| Figure 7.10: | Output current and output voltage when the switching frequency        |

| -            | and commutation time of matrix converter are 80 kHz and 2000          |

|              | nsec respectively                                                     |

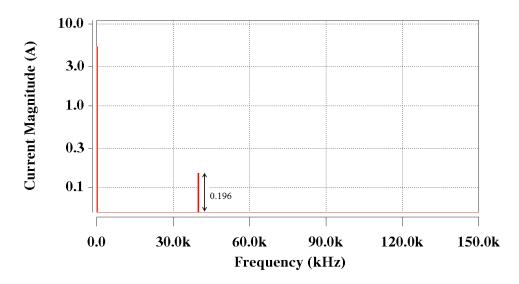

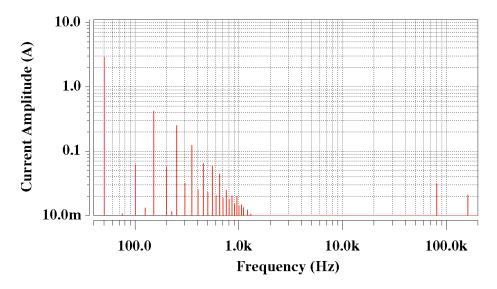

| Figure 7.11: | Harmonic spectrum of output current when the switching                |

|              | frequency and commutation time of matrix converter are 80             |

|               | kHz and 2000 nsec respectively179                              |

|---------------|----------------------------------------------------------------|

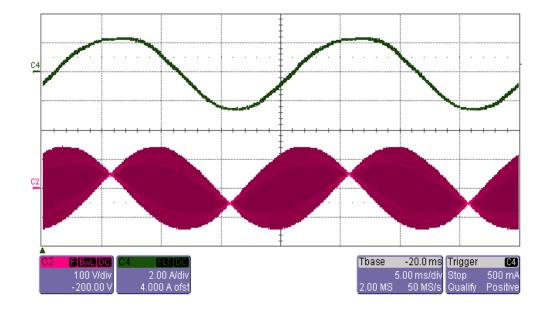

| Figure 7.12:  | Output current and output voltage when the switching frequency |

|               | and commutation time of matrix converter are 80 kHz and 0      |

|               | nsec respectively                                              |

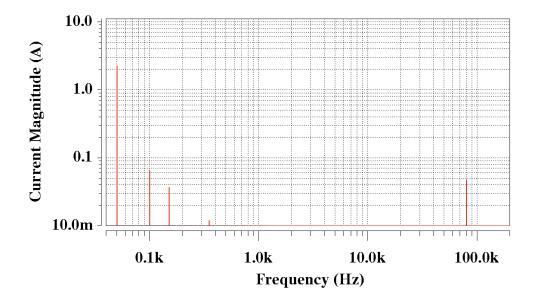

| Figure 7.13:  | Harmonic spectrum of output current when the switching         |

|               | frequency and commutation time of matrix converter are 80      |

|               | kHz and 0 nsec respectively                                    |

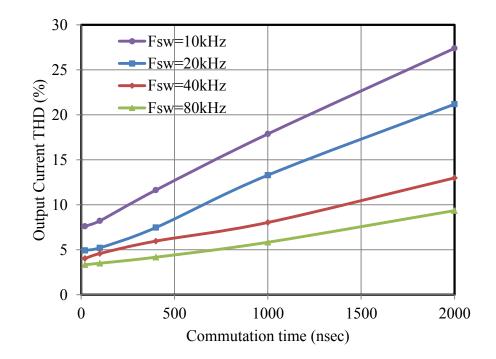

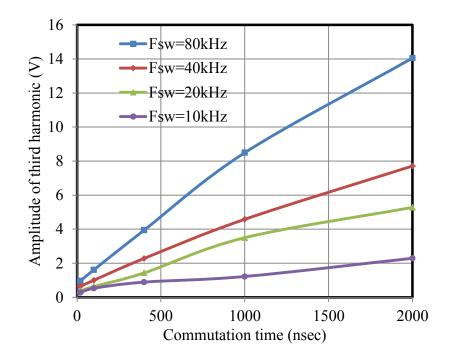

| Figure 7.14:  | THD of the measured output current in various switching        |

|               | frequencies and commutation times                              |

| Figure 7.15:  | Third harmonic of the measured output voltage in various       |

|               | switching frequencies and commutation times183                 |

| Figure 7.16:  | Circuit diagram of the 2-phase to 1-phase matrix converter185  |

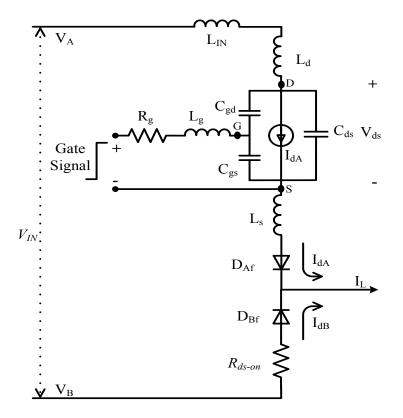

| Figure 7.17:  | Equivalent circuit diagram of the commutation leg187           |

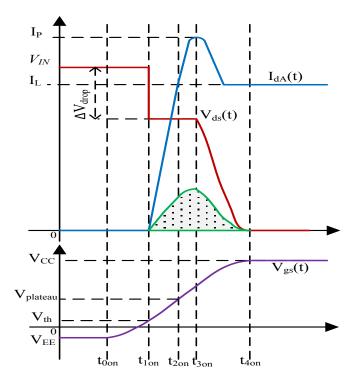

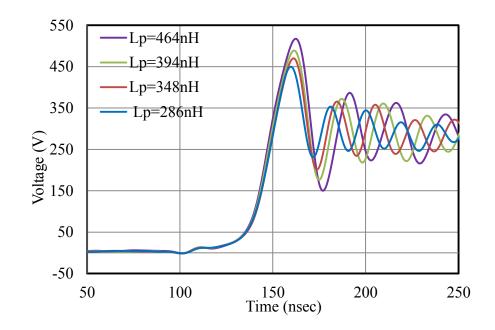

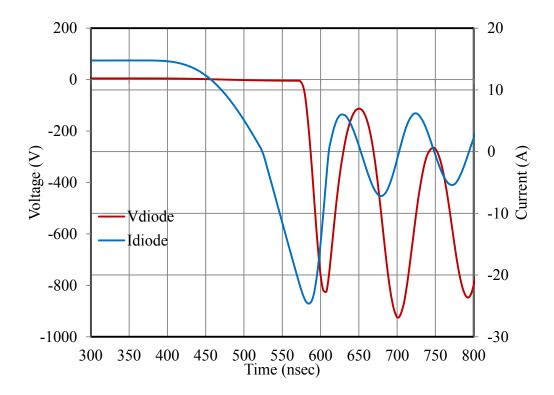

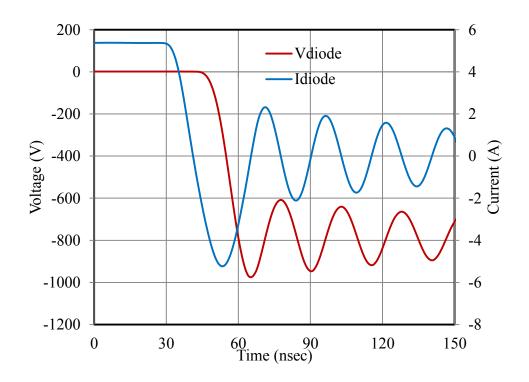

| Figure 7.18:  | Switching waveforms of the SiC MOSFET during turn-on 189       |

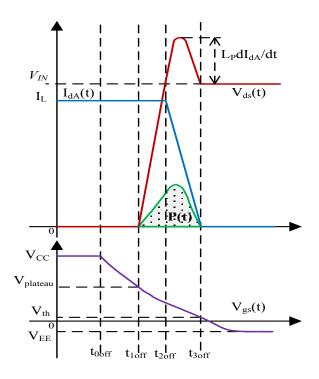

| Figure 7.19:  | Switching waveforms of the SiC MOSFET during turn-off192       |

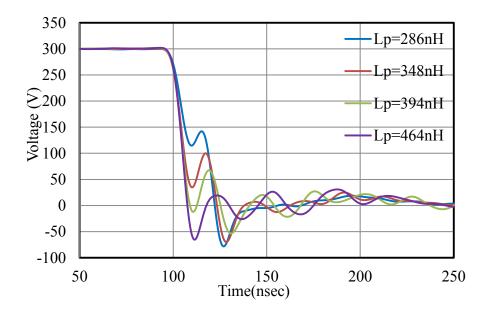

| Figure 7.20:  | Experimental turn-on voltage switching waveform of SiC         |

|               | MOSFET at 300V and 12A for various values of parasitic         |

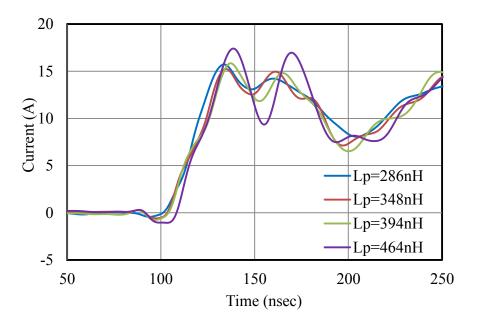

|               | inductance                                                     |

| Figure 7.21:  | Experimental turn-on current switching waveforms of SiC        |

|               | MOSFET at 300V and 12A for various values of parasitic         |

|               | inductance                                                     |

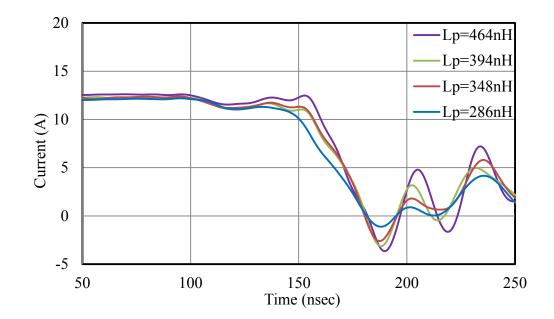

| Figure 7.22:  | Experimental turn-off voltage switching waveform of the SiC    |

|               | MOSFET at 300V and 12A for various values of parasitic         |

|               | inductance                                                     |

| Figure 7.23:  | Experimental turn-off current switching waveforms of the SiC   |

|               | MOSFET at 300V and 12A for various values of parasitic         |

|               | inductance                                                     |

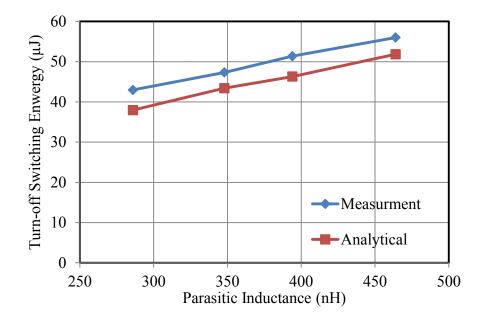

| Figure 7. 24: |                                                                |

|               | MOSFET versus parasitic inductances. Turn-off switching of     |

|               | SiC MOSFET at 300V and 12A                                     |

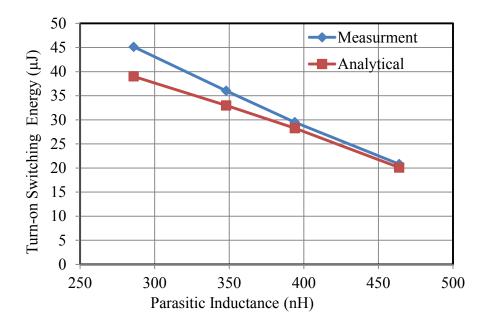

| Figure 7. 25: | Measured and analytical turn-on switching energy of the SiC    |

|               | MOSFET versus parasitic inductances. Turn-on switching of      |

|               | SiC MOSFET at 300V and 12A                                     |

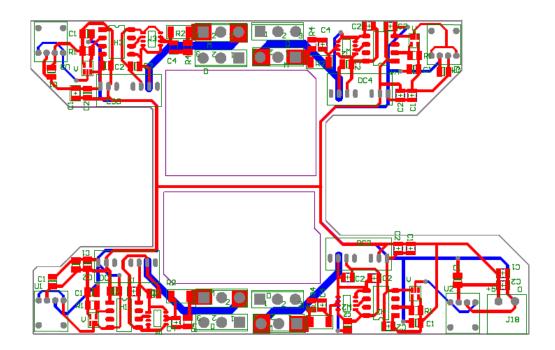

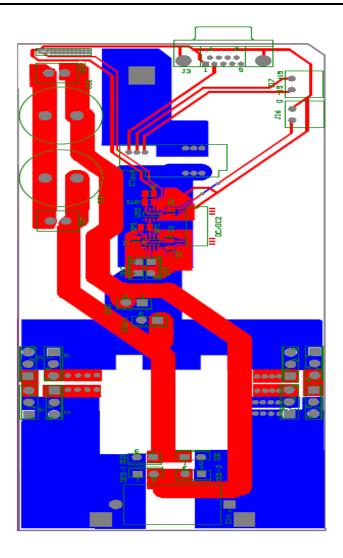

| Figure B.1:   | Drive circuit PCB for the SiC BJT                              |

| Figure B.2:   | Power circuit PCB for the 2-phase to 1-phase matrix converter  |

|               |                                                                |

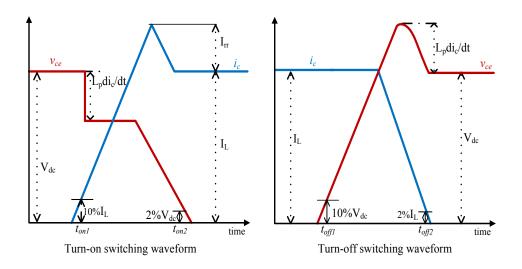

| Figure C.1:   | Simplified switching waveforms of the IGBTs231                 |

| Figure C.2:   | Turn-on switching waveform of the Si IGBT at the temperature   |

|               | of 130°C232                                                    |

| Figure C.3:   | Turn-off switching waveform of the Si IGBT at the temperature  |

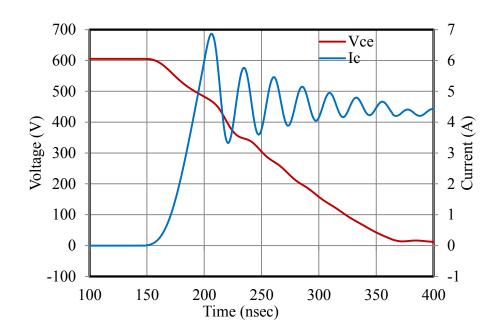

|               | of 130°C235                                                    |

| Figure C.4:   | Turn-on switching waveform of the SiC MOSFET at the            |

|               | temperature of 25°C237                                         |

| Figure C. | 5: Turn- | off switching waveform of the SiC MOSFET at      | the         |

|-----------|----------|--------------------------------------------------|-------------|

|           | temp     | erature of 25°C                                  |             |

| Figure C. | 6: Simpl | lified turn-off switching waveform of the diode. |             |

| Figure C. | 7: Turn- | off switching waveform of the Si diode at a tem  | perature of |

|           | 25°C     |                                                  |             |

| Figure C. | 8: Turn- | off switching waveform of the SiC diode at a ter | mperature   |

|           | of 25    | °C                                               |             |

# **List of Tables**

## Page

| Table | 2.1: | Material properties of Si and 4H and 6H SiC at 25°C10           |

|-------|------|-----------------------------------------------------------------|

| Table | 2.2: | Comparison of the power semiconductor devices commercially      |

|       |      | available                                                       |

| Table | 3.1: | Switching configurations for three-phase matrix converter37     |

| Table | 3.2: | Selection of switching configurations for each combination of   |

|       |      | output voltage and input current sectors40                      |

| Table | 3.3: | Possible commutation scenarios and associated switching types   |

|       |      | in 2-phase to 1-phase matrix converter                          |

| Table | 4.1: | Power devices are used in this work                             |

| Table | 4.2: | The required PCB copper widths for different currents71         |

| Table | 4.3: | The main drive technical specifications of the SiC JFET78       |

| Table | 4.4: | The main drive technical specifications of the SiC BJT80        |

| Table | 5.1: | Different power devices under static and dynamic                |

|       |      | characterizations91                                             |

| Table | 6.1: | The maximum current THD based on the IEEE 519 ( $I_{sc}$ is the |

|       |      | maximum short circuit current at PCC)143                        |

| Table | 6.2: | Scaling factor of inductor volume                               |

| Table | 6.3: | The used components in input filter160                          |

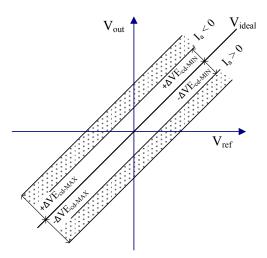

| Table | 7.1: | The voltage error due to commutation time effect introduced by  |

|       |      | matrix converter using four-step current commutation and        |

|       |      | double-side space vector modulation175                          |

| Table | 7.2: | Voltage error due to commutation time effect for different      |

|       |      | switching frequencies and power devices177                      |

| Table | C.1: | Calculated turn-on switching energy from the measurement and    |

|       |      | the obtained turn-on switching energy from the Si IGBT          |

|       |      | datasheet                                                       |

| Table | C.2: | Calculated turn-off switching energies from measurement and     |

|       |      | obtained switching energies from datasheet for the Si IGBT235   |

| Table | C.3: | Calculated turn-on switching energy from the measurement and    |

|       |      | obtained turn-on switching energy from datasheet for the SiC    |

|       |      | MOSFET                                                          |

| Table C.4: | Calculated switching energies from the measurement and the  |     |

|------------|-------------------------------------------------------------|-----|

|            | obtained switching energies from the datasheet for the SiC  |     |

|            | MOSFET                                                      | 238 |

| Table C.5: | Calculated switching energies from the measurement and the  |     |

|            | derived switching energies from datasheet for the Si diode  | 242 |

| Table C.6: | Calculated switching energies from the measurement and the  |     |

|            | derived switching energies from datasheet for the SiC diode | 244 |

### **1.1 Introduction**

Power electronic converters have become widely used in many applications with the rapid development of power semiconductor devices due to improving the converter efficiency and more flexible control of applications. One application of power electronic converters is in motor drives for transportation systems including marine, aviation and vehicle transportation system [1].

Reducing the volume and weight of power converters is an important goal for applications in transportation systems because of the limited space and carrier capability [2]. Additionally, the efficiency of power electronic converters is also important for power density improvement because high efficiency means less cooling which usually increases the power density of power converters. The development of power electronic converters has been closely related to the development of power semiconductor device technologies that capable of handling higher powers [3]. The rapid development of power semiconductor devices in terms of voltage and current rating, improved performance, cost and size has accelerated the utilization of power electronic converters in a variety of electrical applications in industrial, aerospace, utility, communication and transportation systems [3].

Power electronic converters are being developed for more electric aircraft (MEA) applications [4]. The electrical power for the aircraft is provided by generators which are driven by the jet engines of the aircraft. For powering an AC system, the electrical energy which is generated by a variable speed generator is converted to a fixed frequency voltage through an AC/AC power electronic converter [5]. The AC/AC conversion can be achieved by AC/DC/AC converter or direct AC to AC converter such as matrix converter. One of the key benefits claimed for the matrix converter approach is the possibility of greater power density due to the absence of a DC link when compared with a AC/DC/AC converter which is very important for aerospace applications [6, 7].

#### **1.2 Matrix Converter Technology**

AC/AC converter topologies without any energy storage in the intermediate link are referred to as matrix converters. They can provide simultaneous amplitude and frequency transformation of voltage and current [8].

The conventional direct matrix converter performs the power conversion in one stage. Alternatively, the indirect matrix converter topology features a twostage power conversion. In the indirect matrix converter circuit, separate stages are provided for the power conversion similar to the AC/DC/AC converters. However, no energy storage element is implemented in the intermediate link [9]. Regarding their basic functionality, both matrix converter topologies are equivalent. Their different physical implementation only results in different operating characteristics.

Due to the absence of intermediate energy storage, matrix converters are often termed as "all silicon AC/AC converters". However, it should be pointed out that matrix converters require also reactive components for a practical implementation. Those include the input capacitors to provide a voltage impressed input and additional passive components for the input filter to meet the electromagnetic compatibility (EMC) standards [8].

The complexity of the matrix converter topology makes the study and the determination of suitable modulation strategies a complex task. Different modulation techniques were introduced and compared in literature [10-14]. These different modulation strategies give different voltage conversion ratios and the number of commutations employed in each modulation strategy is different with implication on switching losses and waveform quality.

Matrix converter features a lower dependency of their overall semiconductor losses on the switching frequency compared with standard converter concepts [15]. This allows for increased converter efficiency if higher switching frequencies are needed. However, it should be noted that matrix converter also require more semiconductor devices.

The matrix converter topology requires a bidirectional switch capable of blocking voltage and conducting current in both directions [7]. Discrete devices must be used to construct suitable bidirectional cells due to unavailability to date of a discrete semiconductor device that can fulfill this requirement. Different semiconductor technologies have been utilized for the implementing the bidirectional switches of the matrix converters such as the reverse blocking-IGBT technology [16, 17] and the silicon carbide device technology [18-20].

#### **1.3 Research Motivation**

One of the major requirements for aerospace applications which is fulfilled by the matrix converter, is to minimize the volume and weight [2]. It has been stated that an essential component to be minimized is the volume and weight of the passive components in order to maximize the power density of the matrix converter [21]. These passive components are used in the matrix converter to form the input filter. Hence, the part of the minimization of volume and weight of the matrix converter translates into maintaining the input current waveform ripple without increasing the passive components values. One of the approaches to minimize the magnitude of the input current ripple is to increase the switching frequency [22]. Therefore, the increase of power density of the matrix converter is mainly achieved by increasing the switching frequency, enabled by faster and lower loss power semiconductor devices.

Using high switching frequencies and high power devices such as Insulated Gate Bipolar Transistor (IGBT) and Metal Oxide Semiconductor Field Effect Transistor (MOSFET), the power density of power electronics converter has increased since the 1990s [23]. Further improvement is expected in the near future with the implementation of wide band gap semiconductor devices such as Silicon Carbide (SiC) and Gallium Nitride (GaN) because of their even faster switching characteristics which bring benefits in some applications [24].

Among the wide band gap devices, the SiC devices can provide good performance in applications which demand high switching frequencies [25]. SiC devices can also sustain high operating temperatures, thus making them attractive candidates for aerospace applications [26], where the high temperature operation can reduce the weight and volume of the cooling system. Also, the use of SiC devices in applications requiring more than 400V can help in the design of power converters with higher efficiencies due to lower switching losses compared to conventional Silicon (Si) based devices [27].

To fully utilize the SiC power devices and further improve the power density, evaluation of the technology and power converter design approaches should be considered, and this is the basis of this work.

Although the approach for development a high power density power converters seems to be common, the relationship between the overall system performance in terms of efficiency and waveform quality is far from wellunderstood, especially in the extended frequency range offered by different SiC power devices. Furthermore, due to lack of experience and the different

characteristics of the SiC power devices, implementation of SiC power devices in a matrix converter remains a challenge in terms of EMI and lack of suitable capacitance developed for high voltage and high switching. Hence there is a clear need for a systematic performance analysis and design approach for the high power density matrix converter using SiC power devices.

## **1.4 Research Objectives**

The objective of this work is to investigate the impact of SiC power devices on the design and performance of highly energy efficient matrix converters with high power density.

In this process the following aspects are considered:

• Design of suitable gate drive circuits for the different SiC power devices considered.

• Evaluation and characterization of a range of Si (benchmark) and SiC power devices which may be suitable for high switching frequency converters. This characterization includes comparing the driving, conduction and switching losses in matrix converter circuit for each device to enable the formation of a device loss model.

• Design of matrix converter input filter for obtaining minimum volume filters and achieving high power density converter by taking to account power quality standard requirements.

• Matrix converter performance in terms of output waveforms quality and the relationship with the switching frequency and the commutation time.

6

• The influence of parasitic circuit inductance on the SiC power MOSFET' performance in a matrix converter power circuit to highlight the challenges involved in the application of faster switching speed power electronic devices.

### **1.5 Thesis Outline**

The remainder of this thesis is organised as follow:

In chapter 2 the most important power semiconductor devices used in typical motor drives are discussed in terms of their structure and fundamental characteristics.

In chapter 3 the matrix converter concept is introduced and a brief description of the chosen modulation strategy is given. The practical implementation issues of the matrix converter such as bidirectional switch structure, current commutation, input filter and need for a clamp circuit are explained. Simulation results of a matrix converter system for different switching frequencies are also presented.

In chapter 4 the design and implementation of a 2-phase to 1-phase matrix converter using different Si and SiC power devices is described. These circuits are used for measurement of switching phenomena and practically evaluating performance of the devices.

In chapter 5 the conduction and switching performance of a range of Si and SiC power devices are evaluated. The analytical power loss modelling of the matrix converter is presented and the impact of the switching frequency and

temperature on the matrix converter power loss is evaluated for a range of operating points.

In chapter 6 the design of the input filter is described in order to obtain minimum volume filters by taking into account the power quality standard requirements. Then the influence of the switching frequency on the input filter volume of the matrix converter is evaluated by considering converter power loss.

In chapter 7 the matrix converter performance in terms of output voltage and current in relation to the switching frequency and the commutation time is presented to highlight the effect of the commutation time limitations in high switching frequency matrix converters. Furthermore, analytical and experimental investigations into the influence of parasitic circuit inductance on the performance of SiC power MOSFETs in matrix converters are presented.

In chapter 8 the thesis conclusion and an outlook for possible future work are presented.

There has been a surge of interest in the development of power semiconductor devices to meet the demands of compact and more efficient power converters in recent years. The power devices should have low on-state voltage drop and on-state resistance to reduce the conduction losses. They also should be capable to conduct high current and to block high voltage. They should have low switching losses. Additionally, to ensure long term reliability, to enable safe transient device overloading and be insensitive to high irradiation levels the semiconductor material should have minimal degradation effects and withstand elevated temperature levels.

The advancement of semiconductor switching devices is a key driving force for the development of power electronic technology. Therefore, significant efforts have been undertaken in the research and further development of

existing and new power semiconductor technologies such as the SiC technology for the past decades. In this Chapter, the potential benefits of SiC semiconductor materials compared with the Si material are summarized. Then an overview of adequate Si and SiC power semiconductor devices for low voltage power converters that are commercially available or close to commercialization have been expressed.

## 2.1 Silicon and Silicon Carbide

Recently, Si and SiC are two main semiconductor materials that are used to fabricate power semiconductor devices. There are various silicon carbide structures such as 3C-SiC, 4H-SiC and 6H-SiC [28], but only the last two structures are used in commercial devices and will be considered in this study. Some properties of Si and different structures of SiC are summarized in Table 2.1.

| Property                                             | Unit     | Si                   | 4H-SiC             | 6H-SiC               |

|------------------------------------------------------|----------|----------------------|--------------------|----------------------|

| Band Gap Energy E <sub>G</sub>                       | eV       | 1.12                 | 3.26               | 3.02                 |

| Critical Electric Field $U_{crit} \approx E_{BD}$    | MV/cm    | 0.3                  | 2.8                | 2.5                  |

| Intrinsic Carrier Concentration n <sub>i</sub>       | $1/cm^3$ | 1.4×10 <sup>10</sup> | 5×10 <sup>-9</sup> | 1.6×10 <sup>-6</sup> |

| Saturation Carrier Drift Velocity v <sub>sat,n</sub> | cm/s     | 1×10 <sup>7</sup>    | 2×10 <sup>7</sup>  | 2×10 <sup>7</sup>    |

| Thermal Conductivity $\lambda_{th}$                  | W/(Kcm)  | 1.5                  | 3.9                | 4.9                  |

Table 2.1: Material properties of Si and 4H and 6H SiC at 25°C [28-30]

It can be noted from Table 2.1 that the largest differences between 4H-SiC and Si are the high critical electric field and the low intrinsic carrier density

which enable the implementation of power devices with high blocking voltage and small on-state resistance [31]. Additionally, a higher saturation carrier drift velocity allows for higher operating frequencies suitable for high switching frequency applications. The SiC also has superior thermal conductivity compared with Si which making the SiC power device attractive for operation at high temperatures. Therefore, SiC features excellent material properties for the implementation of high voltage, high switching frequency and high temperature power semiconductor devices. Among various structures of SiC materials, 4H-SiC is the preferred material due to its two times higher electron mobility ( $\mu_n$ ) compared with 6H-SiC [32].

#### 2.2 Suitable Devices for AC/AC Converters

Power semiconductor devices for an industrial, three-phase, low voltage AC/AC converter for drive application with nominal input voltage of 400V (rms) needs to have a blocking voltage capability of 1200V.

Due to band gap energy and critical electric field of Si, unipolar Si power switches have beneficial properties compared to bipolar devices for blocking voltage of up to 600V [33]. As the appropriate blocking voltage cannot be provided by Si high voltage MOSFETs, therefore they are not used for motor drive converters and bipolar devices are utilized primarily which have a blocking voltage capability of 1200 V. For this reason, Si IGBTs and Si PiN freewheeling diodes are mainly used in implementing state of the art low voltage motor drive converter systems. Also recently the Si PiN diode has been replaced by a SiC Schottky Barrier Diode (SBD) which provides a hybrid configuration of a Si transistor and a SiC freewheeling diode [34]. This

combination would generally allow for significantly reducing the dynamic losses in the power devices, particularly the turn on loss of the IGBT and the turn off loss of the diode.

To assess the potential of SiC semiconductor devices and performance of SiC AC/AC converter systems, a range of Si and SiC devices are considered in this work. In the following sections a details regarding the structure and operation of the most important Si and SiC power semiconductor devices will be presented. Also the reliable operation requirements of them are identified.

#### 2.3 Si IGBT

IGBT is a monolithic combination of power Bipolar Junction Transistor (BJT) and MOSFET. It provides attractive characteristics of high input impedance of the voltage controlled MOSFET as well as low forward voltage drop at high current densities. There are different kinds of IGBTs in terms of semiconductor structure, properties and processing technology. The two traditional IGBTs are Punch-Through (PT) and Non-Punch-Through (NPT). The PT IGBT has lower on-state voltage drop and turn-off time than the NPT IGBT, whereas the NPT IGBT has higher blocking voltage and is less sensitive to temperature variations [35].

There is an IGBT based device with extended reverse blocking functionality which is named Reverse Blocking IGBT (RB-IGBT). The forward and reverse voltages can be blocked by the RB-IGBT and hence allows replacement of a serial connection of an IGBT and a diode with a single chip. It has been used where bidirectional or reverse blocking power switches are needed such as current source converter or matrix converter [36].

Trench and Field-Stop (T&FS) is one of the main technological trends which provides further development in fabrication of IGBT devices [37]. The structure of T&FS IGBT which is mainly used by the manufacturer Infineon is shown in Figure 2.1. In the structure of T&FS IGBT, an N<sup>+</sup> buffer layer has been added below the N<sup>-</sup> substrate as a field stop layer in comparison with NPT IGBT. Due to the narrow N<sup>-</sup> layer, lower on-state resistance and switching losses can be achieved compared to an NPT IGBT. T&FS IGBT has lower saturation voltage and chip area due to combining a deep trench gate with back side emitter [38, 39].

Figure 2.1: Schematic structure of T&FS IGBT [23]

## 2.4 SiC Diode

The advantages of SiC have accelerated the commercialization of SiC Junction Barrier Schottky (JBS) diodes with blocking voltages over 600 V by Infineon and Cree, which feature ultra-fast turn-on speed and almost zero reverse recovery effect compared to regular Si PiN diodes [40, 41]. The SiC JBS diode is a result of combining the properties of the PiN diode and Schottky diodes. The JBS diode is a Schottky diode with an integrated P<sup>+</sup>-N junction grid into the drift region [42]. The structure of the SiC JBS diode is presented in Figure 2.2 which is mainly used by Cree.

Figure 2.2: Schematic structure of JBS SiC diode [26]

## 2.5 SiC Power MOSFET

MOSFET switches are present nowadays in the majority of power conversion applications. Such popularity against other devices has been mainly justified by the simple and low loss driving requirements along with robust and reliable operation. Regarding the Si based technologies; MOSFETs are normally applied below 600V due to the very large chip resistance at higher voltage levels [34].

The use of SiC material allows a significant extension of the blocking voltage range, due to reduction of the specific chip resistance. For instance, devices rated at 10kV have similar values of specific chip resistance as their 600V Si based counterparts [43].

## 2.5.1 Device Structure and Properties of SiC Power MOSFET

Vertical Depletion MOSFET (DMOSFET) is one of the main structures which provide further development in fabrication of SiC MOSFET device. The SiC DMOSFET structure which is mainly used by the manufacturer Cree is illustrated in Figure 2.3 [44]. It is a vertically structured device that can block very high voltages and conduct very large currents.

Figure 2.3: Schematic structure of SiC DMOSFET [28]

The direction of electron flow during forward operation is from the source via the inverted P-well and within the Junction Field Effect Transistor (JFET) region laterally and then within the drift layer and out via the drain contact vertically. On the other hand, when the gate of SiC MOSFET is turned on while the drain voltage polarity is negative with respect to the source, the reverse current conduction is possible. The direction of electron flow during reverse conduction is from drain to source through the same path as explained for forward conduction [45]. Reverse conduction property becomes interesting when considering synchronous rectification is needed in applications. The current will then be shared between the MOSFET structure and through the intrinsic diode, which cause reduction in the total loss.

The P-N junction of the P-well and the N<sup>-</sup> drift layer in SiC DMOSFET structure form an intrinsic body diode. It is forward biased and conducts current when the drain voltage polarity with respect to the source is negative. The on-state voltage drop of intrinsic PiN diode is around 2.5 to 2.7V. Due to such high voltage drop, an antiparallel Schottky can be used in order to attain optimal switching performance. Caution needs to be taken at higher temperatures and higher current values, when the intrinsic diode may enter in conduction before the external Schottky diode [46]. However in comparison with Si MOSFET, the reverse recovery characteristics for the body diode in a SiC MOSFET is negligible, which is comparable to the SiC diode [47].

In general, the total resistance of a MOSFET is the summation of the individual values from the channel, JFET region and drift region. While, in silicon designs, the drift region becomes dominant at higher voltage levels, the same is not valid for SiC devices due to the thinner width and higher doping concentrations [48].

Regarding the temperature dependence, the channel resistance displays a negative coefficient, while the other two components have a positive coefficient. Therefore, in the SiC MOSFET a lower temperature dependence of the total device resistance can be observed [33].

SiC MOSFETs display a significantly less clear threshold limit and saturation regions in contrast with their Si based counterparts [49]. As a consequence, the device resistance can strongly be affected by the gate voltage. SiC MOSFETs are characterized by an output capacitance density approximately ten times higher than Si devices, due to the very thin drift region and higher doping concentrations. Such characteristic affects the turn on under hard switching conditions, as the output capacitance needs to be discharge through the MOSFET channel. The channel current density may reach very high values in case of high values of dv/dt [50]. The input capacitance is also larger due to the tight cell geometry for achieving higher channel density [51].

#### 2.5.2 Operation and Driving of SiC MOSFET

Control of the SiC MOSFET is the same as the one valid for Si MOSFET. The difference is that the plateau on the gate voltage cannot be completely observed in some SiC MOSFET designs [52]. An important consequence of the low transconductance and threshold voltage of SiC MOSFETs is that these devices may be more susceptible to gate ringing effect [52]. Due to importance of the modest transconductance and short channel effects in SiC MOSFET, it is needed to be driven with higher gate voltage swing in comparison with Si IGBT [52].

### 2.6 SiC JFET

In fact of the referred challenges from the SiC MOSFET, JFETs have regained significant attention due to their simple and robust structure. In contrast with the MOSFET, the JFET is not controlled by an insulated gate structure but rather by a reverse biased PN junction. Hence the structure presents no interface problems related to gate oxide, increasing the reliability and ruggedness since no aging or parameter drift may be observed, making the device attractive for operation at high temperatures [53]. Additionally punchthrough of the gate junction happens only at higher voltages in comparison with Si devices due to the wider band gap of SiC giving a broader gate voltage range capability [53]. Another feature is that most JFET devices have a symmetric channel structure, enabling operation as a synchronous rectifier in the reverse direction. This enables an additional reduction on the conduction losses during freewheeling [54].

#### **2.6.1** Device Structure and Properties of SiC JFET

Two main constructive approaches can be identified for JFETs that are named the vertical and lateral structures [55]. In comparison with the lateral channel devices, the vertical approach have simple fabrication steps and also attains lower chip resistance [55]. The enhanced mode vertical JFETs structure, which is shown in Figure 2.4, is used by the manufacturer Semisouth. In this structure, the channel is formed between the two P-layers from the buried gate structures. The intrinsic PN-diode in such structure is connected from the gate to drain and source terminals. Moreover, the Miller capacitance which is defined as the gate to drain capacitance of the device is considerably high in such structure due to the large gate region overlapping the drain contact. By means of special doping profile and tight cell pitch design it is possible to obtain depletion of the channel at  $V_{gs}$  equal to 0V, leading to a normally-off operation [56, 57]. A certain temperature dependence of the threshold voltage is possible to be observed in the presented structure [55]. Meanwhile a high value of transconductance is necessary in order to attain the nominal current capability before reaching the built-in voltage of the gate source diode [56].

Figure 2.4: Schematic structure of SiC enhanced-mode vertical JFET [38]

### 2.6.2 **Operation and Driving of SiC JFETs**

By considering the basic JFET structure, the most significant drawback of it is the normally-on behaviour, as the channel will block only with continuous negative gate voltage leading to the formation of the depletion region. Due to the normally-on behaviour represents an inherent reliability problem for most circuits, especial gate driving circuits and supply strategies were proposed in the literature but still end up increasing the costs and complexity [18, 58-64]. Another possibility to solve this issue is the use of cascode structures that are nowadays seen as the most promising alternative for the referred problem [65]. In this configuration a low voltage Si MOSFET is connected in series with the SiC JFET. The voltage rating of the MOSFET is chosen to be higher than the maximum absolute value of the JFET pinch-off voltage. The driving of the JFET is indirectly performed by the MOSFET [66].

On the other hand, normally-off devices can be obtained by relying on the potential barrier formed by the grounded gate junction ( $V_{gs}$ =0V). In order to obtain such capability, the channel region needs to be very narrow with low doping concentration that results in a higher channel resistance. Another critical issue related to these devices is the reduction of the threshold voltage with increasing temperature values, that leads to the requirement of bipolar gate voltage driving to attain certain immunity against Electromagnetic Interference (EMI) [67].

In normally-off SiC JFET, conduction occurs only when a positive voltage higher than the threshold value is applied across the gate-source terminals. Such level is very low, normally below 1.5V that makes the device especially susceptible to EMI induced voltages [68].

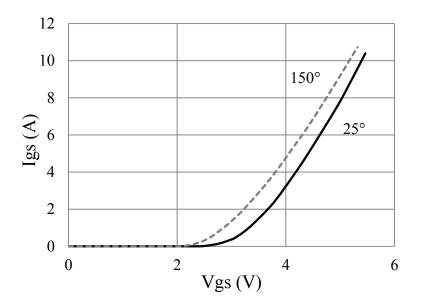

As it is mentioned a especial requirement of normally-off SiC JFET device from Semisouth is that the operation with direct polarization of the gate-source diode is advised by the manufacturer in order to attain the nominal values of forward resistance [69]. Thus a higher value of gate current starts to flow during conduction, as is presented in Figure 2.5 [70]. As it is obvious form Figure 2.5, the temperature dependence is significant and needs to be considered when designing the driver in order to avoid higher losses.

Figure 2.5: Gate-source current of normally-off SiC JFET as a function of gate-source voltage [45]

Therefore, it becomes mandatory to use a driver solution with gate current limitation. [71] proposed a simple drive circuit with bipolar voltage and gate current limiting resistor. The current limiting resistor can be calculated as:

$$R_g = \frac{(V_{cc} - V_{gs})}{I_g \left(@V_{gs}\right)} \tag{2.1}$$

21

where  $V_{cc}$  represents the positive voltage of the driver,  $V_{gs}$  and  $I_g$  are the gate-source voltage drop and gate current value respectively.

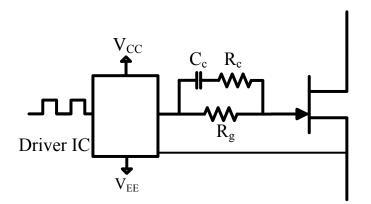

The use of charge pumps is also utilized in a majority of configurations to provide demand peaks on the gate source current, enabling faster charge/discharge of the device parasitic capacitances and thus faster switching speed [53, 58]. The choice of the capacitance value needs to take into consideration not only the desired pump effect but also the inherent charge/discharge dynamic since the capacitor needs to be fully charged before the next transient. If the capacitor charges less than desirable value, it will cause a slight increase in the turn-on losses [72]. Advised is either a value at least 10 times larger than the device Miller capacitance or calculated by the following equation [73]:

$$\frac{2Q_{Miller}}{V_{CC} - V_{EE} - V_{gs}} \le C_c \le \frac{4Q_{Miller}}{V_{CC} - V_{EE} - V_{gs}}$$

(2.2)

Also an additional low resistance in series with the charge pump capacitor allows damping of any observed gate ringing. A simple parallel connection of the pump charge capacitor, damping resistor and gate resistor as gate drive circuit for normally-off SiC JFET is presented in Figure 2.6. In [74] a Schottky diode was also added in parallel with the gate resistor in order to enable fast turn-off.

Figure 2.6: Simplified schematic diagram of the gate drive circuit for normally-off SiC JFET based on the charge pump circuit

### 2.7 SiC BJT

Many years ago, Si BJT was replaced by Si power MOSFETs and IGBTs due to its low current gain and small safe operating area which was caused by the unique second breakdown problem [75]. Indeed, there is almost no significant Si BJT research activity in the past 20 years, but the emergence of SiC as new material for power semiconductor devices has led to consider power BJTs as a possible candidate for high power and high voltage applications. This is due to some advantages of SiC BJTs when compared with other different SiC power devices which are normally-off device, very low specific on-state resistance, positive coefficient of the on-state resistance, fast switching speed, free from any gate oxide. Due to the junction voltage cancellation (base-emitter voltage is equal to base-collector voltage); the device resistance can be mainly summarized by contact/bond resistance plus substrate and collector layer resistances [75]. The SiC BJT as a bipolar device has a behaviour practically identical to a unipolar device at voltage levels around 1kV, due to the outstanding properties of the SiC material [76].

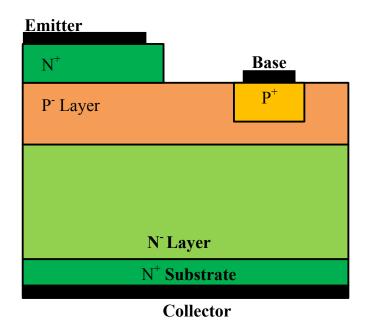

### 2.7.1 Device Structure and Properties of SiC BJT

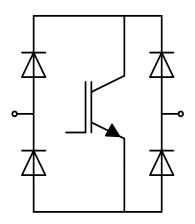

The basic structure of BJT as shown in Figure 2.7 is normally obtained with a complete epitaxial construction [77]. Due to the absence of intrinsic diode function, an external freewheeling diode is necessary.

Figure 2.7: Schematic structure of SiC BJT [53]

The BJT structure itself is known for several decades but the application based on Si was so far limited due to some critical drawbacks like low current gain, poor switching performance, limited safe operation area with possible first and secondary breakdown effects.

Practically all of the referred drawbacks were overcome by use of SiC. The possible reduction of the drift thickness allows lower excess of charges during conduction, thus enabling considerably faster switching behaviour [78]. In comparison with other unipolar structures like MOSFETs, the BJT offers in

### **Chapter 2: Power Semiconductor Devices**

fact the possibility of reaching one of the lowest specific chip resistance values. Due to the voltage cancellation of both junction voltage ( $V_{be,sat}$ = $V_{bc,sat}$ =0.1...0.2V), the most significant components are the resistances of the drift region and emitter/base contacts [76].

The gain obtained with SiC BJTs is more than three times higher than their best Si counterparts and is mainly achievable by optimizations related to constructive aspects [79-82].

The first breakdown is practically non-existent with SiC devices, so the current gain presents a negative thermal coefficient. Meanwhile, the second breakdown is also much less critical with SiC based BJTs, since the superior doping concentration moves the referred phenomenon to much higher current density levels [82].

#### 2.7.2 Operation and Driving of SiC BJT

A vast multitude of driving circuits for Si BJTs can be found in the literature [75, 83]. Although such topologies are also applicable for their Si counterparts in principle, an important difference is the lower required value of base current.

The optimal driving conditions relay on a high peak of the base current at turn-on to minimize the delay and switching. The required peak current,  $I_{bp}$ , depends on the base-collector capacitance,  $C_{bc}$ , and on the expected charging time,  $T_{ch}$ , to charge such capacitor, being calculated by:

$$I_{bp} = \frac{Q_{C_{bc}}}{T_{ch}} \tag{2.3}$$

### **Chapter 2: Power Semiconductor Devices**

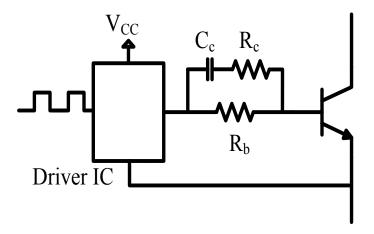

A well-known base drive arrangement that improves the switching transients is based on a charge pump circuit which is illustrated in Figure 2.8 [75]. It is consists of a base resistor and a speed up capacitor in parallel with resistor. The capacitor is charged up to a voltage level equal to the voltage difference between  $V_{CC}$  and  $V_{be(sat)}$  during the turn on transition of SiC BJT and so creating a low impedance path for the base current. In addition, the capacitor provides a negative voltage which applied across the base emitter terminals during the turn off transition of the SiC BJT. This causes improvement in the turn off transient.

Although the presented SiC BJT drive circuit is simple and cost effective, it has some critical drawbacks. The worst of them is that, the injected base current  $I_b$  depends on the value of base-emitter junction voltage  $V_{be}$  as demonstrated in the following equation.

$$I_b = \frac{V_{CC} - V_{be}}{R_b} \tag{2.4}$$