# High Frequency-Link Cycloconverters for Medium Voltage Grid Connection

Nicholas Shattock BEng. (Hons)

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy April 2014

#### Abstract

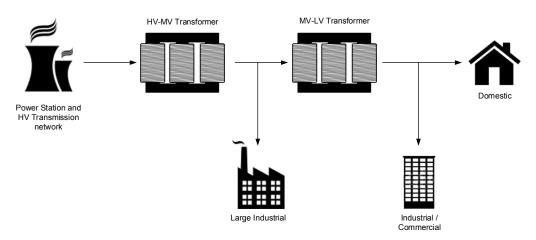

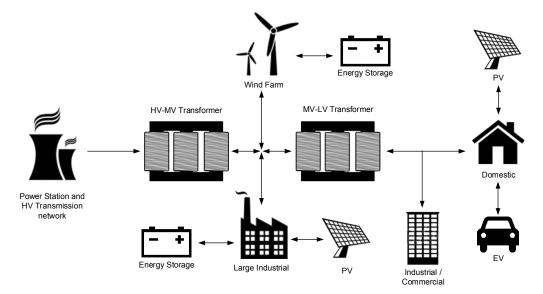

As the deployment of renewable generation increases in the worldwide electrical grids, the development of distributed energy storage becomes more and more of an essential requirement. Energy storage devices connected at Medium Voltage allows for much higher powered deployments and this Ph.D. will focus on the power converter used to interface the energy storage device to the electrical grid.

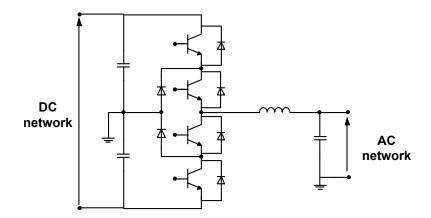

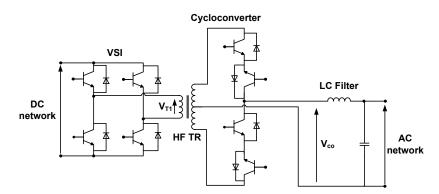

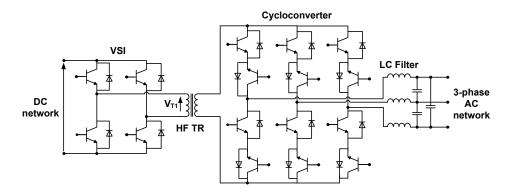

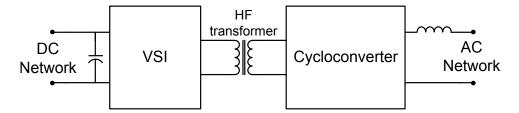

Multi-level converters can be used to provide this interface without huge filtering requirements or the need of a Low Frequency step up transformer. However traditional Multi-level converter topologies require a large number of electrolytic capacitors, reducing the reliability and increasing the cost. Multi-level converters constructed from a Cycloconverter Topology do not require any additional electrolytic capacitors, however the High Frequency transformer, used to provide isolation has to be considerably larger.

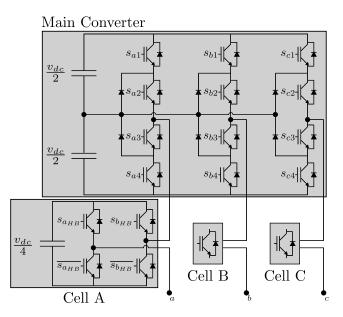

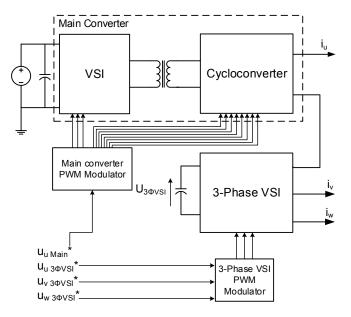

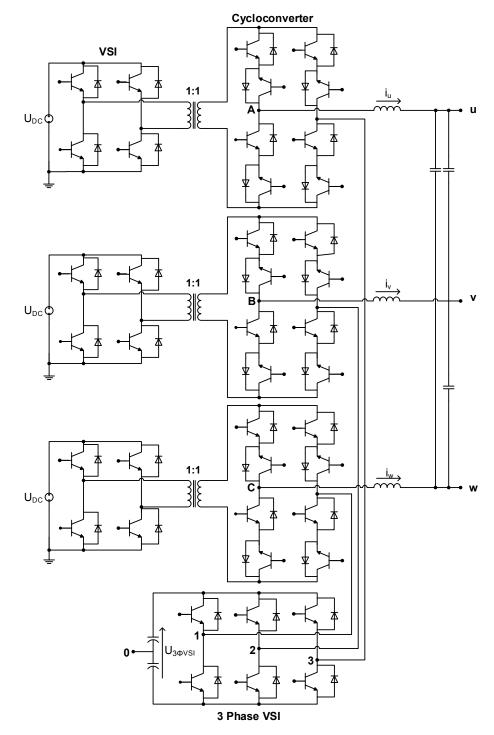

This Ph.D. will investigate a novel hybrid converter topology to provide an interface between an energy storage device, such as a super-capacitor or battery, to the Medium Voltage grid, designed for high reliability and power density. This topology is called The Hybrid Cycloconverter Topology and is based on a Cycloconverter Topology connected to an auxiliary 3-Phase VSI.

A comprehensive simulation study is carried out to investigate the semiconductor losses of this novel converter topology and compared against two alternative topologies. An experimental converter is constructed to validate the theory of operation and to justify its effectiveness.

ii

### Acknowledgments

I would like to thank Professor Greg Asher for his patient support throughout the extended writing up process and Dr Christian Klumpner for inspiring me and for his technical knowledge and advice.

Thanks to the PEMC group at the University of Nottingham for providing a pleasant environment to work in. I would especially like to thank Dr Mohammed Rashied, Dr Alan Watson and Lee Empringham for their advice and assistance throughout my research.

I would also like to thank my peers Jack Bottomley, James Foster and Garry Buckley for their help with getting the  $L^{AT}EX$  document class just right.

I would like to thank my family and particularly my mum Belinda for giving me the encouragement, freedom and self belief that made me who I am today.

And lastly thanks to Larissa and my friends for for all of their support and love that kept me same throughout these times.

iv

# Contents

| 1        | Intr | oducti                                                            | ion                                                                    |  |  |  |  |  |  |

|----------|------|-------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|--|

|          | 1.1  | 1 Existing Solutions to Interface an Energy Storage Device to the |                                                                        |  |  |  |  |  |  |

|          |      |                                                                   | rid                                                                    |  |  |  |  |  |  |

|          | 1.2  |                                                                   | tives of the Research Project                                          |  |  |  |  |  |  |

|          | 1.3  | Thesis                                                            | Structure and Content                                                  |  |  |  |  |  |  |

| <b>2</b> | Ove  | erview                                                            | of Medium Voltage Converter Technology 12                              |  |  |  |  |  |  |

|          | 2.1  | Series                                                            | Connected Multilevel Converters                                        |  |  |  |  |  |  |

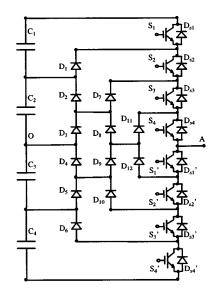

|          |      | 2.1.1                                                             | The Diode-Clamped Inverter                                             |  |  |  |  |  |  |

|          |      | 2.1.2                                                             | The Flying-Capacitor Inverter                                          |  |  |  |  |  |  |

|          | 2.2  | Casca                                                             | ded Multicell Converters                                               |  |  |  |  |  |  |

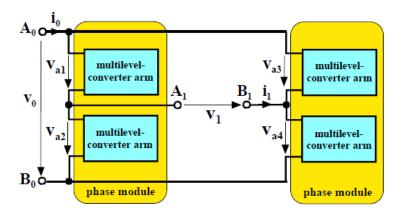

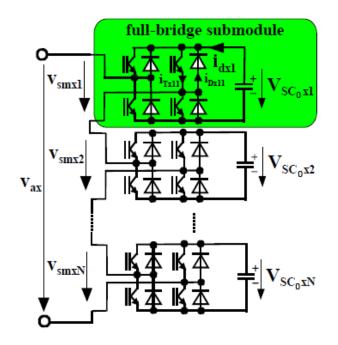

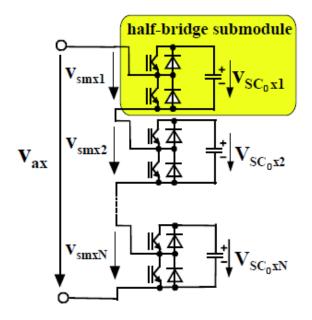

|          |      | 2.2.1                                                             | Modular Multi-Level Converter                                          |  |  |  |  |  |  |

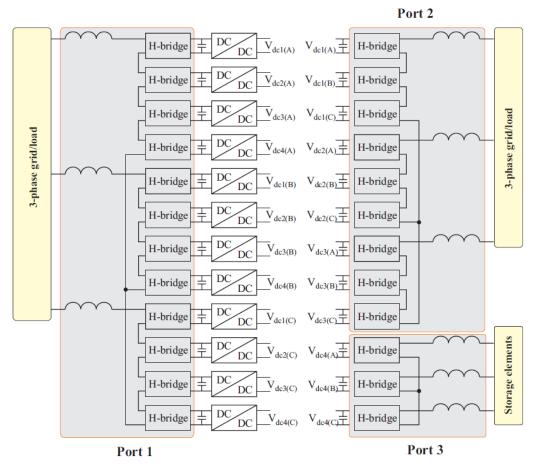

|          |      | 2.2.2                                                             | Modular Cascaded H-Bridge Converter                                    |  |  |  |  |  |  |

|          | 2.3  | Multil                                                            | evel Cycloconverter Topologies                                         |  |  |  |  |  |  |

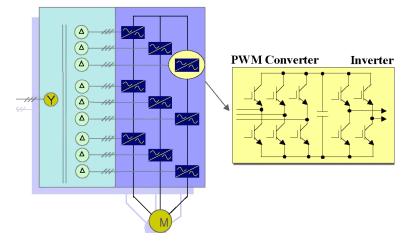

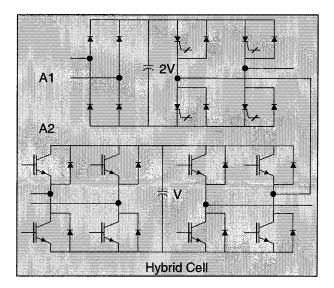

|          | 2.4  |                                                                   | d Converter Topologies                                                 |  |  |  |  |  |  |

|          | 2.5  |                                                                   | ary                                                                    |  |  |  |  |  |  |

| จ        | 0    |                                                                   |                                                                        |  |  |  |  |  |  |

| 3        |      |                                                                   | of Topologies 33                                                       |  |  |  |  |  |  |

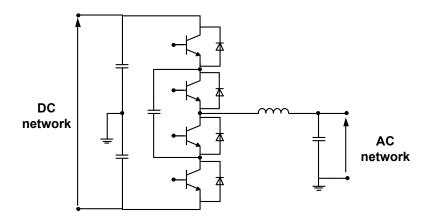

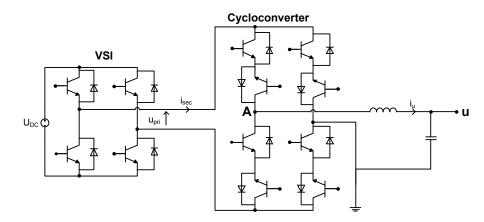

|          | 3.1  |                                                                   | VSI Topology                                                           |  |  |  |  |  |  |

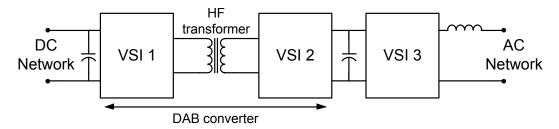

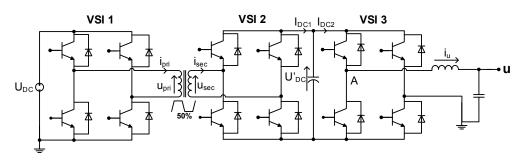

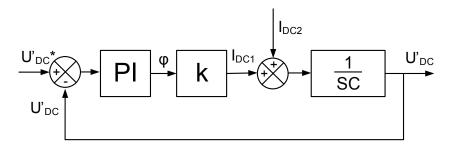

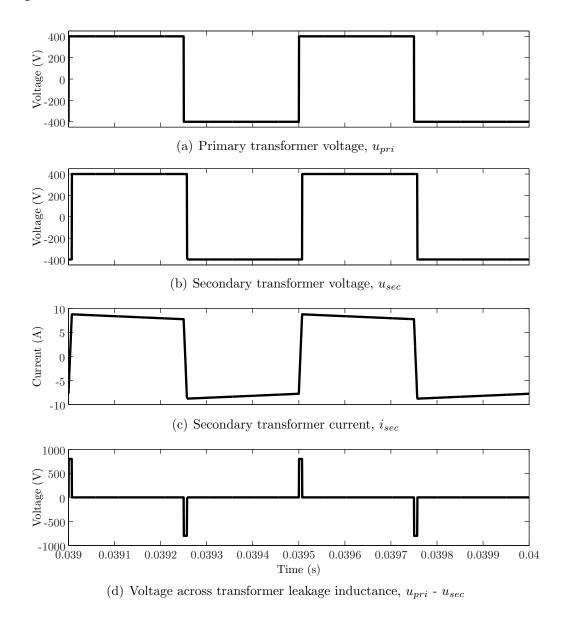

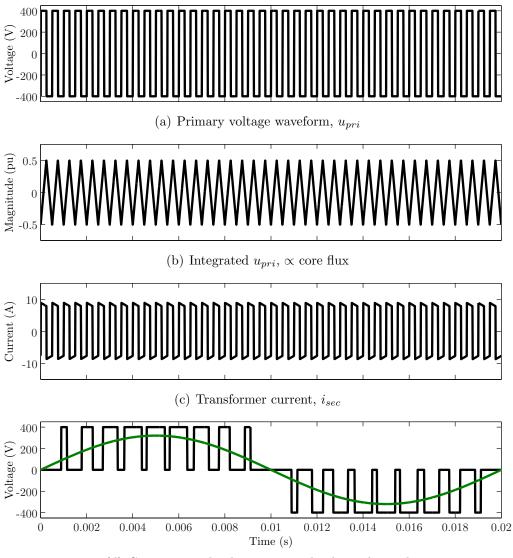

|          |      | 3.1.1                                                             | The Dual Active Bridge Converter                                       |  |  |  |  |  |  |

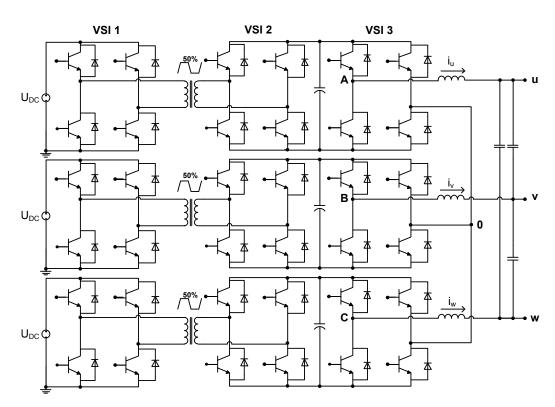

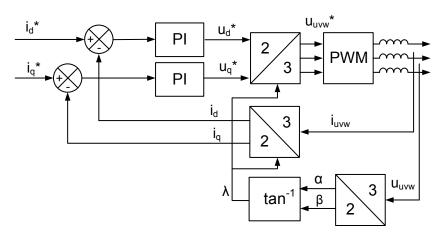

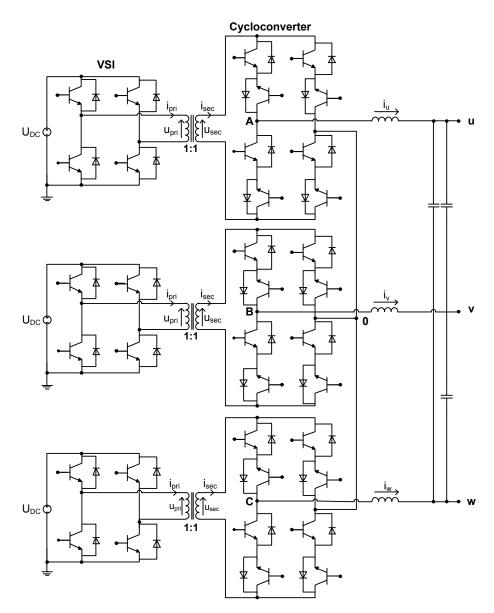

|          | 2.0  | 3.1.2                                                             | 3-Phase Triple VSI Converter Operation                                 |  |  |  |  |  |  |

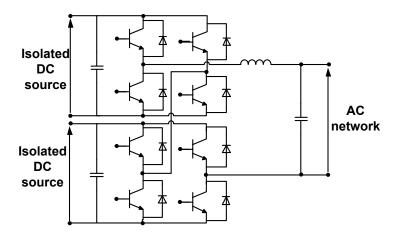

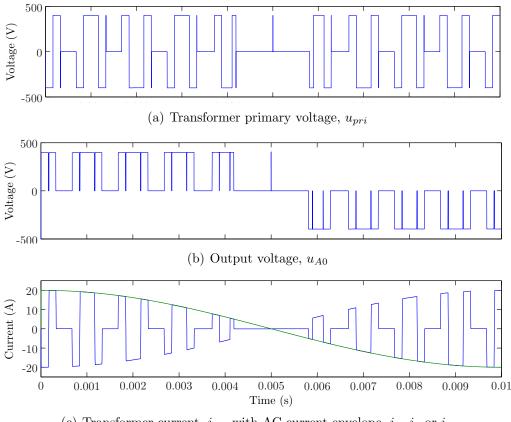

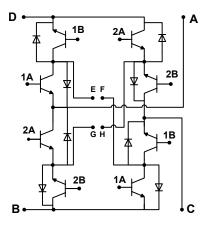

|          | 3.2  | -                                                                 | converter Topology                                                     |  |  |  |  |  |  |

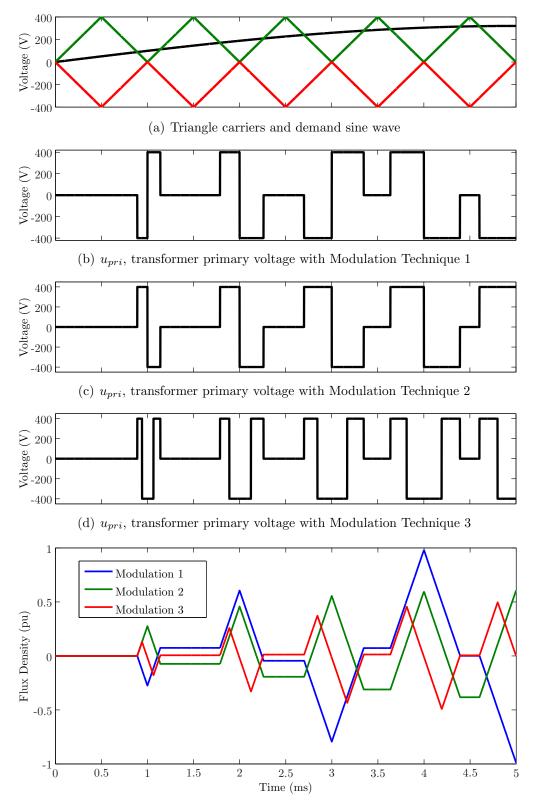

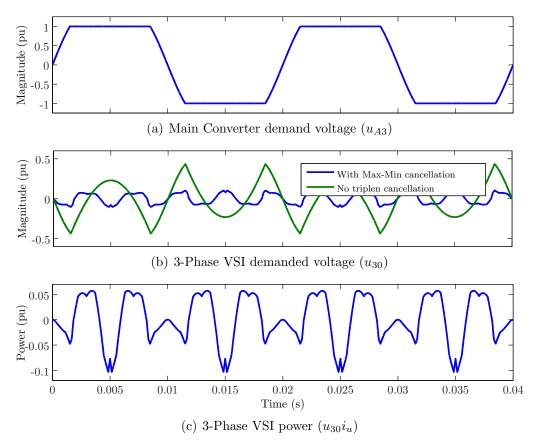

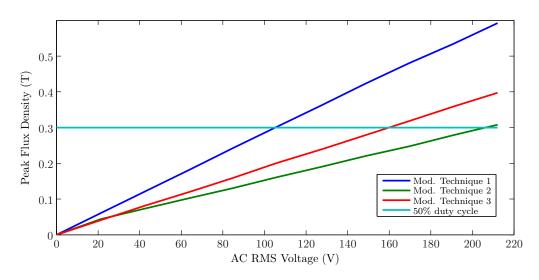

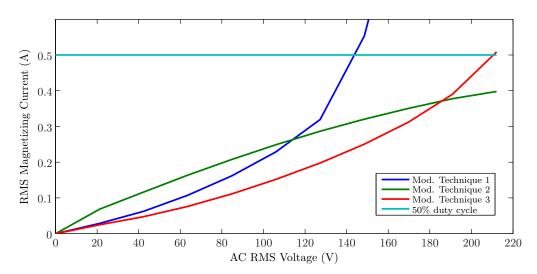

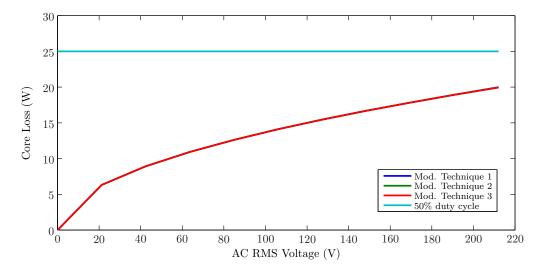

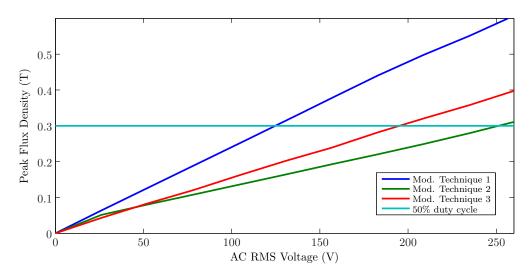

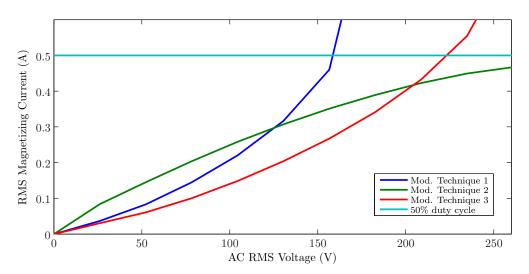

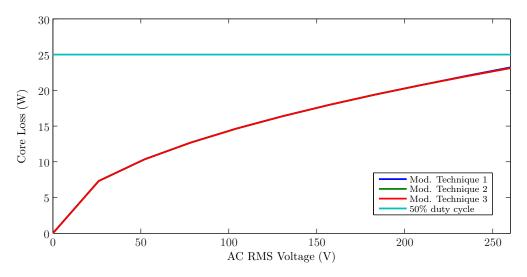

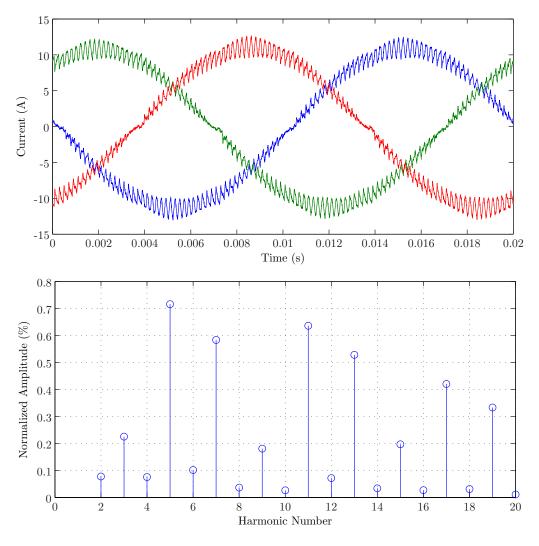

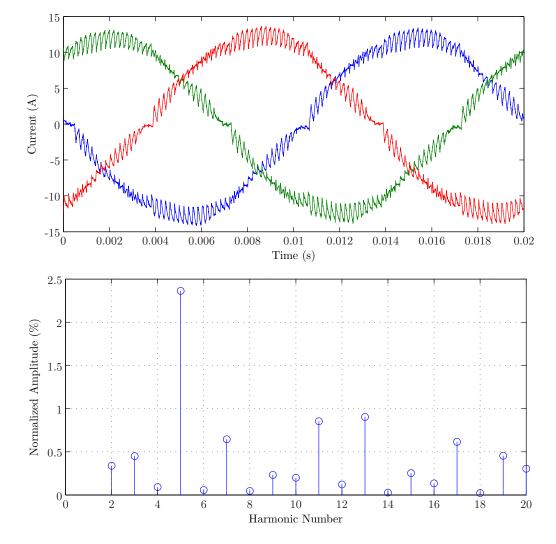

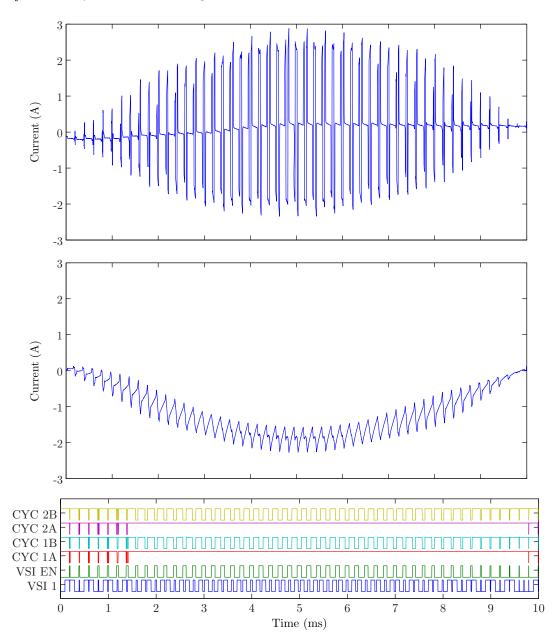

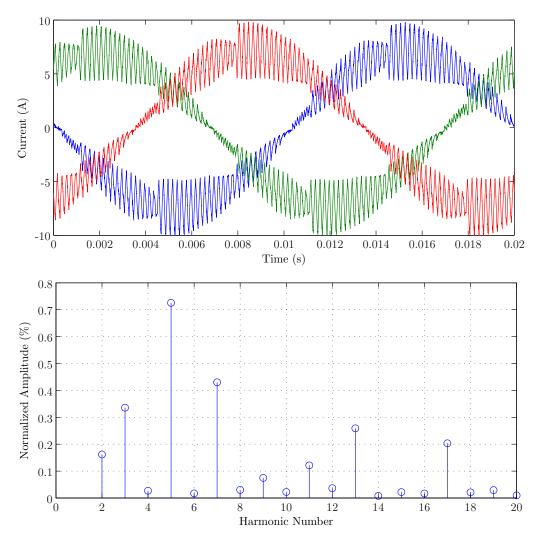

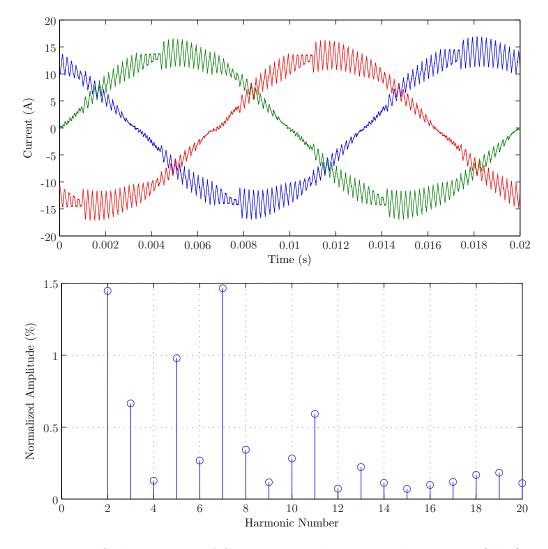

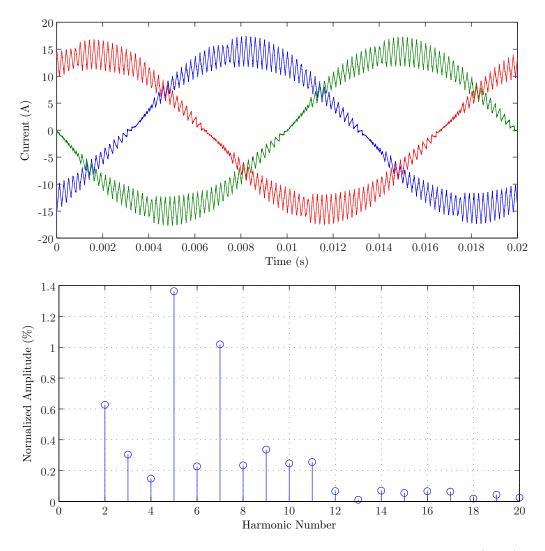

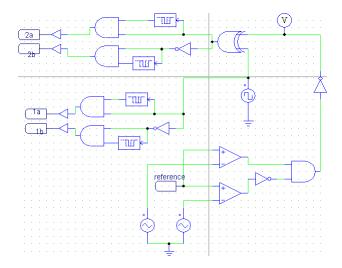

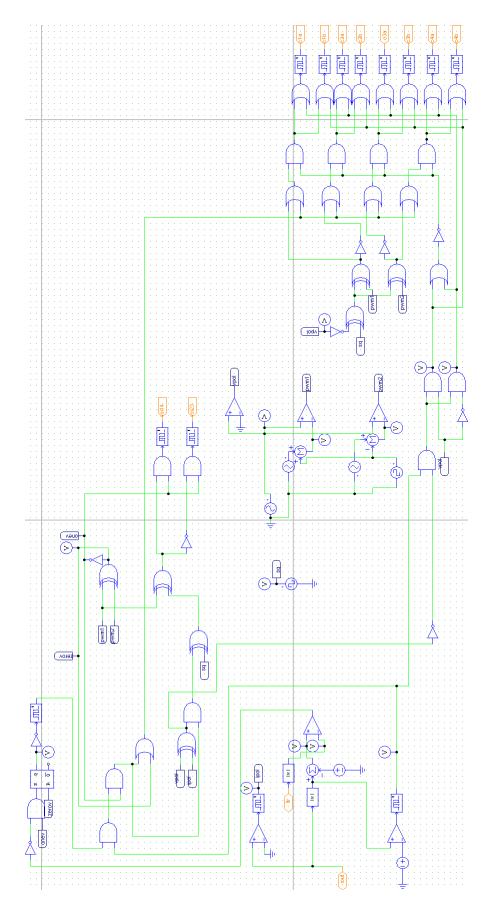

|          |      | 3.2.1                                                             | Switching Strategies for Cycloconverter Topology 40                    |  |  |  |  |  |  |

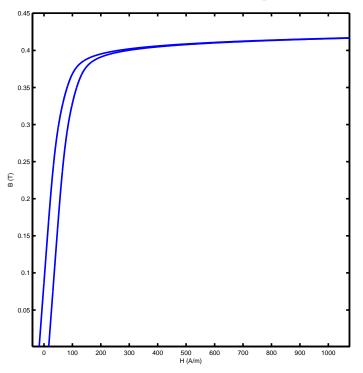

|          | 0.0  | 3.2.2                                                             | Transformer Design Considerations                                      |  |  |  |  |  |  |

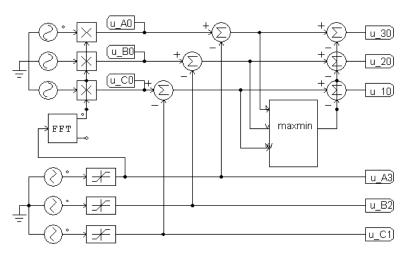

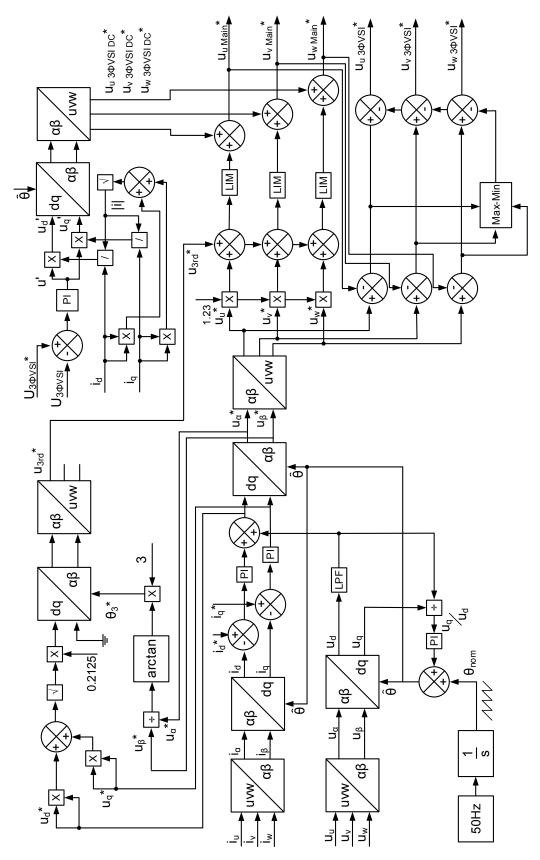

|          | 3.3  |                                                                   | Lybrid Cycloconverter Topology                                         |  |  |  |  |  |  |

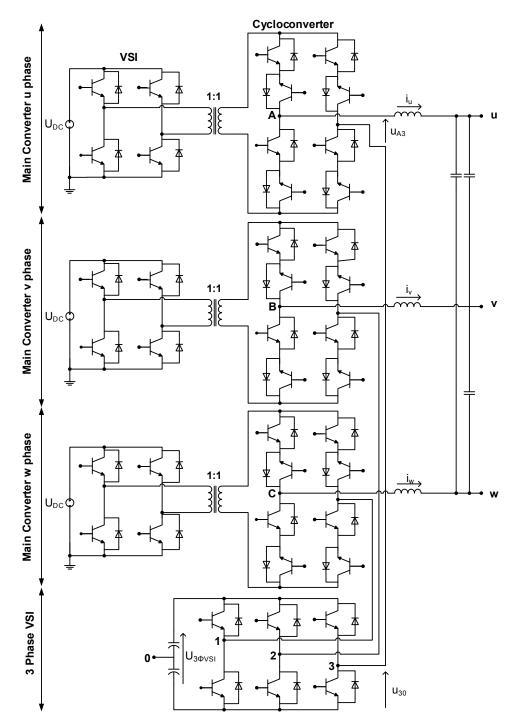

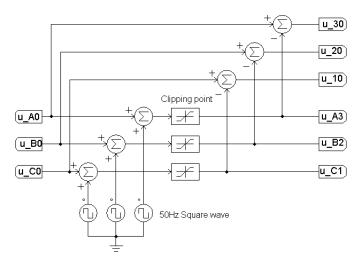

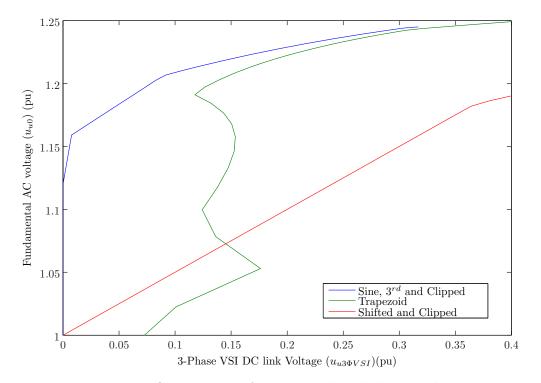

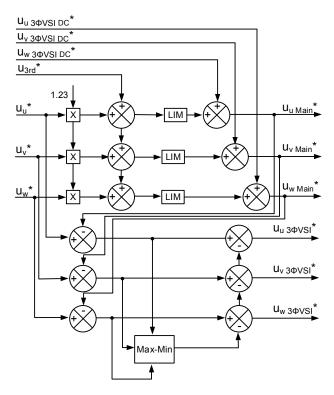

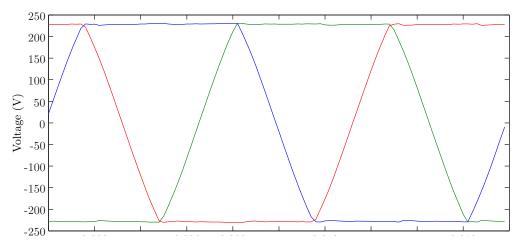

|          |      | 3.3.1                                                             | Voltage Distribution Scheme 1: the Shifted and Clipped                 |  |  |  |  |  |  |

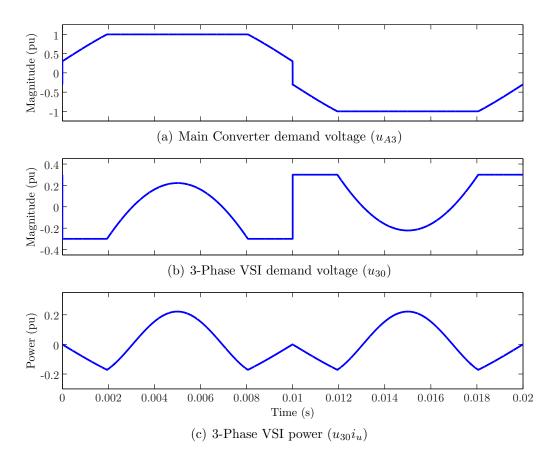

|          |      | 0.0.0                                                             | Waveform Shape 55                                                      |  |  |  |  |  |  |

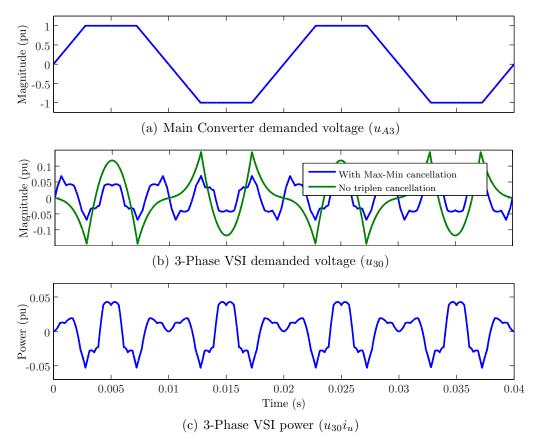

|          |      | 3.3.2                                                             | Voltage Distribution Scheme 2: the Trapezoidal Waveform                |  |  |  |  |  |  |

|          |      | 0.0.0                                                             | Shape                                                                  |  |  |  |  |  |  |

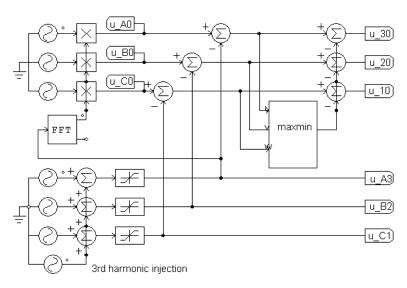

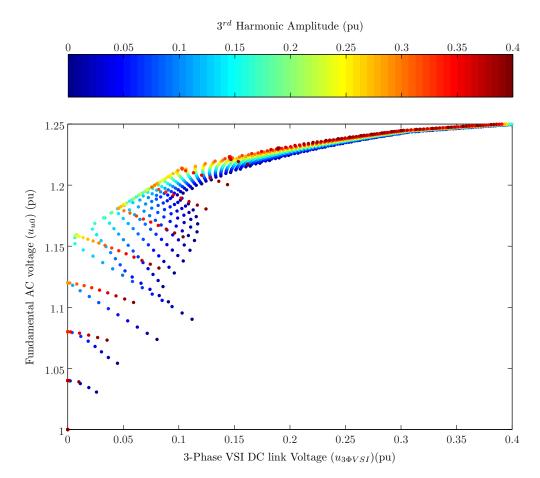

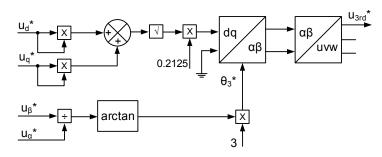

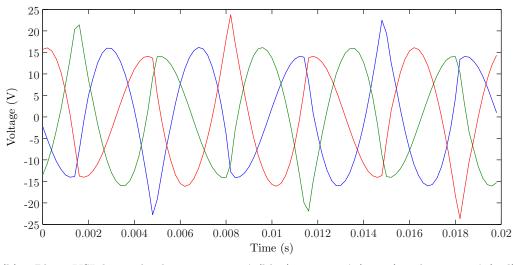

|          |      | 3.3.3                                                             | Voltage Distribution Scheme 3: Sine, 3 <sup>rd</sup> and Clipped Wave- |  |  |  |  |  |  |

|          |      | 0 0 <i>(</i>                                                      | form Shape                                                             |  |  |  |  |  |  |

|          |      | 3.3.4                                                             | Comparison of Proposed Voltage Distribution                            |  |  |  |  |  |  |

|          |      |                                                                   | Schemes on Hybrid Cycloconverter Topology                              |  |  |  |  |  |  |

|          |      |                                                                   | Performance, Based on Average Model Simulations 60                     |  |  |  |  |  |  |

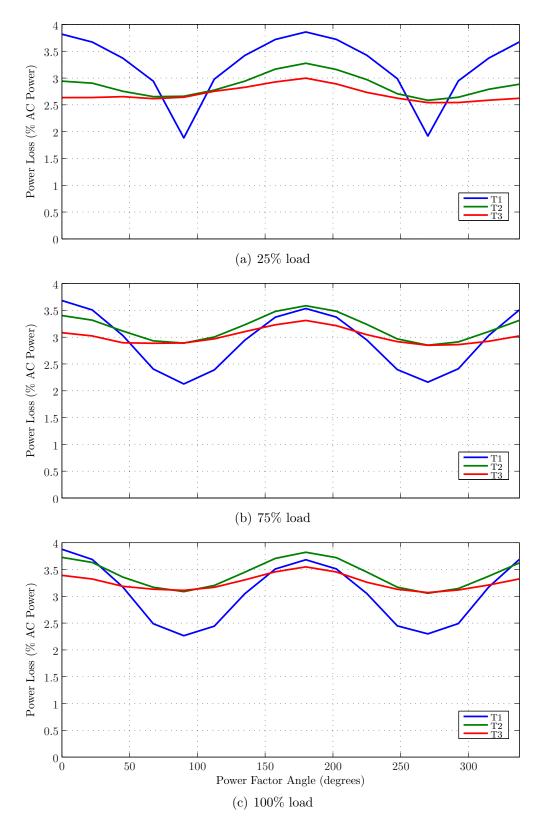

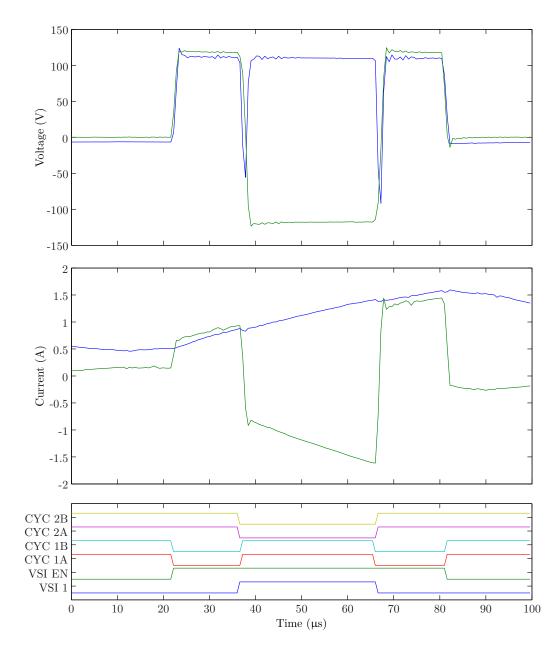

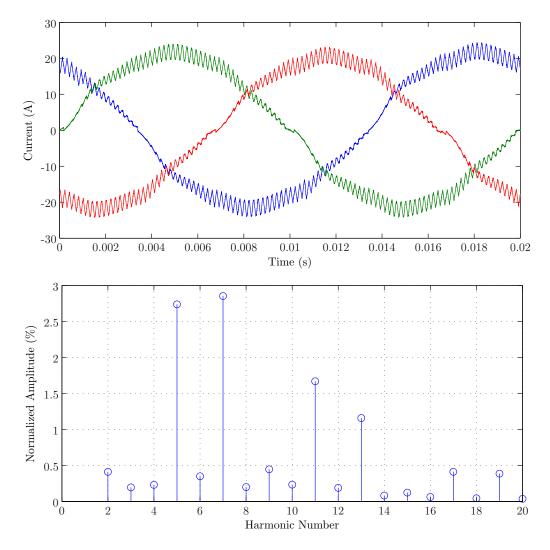

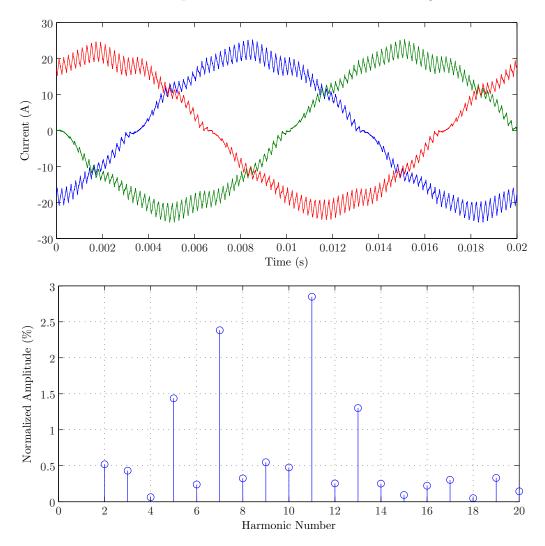

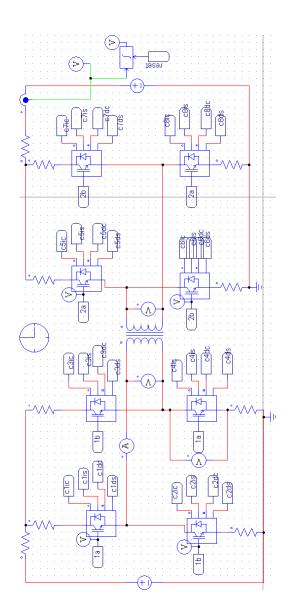

|          | 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Comparison of Topology Performance Based on Switching Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60<br>68                                                                                                                                                                                                      |

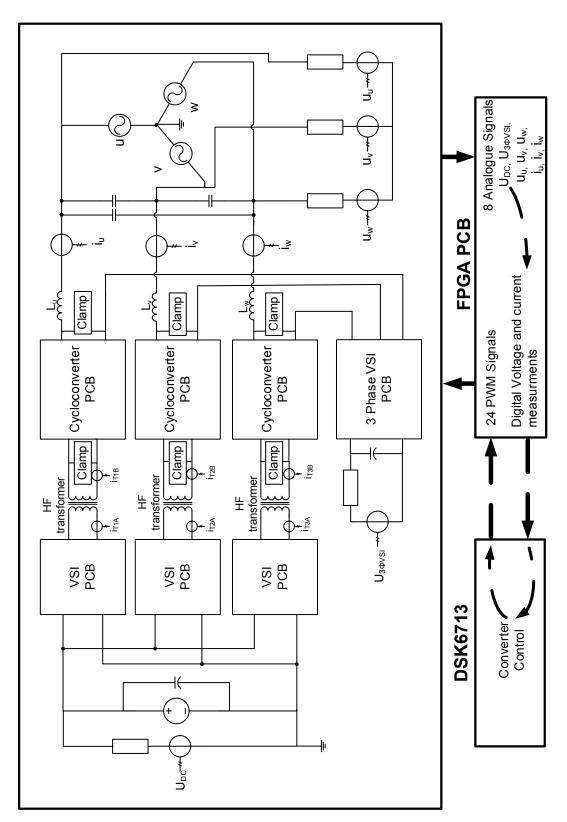

| 4        | Cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nverter Losses for the Cycloconverter Topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71                                                                                                                                                                                                            |

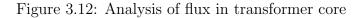

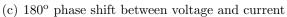

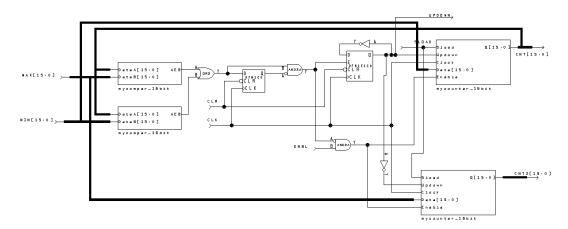

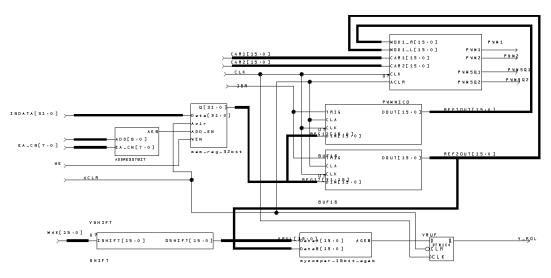

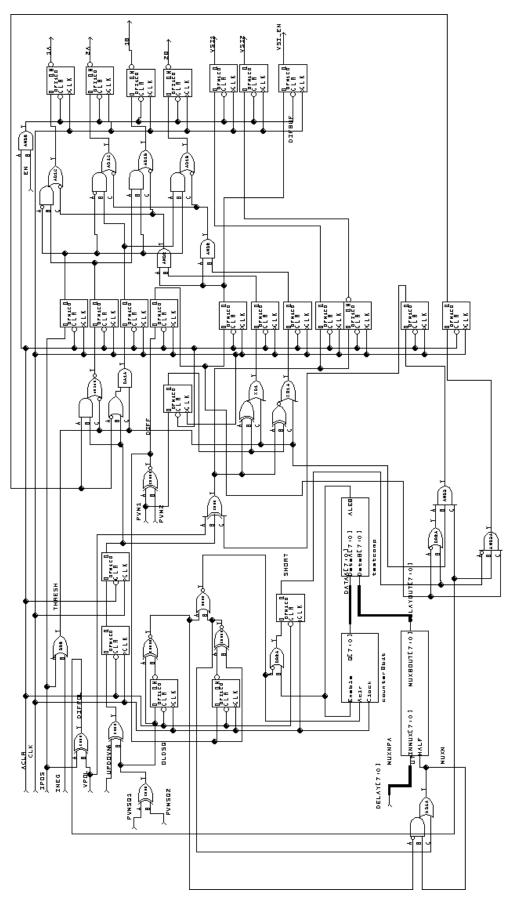

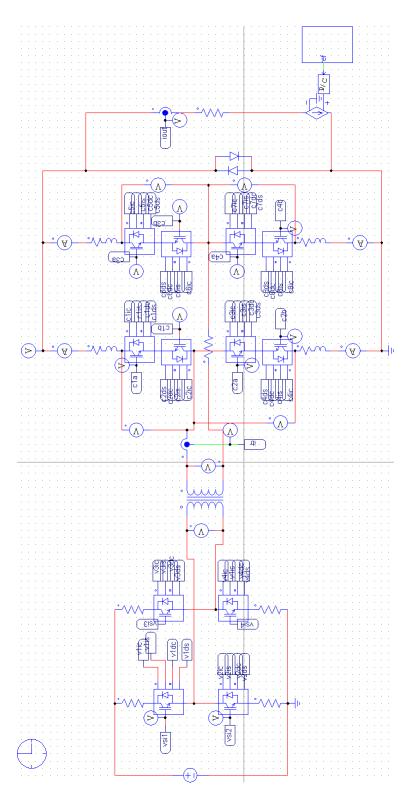

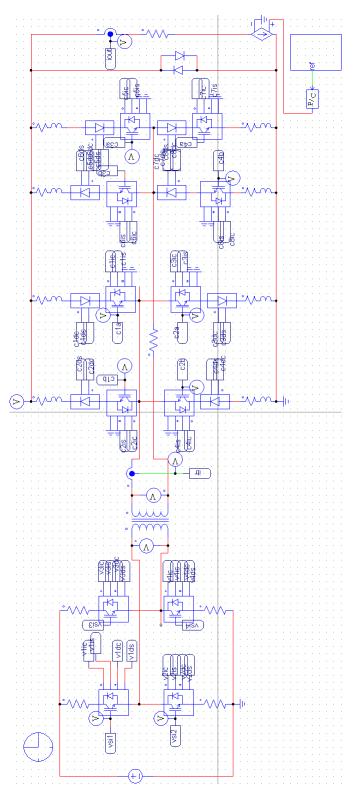

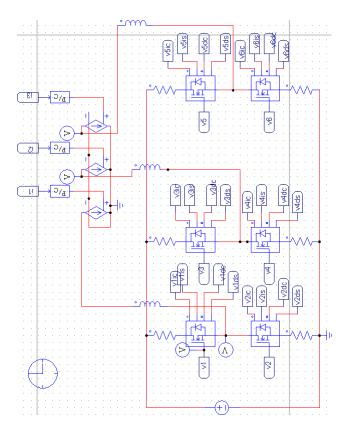

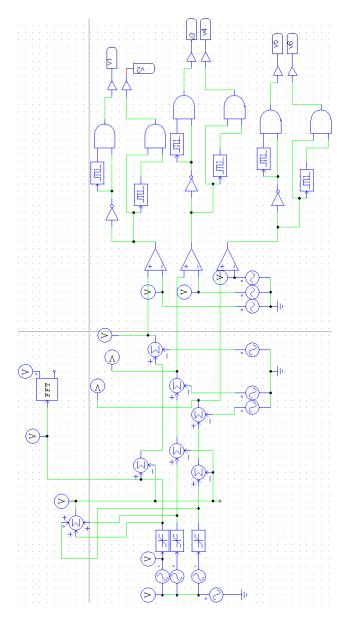

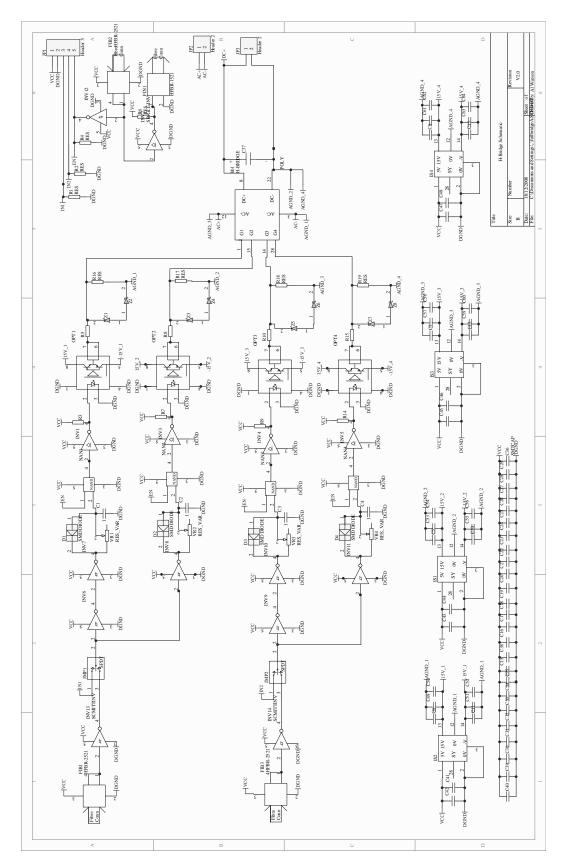

|          | 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Converter Topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                                                                                                                                            |

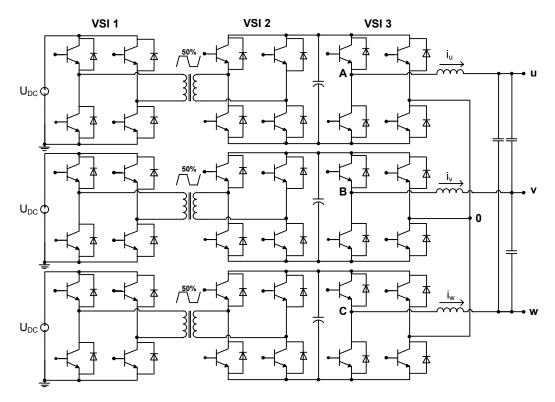

|          | т. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.1.1 Triple VSI Topology (T1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73                                                                                                                                                                                                            |

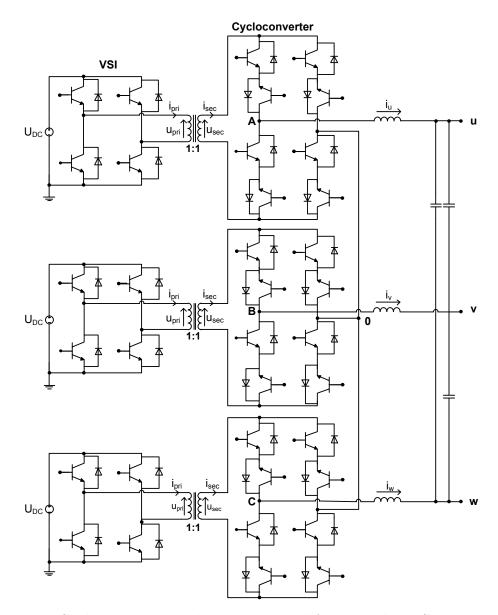

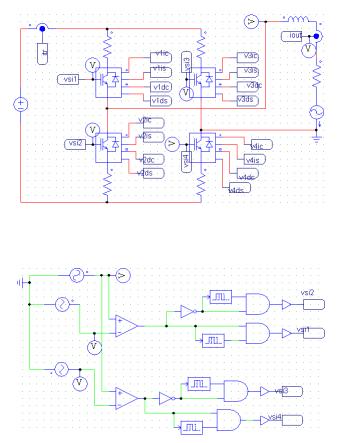

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.1.2 Cycloconverter Topology (T2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74                                                                                                                                                                                                            |

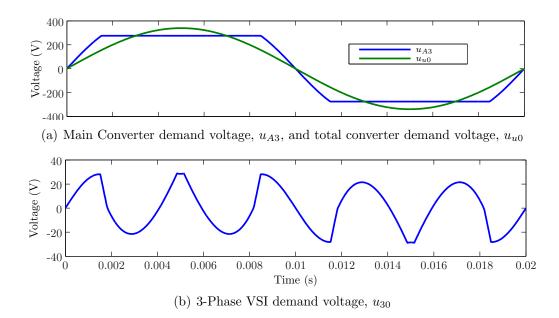

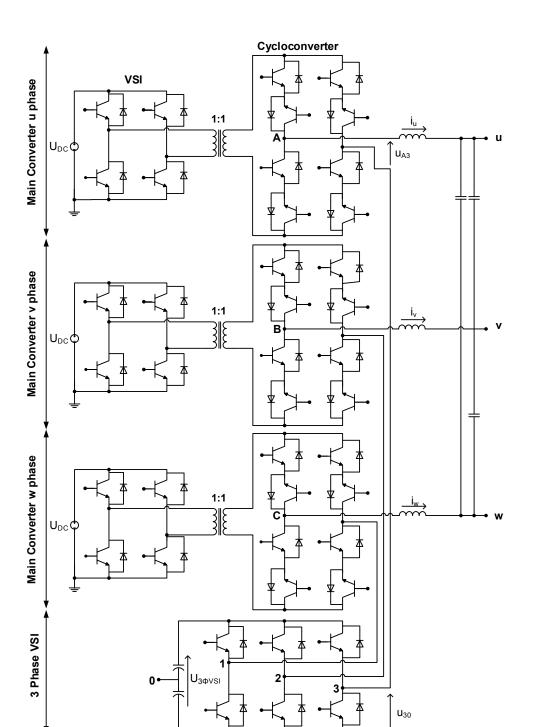

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                               |

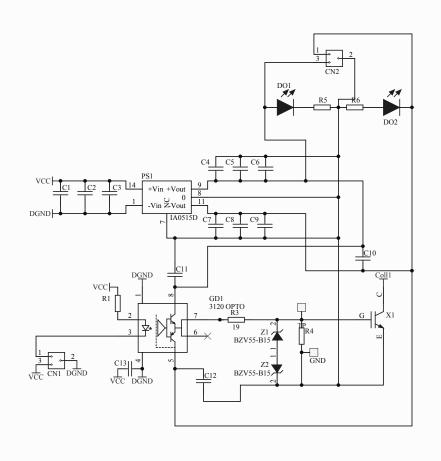

|          | 4.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.1.3 Hybrid Cycloconverter Topology (T3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76                                                                                                                                                                                                      |

|          | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Loss Estimation Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76                                                                                                                                                                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.1 Circuit Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78                                                                                                                                                                                                            |

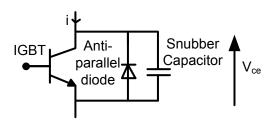

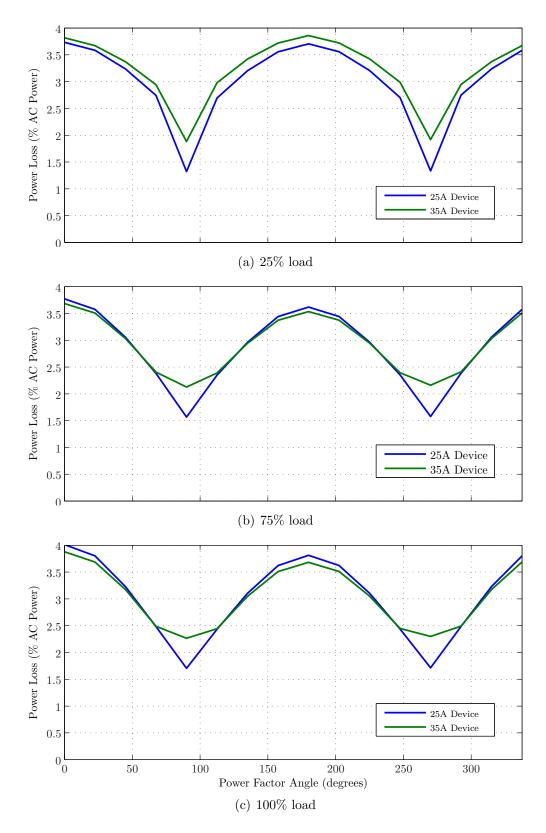

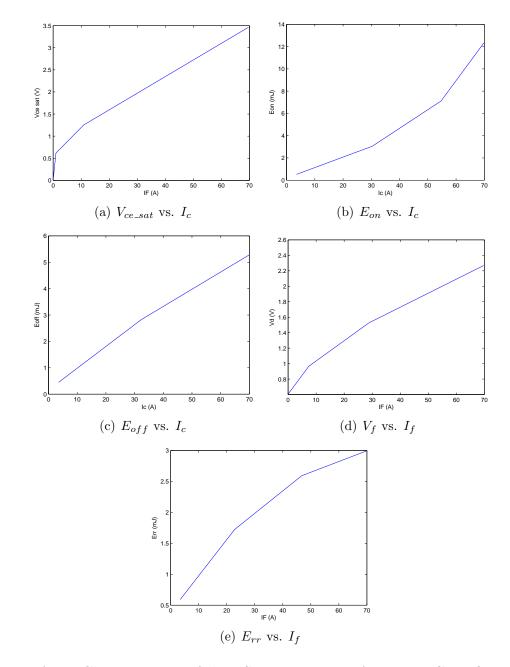

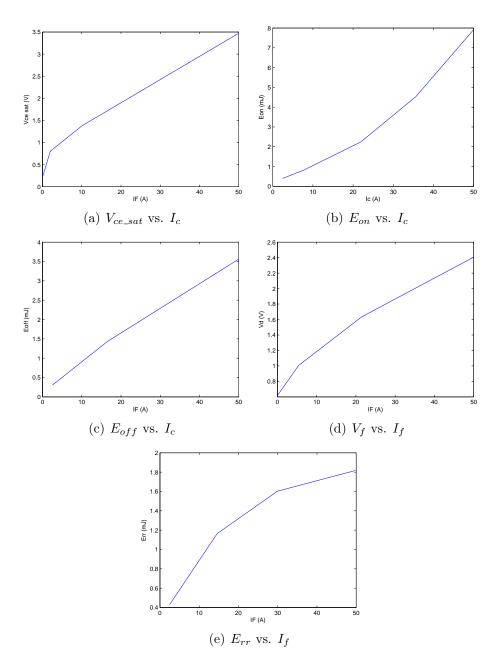

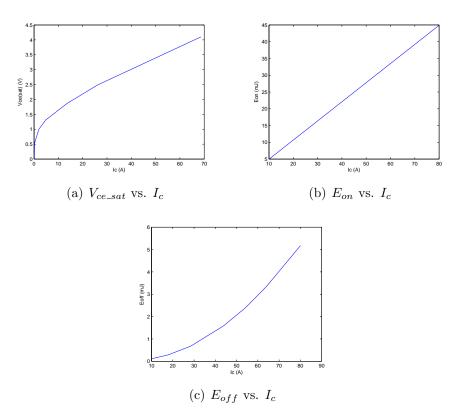

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.2 Simulated Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79                                                                                                                                                                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.3 PSIM Thermal Module Loss Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80                                                                                                                                                                                                            |

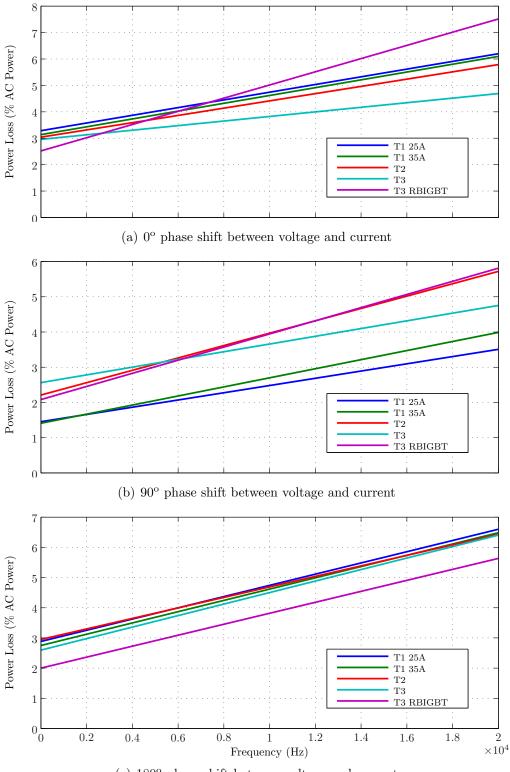

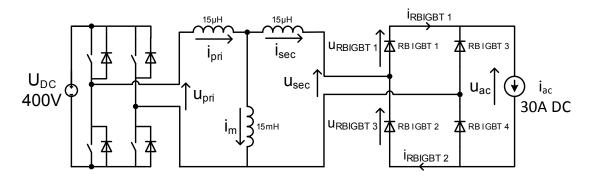

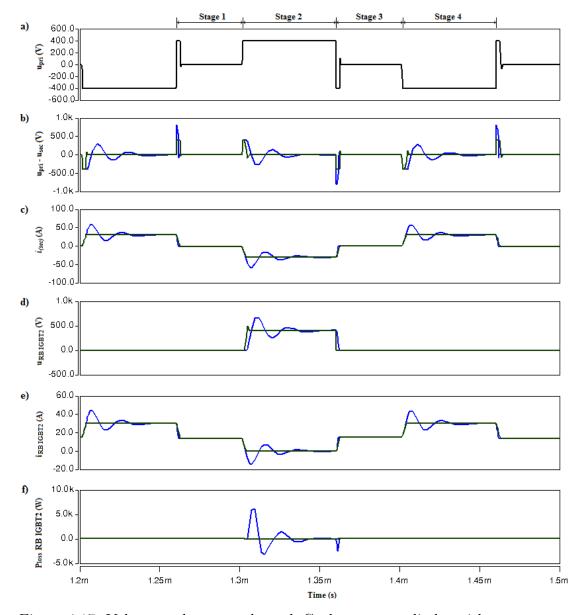

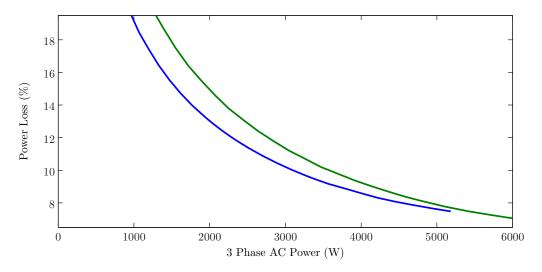

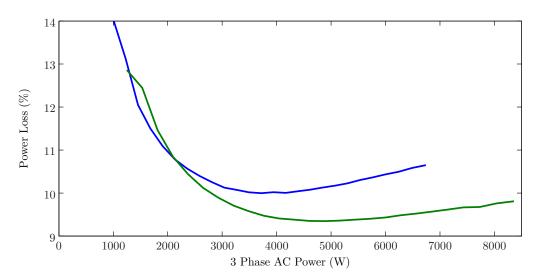

|          | 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84                                                                                                                                                                                                            |

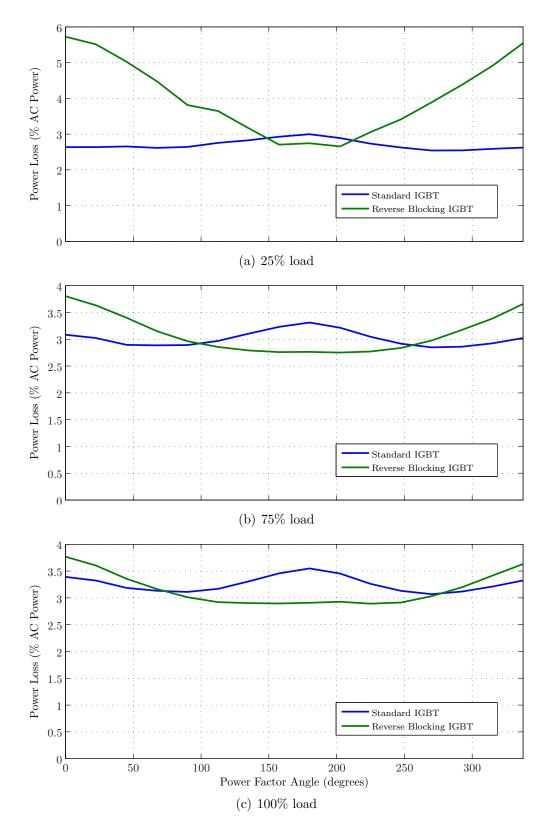

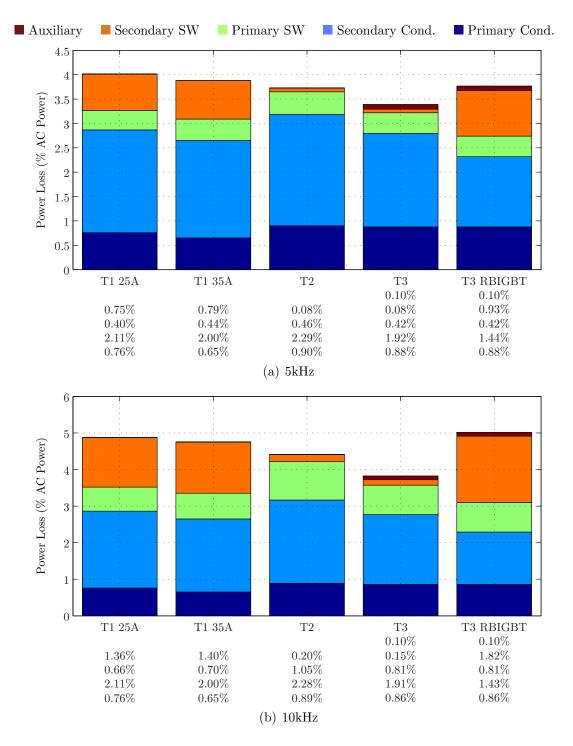

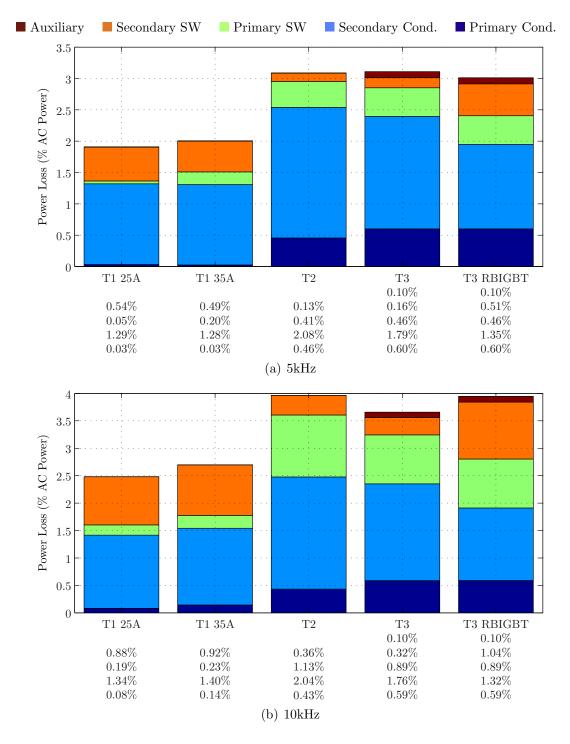

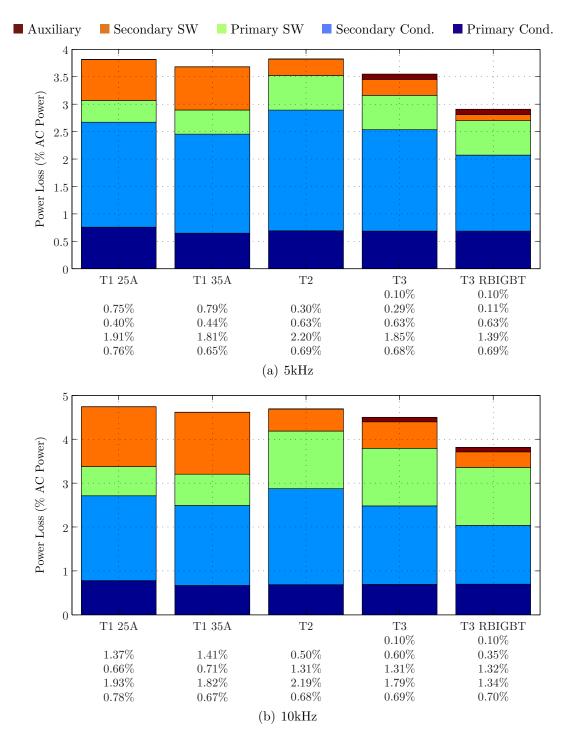

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.1 General Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84                                                                                                                                                                                                            |

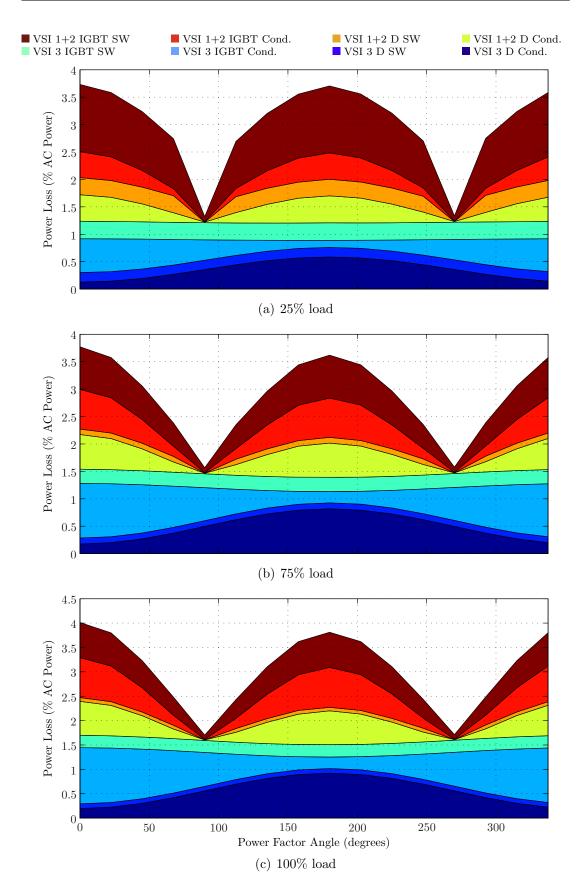

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.2 Analysis of the Benchmark VSI Converter Losses $(T1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85                                                                                                                                                                                                            |

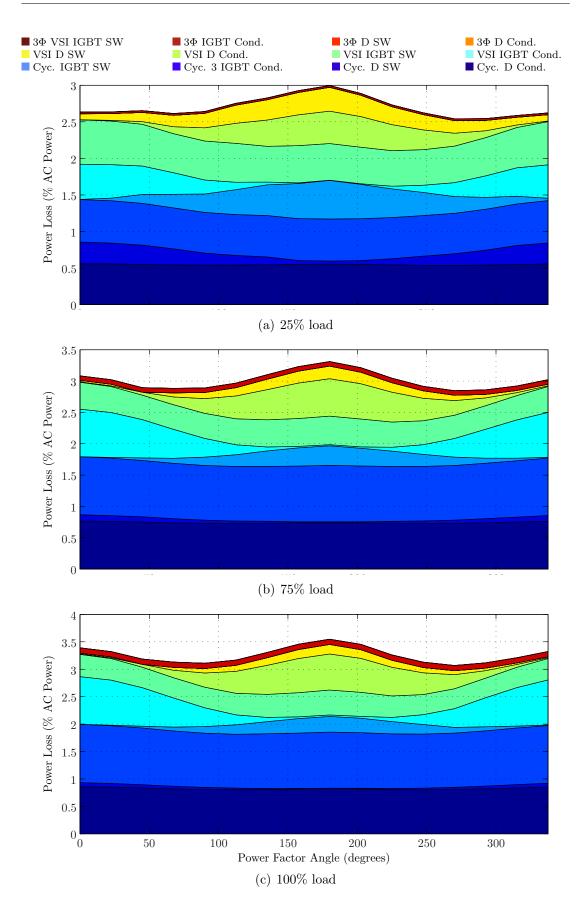

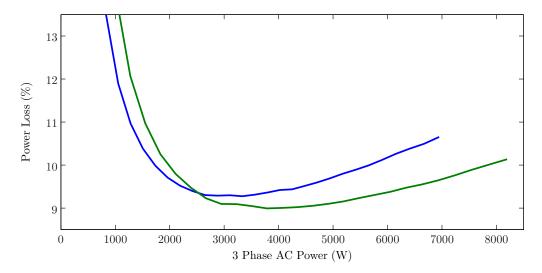

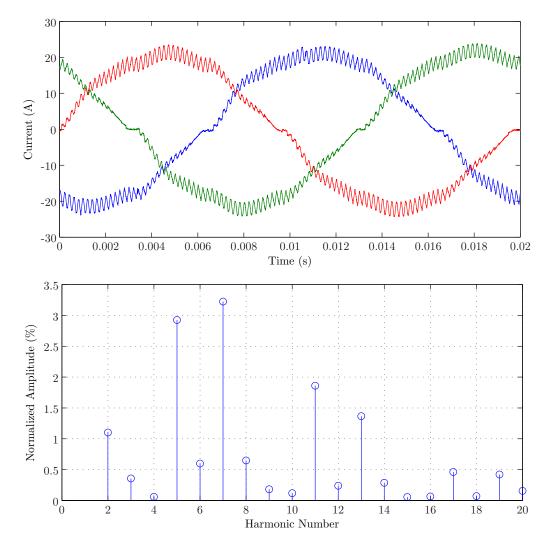

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.3 Analysis of Cycloconverter Topology Losses (T2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                                                                                                                                                            |

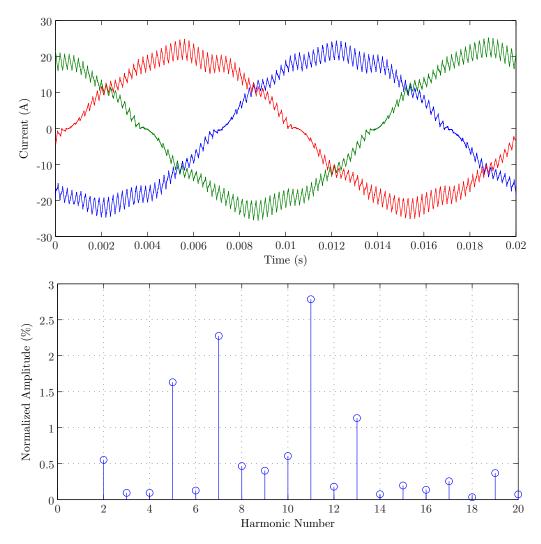

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.4 Analysis of Hybrid Cycloconverter with Auxiliary 3-Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                               |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VSI $(T3)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91                                                                                                                                                                                                            |

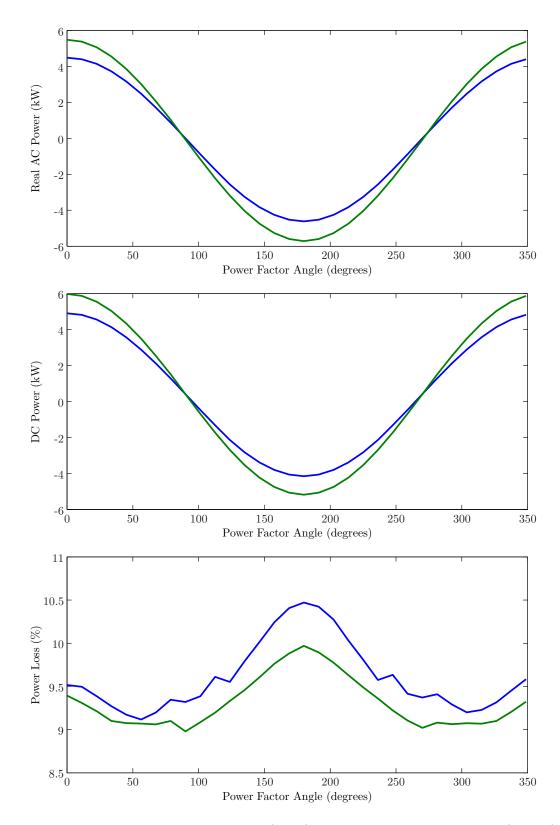

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.5 Further Discussion of Losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94                                                                                                                                                                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.6 Extrapolation of Losses with Switching Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 103                                                                                                                                                                                                           |