# CMOS OPTICAL CENTROID PROCESSOR FOR AN INTEGRATED SHACK-HARTMANN WAVEFRONT SENSOR

Boon Hean Pui, B.Eng (Hons)

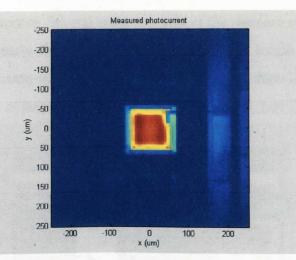

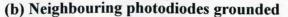

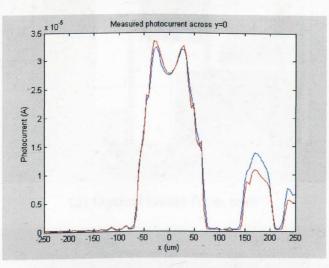

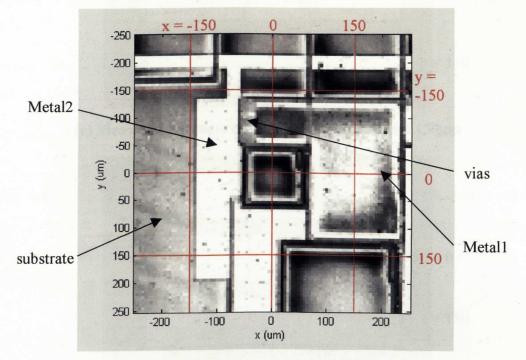

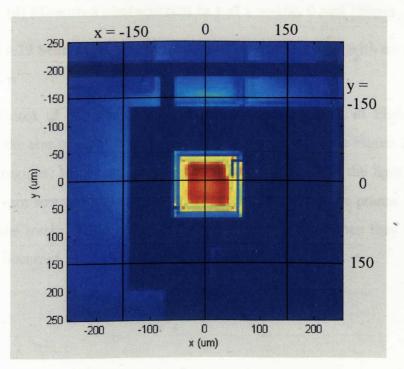

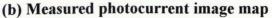

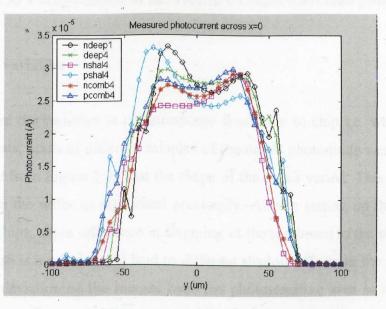

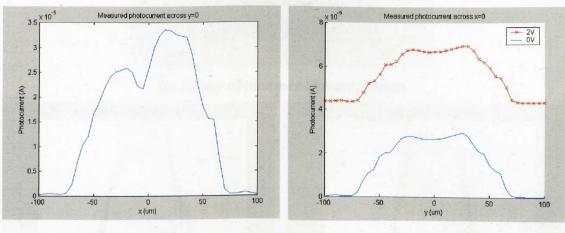

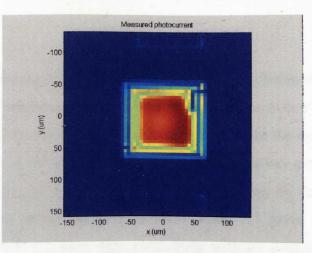

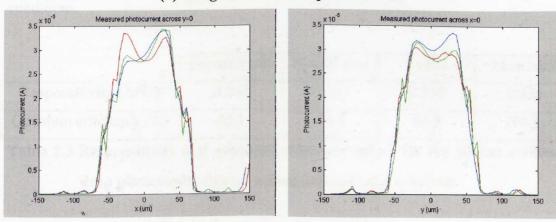

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

September 2004

## ABSTRACT

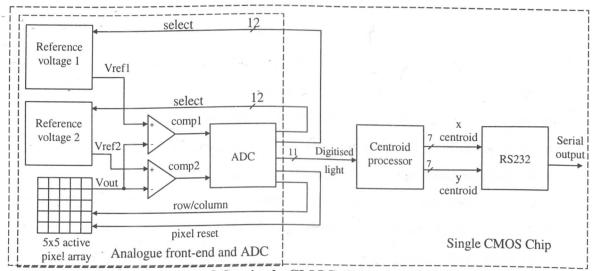

A Shack Hartmann wavefront sensor is used to detect the distortion of light in an optical wavefront. It does this by sampling the wavefront with an array of lenslets and measuring the displacement of focused spots from reference positions. These displacements are linearly related to the local wavefront tilts from which the entire wavefront can be reconstructed. In most Shack Hartmann wavefront sensors, a CCD is used to sample the entire wavefront, typically at a rate of 25 to 60 Hz, and a whole frame of light spots is read out before their positions are processed. This results in a data bottleneck. In this design, parallel processing is achieved by incorporating local centroid processing for each focused spot, thereby requiring only reduced bandwidth data to be transferred off-chip at a high rate. To incorporate centroid processing at the sensor level requires high levels of circuit integration not possible with a CCD technology. Instead a standard 0.7µm CMOS technology was used but photodetector structures for this technology are not well characterised. As such characterisation of several common photodiode structures was carried out which showed good responsitivity of the order of 0.3 A/W. Prior to fabrication on-chip, a hardware emulation system using a reprogrammable FPGA was built which implemented the centroiding algorithm successfully. Subsequently, the design was implemented as a single-chip CMOS solution. The fabricated optical centroid processor successfully computed and transmitted the centroids at a rate of more than 2.4 kHz, which when integrated as an array of tilt sensors will allow a data rate that is independent of the number of tilt sensors employed. Besides removing the data bottleneck present in current systems, the design also offers advantages in terms of power consumption, system size and cost. The design was also shown to be extremely scalable to a complete low cost real time adaptive optics system.

## ACKNOWLEDGEMENTS

If I have seen further it is by standing on the shoulders of giants. -Isaac Newton

I would like to thank Dr. Barrie Hayes Gill for his support, guidance, and not least, patience throughout my research work. I would also like to express my gratitude to Professor Mike Somekh and Dr. Chung Wah See for their help and guidance. To Matt Clark, all your help and brilliant insights are greatly appreciated. To the many research staff, colleagues and technicians who have in one way or another been involved in my work, I thank you.

The research work has been supported by the University of Nottingham, University of Nottingham International Office, University of Nottingham in Malaysia and the Engineering and Physical Sciences Research Council (EPSRC), UK and I would like to thank them for making this possible.

Finally, my sincere thanks go to my friends and family for making this journey bearable, and my deepest gratitude and love to my parents and brother for their belief in me.

# **TABLE OF CONTENTS**

| Aı | BSTRAC | Т                                         | I  |

|----|--------|-------------------------------------------|----|

| 1  | Intr   | ODUCTION                                  | 1  |

|    | 1.1    | Adaptive Optics                           | 1  |

|    | 1.2    | APPLICATIONS                              | 3  |

|    | 1.2.1  | Astronomy                                 | 3  |

|    | 1.2.2  | Ophthalmology                             | 6  |

|    | 1.2.3  | BEAM QUALITY CONTROL                      | 7  |

|    | 1.2.4  | MICROSCOPY                                | 9  |

|    | 1.3    | WAVEFRONT SENSING                         |    |

|    | 1.3.1  | SHACK-HARTMANN WAVEFRONT SENSOR           | 10 |

|    | 1.3.2  | Other Wavefront Sensors                   |    |

|    | 1.4    | CENTROID DETECTION                        | 15 |

|    | 1.4.1  | LATERAL EFFECT PHOTODIODES (LEP)          | 16 |

|    | 1.4.2  | MULTI-ELEMENT PSD                         | 16 |

|    | 1.4.3  | MULTI-ELEMENT PSD PERFORMANCE             |    |

|    | 1.4.4  | Centroid Processing                       | 22 |

|    | 1.5 ,  | PHOTODETECTION                            | 34 |

|    | 1.5.1  | Optical Absorption                        | 34 |

|    | 1.5.2  | QUANTUM EFFICIENCY AND RESPONSITIVITY     |    |

|    | 1.5.3  | Noise and Photodiode Equivalent Circuit   | 39 |

|    | 1.5.4  | PHOTODIODE MEASUREMENTS                   | 42 |

|    | 1.5.5  | TECHNOLOGY AND MATERIALS                  | 44 |

|    | 1.6    | PIXEL ARCHITECTURES IN CMOS               | 51 |

|    | 1.6.1  | PASSIVE PIXEL SENSORS (PPS)               | 52 |

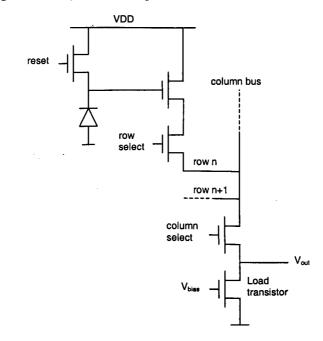

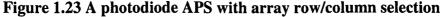

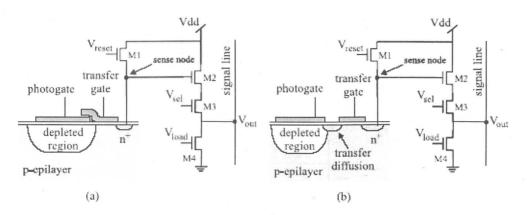

|    | 1.6.2  | ACTIVE PIXEL SENSORS (APS)                | 53 |

|    | 1.6.3  | NOISE REMOVAL AND EXTENDING DYNAMIC RANGE | 57 |

|    | 1.7    | Chapter Summary                           | 60 |

| 2  | Сна    | RACTERISATION OF CMOS PHOTODIODES         | 63 |

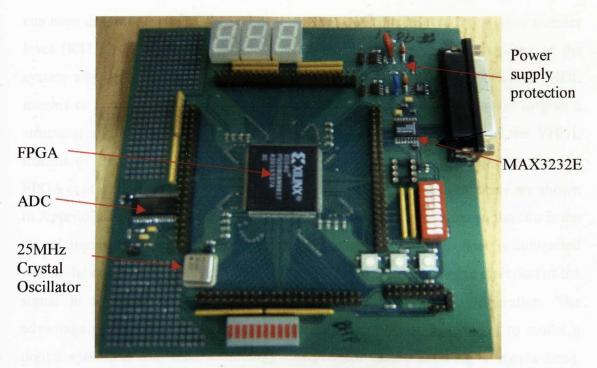

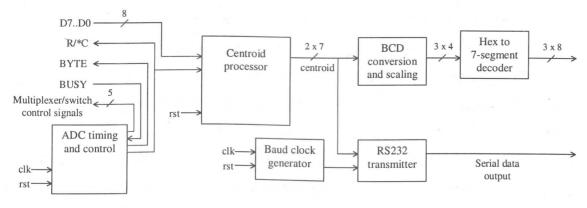

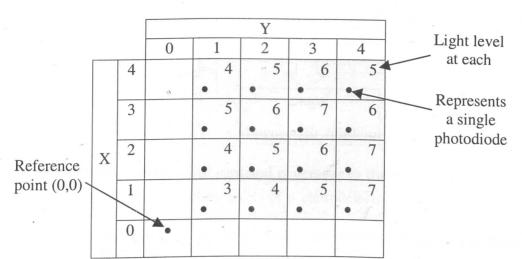

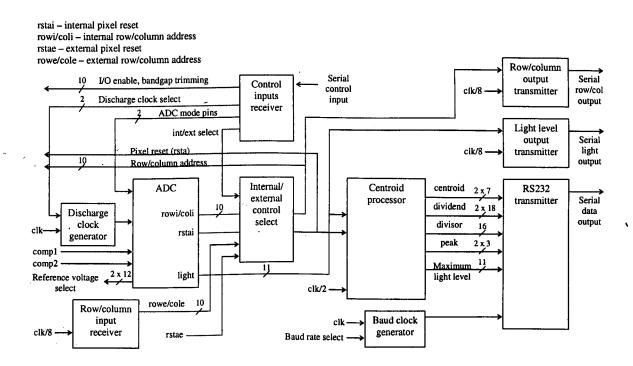

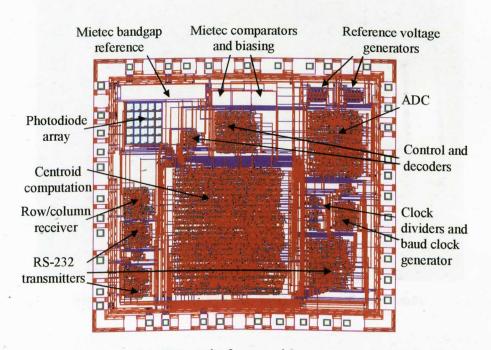

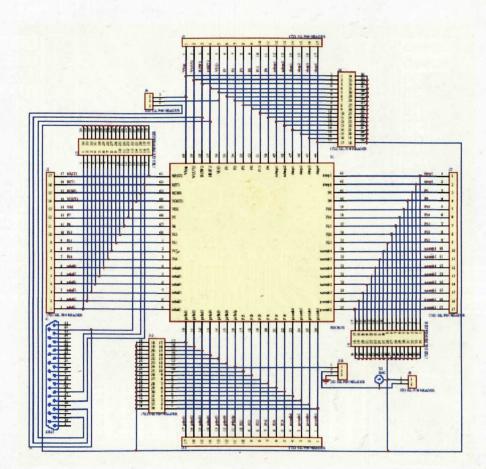

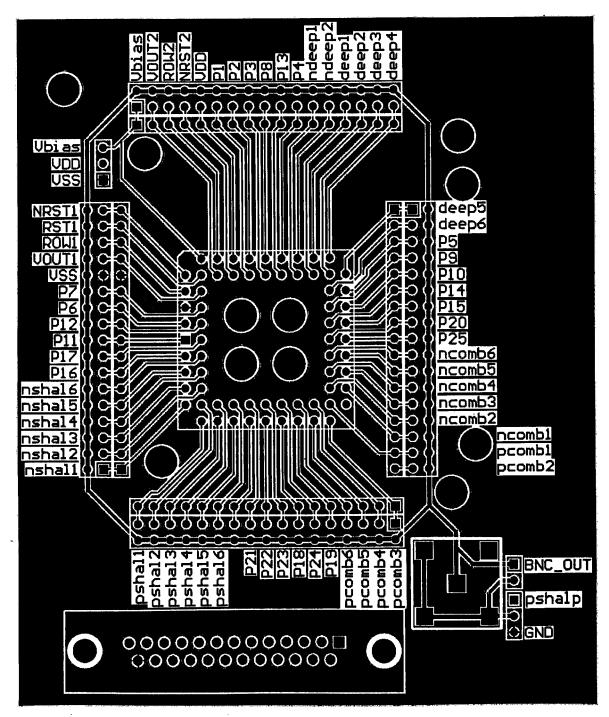

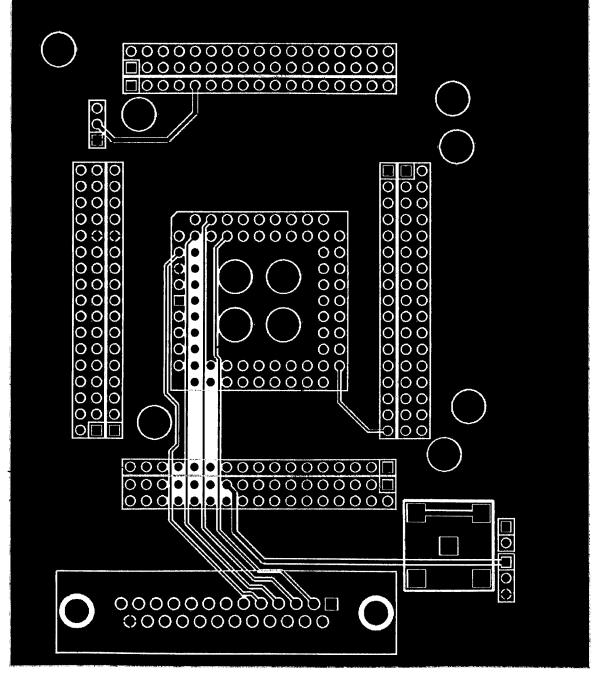

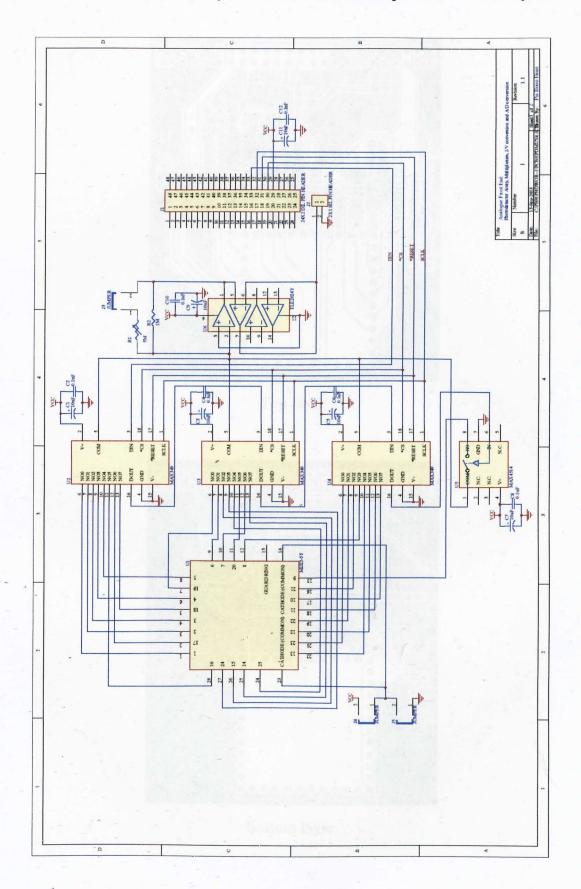

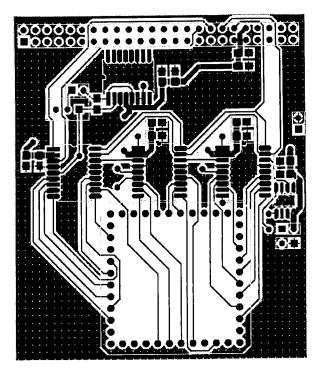

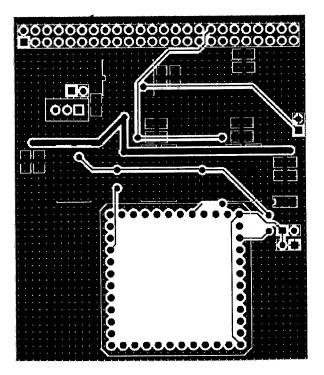

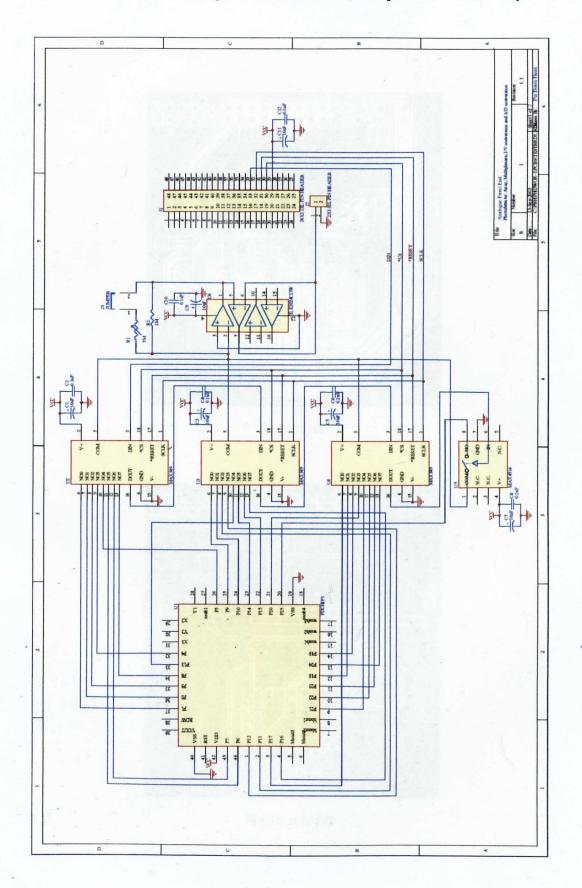

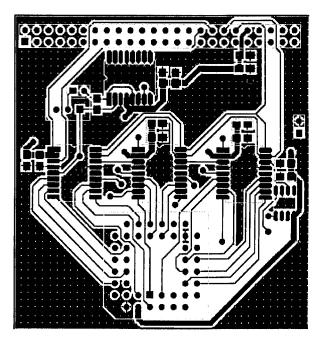

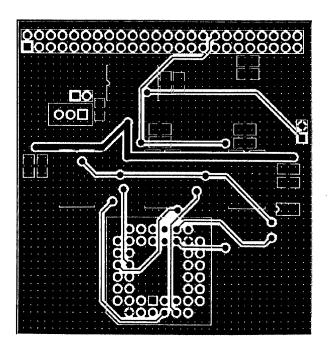

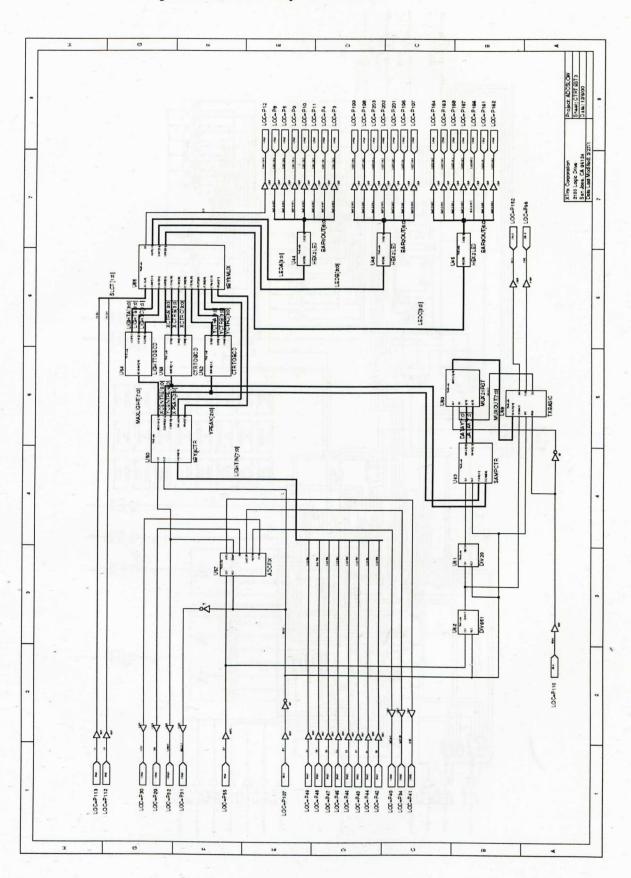

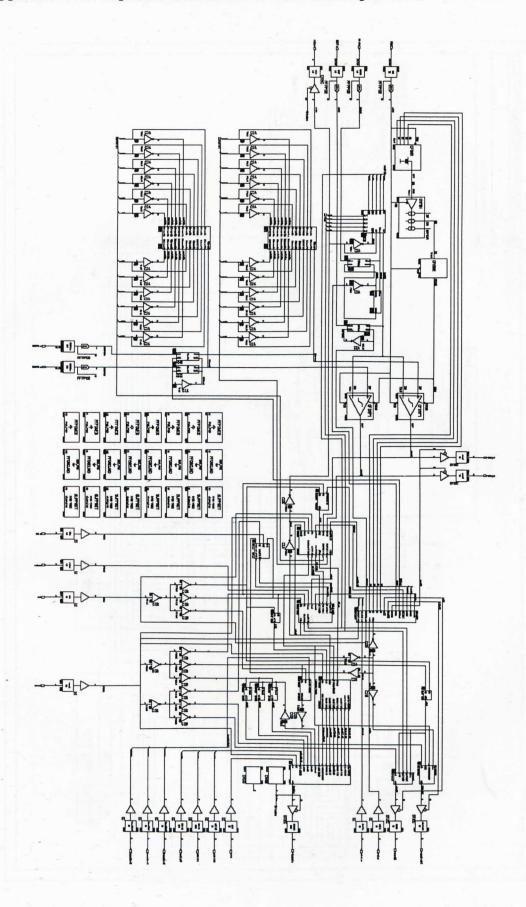

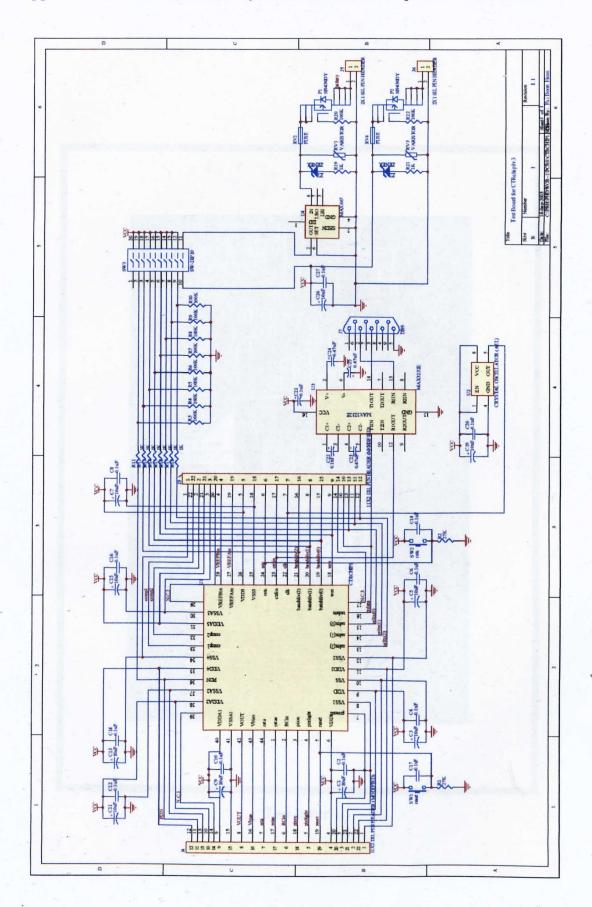

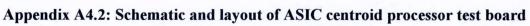

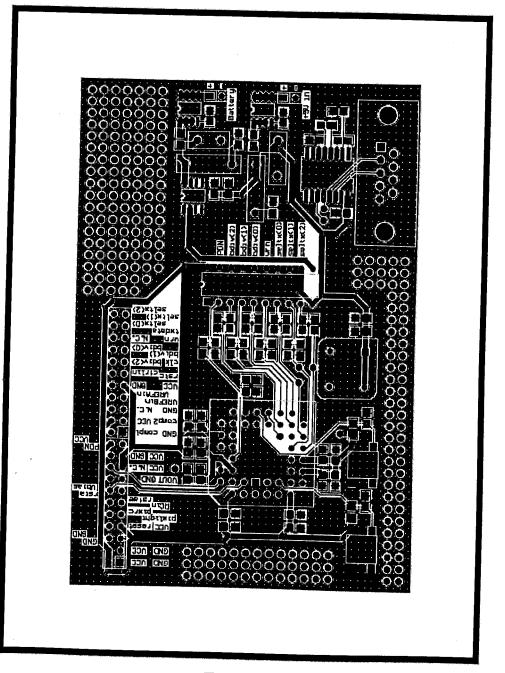

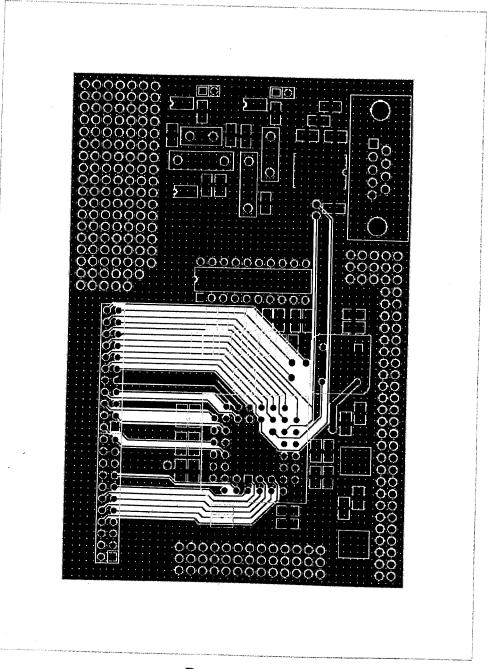

| 4.3.3   | LAYOUT AND TEST BOARD                          | 154 |

|---------|------------------------------------------------|-----|

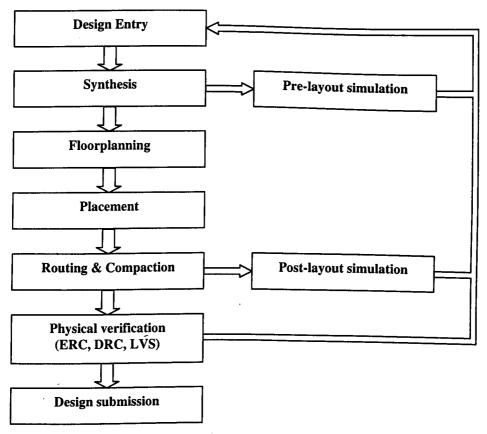

| 4.4     | ASIC CAD Environment and Design Flow           | 157 |

| 4.4.1   | Design and Layout Issues                       | 159 |

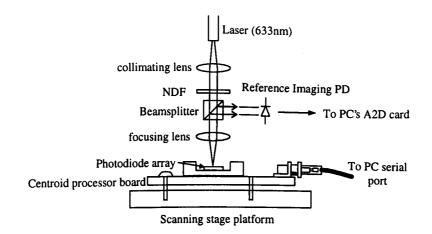

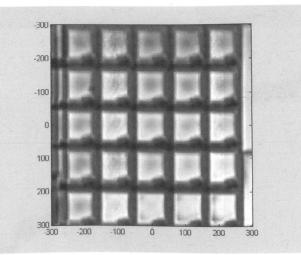

| 4.5     | RESULTS OF CENTROID ASIC                       | 164 |

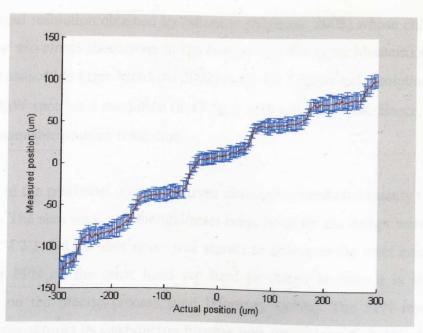

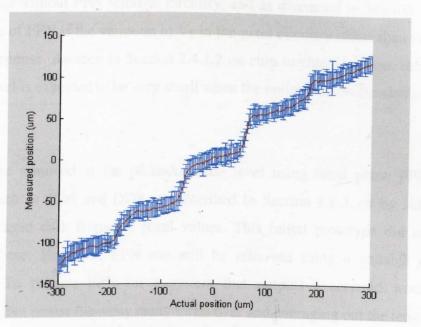

| 4.5.1   | Position Resolution                            | 166 |

| 4.5.2   | Speed                                          | 169 |

| 4.5.3   | DYNAMIC RANGE                                  | 171 |

| 4.5.4   | Scalability                                    |     |

| 4.6     | CHAPTER SUMMARY                                |     |

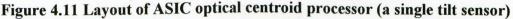

| 5 WAV   | EFRONT RECONSTRUCTION                          | 174 |

| 5.1     | INTRODUCTION                                   |     |

| 5.2     | WAVEFRONT DESCRIPTION                          |     |

| 5.3     | DEFORMABLE MIRRORS                             |     |

| 5.4     | WAVEFRONT RECONSTRUCTION                       | 177 |

| 5.4.1   | Modal Approach                                 | 178 |

| 5.4.2   | ZONAL APPROACH                                 | 179 |

| 5.4.3   | RECONSTRUCTION PROCEDURE                       |     |

| 5.5     | COMPLETE AO SYSTEM                             |     |

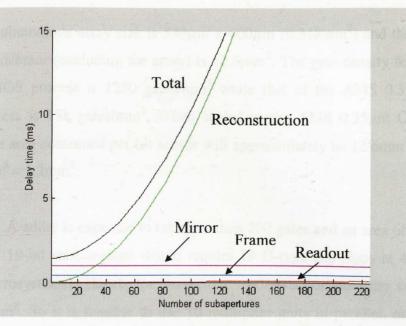

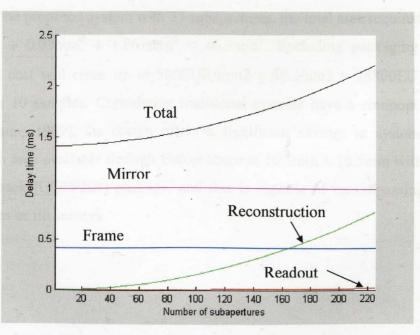

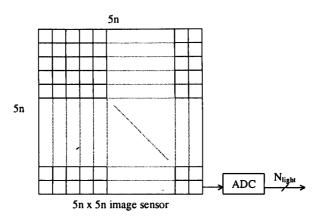

| 5.5.1   | Speed                                          | 186 |

| 5.5.2   | Area and Cost                                  | 191 |

| 5.6     | CHAPTER SUMMARY                                | 192 |

| 6 Con   | CLUSIONS                                       | 193 |

| 6.1     | DISCUSSION                                     |     |

| 6.1.1   | Design Specifications                          | 193 |

| 6.1.2   | CHARACTERISATION OF CMOS PHOTODIODE STRUCTURES |     |

| 6.1.3   | Design Prototyping                             | 195 |

| 6.1.4   | COMPLETE AO SYSTEM                             |     |

| 6.2     | Further Work                                   |     |

| 6.3     | CONCLUSIONS                                    |     |

| Appendi | ICES                                           |     |

|         |                                                |     |

| ,       |                                                |     |

| •<br>•  |                                                |     |

|         |                                                |     |

|         |                                                |     |

Ŷ

.

# **CHAPTER 1**

## INTRODUCTION

## **1.1 ADAPTIVE OPTICS**

Since Galileo pointed his telescope to the heavens some 400 years ago, man has been trying to see further and further into the stars and in greater detail. The fundamental limit of resolving the images is known as the diffraction limit and is governed by the diameter of the lens used. However it was observed that as larger telescope lenses were used, the astronomical images did not get any sharper when the lenses exceeded about 20cm in diameter [Angel 2000]. There was something distorting the images in a seemingly random manner. This was the air around us. Variations in temperature in the atmosphere cause random fluctuations in wind velocity and hence, changes in the refractive index [Tyson 1998]. This leads to distortion in the images obtained. Fortunately there was something we could do about it and it is called adaptive optics.

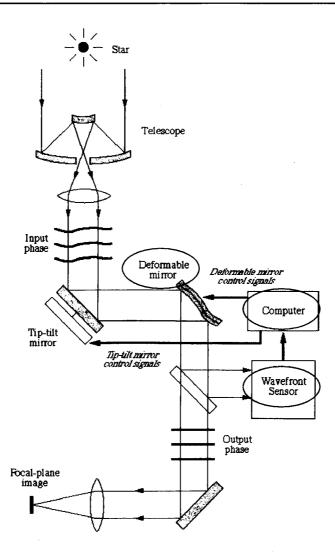

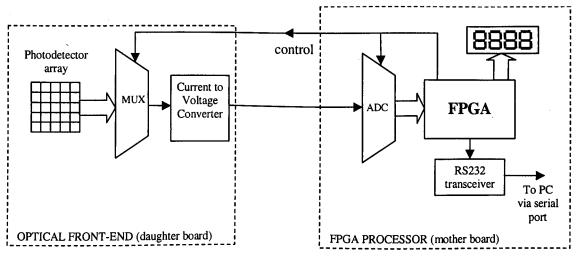

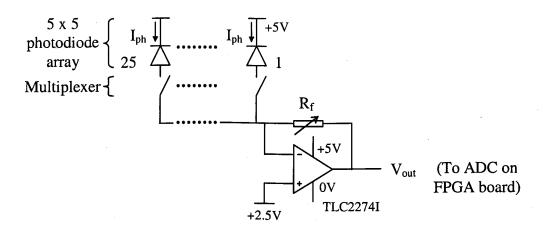

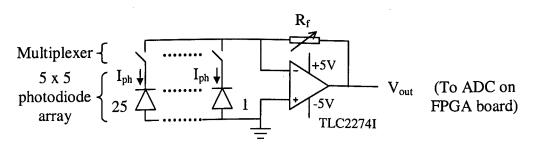

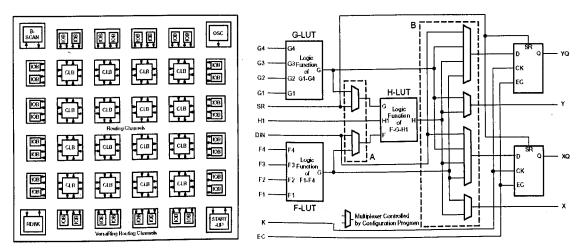

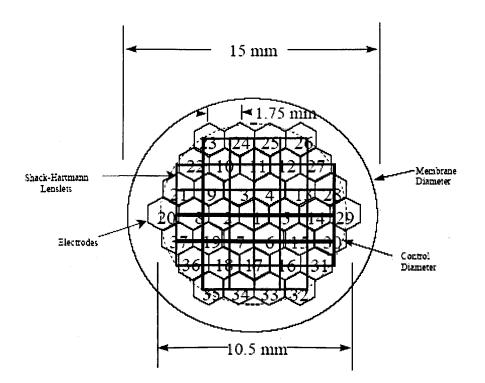

Adaptive optics (AO), which has been heavily developed over the last 30 years, allows automatic compensation of atmospheric systems. It deals with the control of light in a real-time closed-loop fashion and is made up of three fundamental components, the wavefront sensor, the control computer and a corrector element such as a deformable mirror. The wavefront sensor acts like the eyes detecting light from the object of interest, such as an astronomical object or a satellite, and transducing the intensity information of the wavefront into phase information of the aberration in the wavefront. The control computer then calculates the necessary changes required to correct this aberration, and passes this on to the corrector or the deformable mirror where these changes are made. Figure 1.1 shows the components of a typical adaptive optics system as used in a telescope [OByrne 1996]. Often a tilt-tip mirror is used to rapidly remove beam wander in the incoming beam of light while the deformable mirror performs the higher order corrections.

Figure 1.1 A typical adaptive optics system with its fundamental components highlighted [O'Byrne 1996]

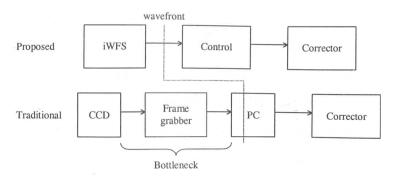

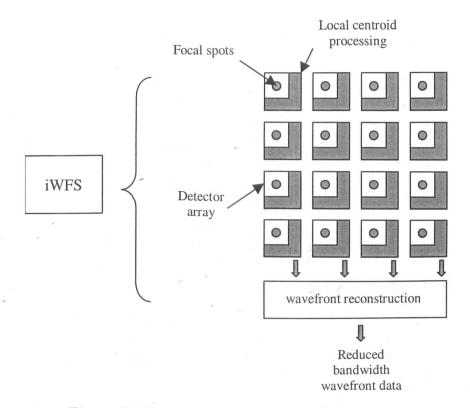

The most widely used wavefront sensor in adaptive optics is the Shack-Hartmann [Platt 2001] and currently with most of these systems a CCD is used to sample the wavefront and a frame grabber is used to acquire and digitise the image before it is transferred to a PC for reconstruction of the wavefront. The bandwidth of these AO systems is often limited to some tens of Hz [Nirmaier 2003]. Integration of these systems with processing at the detector level will reduce the bandwidth of the data to be transferred off-chip thus allowing fast real-time wavefront detection and correction and is the topic of this research. Furthermore, integration of the system even further; realising the concept of a System-on-a-Chip (SoC).

Adaptive optics has traditionally been known for its role in compensating wavefront distortions for astronomical applications. The main reason for this is the cost of the key elements of an adaptive optics system - deformable mirrors, wavefront sensors and control systems requiring high-speed computers. AO systems with a reasonable bandwidth (greater than a few Hz) were extremely expensive, with a component cost of  $> \pm 10^5$  [Munro 1999]. Applications of adaptive optics however are not limited to astronomy or defence initiatives and a number of potential applications are surfacing which will benefit from some form of cheap, fast, adaptive optics systems. These range from laser communications, to medical imaging of the retina, to industrial inspection to the development of more efficient lasers as well as underwater imaging devices and better microscopes. Basically adaptive optics can be used wherever light passes through a distorting medium. Section 1.2 will cover some of the application areas where an adaptive optics system can be applied. In Section 1.3 the concept of wavefront sensing is described paying particular attention to the mechanics of a Shack-Hartmann wavefront sensor and how integration will remove the bottleneck in traditional CCD systems. The process of detecting a centroid which is a fundamental component of a Shack-Hartmann wavefront sensor is covered under Section 1.4. Section 1.5 and 1.6 will then review the theory behind photodetection and the possible implementation structures for this. Section 1.7 summarises the chapter while Section 1.8 will detail the layout of the rest of the chapters.

## **1.2 APPLICATIONS**

In addition to system integration, the development of new low-cost technologies such as Micro-Opto-Electro-Mechanical Systems (MOEMS), liquid crystal wavefront correctors and micromachined deformable mirrors [Anderson 1999, Hatcher 2001, Vdovin 1997] will further open up new areas of applications. Some of the key applications for an adaptive optics system are discussed in the following subsections.

## **1.2.1 ASTRONOMY**

The field of astronomy gave birth to the technique of adaptive optics and is widely used in correcting the imaging capabilities of ground-based telescopes. The image

quality of all ground-based telescopes suffers from atmospheric turbulence, which is the fundamental reason for placing the Hubble Space Telescope in space and the fact that ground-based telescopes are built high in the mountaintops with clear air regions. The spatial resolution of uncompensated telescopes can be more than 10 times better on mountains than at sea level [Tyson 2000].

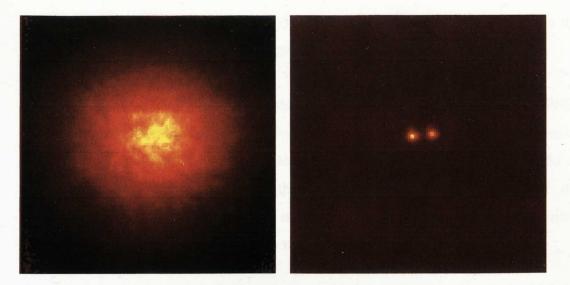

The structure and statistics of turbulence as well as its corresponding effects can be described by a model by Kolmogorov [Tyson 1998]. The effect of this turbulence is to cause high spatial frequency beam spreading, low spatial frequency beam wander, and intensity variations which limits the ability of telescopes to resolve fine details. The level of turbulence at a particular site can be described by a parameter introduced by Fried called the Fried coherence length,  $r_a$ , [Fried 1965] and is the maximum diameter of the aperture that can be used for collection of the wavefront before atmospheric distortion seriously limits its performance. This parameter defines the limit of the achievable resolution without compensation, as shown in Figure 1.2 by the sketch of the typical point spread function of a star being imaged by an astronomical telescope. The Fried coherence length is ~2cm under poor seeing conditions to ~20cm under good seeing conditions [Mansell 2000]. Figure 1.3 shows the uncompensated and compensated image of a binary star as taken at the Starfire Optical Range [Air Force Research Laboratory Directed Energy Directorate 1997]. With compensation, the image halo or beam spread, as in Figure 1.2, has been corrected for and the two distinct stars of the binary star k-Peg can be discerned.

Figure 1.2 Beam spread due to atmospheric turbulence limits the resolution for an aperture of diameter D

Figure 1.3 Uncompensated (left) and compensated (right) images of the binary star k-Peg as taken by the Starfire Optical Range [Air Force Research Laboratory Directed Energy Directorate 1997]

For adaptive optics to work, the aberrations that are caused by the turbulence have to be measured faster than they can change. This is given by the Greenwood frequency  $f_{\rm G}$ , which is strongly dependent on the velocity of the wind, and can range from tens to hundreds of hertz under fair viewing conditions [Tyson 2000]. Another important factor to consider in the design of atmospheric adaptive optics systems is the isoplanatic angle  $\theta_0$ , which determines the maximum angle that we can look away at our object point and still measure the correct wavefront [Tyson 2000]. Because the isoplanatic patch for the atmosphere is so small, only a tiny fraction of the sky will be near suitably bright stars that can serve as reference beacons. A way of overcoming this is to produce artificial guide stars using powerful lasers to illuminate the sky. Two types of artificial guide stars exist. One using Rayleigh scattering of ultraviolet or visible light illuminates the sky at a height of 5 to 15 kilometres in the atmosphere. The other uses resonant scattering of light from a layer of sodium atoms that sits in the upper mesosphere at about 90 to 100 kilometres in altitude. The second scheme has the advantage of putting the reference beacon higher, thus sampling a larger portion of the path of light from a celestial object in space to a telescope on Earth [Olivier 1999]. The disadvantage is that it is more expensive and requires laser at a specific wavelength of 589nm for excitation of sodium atoms. An emerging technique called Multi-Conjugate Adaptive Optics (MCAO) which uses several guide stars and

wavefront sensors allows the field of view to be extended and could overcome the disadvantage of having to use artificial guide stars [Berkefeld 2001].

Besides atmospheric imaging, underwater imaging and fluid mechanics [Neal 1993] will also benefit from the field of adaptive optics. And just as how the advancement of lasers, imaging devices and optical materials has pushed the frontiers of the field of adaptive optics for astronomy, the theories and techniques developed for the correction of atmospheric turbulence is directly applicable to that of other non-astronomical applications enabling their rapid development.

#### **1.2.2 OPHTHALMOLOGY**

Imperfections in the cornea and the eye leads to refractive errors which causes image blurring. This gives rise to long and short sightedness which needs correction with glasses or contact lenses. It is now possible to perform these corrections through eye surgery. Laser-Assisted In-Situ Keratomileusis, or LASIK as it is commonly known, is the procedure of reshaping the cornea with a laser beam to correct for these errors. Typically LASIK corrects for low-order aberrations and in the course of reshaping the cornea to correct these, refractive surgeries can inadvertently increase higher-order aberrations. A wavefront sensor can be used to measure these higher-order aberrations and to allow doctors to have a more detailed and quantitative view of the topography of the cornea before it is operated upon. The first commercial ophthalmic Shack-Hartmann aberrometer, the Complete Ophthalmic Analysis System (COAS), manufactured by WaveFront Sciences, Inc. became available in early 2000 and incorporates a CCD-based Shack-Hartmann wavefront sensor [Salmon]. The human eye is a non-static optical system and the corrections need to be done at a bandwidth of at least several hundred Hz [Nirmaier 2003]. Real-time wavefront correction in the human eye will also allow a better diagnosis of eye diseases like the common glaucoma and will allow the development of the next generation of customised wavefront-guided contact lenses [Thibos 2003].

#### **1.2.3 BEAM QUALITY CONTROL**

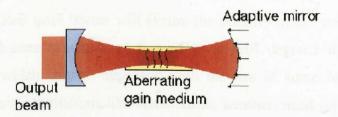

The beam quality and output power of lasers can be degraded by optical aberrations within the laser resonator [Kudryashov 2002]. Adaptive optics allow the correction of these aberrations using either intracavity or extracavity control of the beam. Intracavity control involves using an adaptive mirror as one of the end mirrors of the laser resonator as shown in Figure 1.4.

Figure 1.4 Intracavity laser beam correction [Applied Optics Group; Imperial College]

Intracavity control is able to influence the geometry of the output modes and stabilise the output energy. Also the output parameters of the beam can be changed without the need to reconstruct the entire cavity or altering the power supply block which is costly and time consuming. Intracavity beam control will also aid in the generation of beams with a super-gaussian distribution [Cherezova 1997], which has lower side lobe intensities than a typical Gaussian beam and consequently, a reduction in higher spatial frequencies and a higher intensity profile. This is very attractive for industrial applications.

For lower orders of aberration, extracavity control is easier to implement. Extracavity correction involves performing correction outside the cavity of the resonator. Extracavity control will allow beams to be accurately focused on a sample as well as maintaining beam quality over long distances. For instance, extracavity control will also be used on the Laser Interferometer Gravitational-Wave Observatory (LIGO) system for the detection of gravitational waves [Mansell 1999]. Gravitational waves are produced by events such as collapses, explosions or collisions of celestial objects and its observation will allow a better view of the universe and its beginnings. They are less attenuated than electromagnetic waves like radio waves but the predicted

magnitudes of such waves are extremely small. As such very sensitive means of detection are necessary to detect these waves and typically laser interferometry with large kilometre sized arms is used. It is necessary to maintain the beam quality and its coherence over the length of the arms making adaptive optics necessary.

Another field that has received a lot of attention lately is that of free space optical communications which will allow high-speed transmission of large bandwidths of data in the order of gigabits and without the need for cables [Weyrauch 2002]. The use of highly collimated laser beams will ensure the security of the communication. Air flow and temperature gradients at ground level will degrade the quality of the communication which can be improved with the use of some form of wavefront correction. However limitations like scintillation, weather, need for line-of-sight and sun-blindness needs to be addressed. In free-space optoelectronic interconnects, a key challenge is maintaining precise alignment of the opto-mechanical system, which requires high tolerances of optical components and opto-mechanics. Correcting any misalignment dynamically using adaptive optics will help reduce the specifications and tolerance requirements of the opto-mechanical system and improve the cost/performance trade-off [Gourlay 2000].

In laser fusion, pulse shaping and precision focus of the high-energy lasers involved will ensure the quality of the laser pulse as it goes through the amplification process and will allow safe testing of nuclear devices as well as aid fusion energy research [Metrologic Instruments Inc.]. Industrial applications of laser beam control include laser welding and cutting [Haferkamp 1993]. For pulse piercing technology using deformable mirrors, the piercing time can be reduced and for laser cutting technology the thickness of high-quality cutting can be increased. Adaptive optics was used to laser cut thicknesses up to 16 mm in mild steel without decrease of the cut surface with a thickness increase by maintaining focus of the laser beam [Geiger 1996]. Commercially, adaptive optics can also be applied to optical data storage such as in CD drives.

#### **1.2.4 MICROSCOPY**

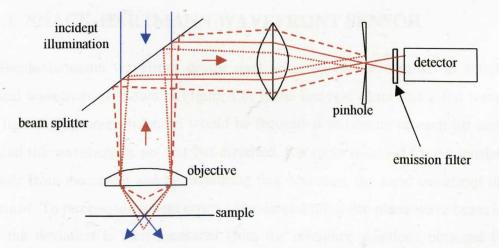

In microscopy, an adaptive optical system can aid in the sensing and correction of aberrations due to imperfections and misalignment in components and the mismatch of refractive indices between the media and the sample to be observed [Booth 2002a, Booth 2002b]. For instance, in a confocal microscope a pinhole is used to block out light from the specimen that are not within the focal plane. This allows strong rejection of multiple scattered light and gives significant improvements in resolution over conventional microscopes [Diaspro 2001]. Its principle is illustrated in Figure 1.5. By scanning the specimen a full 3D image of the specimen can be built up. However, even small amounts of spherical aberration are enough to produce considerable degradation of the imaging performance in the depth direction. Also, confocal microscopes are often operated in reflection because aberrations caused by the refractive index structures within the specimen make imaging in transmission difficult. This results in a loss of phase information only available in transmission. The use of an adaptive optical system would overcome this and allow the compensation of the aberrations introduced by the specimen as well as any misalignment of optical components in the microscope [O'Bryne 1999, Sheppard 1991].

Figure 1.5 Principle of the confocal microscope

In multiphoton fluorescence microscopy, a point source is scanned through the sample volume and the resulting fluorescence is imaged. The localised excitation provides high spatial resolution, efficient background rejection, reduced photobleaching and

increased penetration depth in specimens compared to conventional microscopes. It allows the elimination of the confocal aperture and hence does not limit the number of photons detected. However specimen induced aberration again reduces the achievable resolution as well as increases the necessary laser power to achieve imaging. Aberration correction using feedback will allow the imaging depth to be extended and increase the efficiency of the system [Marsh 2003].

### **1.3 WAVEFRONT SENSING**

As mentioned previously, an integral part of an adaptive optics system is the wavefront sensor which quantitatively measures the amount of aberration present in the wavefront. Wavefront sensing can be either modal or zonal [Tyson 1998]. In modal sensing the wavefront is expressed in terms of coefficients of the modes of a polynomial expansion each representing one of the known aberrations (e.g. tip, tilt, defocus, astigmatism, coma etc.), whose magnitudes are measured separately. Current modal sensors can only sense low-order aberrations. In zonal sensing the wavefront is divided into a number of zones, and the slope or the curvature of the local wavefront is measured in each zone. The Shack-Hartmann wavefront sensor is one such sensor.

### **1.3.1 SHACK-HARTMANN WAVEFRONT SENSOR**

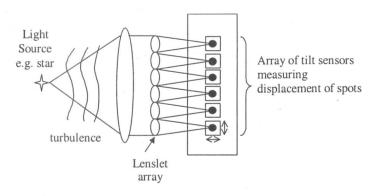

A Shack-Hartmann wavefront sensor uses an array of microlenses<sup>1</sup> to sample the optical wavefront as shown in Figure 1.6. If the incident beam had a flat wavefront, the light falling on each lenslet would be focused at the centre of each tilt sensor. If instead the wavefront is not flat but distorted, the spots obtained by the lenslets will deviate from the centre and by measuring this deviation, the local wavefront tilts are obtained. To remove alignment errors sometimes a reference plane wave beam is used and the deviation is then measured from the reference positions obtained [Tyson 1998].

<sup>&</sup>lt;sup>1</sup> The Shack-Hartmann wavefront sensor is an improvement over the basic Hartmann test which uses an array of hard apertures instead of the lenslet array. The Shack-Hartmann samples the entire wavefront and has the advantage of better photon efficiency. The disadvantage is in the cost of the microlenses and the difficulty in the optical alignment.

Figure 1.6 Shack-Hartmann wavefront sensor

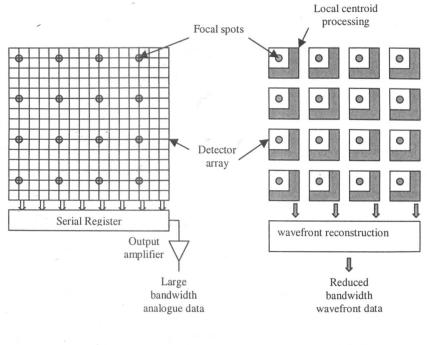

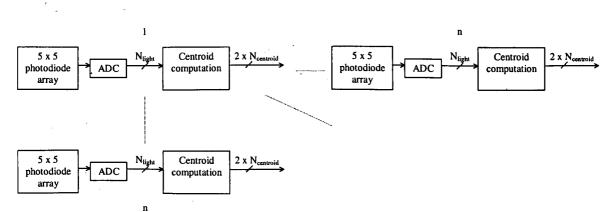

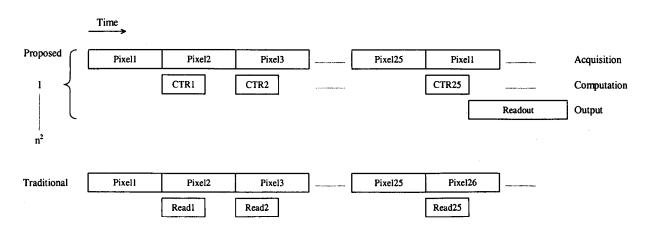

Traditional CCD systems for Shack-Hartmann wavefront sensing use the CCD to sample the entire wavefront and entire array of spots need to be read out before they are processed leading to a data bottleneck. This bottleneck is illustrated in Figure 1.7 in comparison with our proposed system, where each local wavefront tilt is measured by a local tilt sensor with its own detector array and local centroid processing. The parallel readout and processing of the raw data into reduced bandwidth centroid data will allow faster frame rates to be achieved. In addition, the array of tilt sensors can be linked to a matrix processor to reconstruct the estimate of the complete wavefront. Once calculated, the reduced bandwidth wavefront data can then be transferred off-chip. Hence, as a result of parallel processing, the data rate is independent of the number of tilt sensors employed.

(a) Traditional CCD systems

(b) Wavefront sensing with local centroid processing

#### Figure 1.7 Integration of on-chip centroid processing to remove data bottleneck

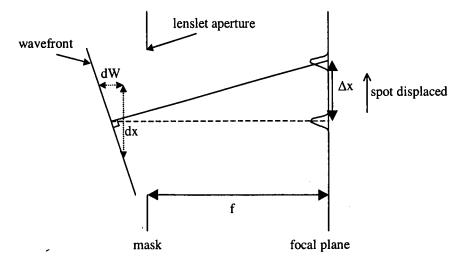

Assuming that at each tiny local portion of the wavefront the only aberration is the tilt, the local wavefront tilt can be linearly related to the displacement of the centroid position from its centre or reference position, as illustrated in Figure 1.8 and given by:

$$\text{Tilt} = \frac{dW}{dx} = \frac{\Delta x}{f} \tag{1.1}$$

where x is the displacement of the centroid and f is the distance of the subaperture from the focal or measurement plane and  $f \gg maximum dW$  over the entire subaperture. From these local wavefront tilts, the entire wavefront can be reconstructed and this will be covered further in Chapter 5.

Figure 1.8 Relationship between local wavefront tilt and displacement of the centroid (for a single lenslet of Figure 1.6)

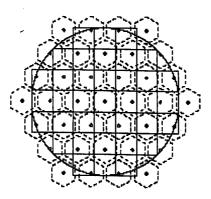

The size of the subaperture required for correct measurement of the wavefront is given by the distance over which the subaperture can pass a coherent beam, i.e. over which the optical phase distortion is highly correlated. In the case of atmospheric optics, this is given by Fried's coherence length,  $r_o$ , which has a dependence of  $\lambda^{6/5}$  with wavelength,  $\lambda$ , and as such astronomical adaptive optics is usually performed in the infrared. Another factor to consider is the number of degrees of freedom required, that is, the number of actuators in the wavefront corrector, and this is closely related to the number of subapertures required. There should be roughly one actuator corresponding to each patch of sky equal in size to Fried's coherence length [Mansell 2000], so the number of subapertures required, N, will be:

$$N \sim (D/r_0)^2$$

(1.2)

where D is the size of the entire pupil or wavefront. Hence the longer the wavelength the lower the complexity.

The Shack-Hartmann wavefront sensor is simple to construct, robust with no moving parts, compact and is by far the most common and established wavefront sensor. It offers high accuracy, reproducibility and a wide dynamic range [de Lima Monteiro 2002]. The work done in this thesis focuses on the use of a Shack-Hartmann wavefront sensor because of the high level of integration possible but it is by no means the only option open to designers of adaptive optic systems. The following section will briefly describe the other wavefront sensing techniques available and why these are less suitable for the purpose of this work.

#### **1.3.2 OTHER WAVEFRONT SENSORS**

The choice of wavefront sensor is very much dependent on the application. Several other common wavefront sensing techniques include interferometers, phase diversity, curvature wavefront sensors and the relatively new pyramid wavefront sensors. Interferometric methods include the lateral shear interferometer which measures the wavefront slope or the first derivative of the phase and the point diffraction interferometer which measures the phase of the wavefront directly [Tyson 1998]. The lateral shear interferometer works by splitting the beam and introducing a lateral shear on one arm and measuring the difference or interference between these two beams. The point diffraction interferometer also generates its own reference but does this by capturing a small part of the beam and expanding this as a plane wave reference. In general, interferometric methods of wavefront sensing require monochromatic, highly coherent sources to work making them unsuitable for certain applications such as astronomical imaging. They are also vibration sensitive, expensive and wavefront extraction is complicated so real-time analysis is difficult. Unlike the Shack-Hartmann, they suffer from phase ambiguity of phases exceeding  $2\pi$  and they cannot be used for pulsed sources. However, the point diffraction interferometer for example,

performs better than the Shack-Hartmann wavefront sensor in strong scintillation where phase discontinuities make the use of linear reconstruction difficult.

Another technique called phase diversity retrieves the phase from the analysis of two simultaneous images, one in-focus and the other defocused [Jefferies 2002]. This method has the advantage of not having any particular requirement on the optical beam and can be used with greatly extended sources. But the algorithm is non-linear and hence slow so it is often used as a post-processing technique for measuring aberrations and deblurring images.

The curvature wavefront sensor works by measuring the irradiances at two planes at the same distance but on opposite sides of the focal point [Roddier 1998b]. By solving the irradiance transport equation that relates the irradiances on the two planes, the curvature of the wavefront can be obtained. They have the advantage of being cheaper and more sensitive than the Shack-Hartmann. However, the equation is non-linear and its solution is not trivial [de Lima Monteiro 2002], and they are difficult to implement for systems that require large number of degrees of freedom such as in highly segmented telescopes [Jefferies 2002] and are only suited for low order systems. On highly segmented mirrors they could still be used for the tip/tilt alignment or the alignment of the primary mirror segment. In confocal microscopy, curvature sensing does not work well due to strong diffraction effects.

Pyramid wavefront sensors work by focusing the wavefront onto the central vertex of a glass pyramid which splits the beam into its four parts with the four edges acting like four Foucault knife edge tests and the images contain information of the aberration present in the wavefront. Pyramid wavefront sensors offer higher sensitivity than Shack Hartmann wavefront sensors and also allow variable gain which makes them useful in wide field adaptive optics. However the fabrication of the pyramids is no simple matter. The quality of the edges between the faces of the pyramids and the size of the roof at the apex of the pyramid are critical [Canadian VLOT Working Group 2003]. Manufacturing of single pyramid structures using the classical figuring and polishing technique is a time consuming process and the production of a large number of identical pyramids is still being developed. A new development, the hybrid curvature and gradient sensor enables one to obtain information on the local curvature as well as the local wavefront tilts or gradients while maintaining the simplicity of the Shack-Hartmann wavefront sensor [Paterson 2000]. The sensor uses quad cells placed at the foci of an array of astigmatic lenslets and the curvature signal is obtained from the difference of the pair of diagonal elements of the quad cell. Experimental results of this design have yet to be published.

Several factors make the Shack-Hartmann wavefront sensor the choice for an integrated wavefront sensor not least of which is that it requires only simple processing in finding the spot positions which can easily be integrated at the sensor level to reduce the amount of data to be sent off chip. Lower resolution imagers can be used in finding the centroid position, instead of obtaining complicated fringe data in interferometric methods for example. The linear relationship between the spot displacement and the local wavefront tilt also means a simple linear reconstruction technique can be used. This translates to fast real-time correction of wavefront aberrations. Integration could also lead to a reduction in size and costs in many applications.

### **1.4 CENTROID DETECTION**

The fundamental process performed in a Shack-Hartmann wavefront sensor is the detection of the optical centroids. Optical position-sensitive detectors (PSDs) detect the centroid position of a light spot projected on their surface and can be divided into two broad categories namely lateral-effect PSDs and multi-element PSDs [Sharman 2002]. Besides adaptive optics, optical position sensing has numerous commercial, industrial and laboratory applications. In the manufacturing process position-sensitive devices are used to characterize lasers, align optical systems, and calibrate and analyze machinery. PSDs are also used as triangulating sensors in various domestic appliances for switching the appliances on and off by detecting the presence of a body. They are also used in the feeding of paper in fax machines and printers and in the reading of disc tracks in CD players.

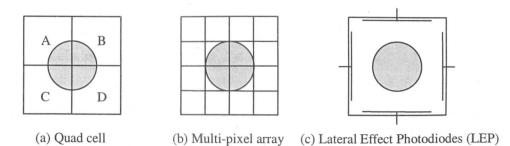

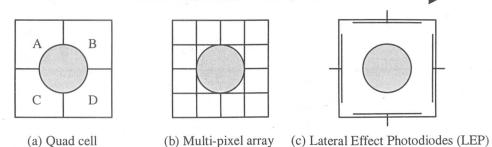

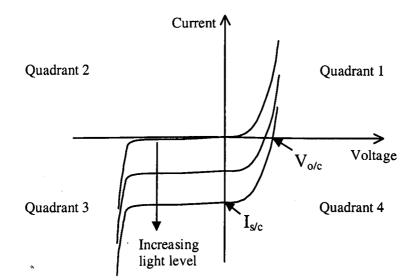

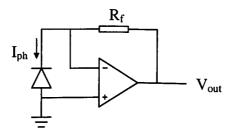

#### **1.4.1 LATERAL EFFECT PHOTODIODES (LEP)**

LEPs, as shown in Figure 1.9 (c), consist of a single resistive sheet formed by a p-n junction. The photogenerated charge carriers in the silicon move towards the appropriate electrode where the photocurrent at each electrode is inversely proportional to the distance between that electrode and the centroid of the incident light beam. Lateral effect PSDs are usually operated under reverse bias. Different geometries and positioning of the electrodes in lateral effect PSDs will give rise to tradeoffs in terms of linearity, sensitivity and resolution [Wang 1989].

A lateral effect PSD requires large uniform sheet resistance for linear operation, which is not readily available in a standard CMOS process making integration with circuitry difficult [de Lima Monteiro 2002] and hence unsuitable for the aims of this work. However, the performance of the LEP shall be compared with other PSD structures in Section 1.4.3.4.

#### **1.4.2 MULTI-ELEMENT PSD**

Multi-element PSDs consists of separate active areas. The simplest two-dimensional multi-element structure would be the quad cell, shown in Figure 1.9 (a). Larger structures are termed multi-pixel arrays. Like LEPs, quad cells have simple readout schemes. The position of the incident spot is determined by the comparison of the signals from the four quadrants as illustrated in Figure 1.9(a) and described below:

$$x = [(B+D) - (A+C)] / [A+B+C+D]$$

y = [(A+B) - (C+D)] / [A+B+C+D] (1.3)

For multi-pixel arrays, the position of the spot can be found either by simply finding the maximum signal in the array, and this is termed binary position sensing [Makynen 1998], or by finding the normalized first order moment of the signals of all the pixels in the array [Horn 1986] and this is given by:

$$C(x) = \frac{\sum r_{xn}I_n}{\sum I_n}; \qquad C(y) = \frac{\sum r_{yn}I_n}{\sum I_n}; \qquad (1.4)$$

where  $r_{xn}$  is the displacement in the x-direction of pixel n  $r_{yn}$  is the displacement in the y-direction of pixel n  $I_n$  is the light (photocurrent) level of pixel n

This essentially finds the weighted average of the different elements. Finding the weighted average offers the advantage of subpixel accuracy at the expense of more complicated processing. Higher order moments can also be found. The second order moment for example can be used to give the axis of least inertia or orientation of the imaged object [Standley 1991]. In the field of computer vision, the centroid and higher order moments are often used for character and object recognition [Cash 1987, Dudani 1977, Low 1998] as well as image compression [Karadimitiou 1998].

Other methods for computing a centroid from multi-pixel arrays also exist, such as the median-sum method used by the students of Johns Hopkins University [Dickinson 2003] for tracking objects, which was motivated by the Robocup competition where robots are built to play soccer. In this method, the row and column currents are summed and the median of these currents represent the centroid. This technique has the advantage of not requiring complex mathematical processing but is only accurate when a large number of pixels are used. Also this technique does not provide subpixel accuracy.

Another technique for determining the centroid of an object is by fitting a suitably defined PSF to a series of images [Fosu 2004]; a Gaussian function for stellar images for example. This method can only be used when the image is spread over more than four pixels but is said to give better accuracy than the moment analysis method. However, it is computationally intensive and complex making integration and real-time operation difficult.

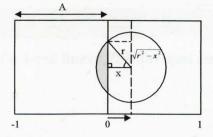

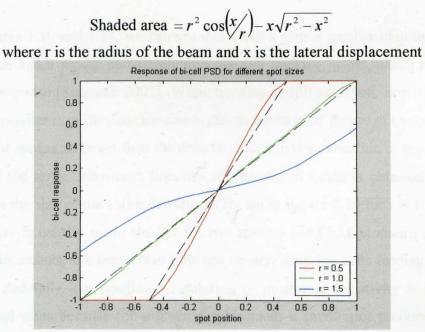

#### **1.4.3 MULTI-ELEMENT PSD PERFORMANCE**

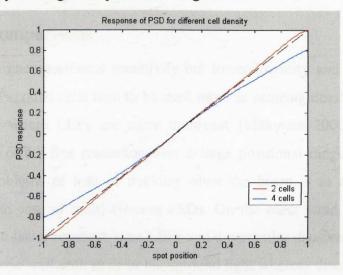

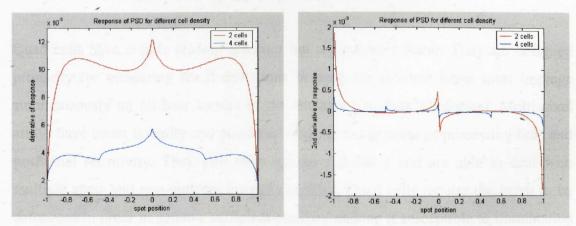

Pixelated position sensitive devices are typically evaluated in terms of linearity, positional sensitivity and positional range. These are affected by the detector size<sup>2</sup>, the cell density i.e. the number of cells for a given detector size, the gap between the cells and the intensity profile of the spot. Consider a uniform circular beam incident on a bi-cell, which is basically a 2-cell device which measures position in 1 dimension. The results of sweeping the beam of varying sizes across the cells are simulated and shown in Figure 1.10. This case is then extended to a 4-cell linear array and the results are shown in Figure 1.11. Note that for the simulations, truncation of the beam in the vertical direction is ignored. That is the height of the cells are infinitely long and the problem is limited to one dimension. These results shall be discussed in terms of spot size, cell density and beam intensity profile.

Figure 1.10 Response of a bi-cell PSD for spot sizes of different radius, r

$<sup>^{2}</sup>$  Detector size is the size of the entire array whereas the cell size is the size of a single element or pixel in the array.

Figure 1.11 Response of a 4-cell linear PSD for spot sizes of different radius, r

#### 1.4.3.1 Spot size

From Figures 1.10 and 1.11, we can see that when a spot is smaller than the size of a cell or pixel and it moves completely into one cell tracking is lost, which results in a step-like response [Sharman 2002]. While tracking is still achieved, non-linearity for spot sizes smaller than the detector size is due to the circular nature of the beam. Non-linearity for spot sizes larger than the detector is due to the truncation of the beam as it moves off the array. Maximum linearity and positional range is obtained when the spot size is the size of the entire detector as shown in Figure 1.10 for r = 1. However, the spot size is usually made smaller for two reasons [de Lima Monteiro 2002]. For large displacements, the beam may impinge on neighbouring cells leading to optical crosstalk. Secondly, the positional resolution or positional sensitivity is higher for smaller spot sizes because for a given displacement a small spot produces a much bigger differential signal.

#### 1.4.3.2 Cell density

The larger the cell density the better the linearity [de Lima Monteiro 2002]. This can be seen from the differential and double differential of the PSD response of a bi-cell and 4-cell linear array in Figure 1.12 (b) and (c). The downside is that the positional sensitivity is poorer as indicated by the slope of the PSD responses. Also larger cell density means more complicated processing and longer processing time. As we have seen, positional sensitivity can be improved by making the spot size smaller. There is a trade-off between linearity and positional sensitivity. Multi-pixel arrays are able to deal better with smaller spot sizes, and likewise for a given spot size of a few pixels, the larger the array the larger the positional range achievable.

(a) Bi-cell and a 4-cell linear array PSD response

(b) Differential of bi-cell and 4-cell PSD response (Fig. (a))

(c) Double differential of bi-cell and 4cell PSD response (Fig. (a))

#### **1.4.3.3 Intensity profile**

The effect of the beam shape and intensity profile also needs to be considered. The response of a quad cell is only linear over the whole range for a rectangular or square beam. With a circular beam, linearity is only achieved over the central region of the quad cell. The situation is even worse for laser beams which have a Gaussian profile [de Lima Monteiro 2002]. For a Gaussian beam, maximum linearity is not obtained with a beam the size of the quad cell but of that smaller due to the infinite extent of a Gaussian beam. With a Gaussian beam incident on a multi-pixel array, typically a spot size of about 1 to 2 pixels would then be suitable for maximum linearity, sensitivity and positional range.

#### **1.4.3.4 PSD comparisons**

Because of its higher positional sensitivity but lower linearity and positional range compared to LEPs, quad cells tend to be used more as centring devices than as linear position sensors where LEPs are more dominant [Mäkynen 2000]. As a custom device, the LEP offers fine resolution over a large positional range as there are no gaps and no problems of loss of tracking when the beam is in a single detector segment as in the case of multi-element PSDs. On the other hand, quad cells have lower noise and a faster response than LEPs and a particular disadvantage of LEPs is that it does not cope well with stray or background light whereas discrete detectors are able to remove this somewhat by applying a threshold.

Quad cells have simple readout schemes but are not very linear. They are designed primarily for measuring small deviations because the incident beam must impinge simultaneously on all four sectors of the detector [On-Trak Photonics]. Multi-pixel arrays have better linearity and positional range at the expense of processing time and positional sensitivity. They also offer greater flexibility and are able to deal with multiple spots and non-uniform intensity profiles. Quad cells require the beam to be defocused in order to achieve sufficient linearity making it susceptible to illumination fluctuations [Mäkynen 2000], that is, smaller spot sizes deal better with scintillations due to atmospheric turbulence. The relative performance of the different PSD structures can be summarised as in Figure 1.13.

Increasing linearity and positional range, decreasing positional sensitivity

Figure 1.13 Performance of the different PSD structures

With any multi-element detector, the issue of crosstalk arises and requires mentioning. There are two possible sources of crosstalk; crosstalk from other elements or cells and crosstalk from the substrate. Crosstalk from outside the array due to diffused carriers actually improves the linearity by increasing the signal at the edges and gives the appearance of larger pixel size at the edges. However, crosstalk from within the array serves to average the centroid value towards the centre leading to a reduction in positional sensitivity.

#### **1.4.4 CENTROID PROCESSING**

In the previous section it was shown how lateral effect photodiodes (LEP), quad cells and multi-pixel arrays are used for the purpose of centroid detection. In this section the processing techniques in computing the centroid from these architectures are presented. Table 1.1 shows a summary of the work done by other groups capable of obtaining optical centroids using standard CMOS or BiCMOS processes. Most LEP systems have the processing performed off-chip because the LEP itself is not usually fabricated on a standard CMOS process due to the high non-linearity obtained. Turner [Turner 1994] demonstrated a LEP in standard CMOS with photocurrents measured externally at a maximum bandwidth of 2.4 kHz. The reported resolution was approximately 0.25µm but with non-linearity at the edges reaching 40%. Centroid processing for quad cell and multi-pixel array architectures, on the other hand, can be readily integrated on-chip.

| Application                     | General purpose<br>machine vision<br>sensor                                                                             | Ophthalmology                                                                          | Robot vision                                                                                                                                       |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Positional</b><br>resolution |                                                                                                                         | 17μm (1.25<br>pixel<br>uncertainty,<br>alternate<br>pixels for x<br>and y<br>centroid) | 120µm<br>(1 pixel)                                                                                                                                 |

| Bandwidth                       | N/A (Bit-serial<br>processor in<br>each column.<br>Multiplication<br>takes 3b <sup>2</sup> cycles<br>of 33MHz<br>clock) | 300 Hz (30pW detectable power)                                                         | 20 kHz                                                                                                                                             |

| Pixel<br>size                   | 9.5µm<br>(fill<br>factor:<br>60%)                                                                                       | 17µm                                                                                   | 120μm<br>(fill<br>factor:<br>5.7%)                                                                                                                 |

| Array<br>size                   | 1536x512<br>pixels                                                                                                      | 8x8 array<br>of 21x21<br>pixels                                                        | 23x23<br>pixels                                                                                                                                    |

| Process                         | 0.35µm<br>CMOS                                                                                                          | 0.35µm<br>CMOS                                                                         | 0.6µm<br>CMOS                                                                                                                                      |

| Architecture                    | Centre of gravity<br>calculation on 3-<br>10 bit digital<br>values                                                      | Winner Take All<br>(WTA) circuitry                                                     | Thresholding<br>(point masking<br>algorithm to<br>detect multiple<br>light), pulse<br>width<br>modulation<br>(lower switching<br>noise but slower) |

| Location                        | Integrated Vision<br>Products (IVP),<br>Sweden                                                                          | Kirchoff Institute<br>of Physics                                                       | Future-<br>University-<br>Hakodate, Japan                                                                                                          |

| Author,<br>Year                 | Johansson,<br>2003                                                                                                      | Nirmaier,<br>2003                                                                      | Akita, 2002                                                                                                                                        |

| Adaptive optical systems         |                |                |                               |               |            |               |                 | 1.4µm for a Optical profile | testing         |                |               |                 |           |                | a 3D measurement | ([i       |             |            |             |             |            |              | tm Ophthalmology   | (1.85 pixel | uncertainty, | alternate x/y |

|----------------------------------|----------------|----------------|-------------------------------|---------------|------------|---------------|-----------------|-----------------------------|-----------------|----------------|---------------|-----------------|-----------|----------------|------------------|-----------|-------------|------------|-------------|-------------|------------|--------------|--------------------|-------------|--------------|---------------|

|                                  |                |                |                               |               |            |               |                 | 200 Hz closed- 1.4µr        |                 |                | wavefront     | reconstruction, | 3.125 kHz | sensor readout | 2 kHz 40µm       | (1 pixel) | -           |            |             |             |            |              | 500 Hz (1nW 17.6µ  | ,           | power) uncer | alterna       |

| 1                                |                |                |                               |               |            |               |                 | 600µm                       | ×               | 600µm 2        |               | <u></u>         | <u></u>   | S              | 40µm 2           | (fill     | factor:     | 18.05%)    |             |             |            |              | 17.6µm 50          |             | ď            |               |

| -<br>-                           | r              |                |                               |               |            |               |                 | 8x8 quad                    | cells           |                |               |                 |           |                | 64x64            | pixels    |             |            |             |             | -          |              | - 16x16            | array of    | 19x19        | pixels        |

| AMI 0.5µm<br>n-well              | CMOS for       | translinear    | amplifier                     | (rest of chip |            | fabricated)   |                 | 1.6µm                       |                 | process        |               |                 |           |                | 0.5µm            | CMOS      |             |            |             |             |            |              | 0.6µm n-           | well CMOS   |              |               |

| Quad cell (on-<br>chip wavefront | reconstruction | using resitive | grid to solve 2 <sup>nd</sup> | derivative of | phase from | adjacent quad | cell centroids) | Quad cells (off             | chip centroid   | computation by | PC)           |                 |           |                | Thresholding     | (with     | logarithmic | sensor and | correlation | circuit for | background | suppression) | WTA                |             |              |               |

| <br>Wireless (MSW),              | Texas          | Instruments    | .,                            |               |            |               |                 |                             | Instrumentation | , De           | University of | Technology      |           |                | University of    | Tokyo     |             |            |             |             |            |              | Kirchoff Institute | of Physics  | ~            |               |

| Ambunao,<br>2002                 | -              |                |                               |               |            |               |                 | de Lima                     | Monteiro,       | 2002           |               |                 |           |                | Oike, 2002       |           |             |            |             |             |            |              | Droste,            | 2001        |              |               |

| Object tracking,<br>navigation, deep-<br>space optical<br>communications | Adaptive optical systems                                                                                                   | Position sensing<br>applications with<br>simultaneous<br>multiple spot<br>detection | Pattern<br>recognition in<br>optical correlator<br>systems                  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 0.6μm<br>(0.05 pixel,<br>850mV<br>saturation)                            | 1                                                                                                                          | 4.3μm<br>(uniform<br>280μm spot,<br>100Hz)                                          | 0.25µm (up<br>to 40% non-<br>linearity at<br>edges)                         |

| 20 kHz (9x9<br>pixels) to 50<br>kHz (3x3 pixels)                         | 1                                                                                                                          | 1                                                                                   | 2.4 kHz for a single 2D LEP (photocurrents measured externally)             |

| 12µm                                                                     | 160µт<br>х<br>160µт                                                                                                        | 50µm<br>(30% fill<br>factor)                                                        | 400µт<br>х<br>180µт                                                         |

| 128x128<br>pixels                                                        | 2x2<br>(single<br>quad cell)                                                                                               | 16x16<br>pixels                                                                     | 2x1 LEPs                                                                    |

| HP 0.5µm<br>CMOS                                                         | 1.2µm<br>CMOS                                                                                                              | 1.2µm n-<br>well CMOS                                                               | 2μm n-well<br>CMOS                                                          |

| Capacitive array<br>(centroid<br>computation for<br>up to 9x9 pixels)    | Quad cell<br>(current-to-<br>voltage<br>conversion and<br>quad cell<br>differencing<br>circuits<br>integrated on-<br>chip) | Thresholding,<br>off-chip centroid<br>calculation of<br>binary image<br>map         | WTA for coarse<br>resolution, LEP<br>for fine<br>resolution                 |

| NASA's Jet<br>Propulsion<br>Laboratory,<br>California                    | The Klipsch<br>School of<br>Electrical &<br>Computer<br>Engineering,<br>New Mexico<br>State University                     | University of<br>Oulu, Finland                                                      | Optoelectronic<br>Computing<br>Systems Center,<br>University of<br>Colorado |

| Pain, 2000                                                               | Furth, 1998                                                                                                                | Makynen,<br>1998                                                                    | Turner,<br>1994                                                             |

| Deweerth,   | Physics of        | Resistive array                                                        | 2µm                                           | 160x160       |                 |                  | -          | Development of                     |

|-------------|-------------------|------------------------------------------------------------------------|-----------------------------------------------|---------------|-----------------|------------------|------------|------------------------------------|

| 1992        | Computation       | (Differential                                                          | BiCMOS                                        | pixels        |                 |                  |            |                                    |

|             | Laboratory,       | transistor pair                                                        | process                                       |               |                 |                  | -          | inspired vision                    |

|             | California        | aggregates                                                             |                                               |               |                 |                  |            | systems                            |

| -           | -                 | image data to                                                          |                                               |               |                 |                  |            |                                    |

|             |                   | two output                                                             |                                               |               |                 |                  |            |                                    |

|             |                   | currents.                                                              |                                               |               |                 |                  |            |                                    |

|             |                   | Resistive array                                                        |                                               |               |                 |                  |            |                                    |

|             |                   | encodes<br>position)                                                   |                                               |               |                 |                  |            |                                    |

| Forcheimer, | Integrated Vision | Centre of gravity                                                      |                                               | 256x256       | 32µm            | 250 Hz           | 1          | General purpose                    |

| 1992        | Products (IVP),   |                                                                        |                                               | pixels        | (fill           |                  |            | d)                                 |

|             | Sweden            | bit data                                                               |                                               |               | factor:<br>48%) |                  |            | sensor                             |

| Standley,   | Massachusetts     | Uniform                                                                | 2µm CMOS                                      | 29x29         | 190µm           | 5 kHz            | ±0.3% of a | Robot vision                       |

| 1991        | Institute of      | resistive line for                                                     | process                                       | pixels        | ×               | 54               | 25 x 25    |                                    |

|             | Technology        | centroid,                                                              | Ι                                             |               | 190µm           |                  | square     |                                    |

|             |                   | quadratic                                                              |                                               |               |                 |                  |            |                                    |

|             |                   | resistive line for                                                     |                                               |               |                 |                  |            |                                    |

|             |                   | ų                                                                      |                                               |               |                 |                  |            |                                    |

|             |                   | (resistive grid                                                        |                                               | ·             |                 |                  |            |                                    |

|             |                   | aggregates 2D                                                          | <u>, , , , , , , , , , , , , , , , , , , </u> |               |                 |                  |            |                                    |

|             |                   | image to 1D                                                            |                                               |               |                 |                  |            |                                    |

|             |                   | problem)                                                               | :                                             | 0             | 1               | ** * * * *       |            |                                    |

| Connason,   | Alberta           | Resistive array                                                        | 3µm p-well                                    | 10X10         | 84µm x          | 3.33 kHz         | lµm        | Laser and process                  |

| 1990        | Microelectronic   |                                                                        | CMOS                                          | pixels        | 90µm            |                  |            | control                            |

|             | Centre, Canada    |                                                                        | process                                       |               |                 | -                |            | instrumentation,<br>tool alignment |

|             |                   | Table 1.1 Other research efforts capable of optical centroid detection | research effor                                | ts capable of | f optical ce    | ntroid detection |            | <b>)</b>                           |

#### **1.4.4.1 Quad-Cell Centroid Processing**

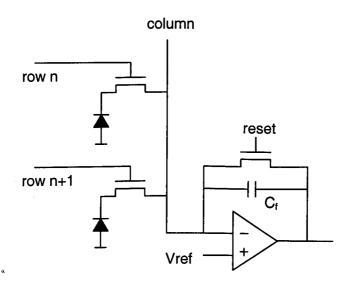

Processing using quad cells are relatively simple requiring only a minimum number of signals; two from each axis. De Lima Monteiro [de Lima Monteiro 2002] demonstrated an approach for an integrated Shack-Hartmann wavefront sensor using an array of 8 x 8 quad cells in a 1.6µm CMOS process. The sensor can be read out at a rate of 3.125 kHz but the current-to-voltage conversion and serial conversion of the analogue voltages into digital format was performed off-chip and the centroid computation was carried out on a PC. The resulting operating frequency of 260Hz was limited by the data acquisition card. Another quad cell centroiding approach, this time in analogue using a 1.2µm CMOS process, by Furth [Furth 1998], integrates the current-to-voltage conversion on-chip using passive and active loads as well as differencing circuits which computes the difference between the photocurrents in the x differencing circuits consist of double-differential and y-direction. The transconductance amplifiers. Experimental results were not reported. However, recently, Ambundo and Furth [Ambundo 2002] have incorporated the wavefront reconstruction on-chip by finding the second derivative of the phase by taking the difference between the centroid currents of neighbouring quad cells and injecting this result into a resistive grid which solves this second derivative to obtain the phase. Normalization allows the centroid computation to be independent of light intensity and was achieved using a modified current amplifier to divide the sum of the four photocurrents in the quad cell. Currently the system has only been simulated and yet to be fabricated and no performance results were shown.

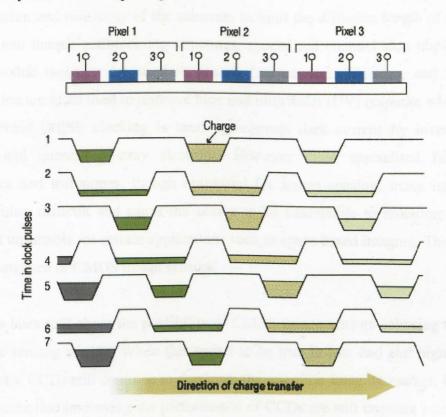

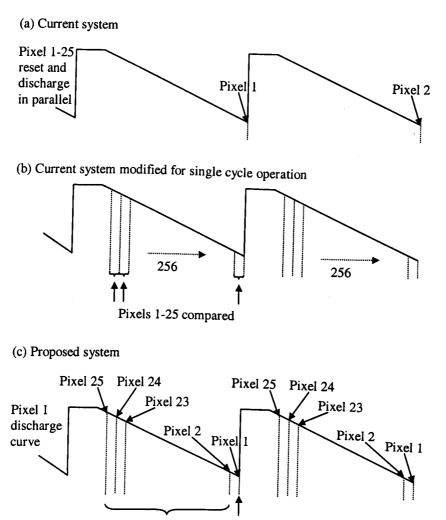

Charge-coupled devices (CCD) are multi-pixel arrays but when used in a Shack-Hartmann wavefront sensing system CCDs are typically<sup>3</sup> used as an array of quad cells with guard row and column pixels between them [Thompson 2002]. Due to the serial readout nature of CCDs, the entire wavefront has to be sampled and a whole frame of light spots read out before they can be processed. This results in a data

<sup>&</sup>lt;sup>3</sup> There are applications where the use of more pixels per subaperture than a quad cell is needed such as in varying seeing conditions. A multi-pixel array can easily be adapted for such circumstances at the expense of reduced signal-to-noise ratio and increased computational load.

bottleneck. Processing of individual light spot positions at the sensor level would alleviate this problem as only reduced bandwidth data need to be transmitted off-chip. However, circuit integration on CCDs remains difficult (see Section 1.5.5.1).

#### 1.4.4.2 Multi-Pixel Array Centroid Processing

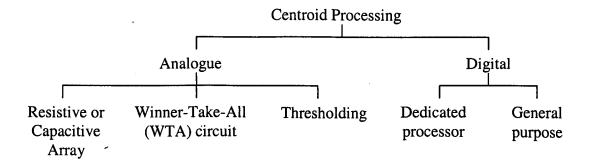

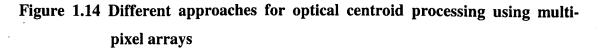

Processing using quad cells offer limited displacement range and require careful alignment of the null point of the system [Tyson 1998] as large offsets from the null point will reduce the dynamic range of the system and lead to significant non-linearity [Dillon 1999]. Using a multi-pixel array will allow the system to cope better with varying aberrations and seeing conditions. Efforts into incorporating centroid computation for multi-pixel arrays at the sensor level can be categorised into two basic approaches, analogue and digital and several different sub-approaches, as illustrated in Figure 1.14.

#### 1.4.4.2.1 Analogue Centroid Processing for Multi-Pixel Arrays

Most multi-pixel array approaches are performed in analogue, using either an analogue current division method capable of subpixel accuracy, or discrete binary position sensing techniques<sup>4</sup>. With the analogue current dividing method. photocurrents are divided on a uniform resistive array [Gonnason 1990, Standley 1991] or a linearly varying capacitive array [Pain 2000]. Both effectively compute the first order moment of the array photocurrents. With the uniform resistive array, the photocurrent of a pixel is divided on the line and the difference in output currents of the ends of the resistive line is directly related to the position of the incident light on the array. With a quadratic resistor line, the second order moment can be obtained and used to determine the orientation of the object [Standley 1991]. In addition to the basic resistive line, Deweerth [Deweerth 1992] used a current mirror and differential transistor pairs to establish feedback allowing the system to continuously respond to changes in spot position. However, non-idealities and mismatch in these additional circuitry caused offsets in the system. With the linear capacitive array, the pixel voltages are sampled onto separate sampling capacitors, the sizes of which are proportional to the integer row and column addresses, hence giving the inner products of the centroid computation of equation (1.4).

Binary position sensing effectively uses a form of thresholding technique to reject all photocurrent levels below a certain threshold level or below the largest signal level in the array or a collection of pixels. Many variations are possible but two commonly used circuits are the winner-take-all (WTA) circuit [Droste 2002, Nirmaier 2003] or some form of on-pixel comparator [Burns 2003, Makynen 1998]. Figure 1.15 shows the basic form of the WTA circuit and its  $I_D$  vs.  $V_{DS}$  characteristic. A WTA circuit consists of an array of competing cells with each cell consisting of two MOSFETs  $M_S$  and  $M_F$ .  $M_S$  senses the input current  $I_i$  while  $M_F$ , if activated, draws the output current  $I_o$ .

<sup>&</sup>lt;sup>4</sup> Digital centroid computation in this thesis refers to the computation of the centroid from several bits of digitized pixel values and not from a binary image map such as in the case of binary position sensing.

Figure 1.15 Basic topology and operation of a WTA circuit [Droste 2002]

Because all the  $M_S$  are identical and are gate-connected, they have the same  $I_D$  vs.  $V_{DS}$  characteristic. The one with the highest input current will generate the highest drain potential and hence the highest  $V_{GS}$  of all the  $M_F$ , therefore sinking most of the current source  $I_{src}$  and shutting off all other  $M_F$ . The computation is continuous in time and the winning output encodes the logarithm of its associated input since the M all the  $M_F$  are operating in subthreshold [Lazzaro 1988]. Saturation of the pixel is determined by the saturation of the WTA  $M_S$  MOSFETs and positional accuracy is limited to that of a single pixel. With this circuit, a very slow response time (several hundred ms) is obtained due to the large photodiode capacitance seen at the drain of  $M_S$ . The capacitance seen was reduced by using a regulated cascode configuration. Response time can be improved further by setting the drain of  $M_S$  to a defined value at startup and by introducing positive feedback into the WTA. But enabling feedback reduces accuracy of position detection due to mismatches. Nirmaier et al. [Nirmaier 2003]

introduced an interdigitated topology to the WTA concept by splitting the single WTA circuit into several groups. This has the advantage of increased robustness against defective outputs, reduced sensitivity to mismatch and faster response.

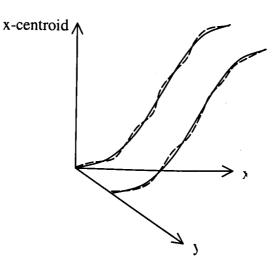

For analogue centroid computation utilizing destructive readout such as in the current division method, or for those utilizing the WTA algorithm, two discrete photodiodes are needed per pixel. One for the x-centroid and one for the y-centroid. This results in lower fill factor, sensitivity and a non-linear spatial response. De Lima Monteiro [de Lima Monteiro 2002] proposed the use of a spiral structure to reduce the non-linearity. With these architectures, the pixels in each row and column are tied together and the photocurrents along each row and column are summed so only two sets of current division or WTA circuits are needed per array, one for each axis, as illustrated in Figure 1.16. In a CCD this would be equivalent to binning all pixels in the row or column [Dillon 1999].

Figure 1.16 Use of two photodiodes per pixel and the summation of photocurrents along each row and column with analogue centroid computation [Droste 2002]

Standley [Standley 1991] used a uniform grid of resistors to aggregate the photocurrents in both the x and y-dimensions, hence eliminating the need for two photodiodes per pixel. However, this suffers from non-linearity due to the tolerance of on-chip resistors as well as increased power consumption and thermal noise. It also required the use of two resistive lines per axis instead of just one. This technique has limited usage in position sensing because the advantage of increased fill factor and sensitivity from removing the need of a second structure is lost by the need to

integrate a resistor at each pixel. However, its use in neural network structures for vision chips is common as interconnectivity between neighbouring pixels is desired.

Makynen [Makynen 1998] used global threshold current comparison per pixel to generate a binary image map and off-chip moment calculation of the binary map to obtain sub-pixel accuracy. Unlike the WTA circuit approach, it is able to deal with multiple beam spots and it does not require two structures per pixel. However, it does not deal well with non-uniform intensity profiles due to its binary representation and the extensive circuitry per pixel leads to low fill factor and sensitivity. With position sensing using on-pixel comparators, it is possible to use a ramp function of the threshold value, to obtain a more accurate centroid estimate as well as deal with non-uniform intensity profiles by obtaining several binary image maps at different threshold levels [Burns 2003]. However, this requires post-processing and several readouts of the array.

#### 1.4.4.2.2 Digital Centroid Processing for Multi-Pixel Arrays

Analogue centroid computation offers the advantage of high speed and high functional density but suffers from lack of flexibility and imprecision due to mismatches and tight tolerances of components. De Lima Monteiro [de Lima Monteiro 2002] found that there was significant spatial variation in on-chip polysilicon-array resistance which leads not only to the shifting of the zero response but also to the slope of the response curve, as per Figure 1.10. Well structures offer higher sheet resistance but has greater spatial variation and poorer temperature and voltage coefficients. Also, as CMOS technology scales, the advantage of speed and functional density of analogue over digital diminishes.

Digital centroid computation involves the analogue-to-digital conversion of the pixel values into several bits of data and computing a weighted average of the photogenerated signals. A generic 256 x 256 pixel array system with an on-chip image processor has been designed which performs several common image processing algorithms including centroiding at 250 frames/s [Forcheimer 1993, Forcheimer 1992]. Recently an even more advanced and larger array sized programmable image

sensor and processor has been developed by the same group [Johansson 2002]. However, in an adaptive optics system such as the Shack Hartmann wavefront sensor, a large number of tilt sensors are required but the pixel count of each tilt sensor can be minimal. Nonetheless, the work presented by the group is encouraging because it shows that it is possible to integrate complex digital circuits alongside a CMOS image sensor and still achieve low noise.

Another generic structure for image processing is the cellular neural network (CNN) architecture where each cell (pixel) senses a point of the input image and interacts with neighbouring cells to perform parallel-processing tasks on the input image [Roska 1993]. All cells operate in parallel and in continuous time so that high operation speeds are obtained [Dominguez-Castro 1997]. However, due to the locality of the connections, global image processing tasks such as centroid detection require longer processing times, and generic structures in general are not optimised for any particular task<sup>5</sup>.

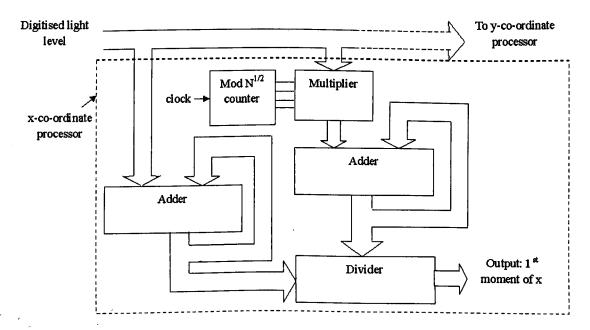

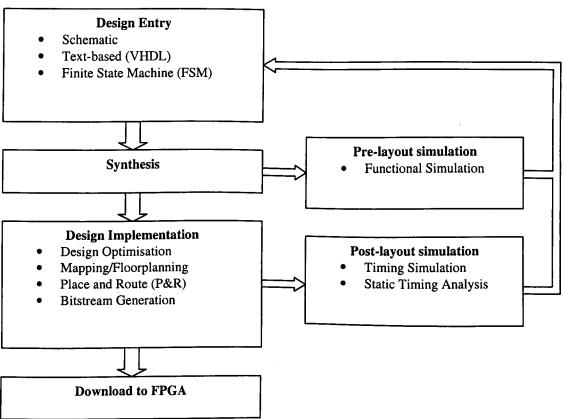

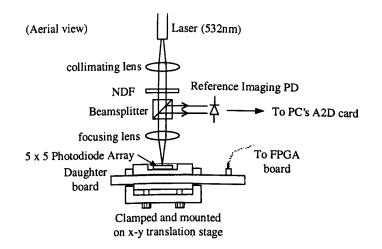

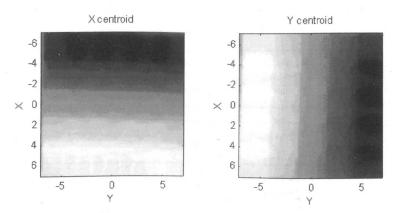

The approach taken in this work is to integrate dedicated local digital centroid processing at each subaperture to measure the local wavefront tilt. By performing the centroid computation of the subapertures in parallel, the processing speed is maximised and the amount of data to be sent off-chip is reduced. In addition to an increase in speed, a single-chip system will have an advantage of reduced system size, costs and power consumption over multi-chip systems. This work represents the only dedicated digital centroid processor designed and fabricated to date<sup>6</sup>.

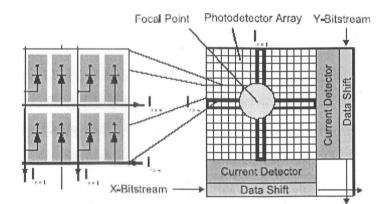

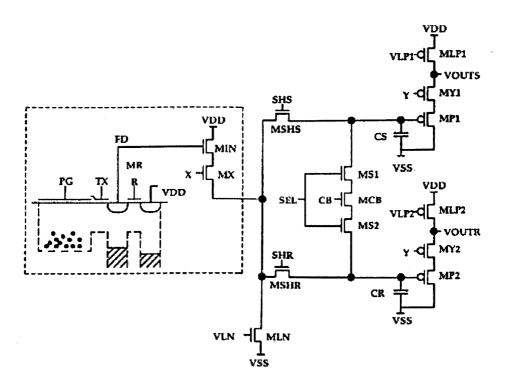

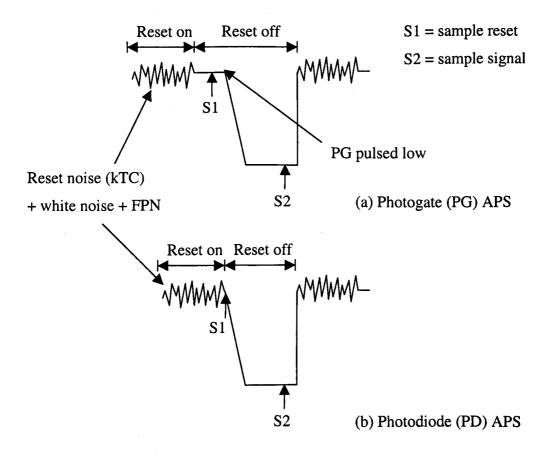

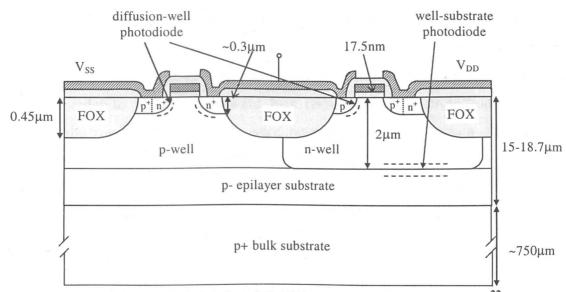

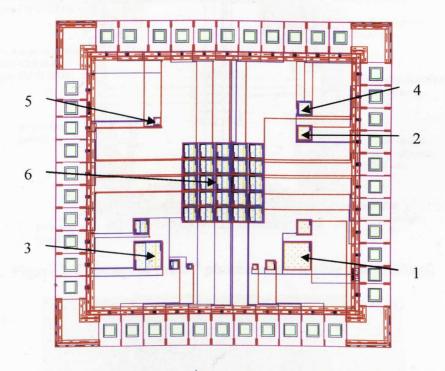

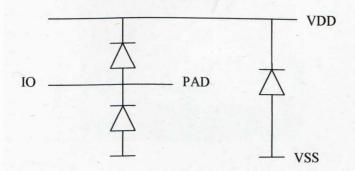

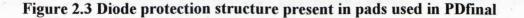

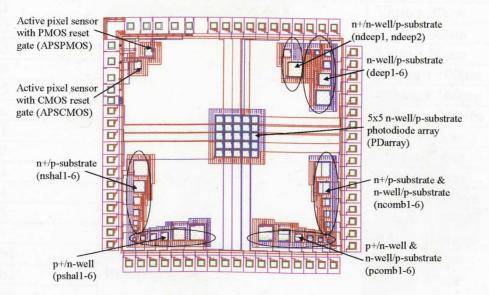

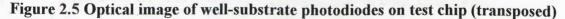

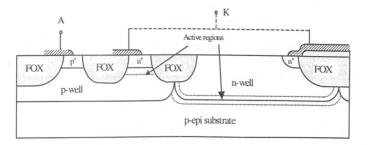

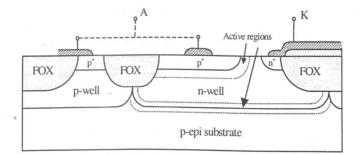

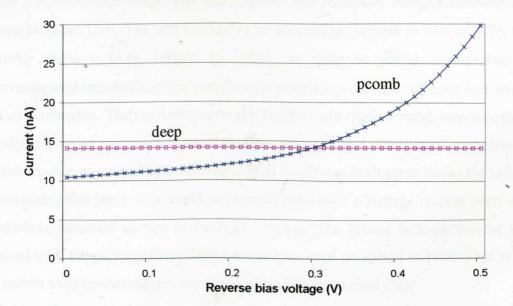

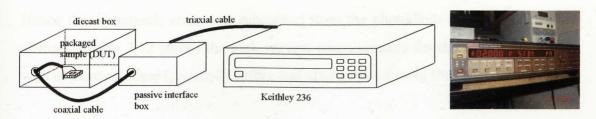

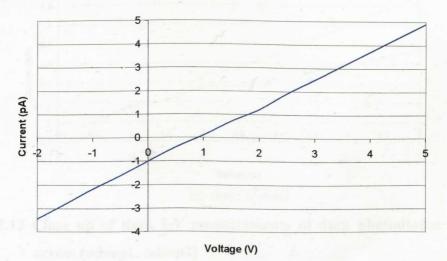

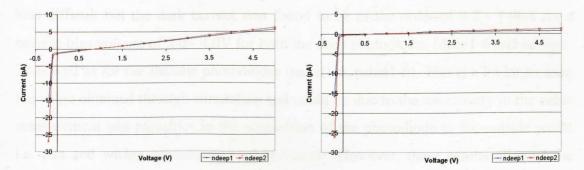

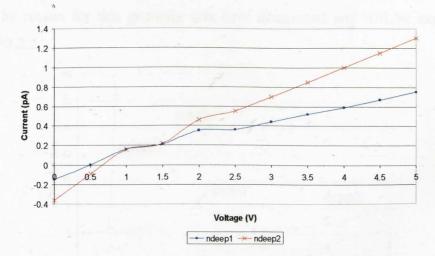

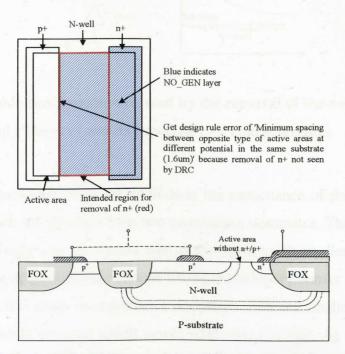

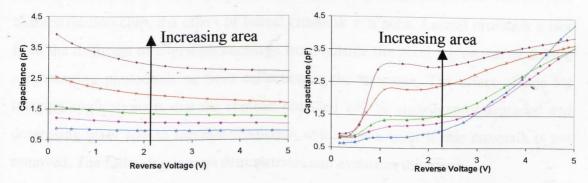

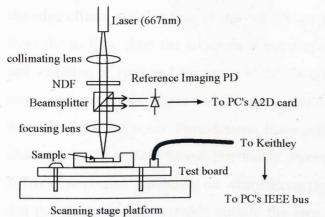

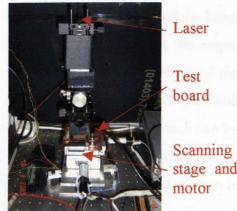

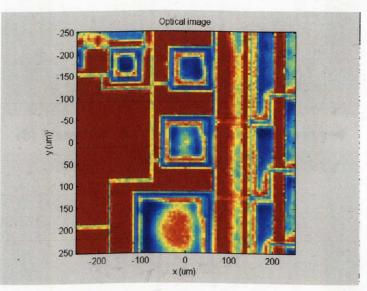

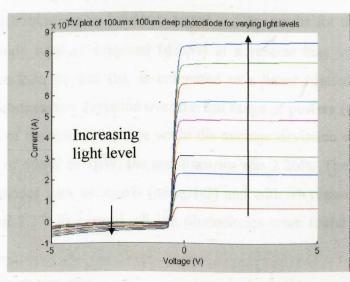

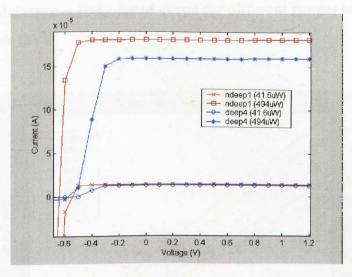

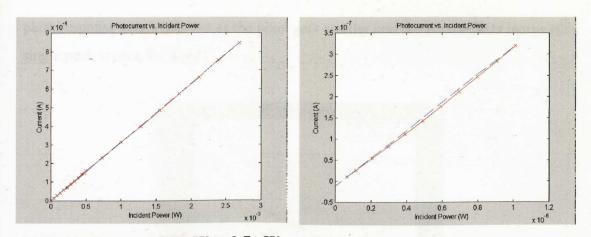

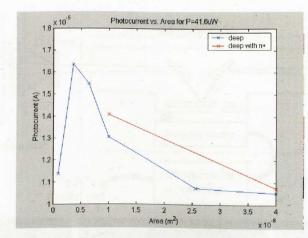

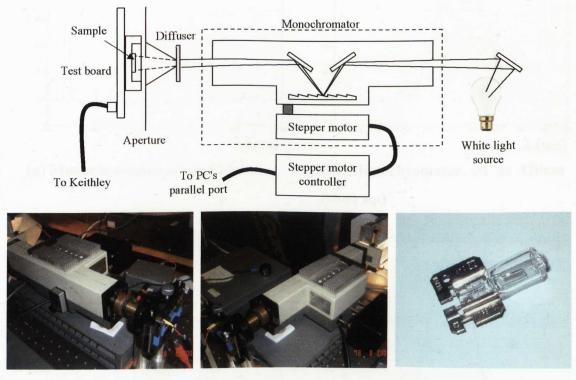

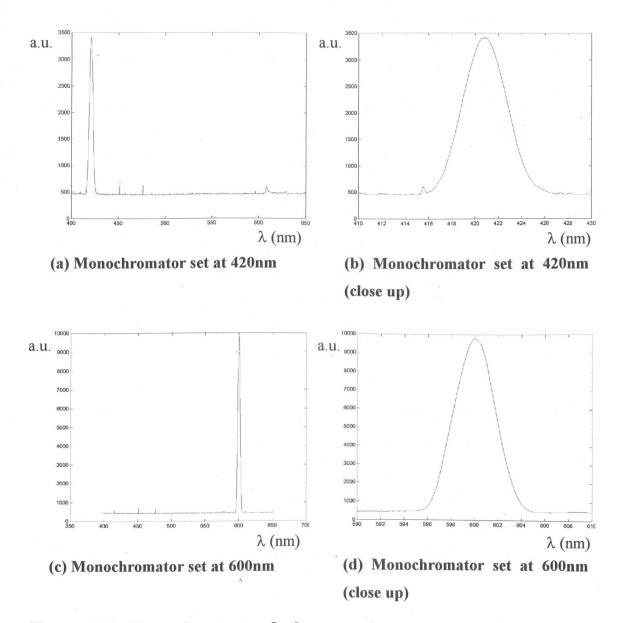

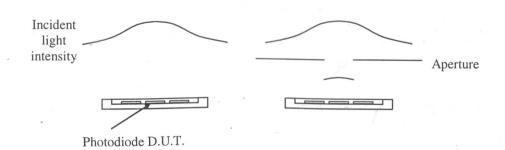

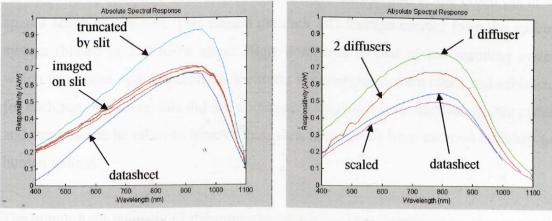

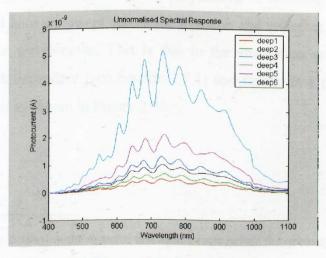

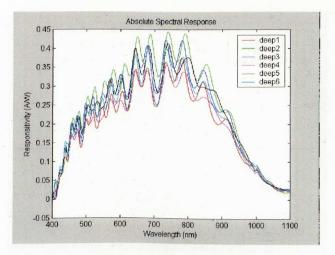

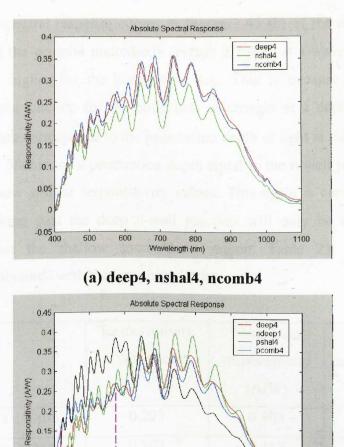

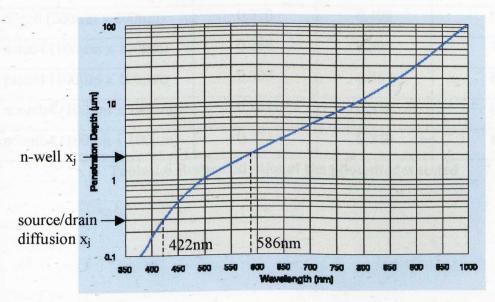

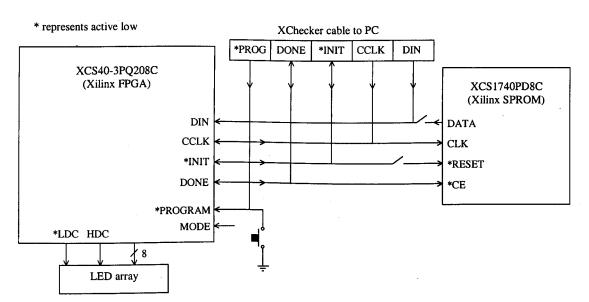

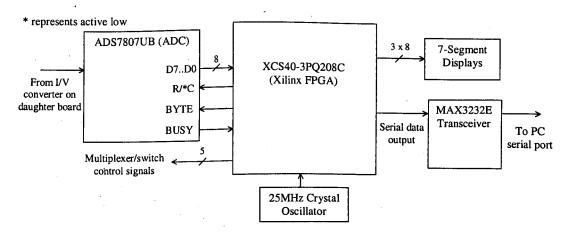

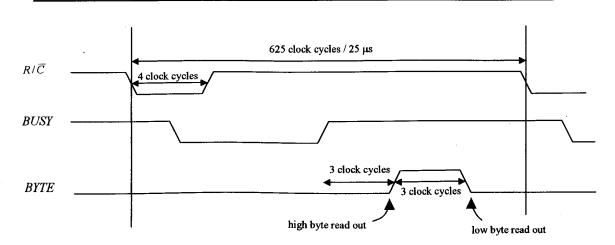

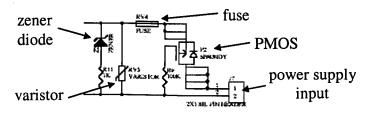

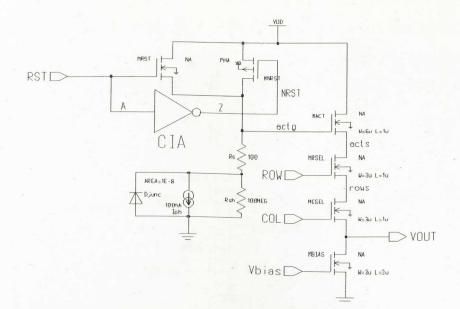

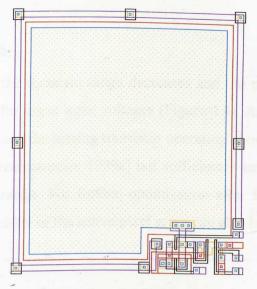

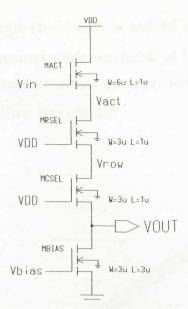

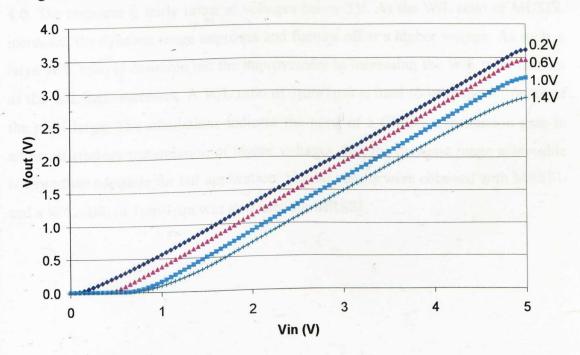

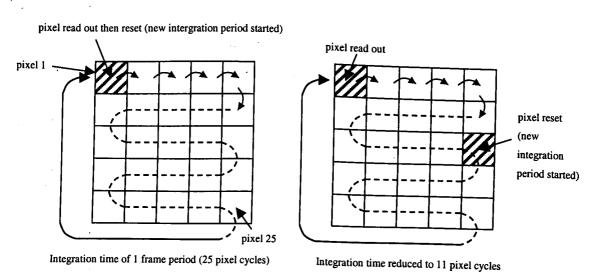

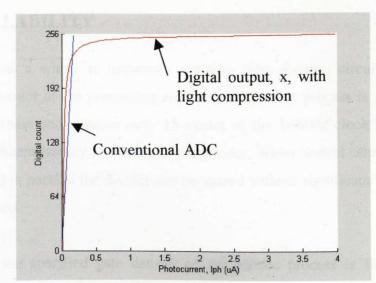

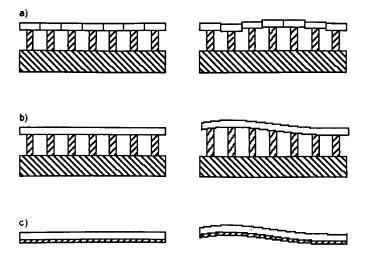

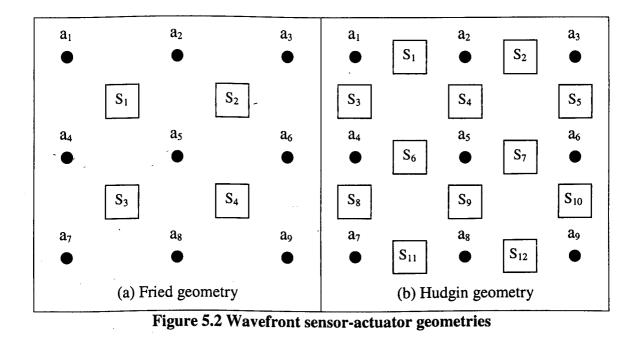

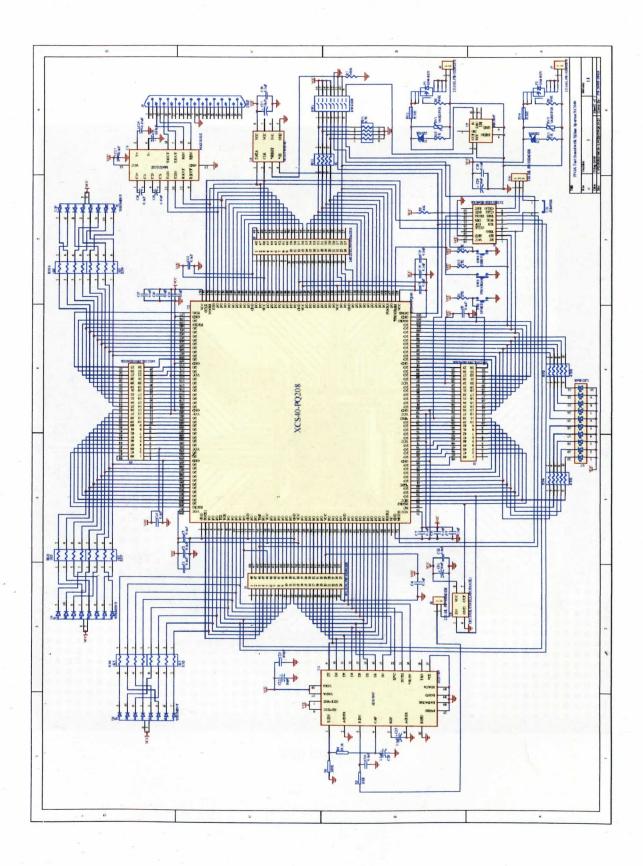

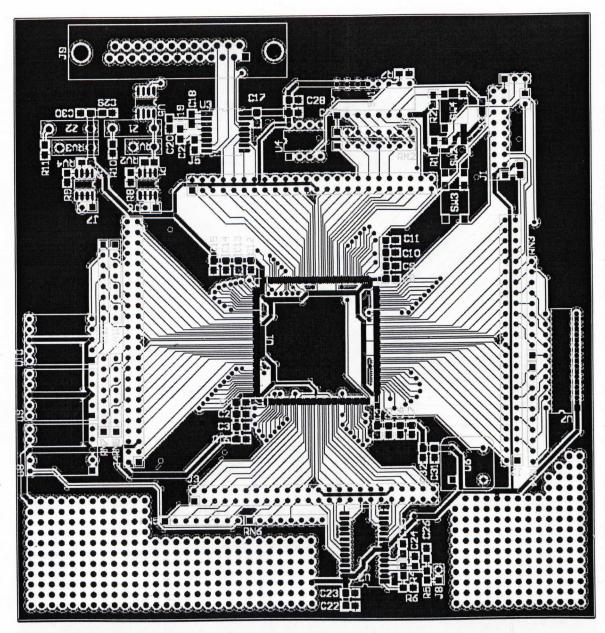

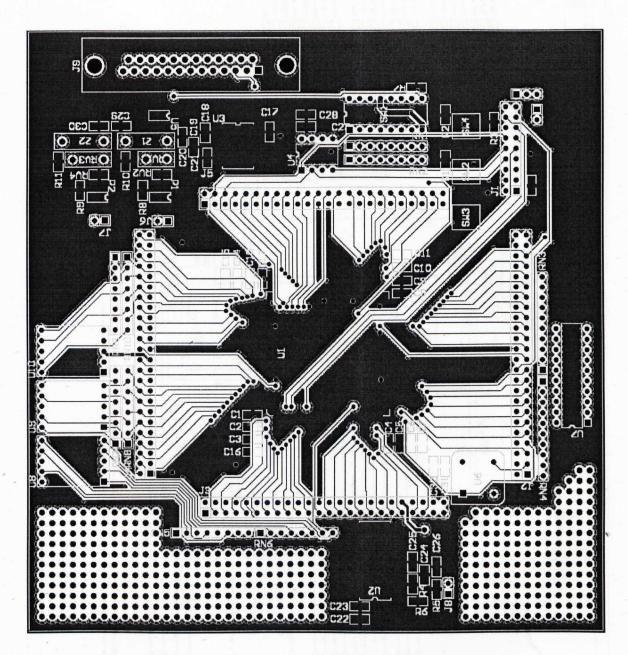

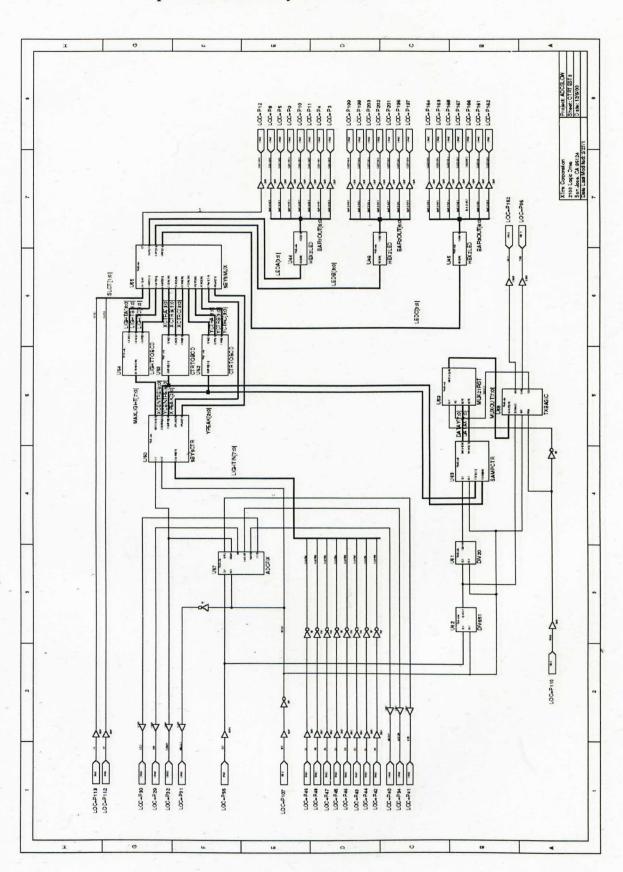

<sup>&</sup>lt;sup>5</sup> However, post-processing of a Shack-Hartmann subaperture image using artificial neural networks is capable of providing a more accurate estimate of the centroid location than with conventional linear estimators (1<sup>st</sup> moment calculation) [Montera 1996].