# CONTROL OF A STATCOM WITH SUPERCAPACITOR ENERGY STORAGE

Phinit Srithorn, M.Eng.

Thesis submitted to the University of Nottingham tor the degree of Doctor of Philosophy

June 2009

1'

To my dear parents and my brother, for their love and support to my study.

# Acknowledgements

I would like to express my sincere gratitude to my supervisor, Dr Mark Sumner of the Power Electronics, Machines and Control (PEMC) research group at the University of Nottingham for his expert guidance and patience throughout the course of my research. I would also like to thank Dr Dave Thomas for acting as internal examiner and Dr Li Zhang of the University of Leeds for acting as external examiner.

I am greatly indebted to Rajamangala University of Technology Isan, Thailand, and the Royal Thai Government for their generous financial support during my study in UK.

I would like to thank Dr Liangzhong Yao, Dr Ram Parashar, and Dr Martin Aten of AREVA T&D Technology Centre, Stafford, UK for giving me the opportunity to work in this research project, and particularly George Russell and Dr Ruchira Winthanage for their friendship. I would also like to thank Prof Noel Shammas and Prof Sarath Tennakoon, Staffordshire University for their advice during my time at Stafford, UK.

Many thanks are due to all my friends and colleagues at PEMC research group for questions answered, assistance rendered and discussions. Thanks also to all ground floor technicians for their support and friendly help over my research course at the University of Nottingham.

Last but not least, I would like particularly to thank my housemates, Jongkol Iammi and Kongpan Areerak who have made my life at Nottingham as home. Special thanks to Wannapa Kunpasuruang for her delicious food and cakes.

### Abstract

STATCOM (STATic COMpensator) has been used in electrical power systems as a shunt-connected compensator for voltage support and to improve power quality. Compared with the conventional compensators such as the synchronous condenser and the SVC (Static Var Compensator), the STATCOM has a faster speed of response to deal with dynamic and transient impacts. Although the STATCOM is capable of reactive power support to improve power quality, the ability to support real power is limited due to the insufficient energy storage capability of the conventional DC-link capacitor. Therefore, the application of the STATCOM to improving power system stability has been limited.

This thesis proposes a solution to enhance the performance of the STATCOM by adding supercapacitor energy storage to the DC-link of the conventional STATCOM. With the fast charge/discharge characteristics of the supercapacitors, the enhanced STATCOM can absorb and inject real power to the ac power grid virtually instantaneously. The control design of the STATCOM based on a vector control strategy is presented, including the design of an instantaneous reactive power controller based on a small-signal model of the ac power system. The control design of the supercapacitor energy storage system (SCESS) based on small-signal models of the dc-to-dc converter is documented. The STATCOM and the SCESS are controlled together using a feed-forward control technique. In addition, this thesis also proposes that the enhanced STATCOM can be applied to reduce instability and tripping due to the rate of change of frequency (ROCOF) protection devices caused by large load impacts. The amount of the energy required for the enhanced STATCOM to maintain the stability of the system is also discussed.

# Contents

-

| Cha  | pter 1 l                       | Power sys   | tem shunt-connected compensators                          |

|------|--------------------------------|-------------|-----------------------------------------------------------|

| 1.1  | Introdu                        | uction      |                                                           |

| 1.2  | Static VAr Compensators (SVCs) |             |                                                           |

|      | 1.2.1                          | Thyristo    | r Controlled Reactor (TCR)5                               |

|      | 1.2.2                          | Thyristo    | r Switched Capacitor (TSC)6                               |

|      | 1.2.3                          | Fixed Ca    | apacitor-Thyristor Controlled Reactor (FC-TCR)            |

|      | 1.2.4                          |             | r Switched Capacitor-Thyristor Controlled Reactor<br>CR)7 |

| 1.3  | STAT                           | ic COMp     | ensator (STATCOM)8                                        |

| 1.4  | A com                          | parison b   | etween STATCOM and SVC14                                  |

| 1.5  | Projec                         | t objectiv  | es17                                                      |

| 1.6  | Thesis                         | overview    | 7                                                         |

| ener | gy stor                        | age         | stem stability improvement using STATCOM with             |

| 2.1  |                                |             |                                                           |

| 2.2  |                                | _           | eration                                                   |

|      | 2.2.1                          | DG plan     | ts23                                                      |

|      |                                | 2.2.1.1     | Combined heat and power plant                             |

|      |                                |             | Renewable energy plant24                                  |

|      | 2.2.2                          |             | of DG on AC power system25                                |

|      |                                | 2.2.2.1     | Network fault level change                                |

|      |                                | 2.2.2.2     | Network voltage change                                    |

|      |                                | 2.2.2.3     | Power quality                                             |

|      |                                | 2.2.2.4     | System stability                                          |

| 2.3  | Analys                         | sis of inst | ability within system with DG29                           |

|      | 2.3.1                          | Instabili   | ty within system with DG30                                |

|      | 2.3.2                          | Energy s    | storage required                                          |

| 2.4  | Simula                         |             | generator supplying a system with a sudden load change    |

.

|            | 2.4.1                                       | A generator supplying a system with a sudden load change without support from STATCOM-ES | 38  |

|------------|---------------------------------------------|------------------------------------------------------------------------------------------|-----|

|            | 2.4.2                                       | A generator supplying a system with a sudden load change w support from STATCOM-ES       |     |

| 2.5        | Concl                                       | usions                                                                                   | 44  |

| Cha        | mton 2                                      | STATCOM                                                                                  | A.6 |

| Спа<br>3.1 | -                                           | uction                                                                                   |     |

| 3.2        |                                             | onnected power converter                                                                 |     |

|            | 3.2.1 Two-level three phase power converter |                                                                                          |     |

|            | 3.2.2                                       | Multilevel power converter                                                               |     |

|            |                                             | 3.2.2.1 Diode-clamped multilevel converter                                               | 51  |

|            |                                             | 3.2.2.2 Flying capacitor multilevel converter                                            | 52  |

|            |                                             | 3.2.2.3 Cascaded multilevel converter                                                    | 53  |

| 3.3        | Power                                       | flows between converter and ac grid                                                      | 56  |

| 3.4        | STAT                                        | СОМ                                                                                      | 60  |

|            | 3.4.1                                       | Scalar control                                                                           | 62  |

|            | 3.4.2                                       | Vector control                                                                           | 63  |

|            | 3.4.3                                       | Control design                                                                           | 64  |

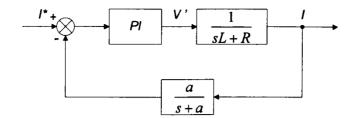

|            |                                             | 3.4.3.1 Current control design                                                           | 68  |

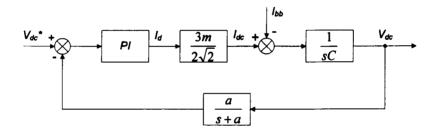

|            |                                             | 3.4.3.2 DC-link voltage control loop design                                              | 70  |

|            |                                             | 3.4.3.3 V <sub>pcc</sub> control loop design                                             | 72  |

| 3.5        | Simula                                      | ation of the STATCOM                                                                     | 73  |

|            | 3.5.1                                       | Simulation of a power system without VAr support                                         | 76  |

|            | 3.5.2                                       | Simulation of a power system using a conventional STATCC only                            |     |

| 3.6        | Conclu                                      | usions                                                                                   | 81  |

| Cha        | pter 4 S                                    | STATCOM with supercapacitor energy storage                                               | 82  |

| 4.1        | Introdu                                     | uction                                                                                   | 82  |

| 4.2        | Electri                                     | cal energy storage technologies                                                          | 83  |

|            | 4.2.1                                       | Pumped-hydro energy storage                                                              | 84  |

|            | 4.2.2                                       | Compressed-air energy storage (CAES)                                                     | 84  |

|     | 4.2.3  | Superconducting magnetic energy storage (SMES)          | .85          |

|-----|--------|---------------------------------------------------------|--------------|

|     | 4.2.4  | Flywheel energy storage (FES)                           | . 86         |

|     | 4.2.5  | Fuel cells                                              | . 87         |

|     | 4.2.6  | Battery energy storage (BES)                            | . 89         |

|     | 4.2.7  | Supercapacitor energy storage (SCES)                    | . <b>9</b> 0 |

| 4.3 | Superc | capacitor Energy Storage System (SCESS)                 | . <b>93</b>  |

|     | 4.3.1  | Constraints on the operation of the SCESS               | . 94         |

|     | 4.3.2  | Inductor design                                         | . 96         |

|     | 4.3.3  | DC-link capacitor design                                | . 97         |

|     | 4.3.4  | SCESS control strategies                                | . 98         |

|     |        | 4.3.4.1 Voltage mode control                            | . 99         |

|     |        | 4.3.4.2 Current mode control                            | 100          |

|     | 4.3.5  | SCESS control design 1                                  | 102          |

|     |        | 4.3.5.1 Boost mode control design 1                     | 102          |

|     |        | 4.3.5.2 Buck mode control design 1                      | 104          |

| 4.4 | STAT   | COM plus SCESS                                          | 106          |

| 4.5 | Simula | ation of STATCOM plus SCESS                             | 110          |

|     | 4.5.1  | Simulation of basic operation of STATCOM plus SCESS     | 111          |

|     | 4.5.2  | Simulation of a power system using a STATCOM plus SCESS |              |

|     | 4.5.3  | Comparison of the system with and without STATCOM plus  |              |

| 4.6 | Concl  | usions                                                  | 120          |

|     |        |                                                         |              |

|     | -      | Experimental setup <sup>1</sup>                         |              |

| 5.1 |        |                                                         |              |

| 5.2 | •      | n considerations for STATCOM plus SCESS                 |              |

| 5.3 | Exper  | imental rig                                             |              |

|     | 5.3.1  | The STATCOM                                             |              |

|     | 5.3.2  | The SCESS                                               |              |

|     | 5.3.3  | -                                                       |              |

|     |        | 5.3.3.1 Current mirror circuit                          | 131          |

ı

|     |          | 5.3.3.2 Gate driver circuit                                                        |

|-----|----------|------------------------------------------------------------------------------------|

|     | 5.3.4    | Voltage and current measurement                                                    |

|     |          | 5.3.4.1 Voltage measurement                                                        |

|     |          | 5.3.4.2 Current measurement                                                        |

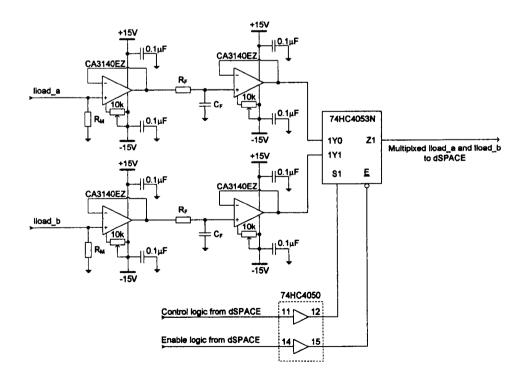

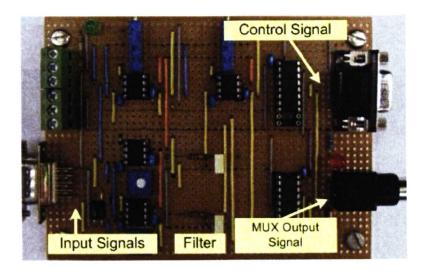

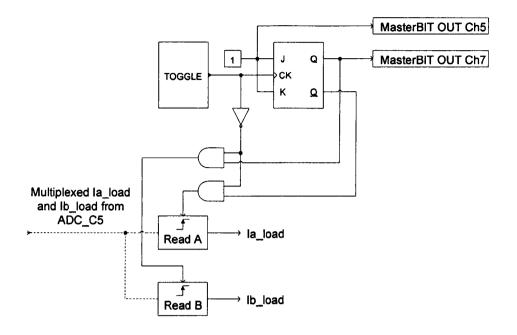

|     |          | 5.3.4.3 Analogue data multiplexer                                                  |

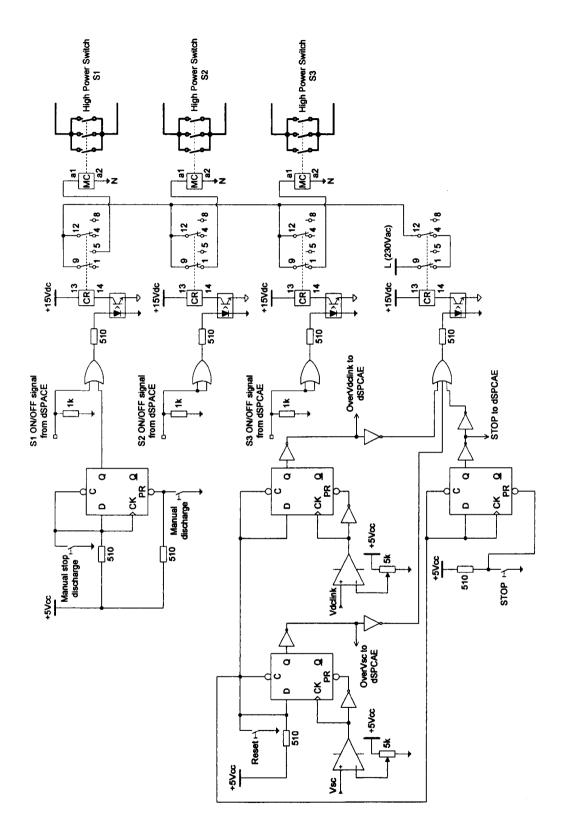

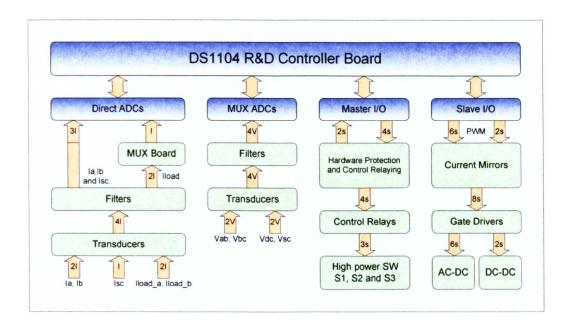

|     | 5.3.5    | Hardware protection and control relaying board                                     |

|     | 5.3.6    | The control platform                                                               |

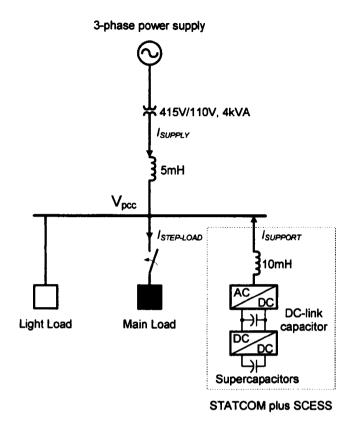

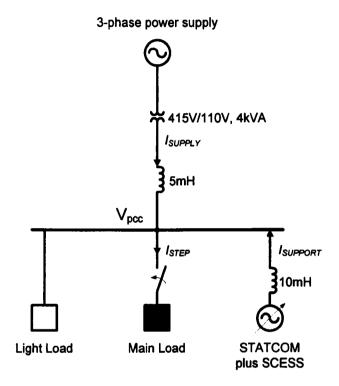

| 5.4 |          | st rig for demonstrating the benefits to a power system using<br>COM plus SCESS144 |

|     | 5.4.1    | The hardware                                                                       |

|     | 5.4.2    | The conceptual control146                                                          |

| 5.5 | Conclu   | usions                                                                             |

| ~.  |          |                                                                                    |

|     |          | Experimental results                                                               |

| 6.1 |          | uction                                                                             |

| 6.2 |          | ts to a power system using conventional STATCOM only 152                           |

| 6.3 |          | operation of STATCOM plus SCESS163                                                 |

| 6.4 | Benefi   | ts to the power system using a STATCOM plus SCESS                                  |

| 6.5 | Compa    | arison of a system with and without STATCOM plus SCESS 174                         |

| 6.6 | Conclu   | 176 Isions                                                                         |

| Cha | pter 7 C | Conclusions and future work178                                                     |

| 7.1 |          | system stability improvement using the STATCOM with energy                         |

| 7.2 |          | andard STATCOM based on a small-signal modelling controller                        |

| 7.3 | The en   | hanced STATCOM with Supercapacitors                                                |

| 7.4 | Future   | work182                                                                            |

| 7.5 | Publica  | ations resulting from the project184                                               |

|     |          |                                                                                    |

| App | cuuix B  |                                                                                    |

| Appendix C   |  |

|--------------|--|

| Appendix D   |  |

| Appendix E   |  |

| Bibliography |  |

•

# Table of figures

| Figure 1-1 | Static VAr Compensators (SVCs)4                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 | The simplified representation of (a) a synchronous condenser and<br>(b) a STATCOM                                                                                    |

| Figure 1-3 | The simplified representation of a synchronous condenser voltage<br>and current when operated as (a) inductive VAr generator, and (b)<br>capacitive VAr generator    |

| Figure 1-4 | The representation of a synchronous condenser voltage and current<br>when operated, with losses, as (a) inductive VAr generator, and (b)<br>capacitive VAr generator |

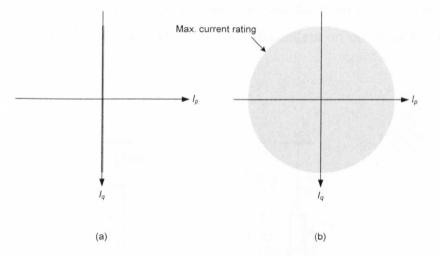

| Figure 1-5 | The comparison of the current controlled by the ideal (a) standard STATCOM, and (b) STATCOM with energy storage                                                      |

| Figure 1-6 | The equivalent circuit of (a) STATCOM and (b) SVC14                                                                                                                  |

| Figure 1-7 | V-I characteristic of STATCOM15                                                                                                                                      |

| Figure 1-8 | V-I characteristic of SVC                                                                                                                                            |

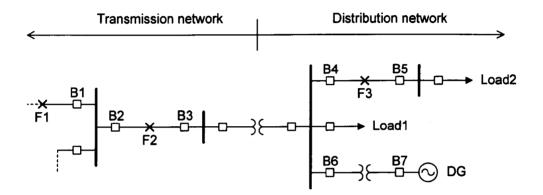

| Figure 2-1 | Protection relevant to distributed generation                                                                                                                        |

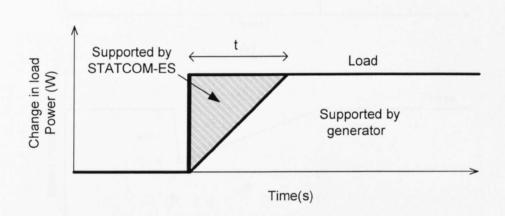

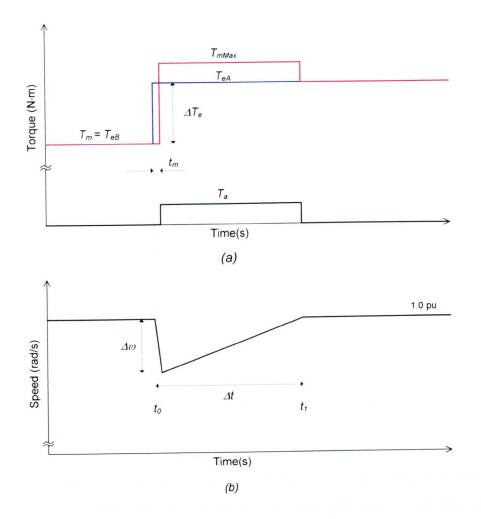

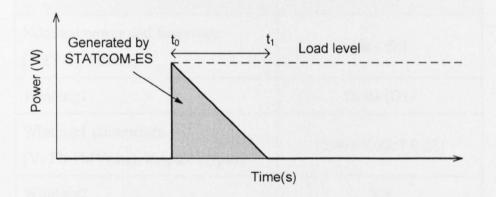

| Figure 2-2 | A sudden change of the load demand which is jointly supplied by<br>the STATCOM-ES and a generator                                                                    |

| Figure 2-3 | The simplified representation of (a) the mechanical, electrical and accelerating torque (b) the speed ( $\omega$ ) variation during load impact<br>34                |

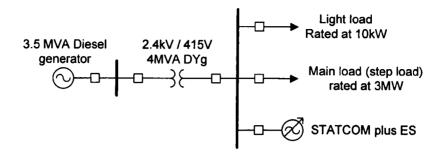

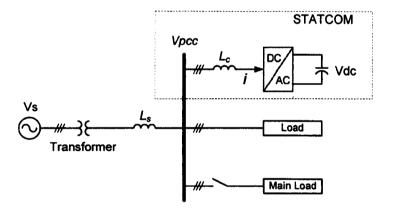

| Figure 2-4 | The power circuit diagram of the system used in the simulation 38                                                                                                    |

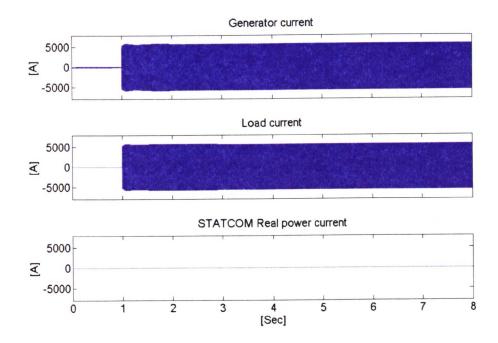

| -          | Generator current, load current, and support current during the operation of the system without real power support                                                   |

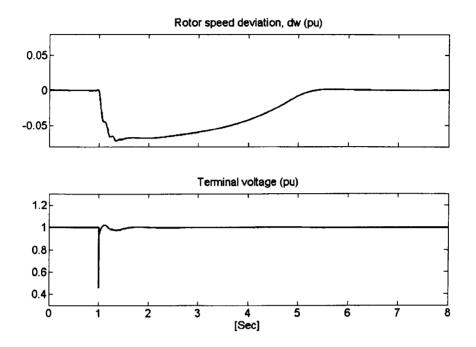

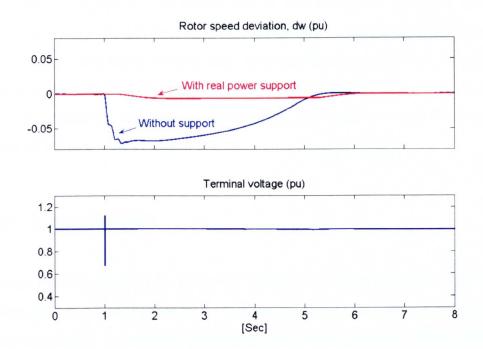

| Figure 2-6 | Rotor speed deviation and terminal voltage during the operation of<br>the system without real power support                                                          |

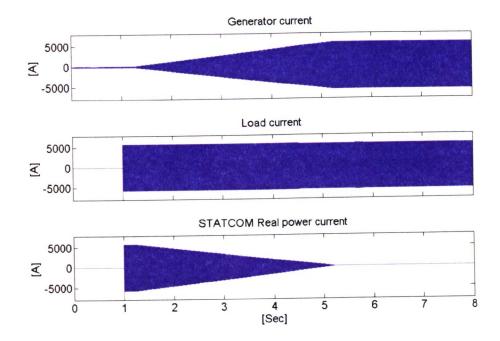

|            | Generator current, load current, and support current during the operation of the system with real power support from the STATCOM plus energy storage                 |

| Figure 2-8 | Rotor speed deviation and terminal voltage during the operation of<br>the system with real power support from the STATCOM plus<br>energy storage                     |

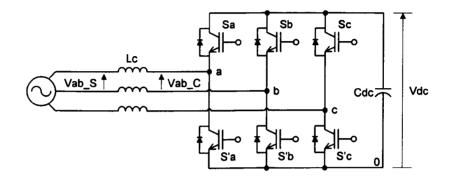

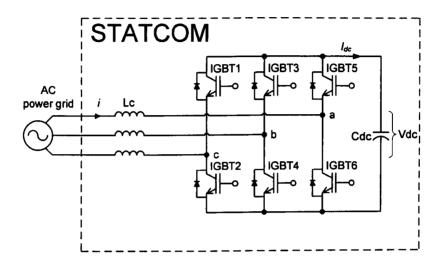

| Figure 3-1 | The conventional 6-pulse grid connected power converter                                                                                                              |

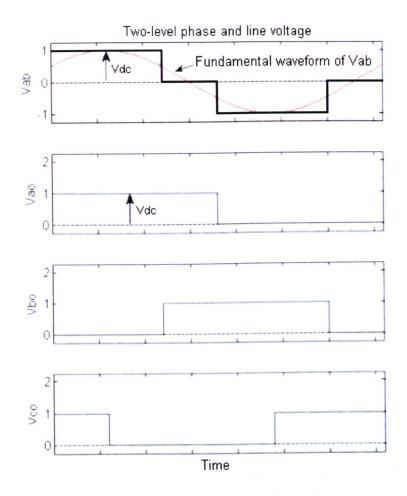

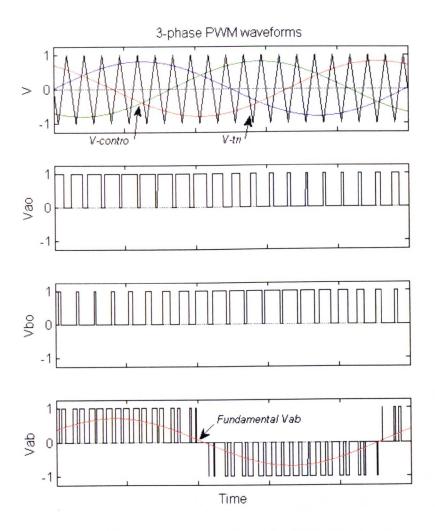

| Figure 3-2 | Phase and line voltage of the 2-level dc-to-ac converter                                                                                                             |

| -          | Phase and line voltage of the 2-level dc-to-ac converter with PWM switching technique                                                                                |

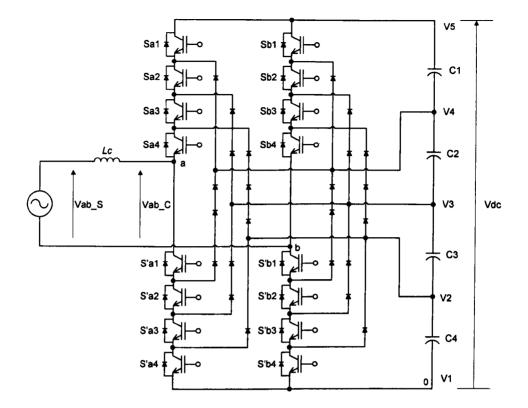

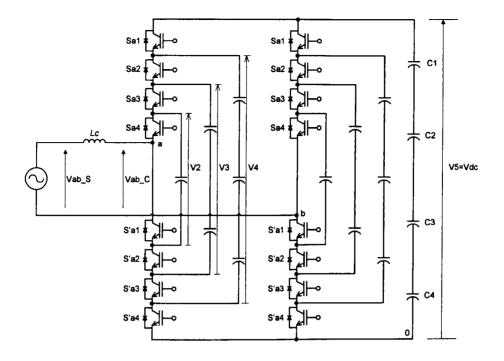

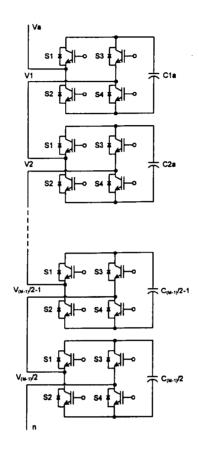

| Figure 3-4 Circuit diagram of a 5-level diode-clamped converter                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-5 Circuit diagram of a 5-level flying capacitor converter                                                                                           |

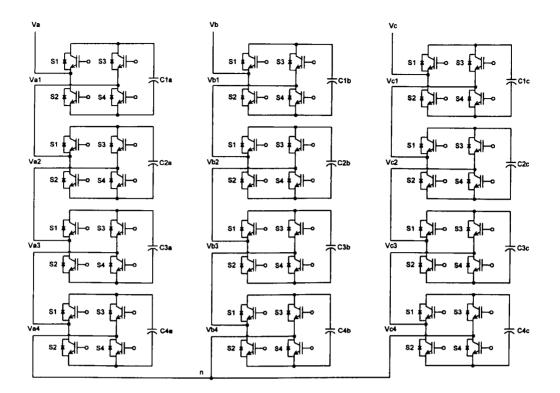

| Figure 3-6 Circuit diagram of a single phase cascaded multilevel converter 54                                                                                |

| Figure 3-7 A star-connected cascaded 9-level converter                                                                                                       |

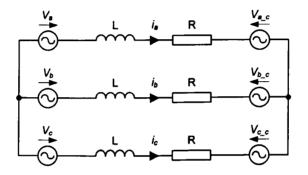

| Figure 3-8 The equivalent circuit diagram of a three phase voltage source converter connected to the ac power grid                                           |

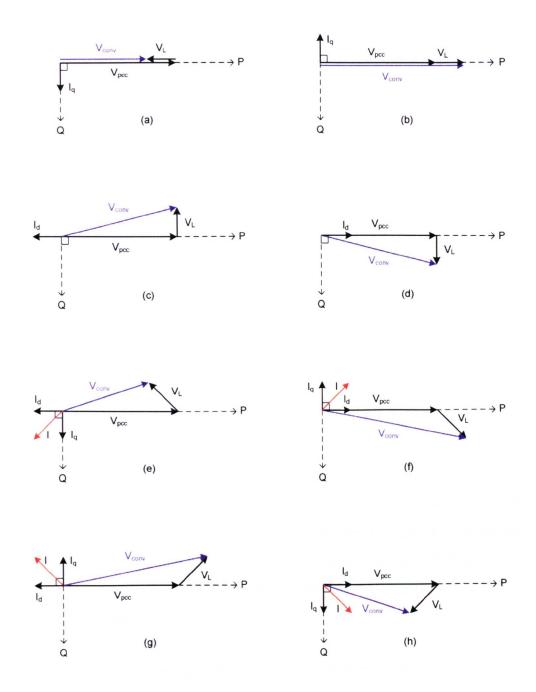

| Figure 3-9 The possible power flow controls between voltage source converter<br>and grid                                                                     |

| Figure 3-10 A power circuit diagram of a STATCOM61                                                                                                           |

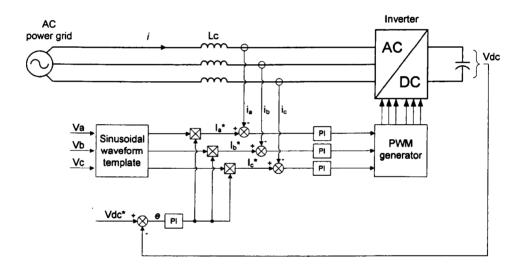

| Figure 3-11 A simplified scalar control strategy62                                                                                                           |

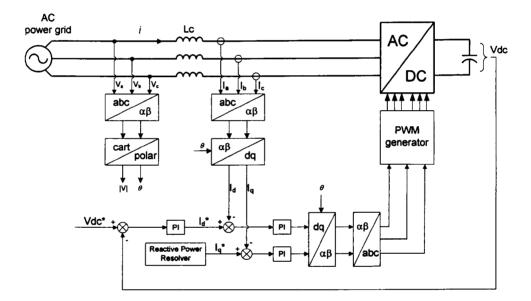

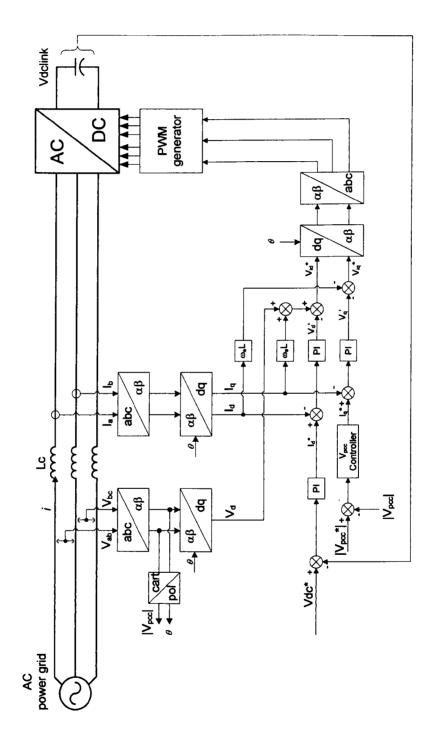

| Figure 3-12 A simplified vector control strategy                                                                                                             |

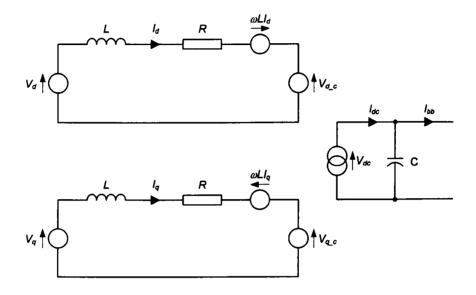

| Figure 3-13 The d-q frame equivalent circuit diagram of STATCOM                                                                                              |

| Figure 3-14 Control structure for STATCOM67                                                                                                                  |

| Figure 3-15 Current control loop70                                                                                                                           |

| Figure 3-16 DC-link voltage control loop71                                                                                                                   |

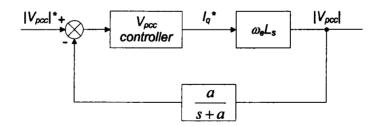

| Figure 3-17 V <sub>pcc</sub> control loop72                                                                                                                  |

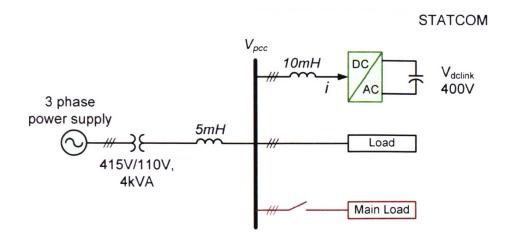

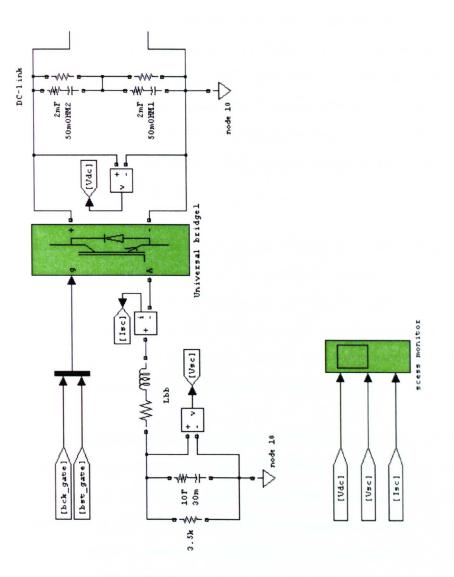

| Figure 3-18 Power circuit diagram setup for simulation study                                                                                                 |

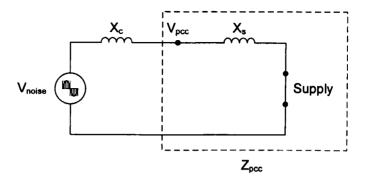

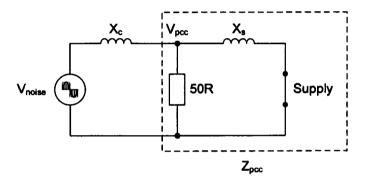

| Figure 3-19 An equivalent circuit diagram of the voltage divider formed by the additional reactor, X <sub>s</sub> , and the coupling reactor, X <sub>c</sub> |

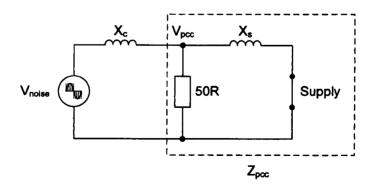

| Figure 3-20 An equivalent circuit diagram showing Z <sub>pcc</sub> is reduced by the 50 ohm resistor connected at V <sub>pcc</sub>                           |

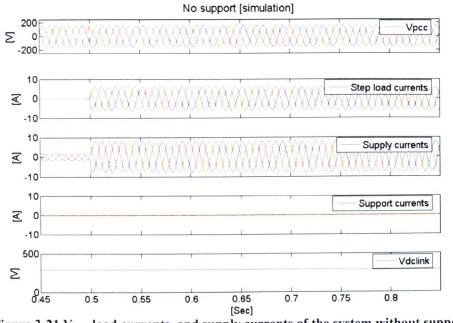

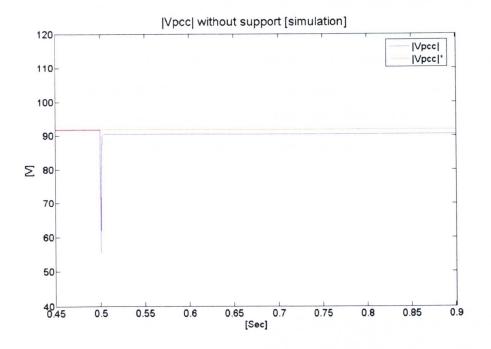

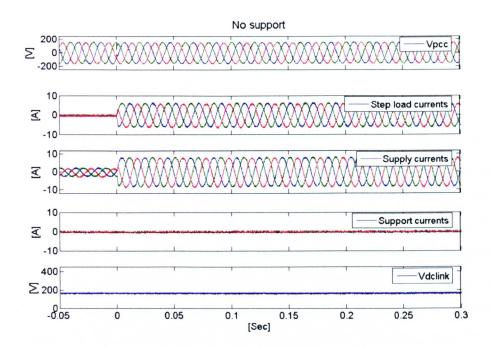

| Figure 3-21 V <sub>pcc</sub> , load currents, and supply currents of the system without support [simulation]77                                               |

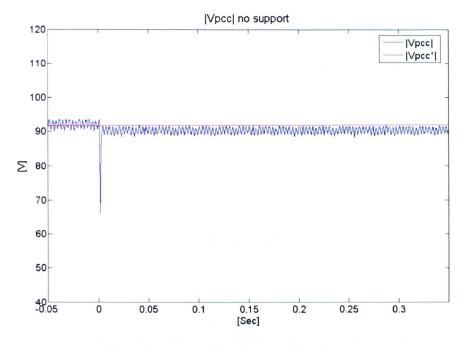

| Figure 3-22  V <sub>pcc</sub>   of the system without support [simulation]77                                                                                 |

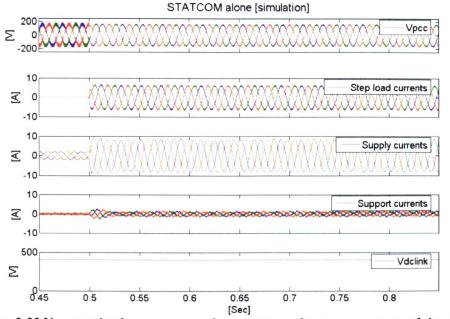

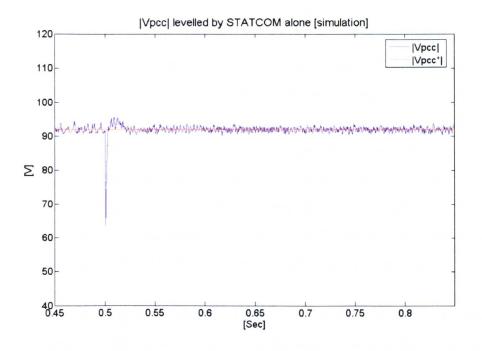

| Figure 3-23 V <sub>pcc</sub> , step load currents, supply currents, and support currents of the system with STATCOM only [simulation]                        |

| Figure 3-24 $ V_{pcc} $ of the system with STATCOM only [simulation]                                                                                         |

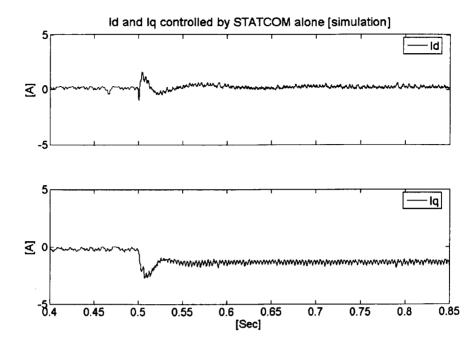

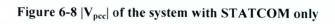

| Figure 3-25 The controlled $I_d$ and $I_q$ for the system with STATCOM only [simulation]                                                                     |

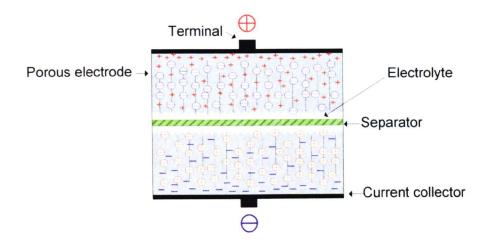

| Figure 4-1 Insights into a simplified supercapacitor cell                                                                                                    |

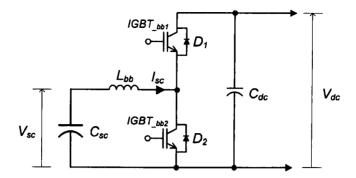

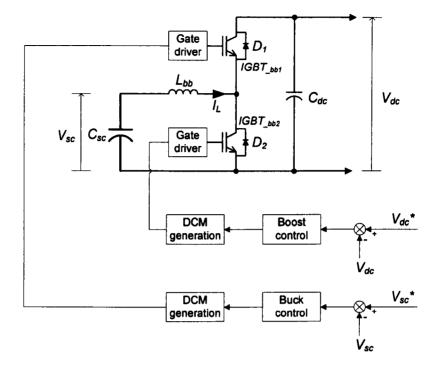

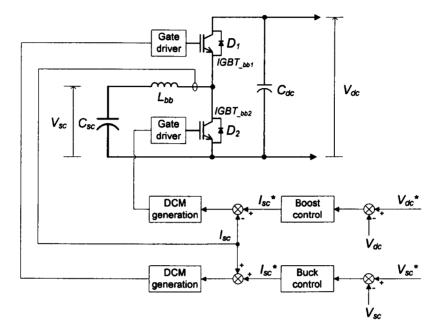

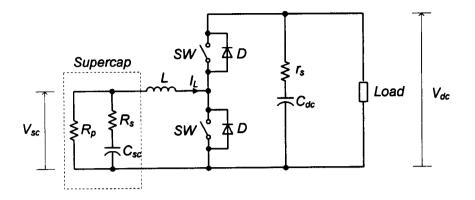

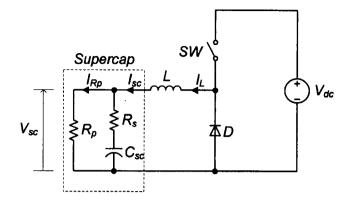

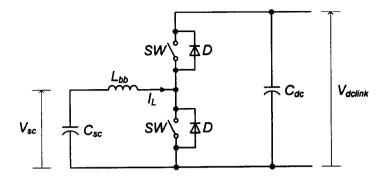

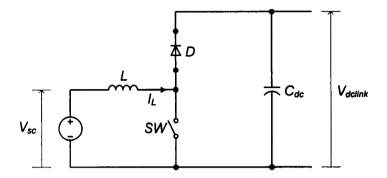

| Figure 4-2 The power circuit of the SCESS94                                                                                                                  |

| Figure 4-3 The voltage mode control structure                                                                                                                |

| Figure 4-4 The current mode control structure                                                                                                                |

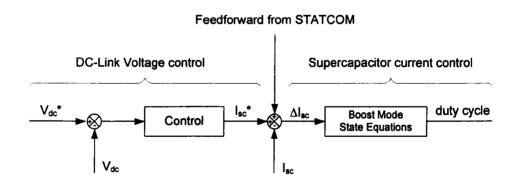

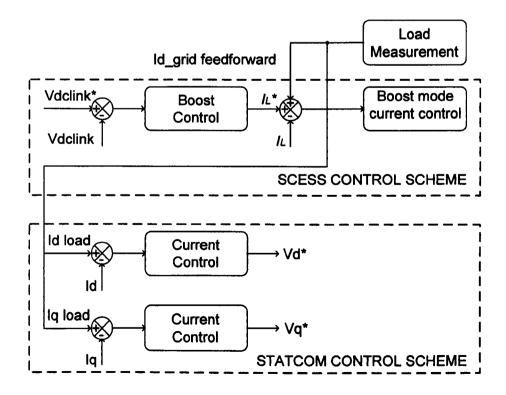

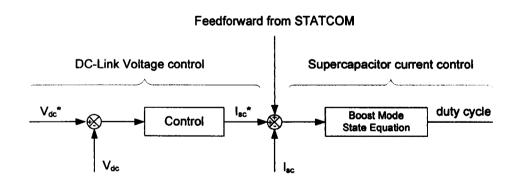

| Figure 4-5 Boost mode control concept                                                                                                                        |

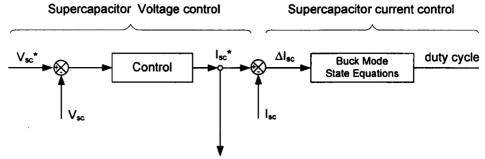

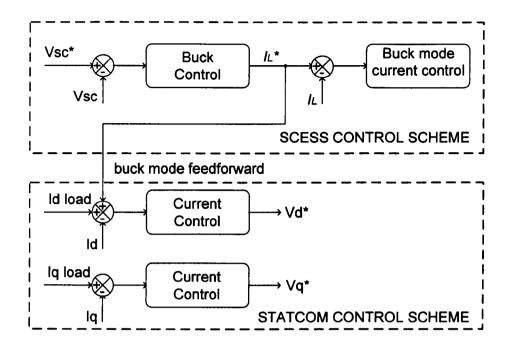

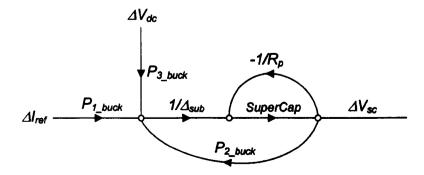

| Figure 4-6 Buck mode control concept 105                                                                                                                     |

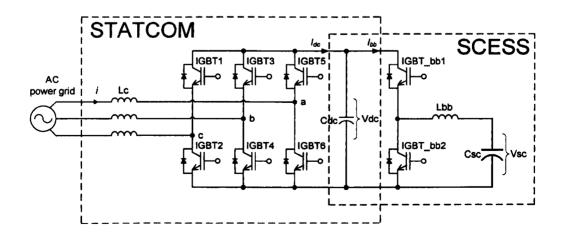

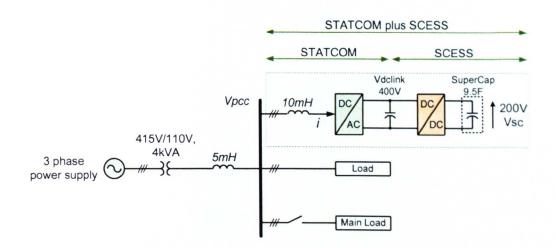

| Figure 4-7 The power circuit diagram of the STATCOM plus SCESS 106                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

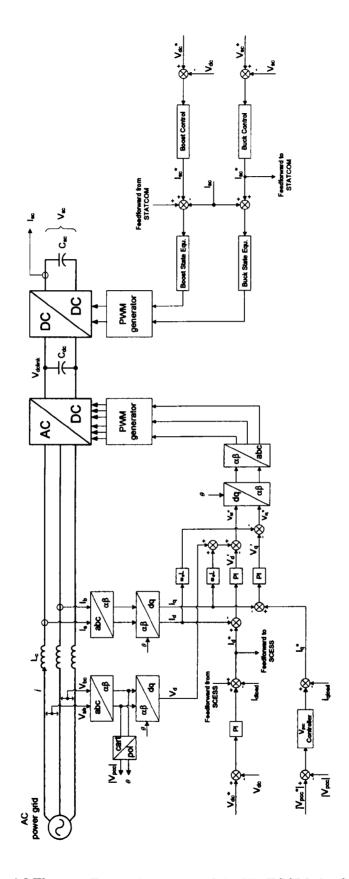

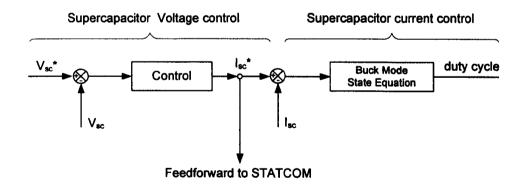

| Figure 4-8 The overall control structure of the STATCOM plus SCESS 108                                                                                                                                                     |

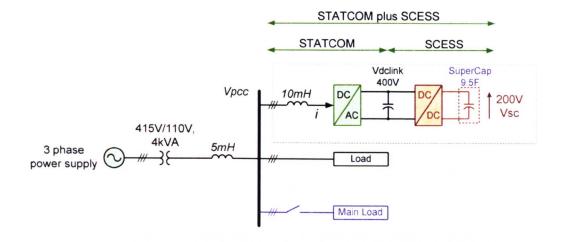

| Figure 4-9 Power circuit diagram setup for simulation study110                                                                                                                                                             |

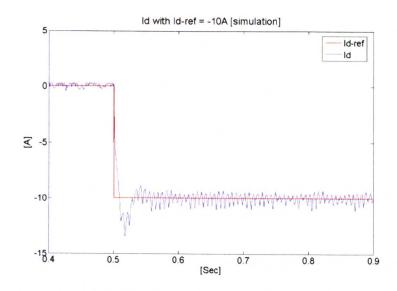

| Figure 4-10 Response of d-axis current control to a step change of negative<br>10A [simulation]                                                                                                                            |

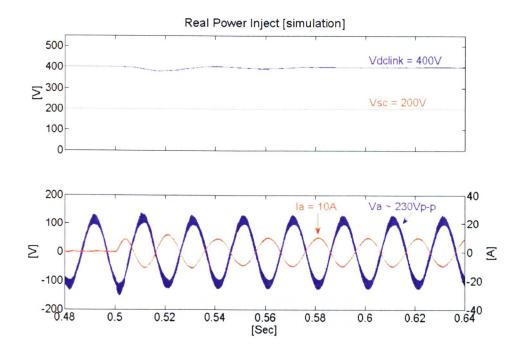

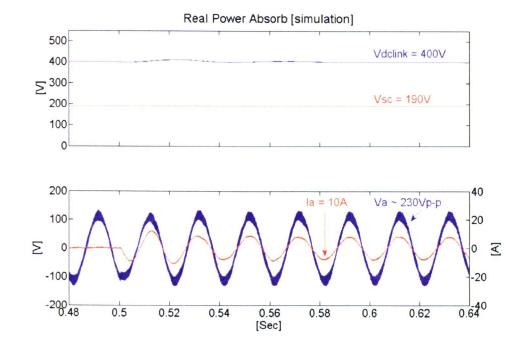

| Figure 4-11 V <sub>dclink</sub> , V <sub>sc</sub> , V <sub>a</sub> , and I <sub>a</sub> during the period when the STATCOM plus<br>SCESS inject real power to grid [simulation]112                                         |

| Figure 4-12 V <sub>dclink</sub> , V <sub>sc</sub> , V <sub>a</sub> , and I <sub>a</sub> during the period when the STATCOM plus<br>SCESS absorbs real power from grid (i.e. charge the<br>supercapacitors) [simulation]113 |

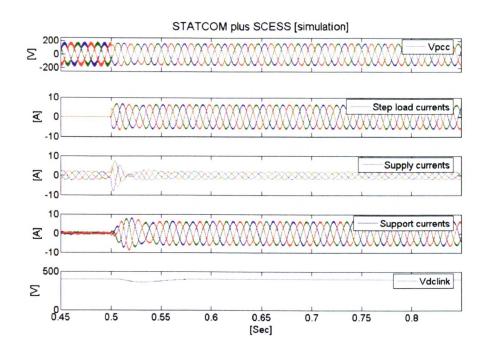

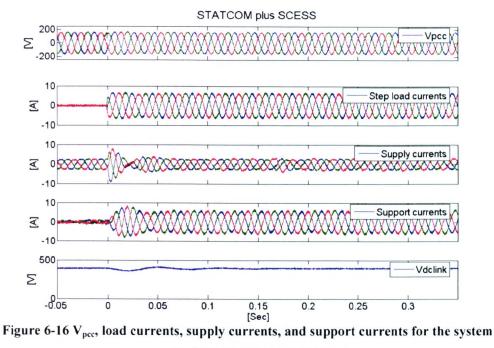

| Figure 4-13 V <sub>pcc</sub> , load currents, supply currents, and support currents for the system with STATCOM plus SCESS [simulation]114                                                                                 |

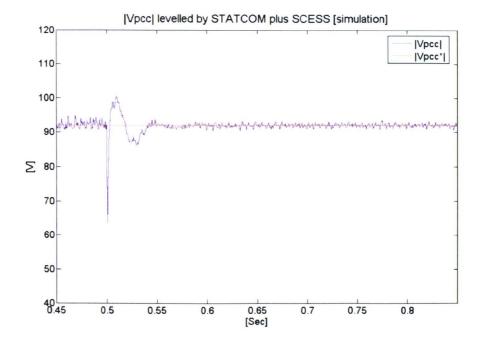

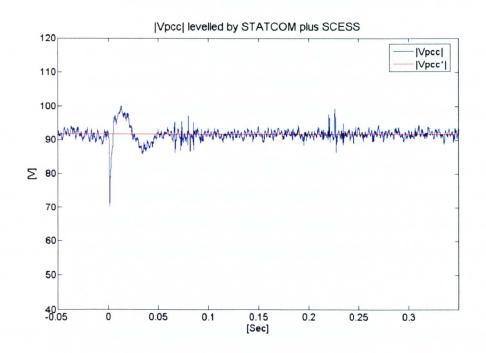

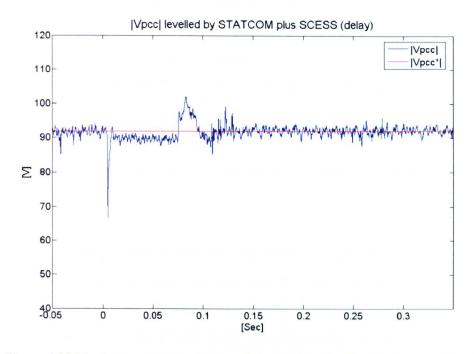

| Figure 4-14 $ V_{pcc} $ of the system with STATCOM plus SCESS [simulation] 116                                                                                                                                             |

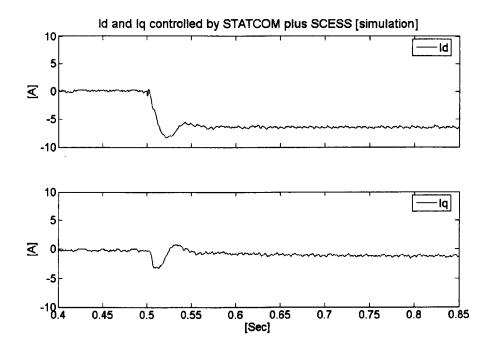

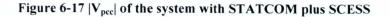

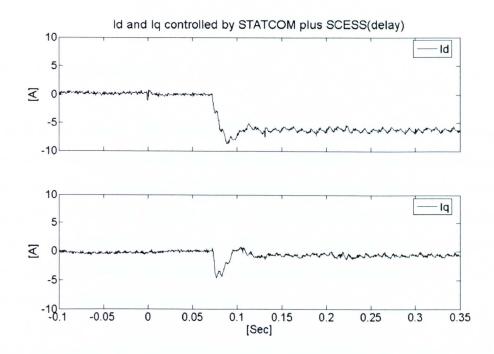

| Figure 4-15 Controlled I <sub>d</sub> and I <sub>q</sub> for the system with STATCOM plus SCESS [simulation]                                                                                                               |

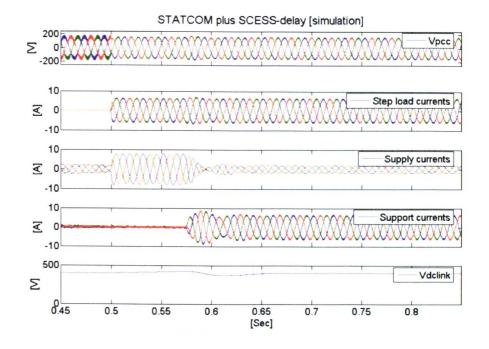

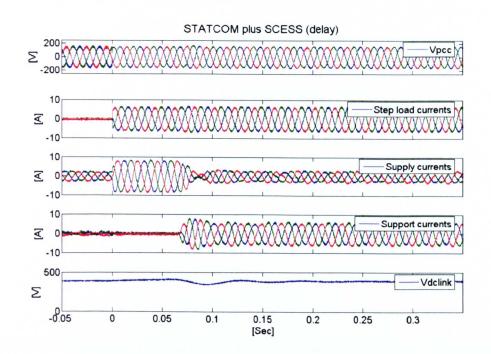

| Figure 4-16 V <sub>pcc</sub> , load currents, supply currents, and support currents of the system with STATCOM plus SCESS when its operation is delayed from t=0.5s to t=0.575s [simulation]118                            |

| Figure 4-17  V <sub>pcc</sub>   of the system with STATCOM plus SCESS when its operation is delayed by 75ms [simulation]119                                                                                                |

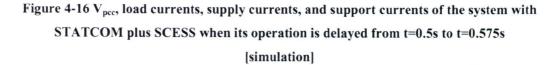

| Figure 4-18 The controlled $I_d$ and $I_q$ for the system with STATCOM plus SCESS when its operation is delayed by 75ms [simulation] 119                                                                                   |

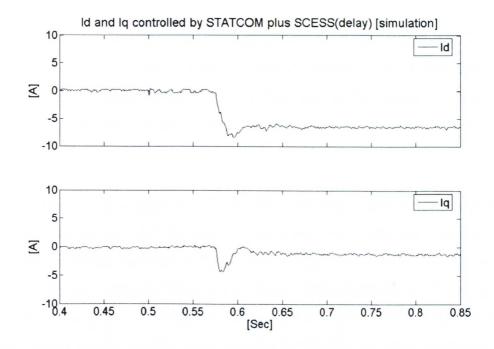

| Figure 5-1The overall experimental setup                                                                                                                                                                                   |

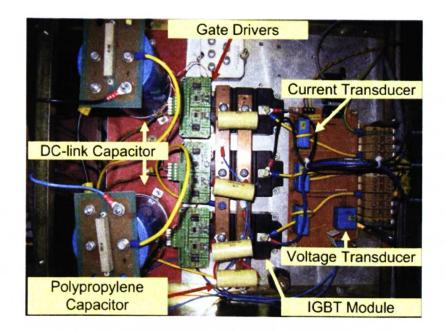

| Figure 5-2 Top view of the inverter                                                                                                                                                                                        |

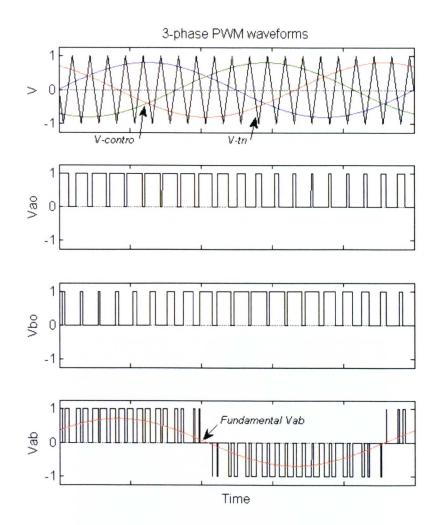

| Figure 5-3 Sinewave PWM switching technique                                                                                                                                                                                |

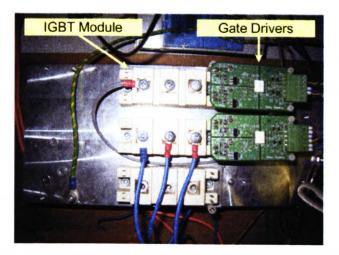

| Figure 5-4 Top view of the DC-DC converter                                                                                                                                                                                 |

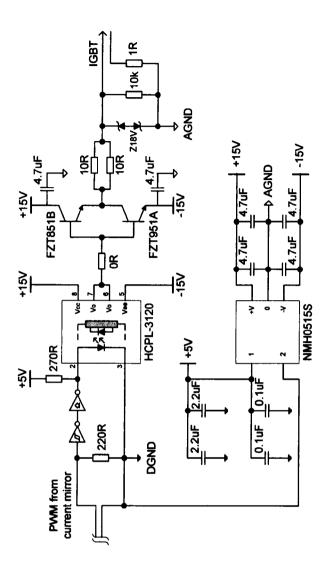

| Figure 5-5 Current mirror circuit diagram                                                                                                                                                                                  |

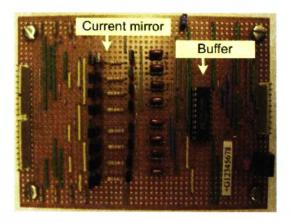

| Figure 5-6 Top view of the current mirror circuit board                                                                                                                                                                    |

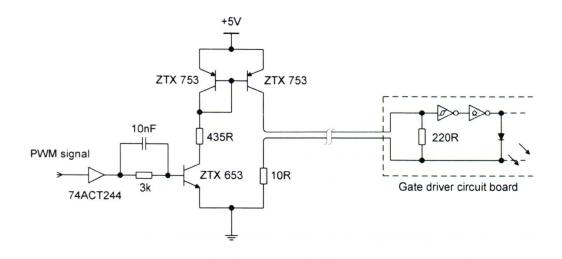

| Figure 5-7 Gate driver circuit diagram                                                                                                                                                                                     |

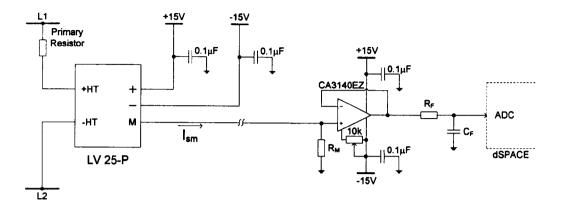

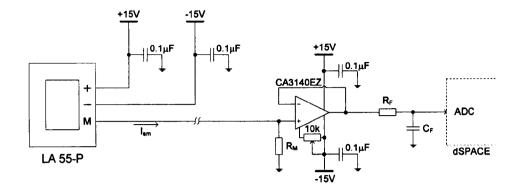

| Figure 5-8 Voltage measurement circuit diagram                                                                                                                                                                             |

| Figure 5-9 Current measurement circuit                                                                                                                                                                                     |

| Figure 5-10 Analog multiplexer circuit board                                                                                                                                                                               |

| Figure 5-11 The analogue multiplexer board                                                                                                                                                                                 |

| Figure 5-12 The de-multiplexer implemented in dSPACE                                                                                                                                                                       |

| Figure 5-13 The circuit diagram for Vdclink and Vsc hardware protection and control relaying board                                                                                                                         |

.

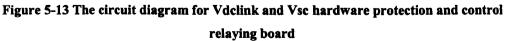

| Figure 5-14 The functional block diagram of the control platform143                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-15 Single line diagram of the overall power circuit diagram 145                                                                                                                                   |

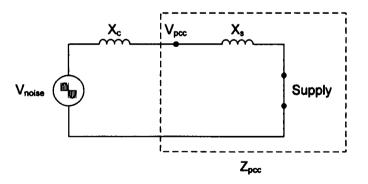

| Figure 5-16 Equivalent circuit diagram of the voltage divider formed by the additional inductor                                                                                                            |

| Figure 5-17 Equivalent circuit diagram of the voltage divider formed by the additional inductor and the 50 ohm resistor connected at V <sub>pcc</sub> 146                                                  |

| Figure 5-18 Buck mode control diagram (mode 2)148                                                                                                                                                          |

| Figure 5-19 Boost mode control diagram (mode 3)148                                                                                                                                                         |

| Figure 6-1 Single line diagram of the experimental rig151                                                                                                                                                  |

| Figure 6-2 V <sub>pcc</sub> , load currents, and supply currents of the system without support                                                                                                             |

| Figure 6-3 $ V_{pcc} $ of the system without support                                                                                                                                                       |

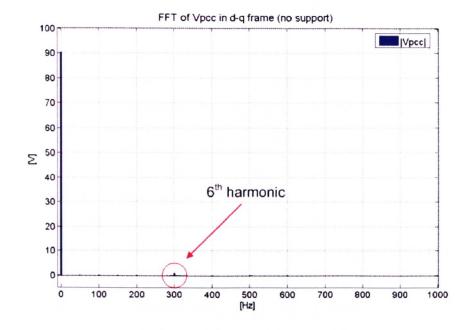

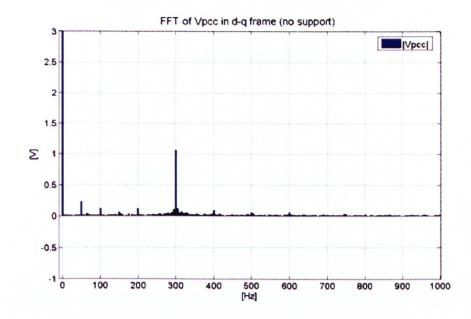

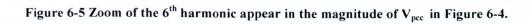

| Figure 6-4 Harmonic contents of $V_{pcc}$ in the d-q frame of reference                                                                                                                                    |

| Figure 6-5 Zoom of the 6 <sup>th</sup> harmonic appear in the magnitude of V <sub>pcc</sub> in Figure 6-4                                                                                                  |

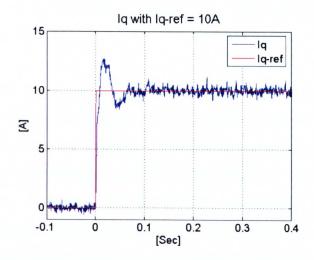

| Figure 6-6 Response of q-axis current control to a step change of 10A 156                                                                                                                                  |

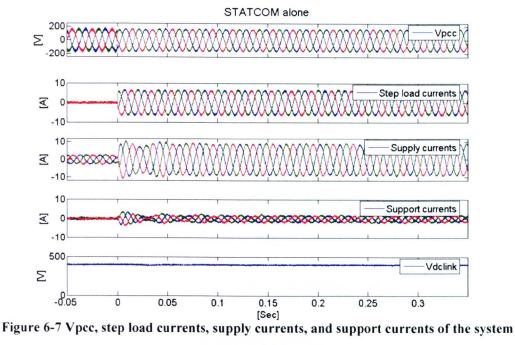

| Figure 6-7 Vpcc, step load currents, supply currents, and support currents of the system with STATCOM only                                                                                                 |

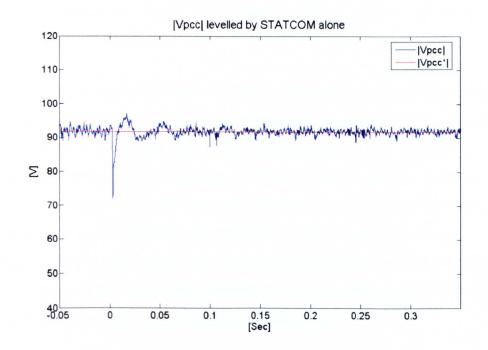

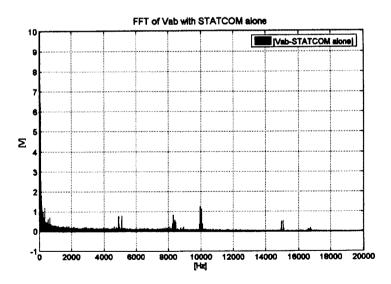

| Figure 6-8 $ V_{pcc} $ of the system with STATCOM only                                                                                                                                                     |

| Figure 6-9 The controlled I <sub>d</sub> and Iq for the system with STATCOM only 160                                                                                                                       |

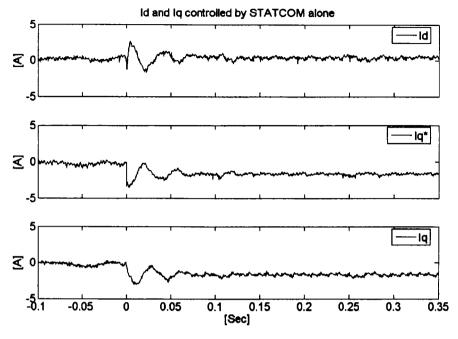

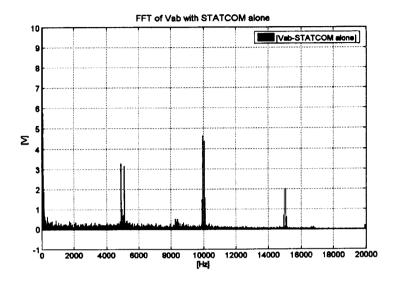

| Figure 6-10 Harmonic content of $V_{pcc}$ prior to the load change                                                                                                                                         |

| Figure 6-11 Harmonic content of $V_{pcc}$ after the load change                                                                                                                                            |

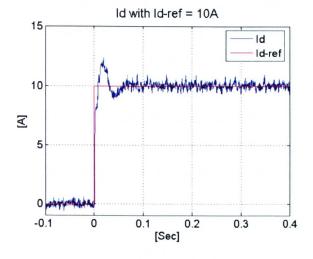

| Figure 6-12 Response of d-axis current control to a step change of 10A 164                                                                                                                                 |

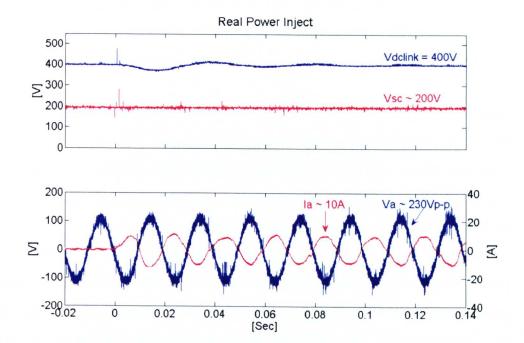

| Figure 6-13 Vdclink, V <sub>sc</sub> , V <sub>a</sub> , and I <sub>a</sub> during the period when the STATCOM plus SCESS inject real power to grid                                                         |

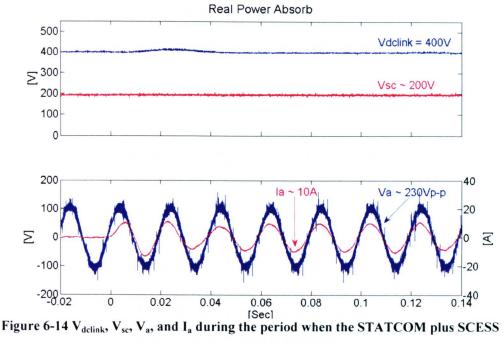

| Figure 6-14 V <sub>dclink</sub> , V <sub>sc</sub> , V <sub>a</sub> , and I <sub>a</sub> during the period when the STATCOM plus<br>SCESS absorbs real power from grid (i.e. charge the<br>supercapacitors) |

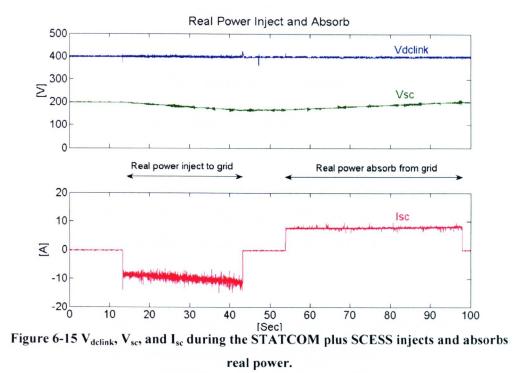

| Figure 6-15 V <sub>dclink</sub> , V <sub>sc</sub> , and I <sub>sc</sub> during the STATCOM plus SCESS injects and absorbs real power                                                                       |

| Figure 6-16 V <sub>pcc</sub> , load currents, supply currents, and support currents for the system with STATCOM plus SCESS                                                                                 |

| Figure 6-17 $ V_{pcc} $ of the system with STATCOM plus SCESS                                                                                                                                              |

| Figure 6-18 The controlled $I_d$ and $I_q$ for the system with STATCOM plus SCESS                                                                                                                          |

|                                                                                                                                                                                                            |

| Figure 6-1 | 9 V <sub>pcc</sub> , load currents, supply currents, and support currents of the<br>system with STATCOM plus SCESS when its operation is delaye<br>by 70ms |                |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 6-2 | 0  V <sub>pcc</sub>   of the system with STATCOM plus SCESS when its operation is delayed by 70ms17                                                        | 75             |

| Figure 6-2 | 1 The controlled $I_d$ and $I_q$ for the system with STATCOM plus<br>SCESS when its operation is delayed by 70ms                                           | 75             |

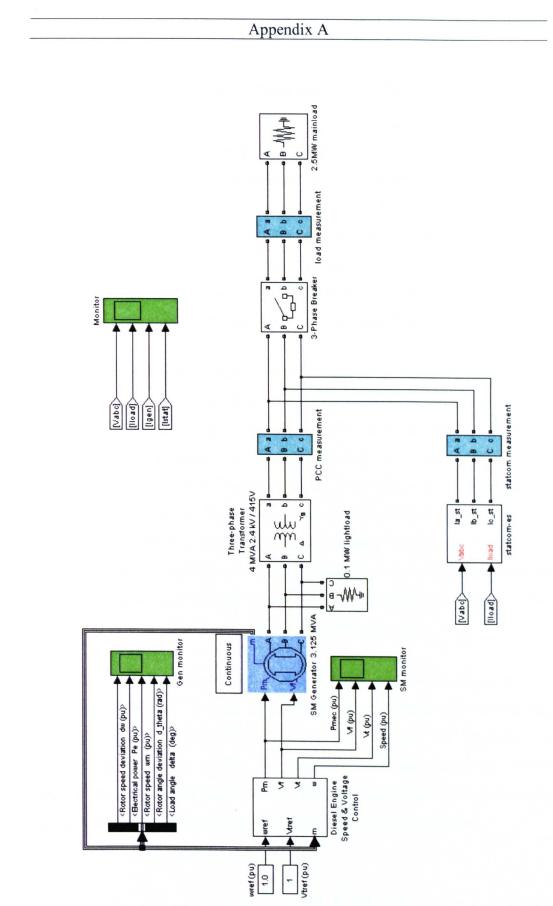

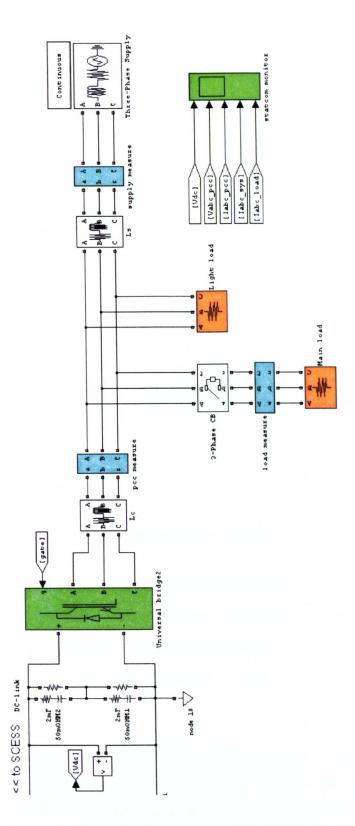

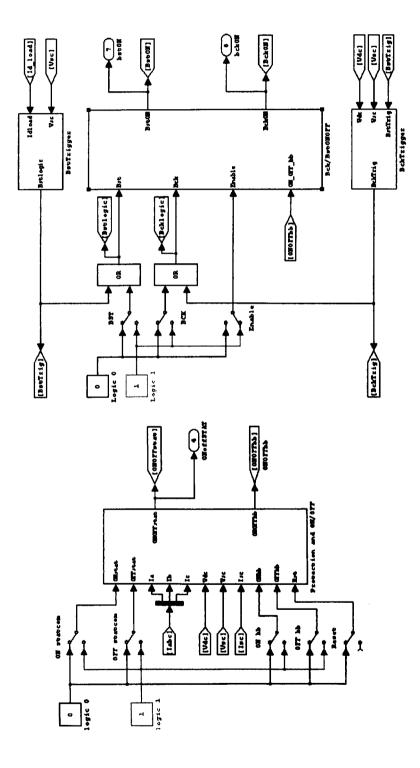

| Figure A-1 | 1 The overall simulation model18                                                                                                                           | 37             |

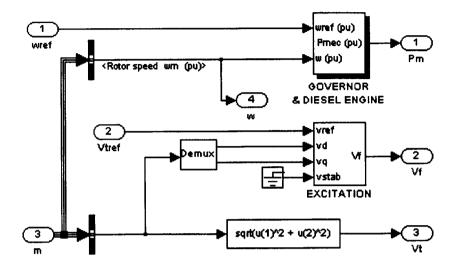

| Figure A-2 | 2 Detail of the speed and voltage control block in Figure A-1 18                                                                                           | 39             |

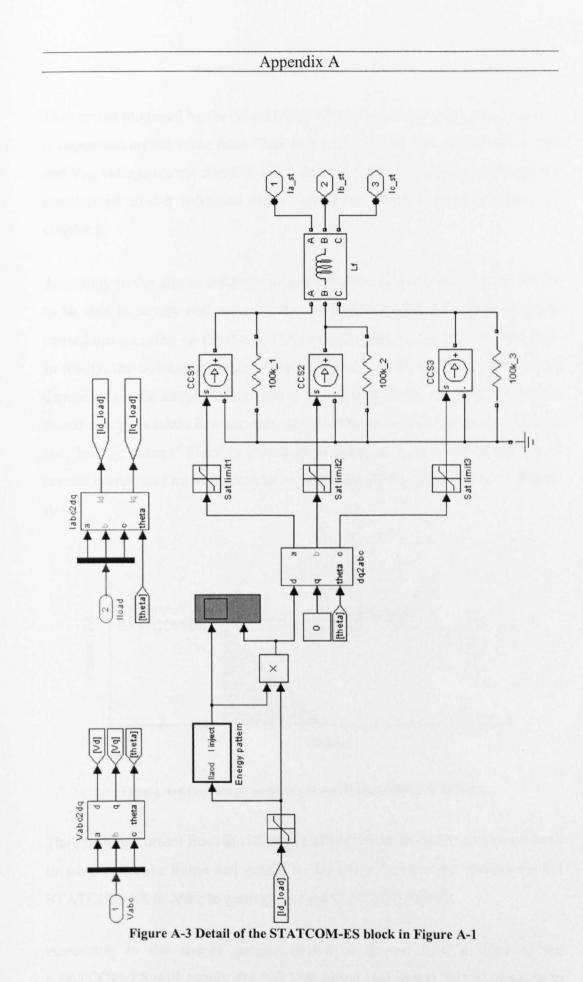

| Figure A-3 | B Detail of the STATCOM-ES block in Figure A-1                                                                                                             | <del>)</del> 0 |

| Figure A-4 | the energy pattern produced by the STATCOM-ES                                                                                                              | <b>)</b> 1     |

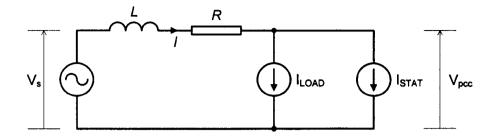

| Figure B-1 | The power circuit of the ac power system using a STATCOM 19                                                                                                | <del>)</del> 6 |

| Figure B-2 | 2 The equivalent circuit of the system show in figure B-1                                                                                                  | <b>}</b> 7     |

| Figure C-1 | Power circuit of the SCESS                                                                                                                                 | )2             |

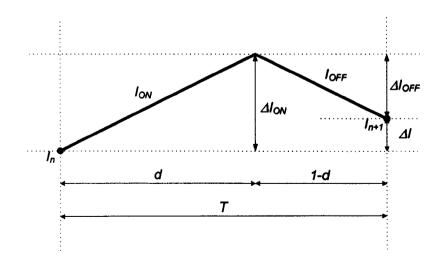

|            | 2 Change in inductor current over one sampling period                                                                                                      |                |

| Figure C-3 | Boost mode circuit diagram20                                                                                                                               | )4             |

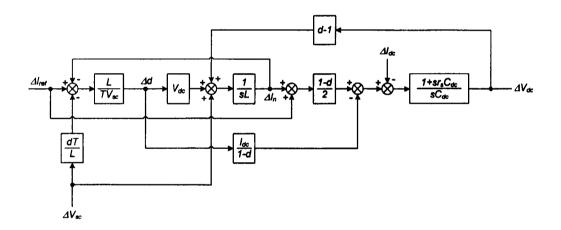

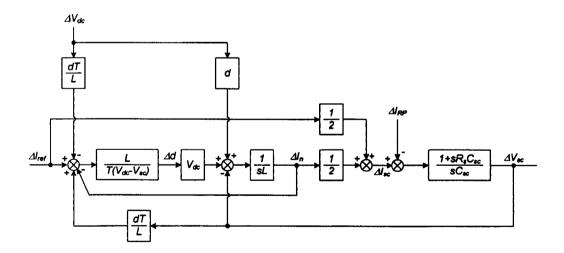

| Figure C-4 | Small-signal block diagram of the SCESS operating in boost mod                                                                                             |                |

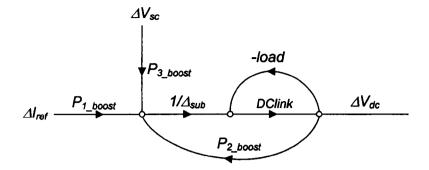

| Figure C-5 | the simplified small-signal diagram of the boost mode SCESS.20                                                                                             |                |

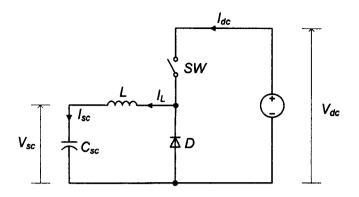

| Figure C-6 | Buck mode circuit diagram21                                                                                                                                | 0              |

|            | The small-signal block diagram of the SCESS operating in buck mode21                                                                                       | 2              |

| Figure C-8 | The simplified small-signal diagram of the SCESS operating in buck mode                                                                                    | 3              |

| Figure D-1 | Power circuit of the SCESS                                                                                                                                 | 6              |

| Figure D-2 | 2 The SCESS boost mode power circuit                                                                                                                       | .7             |

| Figure D-3 | Inductor current waveform during one sampling period                                                                                                       | .7             |

| Figure D-4 | Boost control concept21                                                                                                                                    | 8              |

| Figure D-5 | The SCESS buck mode power circuit                                                                                                                          | 21             |

| Figure D-6 | Buck mode control concept22                                                                                                                                | 21             |

| Figure E-1 | The single line diagram of the proposed system                                                                                                             | :5             |

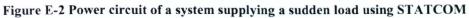

| ~          | Power circuit of a system supplying a sudden load using STATCOM                                                                                            | 26             |

| Figure E-3 | Power circuit of the SCESS                                                                                                                                 | 7              |

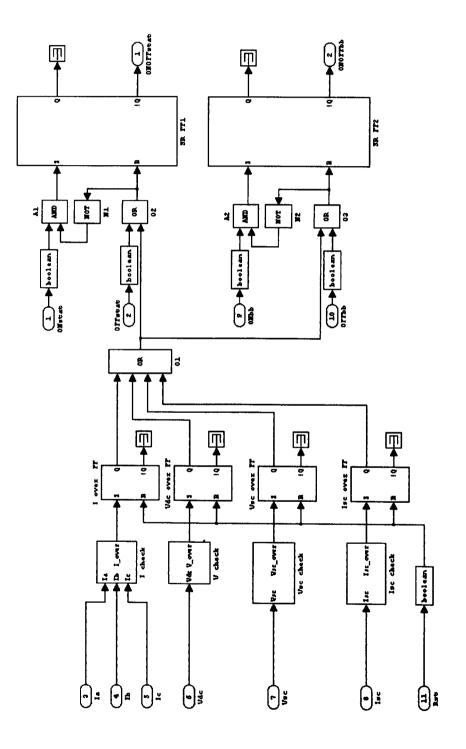

| Figure E-4 | The STATCOM plus SCESS control model                                                                                                                       | 0              |

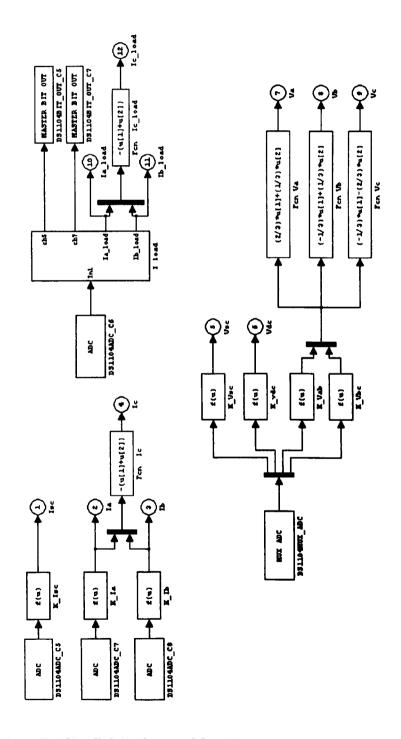

| Figure E-5 | Simulink implemented for dSPACE to read the input data23<br>[xiii]                                                                                         | 2              |

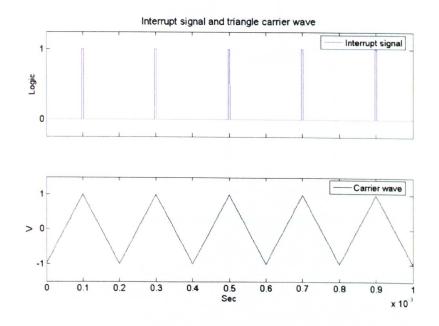

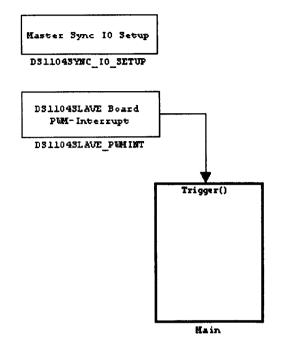

| Figure E-6 Interrupt signal for the simulation              | . 234 |

|-------------------------------------------------------------|-------|

| Figure E-7 Interrupt signal for dSPACE controller board     | . 235 |

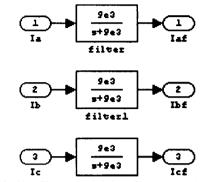

| Figure E-8 The filter model for the three-phase current     | . 236 |

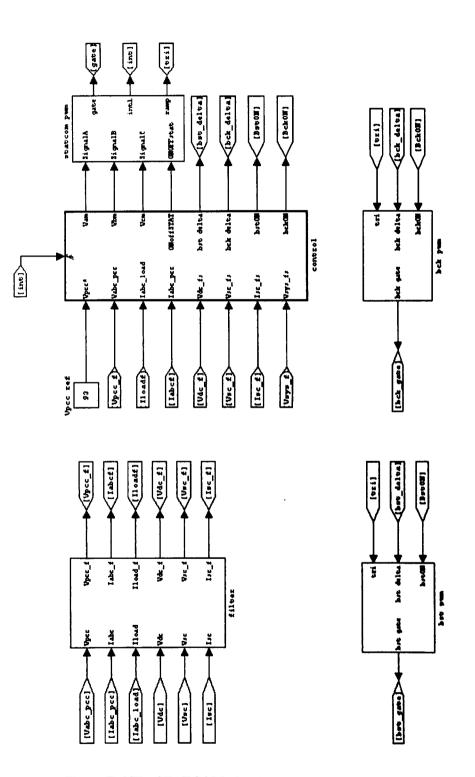

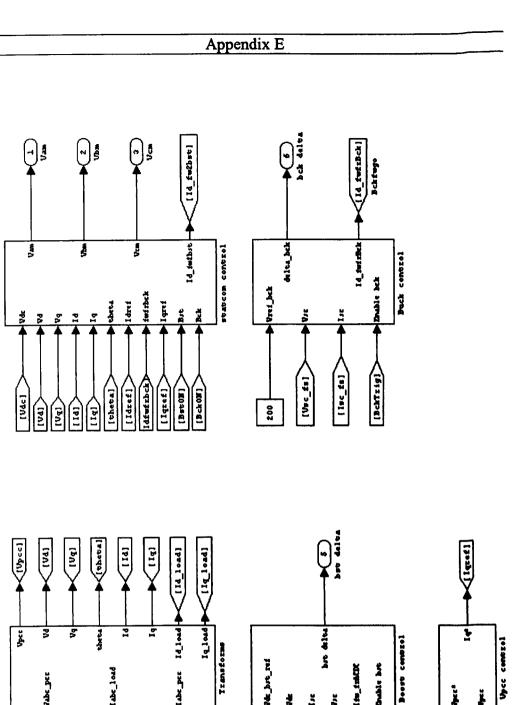

| Figure E-9 The 'control' block                              | . 237 |

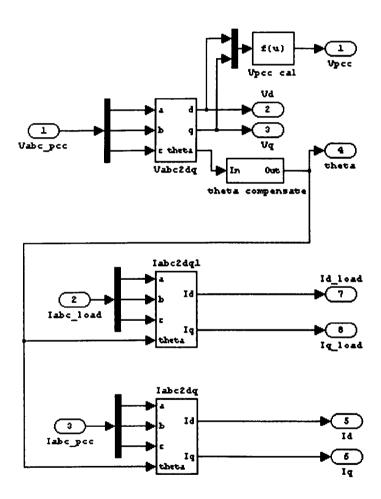

| Figure E-10 The 'transform' block                           | . 238 |

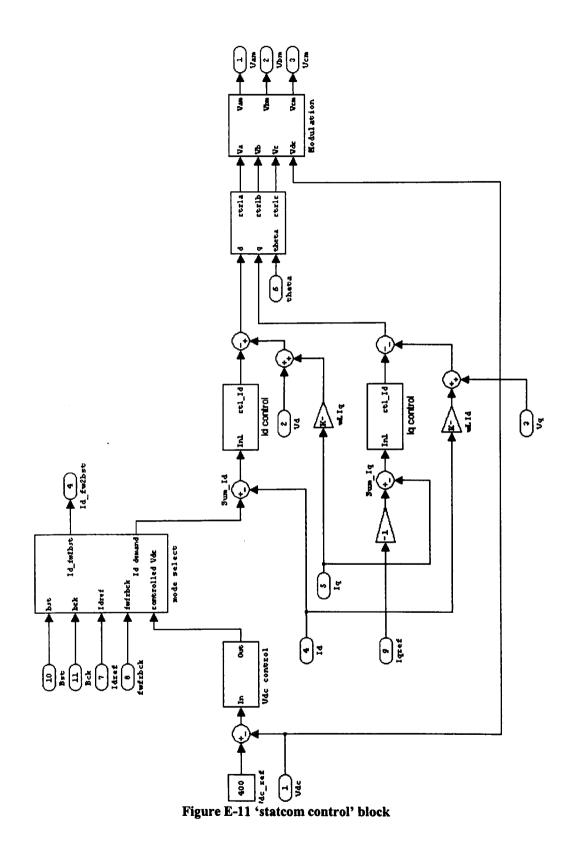

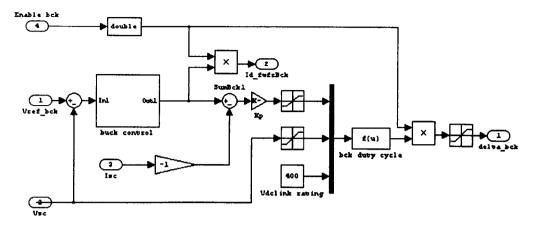

| Figure E-11 'statcom control' block                         | . 240 |

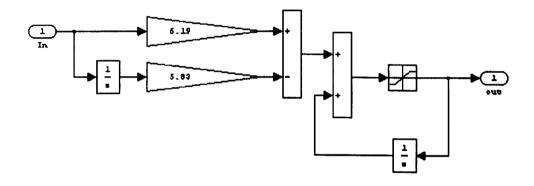

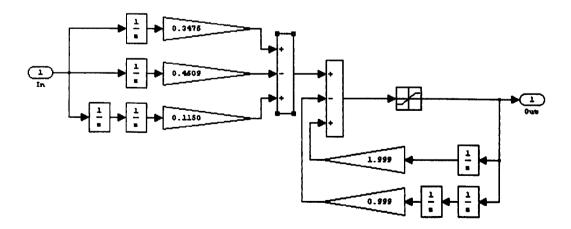

| Figure E-12 DC-link control implemented using simulink      | . 241 |

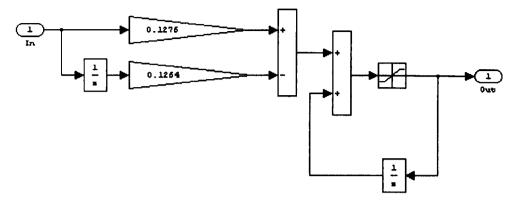

| Figure E-13 Current control implemented using simulink      | . 241 |

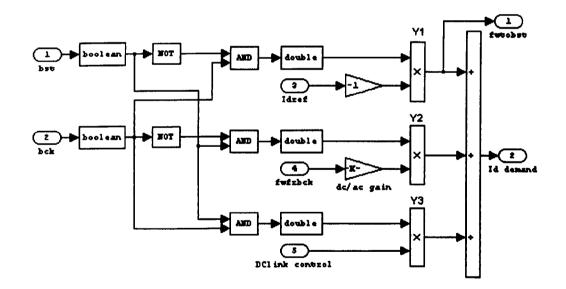

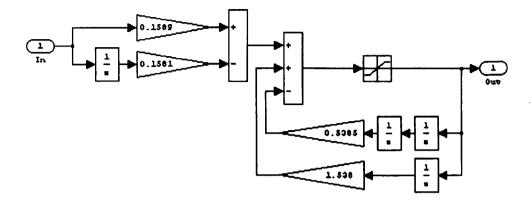

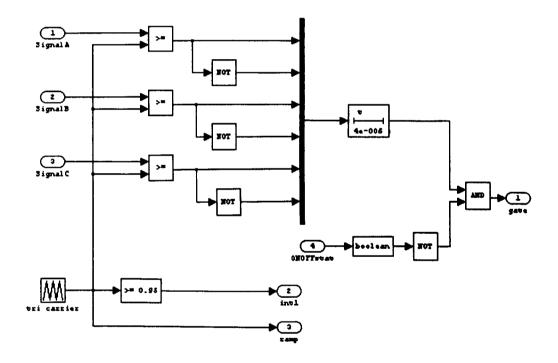

| Figure E-14 Detail of 'mode select' block                   | . 243 |

| Figure E-15 $V_{pcc}$ controller implemented using simulink | . 244 |

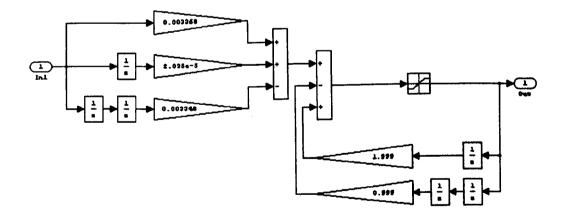

| Figure E-16 'boost control' block                           | . 245 |

| Figure E-17 Boost mode controller                           | . 246 |

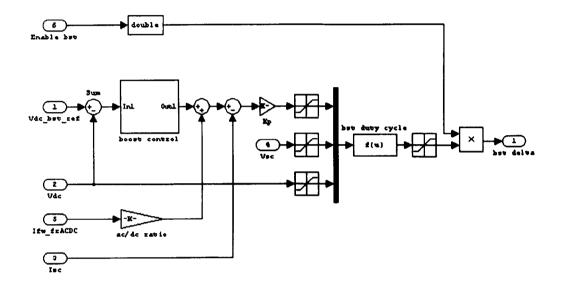

| Figure E-18 'buck control' block                            | . 247 |

| Figure E-19 Buck mode controller                            | . 247 |

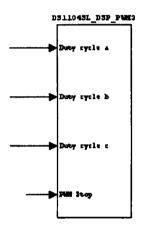

| Figure E-20 PWM generation for the simulation               | . 248 |

| Figure E-21 dSPACE built-in three-phase PWM generator block | . 249 |

| Figure E-22 dSPACE built-in 4-channel PWM generator block   | 250   |

| Figure E-23 Auxiliary control blocks                        | .251  |

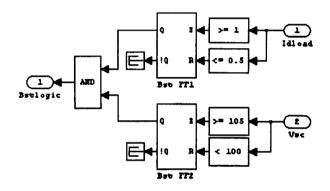

| Figure E-24 'Boost Trigger' block                           | .252  |

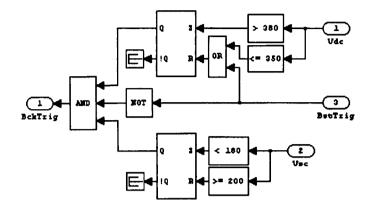

| Figure E-25 'Buck Trigger' block                            | .253  |

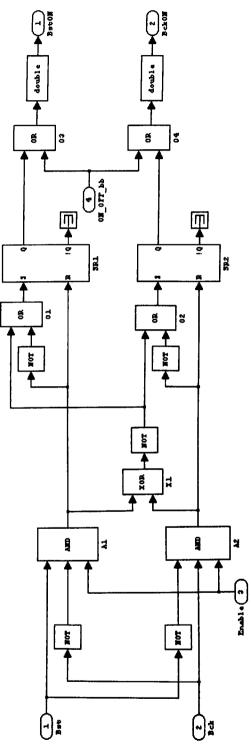

| Figure E-26 'Bck/Bst ONOFF' block                           | 254   |

| Figure E-27 'Protection' block                              | 256   |

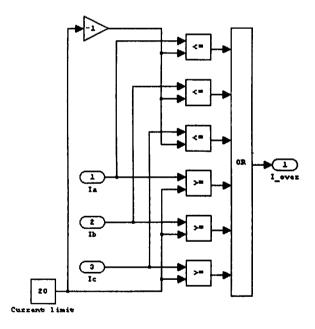

| Figure E-28 'I check' block                                 | 257   |

# **Chapter 1**

# Power system shunt-connected compensators

#### **1.1 Introduction**

The main constituent components of ac power systems are generators, transmission and distribution lines, and loads. The generators are rotating synchronous machines which converts mechanical power into usable electricity. The transmission and distribution lines are the electrical medium used to transport electricity from the generation sites to the load centres. The loads are components or equipment that consume energy. Both real and reactive power have to be supplied to loads. The operation of ac power systems is based on the fundamentals that 1) all the generators connected to the network must run in synchronism with each others in such a way that the corresponding frequency remains constant or varies within an acceptable

#### Power system shunt-connected compensators

range and 2) the voltage levels at all buses should be kept constant or close to the ratings.

In transmission and distribution systems, the lines are characterised dominantly by the distributed reactance (series inductance and shunt capacitance), and the transmitted real power is generally associated with reactive power. Thus, when loading, the voltage profile along the line will differ from the desired level which may cause a large magnitude variation at the load buses and eventually lead to power quality problems and possible voltage instability. Undervoltage will cause low performance of the associated loads, while overvoltage will be the cause of equipment failure due to insulation breakdown. In addition, transient events such as faults, line and load switching, and other disturbances can cause a sudden change of the real power demand in the system. The sudden change of real power causes a generator or a group of generators to accelerate and others to decelerate away from their steady state speed resulting in a variation of the system frequency, and power oscillation. This may lead to the loss of synchronism and even in the separation of some components which can cause cascade failure of the system. Therefore the control of power flow is necessary and has been a priority since the early age of ac power systems in order to maintain good power quality and system stability.

It is clear that transient events always occur in ac power systems although the system operator will have taken every reasonable precaution to reduce the number of them including the improvement of the robustness of the loads. Therefore one of the solutions to limit the effects of the transients is to apply some form of the mitigation device such as a compensator.

In the past, transmission and distribution systems were designed with large stability margins. Permanently connected reactance and mechanically switched shunt capacitors (MSC) and reactors (MSR) have been used to ensure that the voltage profile along the transmission and distribution lines is within the prescribed range. Although both MSC and MSR can be used for loads that vary from hour to hour as a daily variation, the operation of the MSC and the MSR cannot handle fast changes in the reactive power demand. Instead, synchronous condensers (rotating synchronous machines without a prime mover and turbine) were installed to handle the fast changes in reactive power demand, and to minimise power oscillations.

A power system can be interconnected for economic and environmental reasons - avoiding the construction of both new generation and transmission facilities, and for higher utilisation of the existing power systems. Basically the interconnected system provides an increase in stability limits, as more real and reactive power are available than in the separate power system. However to utilise the extra supply available for stability improvement, the control of power has to be rapid. Advances in the recent development of high power semiconductors and power electronic technology have made possible the development of fast compensators, without mechanical movement, for application in power systems. These provide a significant improvement compared to the classical forms of stability improvement such as MSC and MSR.

The aim of this project was to develop a new, fast power electronics based on compensation device capable of compensating quickly for both real and reactive power changes. The device includes supercapacitors as energy storage devices. Before describing the specific aims and objectives of this project, a brief review of existing compensation technology now follows.

#### **1.2 Static VAr Compensators (SVCs)**

Due to the slow response time of the mechanically switched reactor and capacitor shunt compensator, they are not suitable for use as dynamic compensation equipment in ac power systems where a transient event can be severe. Their behaviour results in a steplike output and this is another reason why mechanically switched compensators are not preferable for dynamic compensation.

An SVC operates with the same principle of the MSC and MSR. It generates and absorbs reactive power, but the precise control of the firing angle of a thyristor switch gives the SVC the ability to provide reactive power continuously and sufficient speed of response to handle fast changes. Therefore an SVC can maintain a smooth voltage profile and improve the system stability under various conditions [1].

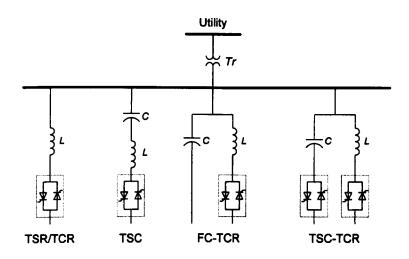

One of the first static VAr compensators was commercially installed for an electric arc furnace compensation in 1972 [1]. For the transmission level, the EPRI funded SVC project was installed in 1978 at the Shanon substation of the Minnesota Power and Light system [2]. In general the SVC can be a combination of a Thyristor Switched Reactor (TSR), a Thyristor Controlled Capacitor (TSR), and a Fixed Capacitor (FC) as shown in Figure 1-1 [1-4]. With the appropriate control coordination of that equipment, the combination can vary the reactive power to meet the required value.

Figure 1-1 Static VAr Compensators (SVCs)

### **1.2.1** Thyristor Controlled Reactor (TCR)

A single-phase thyristor controlled reactor (TCR) consists of a linear reactance of inductance L connected in series with a bidirectional thyristor (a pair of inverse-parallel connected thyristors) as shown in Figure 1-1. The thyristors are made up of high power rating thyristors connected in series in order to gain higher total voltage and current ratings suitable for ac power system applications. In practice three sets of single phase TCRs are usually connected together in delta configuration in order to prevent the triplen harmonic currents i.e. third, ninth, fifteenth produced from the TCRs entering the power systems. The triplen harmonic currents will circulate in the delta configuration.

Reactive power compensation can be obtained and controlled from the minimum value (zero) to the maximum value by controlling the firing angle delay with respect to the applied voltage. A 90 degree firing angle is applied with respect to the ac bus voltage zero crossing to obtain full conduction of the thyristors (the valve is closed); while a 180 degree firing angle will result in no conduction (the valve is open). Unless the firing signals are applied repeatedly, the thyristors will automatically block (turned off) immediately after the current crosses zero [2, 3].

A single-phase thyristor switched reactor (TSR) has its physical arrangement similar to the mentioned TCR, but it is controlled by the firing angle delay at 90 and 180 degree only i.e. at maximum and minimum conduction or open and closed, thus the TSR will not generate harmonics, however with its on-off control operation its application is limited [3].

#### **1.2.2 Thyristor Switched Capacitor (TSC)**

A single-phase thyristor switched capacitor (TSC) is shown in Figure 1-1. It is comprised of a capacitor C, a bidirectional thyristor switch, and a relatively small surge reactor L all connected in series. The small reactor is included in the TSC for the purpose of limiting the magnitude of the inrush current under the worst case occasionally caused by severe transients such as when the uncharged TSC capacitor is initially energized. Without this reactor the inrush current may reach beyond the withstand rating of the thyristor. This reactor is also used to prevent the thyristor from severe damage due to the high surge current under abnormal operating conditions. It may be designed to avoid resonances of TSC with the system impedance [2]. A three-phase TSC application is also performed by three sets of the single-phase components connected in delta the same as for the configuration for the TCR/TSR.

However, unlike the TCR/TSR where the current through and the voltage across the reactor will automatically cease after the thyristor is turned off, the voltage across TSC capacitor will be at its peak value when the TSC branch current reaches zero. The capacitor voltage then remains charged at peak value. As a consequence, a double voltage stress appears on the nonconducting thyristor and it is necessary to increase the number of series thyristors in a valve string. Therefore the number of thyristors used is twice the number used for the TCR/TSR. Turning on the TSC branch should be made while the voltage across the thyristor valve is zero, when the applied voltage is equal to the capacitor residual voltage i.e. when dv/dt = 0 at peak value of the applied voltage to avoid any severe transients.

The gating causes the thyristor valve to conduct for a half cycle period. Therefore the TSC can not provide the capacitance continuously but in a discrete or step pattern.

[6]

## 1.2.3 Fixed Capacitor-Thyristor Controlled Reactor (FC-TCR)

A Fixed Capacitor-Thyristor Controlled Reactor (FC-TCR) is a combination of a permanently connected shunt capacitor or fixed capacitor and a TCR. A basic circuit for the FC-TCR is shown in Figure 1-1. The fixed capacitor provides a constant leading VAr. Some of this is cancelled by the variable lagging VAr of the TCR, resulting in a fully controlled and smooth compensation.

The operation of FC-TCR is dominated by the controlling of the TCR as explained in section 1.2.1. In principle the disadvantage of this SVC is the losses they produce; even at zero VAr output, standby losses exist. Because their operation is based on the cancellation of the current through both the fixed capacitor and the TCR, at zero VAr output, some current flows through the TCR to cancel the fixed capacitance and this generates loss. The overall losses increase with the TCR current, but conversely decrease with capacitive VAr output. It is good for industrial applications where high capacitive VAr is required for power factor correction, but has poor dynamic compensation which may be a disadvantage for transmission systems [2].

## 1.2.4 Thyristor Switched Capacitor-Thyristor Controlled Reactor (TSC-TCR)

The basic concept of a combined Thyristor Switched Capacitor-Thyristor Controlled Reactor (TSC-TCR) is indicated in Figure 1-1. In practice there may be many paralleled TSC branches in order to provide the coarse steps of capacitive VAr, and one large TCR to adjust a fine continuous control VAr in between them. It was mainly developed with the intention to minimise the standby losses and for dynamic compensation. The basic principle operation is that the TSC branches will be switched in to provide compensation slightly (i.e typically above 5%) above the VAr required value, and then TCR will absorb the surplus VAr to get the precise output VAr. At zero VAr output the TSC branches will be switched out and no TCR is required to cancel the fixed VAr. Therefore the loss at the standby point is zero or nearly zero. At other operating points, the losses will vary depending on the surplus capacitive VAr [2, 3].

#### **1.3 STATic COMpensator (STATCOM)**

In the previous sections, reactive power generated by means of SVC is based on using thyristors as control elements to vary the reactive power produced by passive power components, the capacitor and reactor banks. However the recent developments in the field of high power, power electronic devices has demonstrated the use of static VAr generator which is not based on capacitor and reactor banks. Only a small DC-link capacitor is used, but the device can provide both capacitive and inductive VAr. Therefore it may be possible to improve the size and cost of the static VAr generator in the future [2].

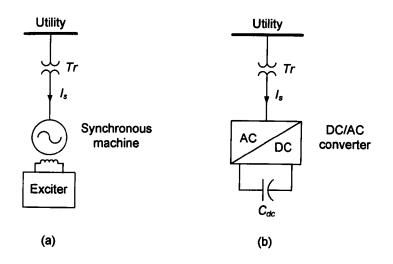

A recently developed VAr generator is called STATic COMpensator (STATCOM). In principle, the operation of the STATCOM is comparable to a synchronous condenser. A simplified circuit arrangement of both the synchronous condenser and the STATCOM is shown in Figure 1-2 [1, 3].

Figure 1-2 The simplified representation of (a) a synchronous condenser and (b) a STATCOM

The synchronous condenser shown in Figure 1-2 (a) consists of a rotating synchronous machine with its excitation system, and a transformer 'Tr' to adapt the voltage to the utility level at the point of common coupling,  $V_{pcc}$  (if required). The relationship of the synchronous condenser voltage and current during inductive and capacitive generation is shown in Figure 1-3.

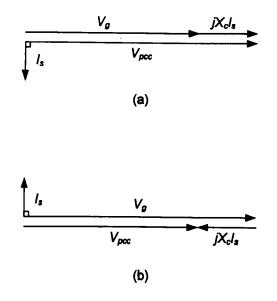

Figure 1-3 The simplified representation of a synchronous condenser voltage and current when operated as (a) inductive VAr generator, and (b) capacitive VAr generator

Where

- $V_g$  is the voltage generated by the synchronous condenser, V.

- $V_{pcc}$  is the voltage at utility bus at the point of common coupling, V.

- $I_s$  is the support current flowing between the utility bus and VAr generator, A.

- $X_c$  is the equivalent reactance of a coupling reactor and transformer,  $\Omega$ .

In Figure 1-3 (a) when the synchronous condenser is underexcited, it generates a voltage  $V_g$  which is in-phase with the utility voltage  $V_{pcc}$  but with a magnitude lower than that of  $V_{pcc}$ . The resulting voltage drop across the equivalent reactance  $jX_cI_s$  gives a 90 degree lagging current  $I_s$  (with respected to the utility voltage). This example indicates that the synchronous condenser is operating in inductive VAr mode or is absorbing VAr from the  $V_{pcc}$  bus. On the other hand, Figure 1-3 (b) shows that the synchronous condenser is operating in capacitive VAr mode or is injecting VAr into  $V_{pcc}$  bus when the synchronous condenser is overexcited. The voltage  $V_g$  is raised to a level higher than that of utility voltage  $V_{pcc}$  (still in-phase with  $V_{pcc}$ ) and the voltage drop across the equivalent reactance results in a 90 degree leading current  $I_s$ .

The operating principle of the synchronous condenser depends on the current flow through the equivalent reactance which is governed by the basic relationship as in Equations (1-1), (1-2) and (1-3)[5, 6].

$$I_s = \frac{V_g - V_{pcc}}{jX_c} \tag{1-1}$$

$$P = \left(\frac{v_g - v_{pcc}}{x_c}\right) \sin \delta \tag{1-2}$$

$$Q = \left(\frac{v_g v_{pcc}}{x_c}\right) \cos \delta - \left(\frac{v_{pcc}^2}{x_c}\right)$$

(1-3)

Where

- P is the real power flows between the generated voltage and utility bus, W.

- Q is the reactive power flows between the generated voltage and utility bus, VAr.

- $\delta$  is the phase displacement angle between the generated voltage and utility voltage, degree.

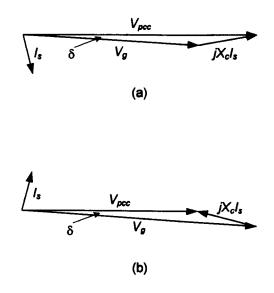

In practice as the synchronous condenser is not driven by a mechanical input power from a prime mover, its overall losses are then supplied by the system utility. As a result, the generated voltages will not be in-phase ideally with utility voltage, but lags slightly by an angle  $\delta$  which can be derived from Equation (1-2). Therefore, the current I<sub>s</sub> will not be the ideal value of 90 degrees leading or lagging. There will also be a slight variation depending on losses as illustrated in Figure 1-4.

Figure 1-4 The representation of a synchronous condenser voltage and current when operated, with losses, as (a) inductive VAr generator, and (b) capacitive VAr generator

The STATCOM shown in Figure 1-2 (b), consists of a dc-to-ac voltage source converter VSC, a small DC-link capacitor  $C_{dc}$ , and a coupling reactor with a

transformer required to connect to the  $V_{pcc}$  bus. As mentioned above, the basic operating behaviour of the STATCOM resembles that of the synchronous condenser described with Figure 1-3 and Figure 1-4. If the voltage produced by the VSC is higher than the utility voltage at which it is connected to, the STATCOM operates as a capacitive VAr generator injecting reactive power to the utility. Conversely if the voltage produced is less than utility voltage, the STATCOM will absorb reactive power from the utility acting as a reactive load [2, 3, 5]. As with synchronous condenser operation, the losses of the STATCOM are usually supplied by the utility, not from the DC-link capacitor. A slight angle difference of the voltage generated by the STATCOM and utility voltage indicates the losses in the STATCOM system.

Compared to the synchronous condenser, the STATCOM has a faster response time for reactive compensation [7-11] although, apart from the way they create their voltage, their compensation principles are very similar. Furthermore, the STATCOM can be used with energy storage in order to improve the ability to increase power system stability [12]. Furthermore, unlike the rotating synchronous machine the STATCOM contributes less fault current when faults occur.

In ac power systems, there will be a significant improvement in the stability if the compensation equipment can contribute a sufficient amount of the real and reactive power to the system during short period disturbances [12, 13]. However, the ability of the standard STATCOM is limited as its operation will be actively possible for only reactive power compensation as described with Figure 1-3. The STATCOM DC-link voltage will vary massively when exchanging real power with the utility due to the limited energy storage capacity of the DC-link capacitor used. At any instance if the drop of DC-link voltage is obvious, due to the lack of energy in the dc side, the STATCOM cannot produce a sufficient output voltage, and this will cause the STATCOM to trip. Some examples of applications of the STATCOM have been reported in [11, 14-16].

#### Power system shunt-connected compensators

To improve the STATCOM's performance, a significant amount of energy is needed in order to keep the DC-link voltage constant at the level that the STATCOM can produce the required voltage for real power compensation. A constant DC power supply would be ideal for this performance improvement, but if its primary source is the same ac supply for the ac side of the STATCOM, compensation is impossible. Adding energy storage to the DC-link capacitor is an option resulting in the STATCOM that can actively inject and absorb real and reactive power from the utility. The additional energy storage will give the STATCOM the flexibility to control the support current fully in all four quadrants as shown in Figure 1-5(b) compared to the standard STATCOM current shown in Figure 1-5 (a). This compensation with a mixed support of real and reactive power is the best solution for many cases in power systems [13].

Figure 1-5 The comparison of the current controlled by the ideal (a) standard STATCOM, and (b) STATCOM with energy storage

In Figure 1-5(b) the shaded area indicates the active area for the current controlled by the STATCOM with a significant amount of energy in the dc side. Both the real power current  $I_p$  and the reactive power  $I_q$  can be controlled flexibly within the shaded area bounded by the STATCOM rating, while the standard STATCOM can control only the reactive current as shown in Figure

1-5(a). Some examples of STATCOM enhanced with energy storage can be found in the literature review in the technical research publication [17-21].

### 1.4 A comparison between STATCOM and SVC

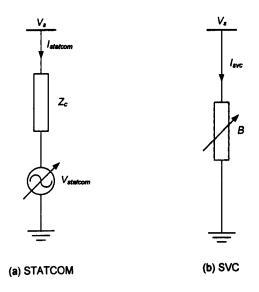

The equivalent circuit of a STATCOM compared with that of a SVC is shown in Figure 1-6. The STATCOM is modelled using a variable voltage source  $V_{statcom}$  connected in series with the impedance of the coupling reactor  $Z_c$  (and of the transformer) coupled to the power system voltage  $V_s$ . As a result, this circuit will operate as a current source connected to the ac power system with its capability depending on the output terminal voltage  $V_{statcom}$  produced electronically [1]. In contrast, the SVC is modelled using a variable susceptance B indicating that the amount the compensation will be controlled by varying the susceptance, and clearly it is dependent on the system voltage  $V_s$ .

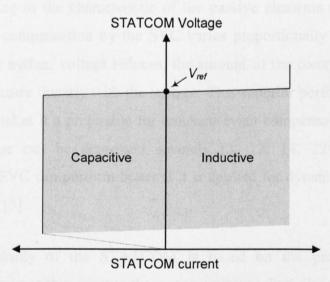

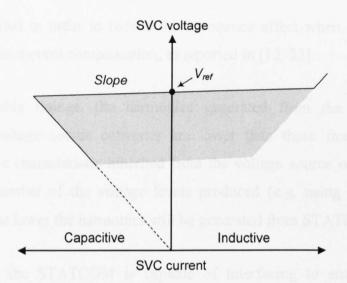

Figure 1-6 The equivalent circuit of (a) STATCOM and (b) SVC

The compensation characteristics of both the STATCOM and SVC are shown in Figure 1-7 and Figure 1-8 respectively. Typically they are required to operate with a specific slope reactance as illustrated in the figures in order to provide a linear operating region for the compensation. This slope is designed in order to prevent the severe oscillations which may occur at the limits if the compensator is designed to operate without a regulation droop (zero slope). In general, the regulation slope is in the range of 2 to 5% which allows the voltage variation of up to  $\pm$ 5% around the reference voltage [3, 4]. Therefore, the regulation droop of the V-I characteristic shown in Figure 1-7 and Figure 1-8 indicate that the terminal voltage will be allowed to be a value smaller than the nominal no-load value when it reaches full capacitive compensation, and also the terminal voltage will be allowed to be higher than the nominal voltage if it is at full inductive compensation.

Figure 1-7 V-I characteristic of STATCOM

Figure 1-8 V-I characteristic of SVC

Considering both the V-I characteristics of the STATCOM and SVC, the STATCOM has a better performance. It can be seen clearly that the STATCOM can continue to operate with its rated current (as indicated by the shaded area) although the system voltage is reduced down to a very low level, while according to the characteristic of the passive elements (capacitor and inductor) the compensation by the SVC varies proportionally to the system voltage. If the system voltage reduces, the amount of the compensation from the SVC decreases linearly with the voltage. This superior performance of the STATCOM makes it a preferable for transient event compensation where the system voltage can be depressed severely [3, 12, 14, 22]. However a conventional SVC can perform better if it is applied for dynamic overvoltage compensation [3].

The controllability of the STATCOM is based on the production of a sinusoidal voltage with respect to the system voltage – both the magnitude and phase can be adjusted very rapidly (within milliseconds). For the SVC the compensation is controlled by varying the conduction period of the thyristor to adjust the susceptance of the capacitor and reactor. This may react with the system impedance to cause a severe resonance. Therefore the SVC control

speed is limited in order to reduce this resonance effect when applying the SVC to transient event compensation, as reported in [12, 23].

For comparable ratings, the harmonics generated from the STATCOM employing voltage source converter are lower than those from the SVC. Regarding the characteristic inherited from the voltage source converter, the higher the number of the voltage levels produced (e.g. using a multilevel converter), the lower the harmonics will be generated from STATCOM [12].

Furthermore, the STATCOM is capable of interfacing to energy storage devices in order to improve the performance in such a way that the compensation can be provided with a mixture of real and reactive power support, which makes it better to compensate for the transient stress as mentioned above.

#### **1.5 Project objectives**

For many cases in ac power systems, especially during transient stressed conditions the lack of real power support from system compensators may lead to the failure due to low stability margins. A STATCOM with the ability to support both reactive and real power dynamically can provide a significant improvement to the security of ac power systems, even if the real power is only supported for a short period of time.

The aim of this thesis is to investigate the use of a SuperCapacitor Energy Storage System (SCESS) to enhance the performance of a conventional STATCOM. The supercapacitor, a newly developed energy storage device, is suitable for short-period charge/discharge applications. The proposed STATCOM with SCESS will therefore offer a superior ability to compensate with a mixture of both real and reactive power that can be useful for the shortperiod stressed conditions in ac power systems. Simulation work will be

#### Power system shunt-connected compensators

carried out to demonstrate the benefits to an ac power system using the STATCOM, and using the STATCOM plus SCESS, within a specific system scenario to support the proposed idea. Finally, experimental tests will be carried out to validate the proposed control technique. The main objectives of this project can be summarised as below:-

- I. To investigate the use of the enhanced STATCOM with energy storage for improving the stability within the system with distributed generation (DG).

- II. To determine the circuit configuration and control methods required for creating a STATCOM plus SCESS.

- III. To investigate the SuperCapacitor Energy Storage System (SCESS) applied for enhancing the performance of the conventional STATCOM.

- IV. To demonstrate the benefits of an ac power system using the enhanced STATCOM with SCESS.

#### 1.6 Thesis overview

In order to accomplish the objectives of this project, this thesis presents the work undertaken in the following seven chapters which are briefly described below.

In chapter 2, power system improvement using the enhanced STATCOM with energy storage is described. The Distributed Generation (DG) plants are mentioned briefly. An analysis of instability within the system with DG is

#### Power system shunt-connected compensators

discussed with mathematical support. The minimum amount of the energy required to be applied with the STATCOM is derived from the analysis, with the aim to minimise the instability caused by the rate of change of frequency (ROCOF). Simulations were carried out in order to support the idea.

In chapter 3 the details of the conventional or standard STATCOM including the operation and design are presented. The vector control strategy for the STATCOM is designed step by step including the current control, DC-link voltage control, and the external loop control design for the ac grid support is described. A simulation to demonstrate the benefits of an ac power system using the standard STATCOM that is implemented with digital controller is also explained in chapter 3.

In chapter 4 the brief review of energy storage technologies is presented in the beginning of the chapter. The SCESS and its control technique are described in greater detail including the dc-to-dc bidirectional power converter which is used as the main control device in SCESS. A simulation to demonstrate the benefits of an ac power system using the enhanced STATCOM with supercapacitor energy storage is then explained at the end of this chapter.

In chapter 5 the overall experimental setup regarding the system scenario used in the simulation work is described section by section from the major components to the supporting components. Practical circuit diagrams are explained fully with the graphical illustration and images of the hardware built for the experimental tests. The dSPACE digital controller board is also described.

In chapter 6 the experimental results are illustrated and the explanation of those results is clearly documented with each result. In order to experimentally validate the main idea of this thesis, the superior performance of the enhanced STATCOM is highlighted at the end of this chapter

Finally chapter 7 gives the conclusions of this project. Some useful suggestions for the future work that can be continued from this project are presented briefly.

.

# **Chapter 2**

# Power system stability improvement using STATCOM with energy storage

#### 2.1 Introduction

The first priority for operating ac power systems is to secure the condition that the whole system can supply energy to meet the demand, even in the presence of system disturbances. An ac power system operating under this condition is generally called a stable system. The voltage magnitude and angle at each unit (bus) of the system reflects power flows from generating buses to load buses. Therefore this condition is a balance between generation and consumption. For stable systems, at the generation units the mechanical power input by the prime mover of the generator equals the electrical power consumed plus losses, transmitting to and from other buses. The stability of the ac power system requires that the amount of the mechanical power converted is equal to the electrical power consumed.

Considering the generator in mechanical terms, this balance leads to the condition that the accelerating torque applied to the shaft of the prime mover equals the decelerating (retarding) torque caused by the electrical output of the generator. Zero net torque results if the shaft of the generator is rotating at a constant speed, generally called synchronous speed. In electrical terms, the system frequency is directly proportional to the speed of the generator. Thus, the constant speed of the rotating shaft gives the constant system frequency. Disturbances causing imbalance between the mechanical and electrical power will result in a change in the rotor speed and thus the system frequency. However if the systems are able to automatically return to the balanced condition again, they are called stable systems [6].

Recently the study of ac power systems has been concerned with embedded or distributed generation (DG) which has increasingly penetrated into the distribution networks, where generation can be located close to the consumers in order to minimise transmission losses. Although many utilities have brought the benefits of distributed generation to their systems, there are some other impacts which must be considered. In this chapter DG and its technical impacts on the system are described, and proposals are introduced to minimize these technical impacts.

# 2.2 Distributed generation

The aim of Distributed Generation (DG) is to provide power sources close to the demand centre i.e. DG is embedded in the distribution network. Therefore, unlike the conventional distribution network, DG provides the capability of interacting with the power system and becoming an active distribution network. DG can be classified as smaller generation (compared to the central generation) which is embedded in or connected to distribution networks to supply the consumer demand locally, and it is not planned and dispatched centrally by the utility [24-27].

# 2.2.1 DG plants

There are several types of the DG plants connected to distribution networks. According to the energy sources used to generate electricity, the DG can be categorised into two groups – the combined heat and power plant, and the renewable energy plant. The latter normally requires further compensation as it may be an intermittent primary source.

# 2.2.1.1 Combined heat and power plant

In general, primary energy sources such as coal, petroleum, natural gas and uranium are used to generate electricity through a thermal process. However they can not convert all of their thermal energy into electricity, and approximately half the energy (heat) is lost and emitted through the cooling systems as wasted heat.

In a combined heat and power plant (CHP), also known as cogeneration, the excess heat is captured and used locally on site or close to the site i.e. the CHP can produce electrical power and useable heat simultaneously. It is mostly implemented with a synchronous generator; however some plants may use an induction generator to generate electricity. CHP is the most significant distributed generation technology embedded in distribution networks [25].

# 2.2.1.2 Renewable energy plant

For renewable energy plants, unlike CHP, their siting is determined by the location of the primary renewable energy sources. Their electrical output power is also dependent on the availability of the energy source. The generator used must be operated when the primary energy is available, unless the plant is capable of energy storage.

The output of wind power plants is proportional to the wind speed, which differs depending on the locations. It is obvious that to integrate the wind power plant into an ac power network, wind turbines need to be located in areas where wind resource is available. Mostly the available positions for wind power plants are away from residential areas which can make it difficult to connect to the distribution network, and sometimes leading to a considerable amount of the investment.

For wind farm power plants, because of the fluctuation of the turbine speed according to windspeed variation, induction generators with the associated gearbox appear to have become the preferred choice due to their high reliability, robustness, and low cost and maintenance [25, 28-30]. If an adequate mechanical damping system or power electronic conversion system is included to complement the aerodynamics of the turbine, a synchronous generator can be used [21, 25, 31]. Similarly in the small and medium hydro-electric plants, induction or synchronous generators are installed for converting the flows of water to the consumable electricity dispersed within distribution networks.