# Space Vector Modulation of a 4-Leg Matrix Converter

Nicholas J. Mason, BEng. MSc.

Thesis submitted to The University of Nottingham for the degree of Doctor of Philosophy

November 2011

I'd like to dedicate this work to my father, David Mason, who passed away before he was able to see its completion, and whose memory is, and will always be, an inspiration to me.

# Abstract

THIS thesis covers the investigation into the use of Space Vector Modulation for the control of a 4-leg matrix converter, which is capable of providing a 3-phase plus neutral supply from a standard balanced 3phase source. Traditional 3x3 matrix converters have limited use in this application as they are only capable of supplying a balanced three-phase load. It would be desirable to be able to power unbalanced and nonlinear loads, requiring that the converter provides a neutral connection. As with voltage source inverters, this goal can be achieved by extending the number of output legs in the matrix converter to four. In this thesis, a new Space Vector Modulation technique is proposed for this 4-leg, or 3x4, matrix converter. This technique is an extension of the method currently in use on 3x3 matrix converters, and so it allows the de-coupled control of both the input and output. The thesis then goes onto cover the build of a demonstration converter, looking at the different aspects which make up a converter, to finally go on to prove the theory, and a set of results are presented to validate this.

# Acknowledgements

I would like to express my utmost thanks for my supervisors, Prof. P. Wheeler and Prof. J. Clare, for both of their guidance and support, and most importantly, for their utmost patience in me. I am sure there were times when they, like me, gave up hope that this work would ever be completed, but their willingness to help always meant that I could get going going again.

I'd do also like to thank all of the staff within the PEMC group at the University of Nottingham who have helped me over the now many years that this work has been in progress. Alongside this I would like to specifically thank Dr Lee Empringham and Dr Alan Watson for there help at times with the build of the converter, who, along with the workshop technicians were always happy to help when I needed it and whose help is much appreciated.

I'd then like to thank my family and friends, they have been such a immense support to me, more so than I think many of them know. They have often picked me up and brushed me off when times were bad, and so to them I owe a debt of gratitude. In particular though I would like to say so many thanks to my wonderful partner Elizabeth Heslop, without her help and support over the months and years that this has taken, through the sad times and the happy, I am sure it would never have been finished, and so for that I am eternally thankful. I'd also like to say thank you to my mother, who's always been a support to me, and has really helped so many times.

And finally like to thank my sponsor, the Engineering and Physical Science Research Council(EPSRC), without whose support I would not have been able to embark on this course of study, and I am sure they, as much as anyone will be happy for me to complete.

# Contents

| A | Acronyms xvii    |                                                                  |    |

|---|------------------|------------------------------------------------------------------|----|

| 1 | 1 Introduction 1 |                                                                  |    |

|   | 1.1              | The Matrix Converter                                             | 3  |

|   | 1.2              | The 4-leg Inverter                                               | 6  |

|   | 1.3              | The 4-leg Matrix Converter                                       | 7  |

|   | 1.4              | Applications and Limitations                                     | 7  |

|   | 1.5              | Objectives                                                       | 8  |

|   | 1.6              | Thesis Overview                                                  | 9  |

| 2 | Fou              | r-Leg Inverter Modulation                                        | 11 |

|   | 2.1              | Space Vector Modulation of the 4-Leg 4-Wire Inverter             | 13 |

|   | 2.2              | Carrier Based Pule-Width Modulation of the 4-Leg 4-Wire Inverter | 19 |

| 3 | Mat              | trix Converter Modulation                                        | 23 |

|   | 3.1              | Basic theory                                                     | 24 |

|   | 3.2              | Alesina/Venturini Method                                         | 26 |

|   | 3.3              | Alesina/Venturini Optimum Method                                 | 27 |

|   | 3.4              | Space Vector Modulation                                          | 29 |

| 4 | Con              | nmutation Methods                                                | 36 |

|   | 4.1              | Overlap Commutation                                              | 37 |

|   | 4.2              | Dead-time Commutation                                            | 38 |

|   | 4.3              | 4-Step Commutation                                               | 39 |

|   | 4.4              | Threshold 2-Step Current Commutation                             | 40 |

#### CONTENTS

|   | 4.5  | Voltag  | e Sensed Current Commutation 4                                 | 2  |

|---|------|---------|----------------------------------------------------------------|----|

| 5 |      |         | of the Space Vector Modulation technique for the x Converter 4 | 5  |

|   | 5.1  | The In  | uput Voltage Plane                                             | 6  |

|   | 5.2  | The In  | put Current Plane                                              | 8  |

|   | 5.3  | The O   | utput Voltage Space                                            | 9  |

|   | 5.4  | The Sv  | witching States                                                | 52 |

|   |      | 5.4.1   | Output Voltage and Switching States 5                          | 57 |

|   |      | 5.4.2   | Input Current and Switching States 6                           | 60 |

|   | 5.5  | Deterr  | mining the output sector 6                                     | 52 |

|   | 5.6  | Deterr  | mining the input sector                                        | 66 |

|   | 5.7  | Selecti | ing the Switching States 6                                     | 58 |

|   | 5.8  | Comb    | ining the Input and Output Spaces                              | 0  |

|   | 5.9  | Calcul  | lating the Duty Cycles                                         | 74 |

|   | 5.10 | Voltag  | e Transfer Ratio                                               | 80 |

|   | 5.11 | Other   | Four-Leg Matrix Converter Modulation Methods 8                 | 88 |

| 6 | Sim  | ulation | of the 4-leg Matrix Converter 9                                | 0  |

|   | 6.1  | Simula  | ation using Matlab                                             | 91 |

|   |      | 6.1.1   | 4-Leg Inverter                                                 | 91 |

|   |      | 6.1.2   | 4-Leg Matrix Converter                                         | 0  |

|   | 6.2  | Simula  | ation using Saber                                              | 26 |

|   |      | 6.2.1   | Saber Simulation Results                                       | 66 |

|   |      | 6.2.2   | Further Saber Simulation Work                                  | 4  |

| 7 | Mat  | rix con | verter design and construction 20                              | )1 |

|   | 7.1  | Introd  | uction and overview                                            | )1 |

|   | 7.2  | Matrix  | Converter Power Circuit                                        | )3 |

|   |      | 7.2.1   | Devices                                                        | )4 |

|   |      | 7.2.2   | Gate Drive Circuit                                             |    |

|   |      | 7.2.3   | Output Current Sensing                                         | )7 |

|   |      | 7.2.4   | Input Voltage Sensing                                          |    |

|    |        | 7.2.5   | Clamp Circuit                              | 210 |

|----|--------|---------|--------------------------------------------|-----|

|    |        | 7.2.6   | PCB Design and implementation              | 210 |

|    |        | 7.2.7   | Input Filter                               | 211 |

|    |        | 7.2.8   | Output Inductors and Load                  | 212 |

|    | 7.3    | Matrix  | Converter Control                          | 213 |

|    |        | 7.3.1   | Digital Signal Processor                   | 213 |

|    |        | 7.3.2   | Field Programmable Gate Array              | 217 |

|    |        | 7.3.3   | Host Port Interface                        | 220 |

|    |        | 7.3.4   | Matlab/PC                                  | 221 |

| 8  | Exp    | erimen  | tal Results                                | 224 |

|    | 8.1    | Initial | Testing                                    | 224 |

|    | 8.2    | Balanc  | ced Load                                   | 225 |

|    | 8.3    | Unbal   | anced Load                                 | 233 |

|    | 8.4    | Summ    | nary                                       | 237 |

| 9  | Con    | clusior | 15                                         | 238 |

| Α  | Pap    | ers pub | lished as a result of this work            | 240 |

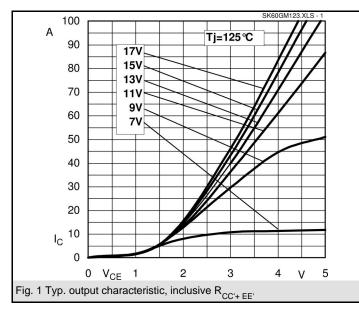

| В  | IGB    | T Data  | sheet                                      | 241 |

| C  | FPG    | GA Men  | nory Locations within the DSP Memory Space | 247 |

| Re | eferer | nces    |                                            | 253 |

# List of Figures

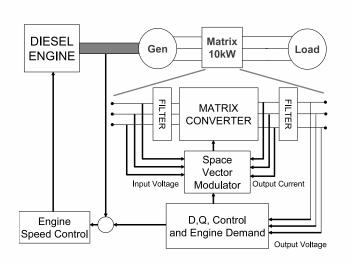

| 1.1  | An Example of a Standalone Power Supply System using<br>a variable speed generator    | 2  |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | A 4-Leg Matrix Converter as part of a Standalone Power<br>Generation System           | 2  |

| 1.3  | A 3-phase Cycloconverter                                                              | 4  |

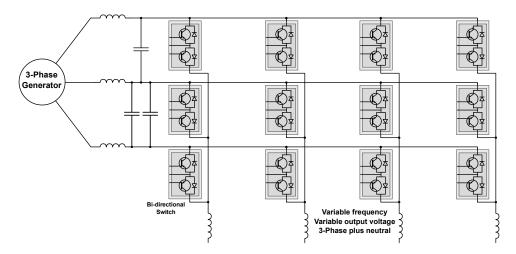

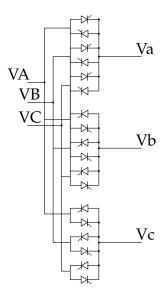

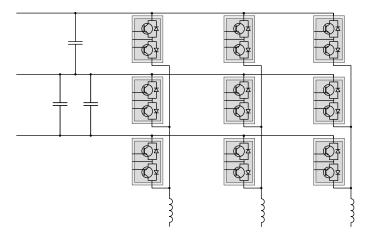

| 1.4  | A 3-Leg Matrix Converter                                                              | 5  |

| 1.5  | A 4-Leg Inverter                                                                      | 6  |

| 1.6  | A 4-Leg Matrix Converter                                                              | 7  |

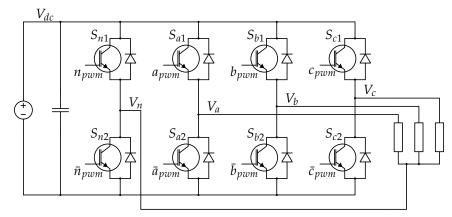

| 2.1  | 3-Leg 4-Wire Inverter with a Split dc Neutral Connection .                            | 11 |

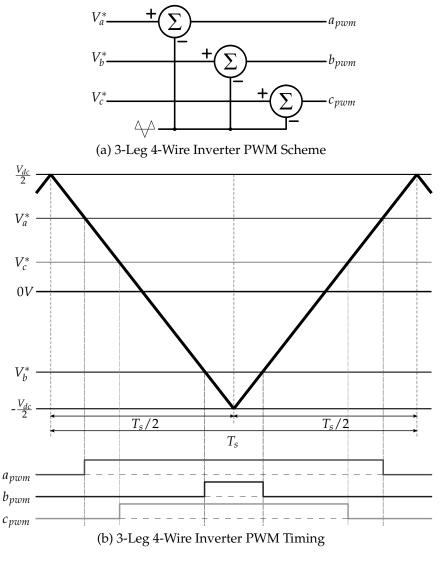

| 2.2  | 3-Leg 4-Wire Inverter PWM                                                             | 12 |

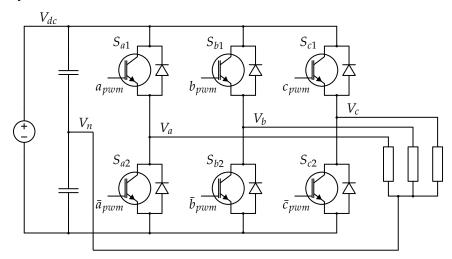

| 2.3  | 4-Leg 4-Wire Inverter                                                                 | 13 |

| 2.4  | 3-Leg Inverter Demand Vector                                                          | 15 |

| 2.5  | 4-Leg Inverter Switching Vectors                                                      | 17 |

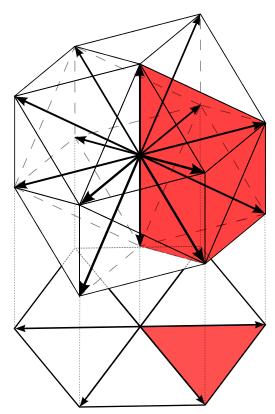

| 2.6  | 4-Leg Inverter Demand Vector                                                          | 18 |

| 2.7  | 4-Leg Inverter Demand Vector Tetrahedron                                              | 19 |

| 2.8  | 4-Leg Inverter Space Vector Modulation PWM Output                                     | 19 |

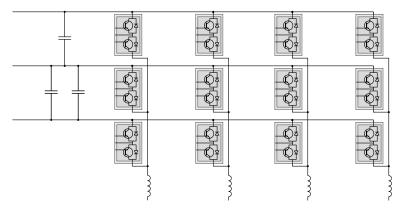

| 2.9  | 4-Leg 4-Wire Inverter                                                                 | 20 |

| 2.10 | 4-Leg 4-Wire Inverter Carrier-based PWM                                               | 22 |

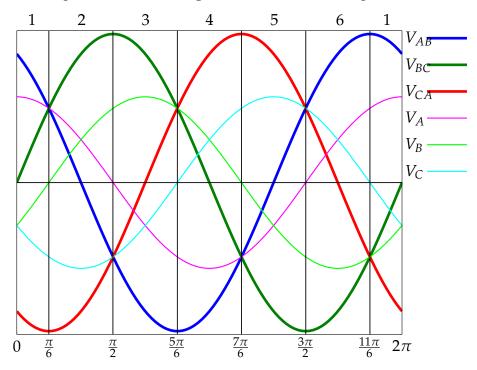

| 3.1  | Base set of SVM Vectors for a Balanced 3-Phase Set plotted in the $\alpha\beta$ plane | 30 |

| 3.2  | Output Voltage Vectors plotted in the $\alpha\beta$ plane                             | 33 |

| 3.3  | Input Current Vectors plotted in the $\alpha\beta$ plane                              | 34 |

| 3.4  | Input Current and Output Voltage Sectors, showing the required switching states       | 34 |

| 4.1 | Segment from a Matrix Converter Circuit                                                          | 36 |

|-----|--------------------------------------------------------------------------------------------------|----|

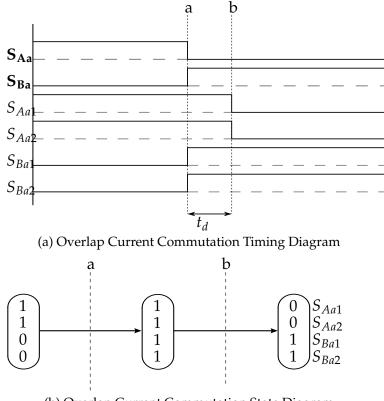

| 4.2 | Overlap Current Commutation                                                                      | 37 |

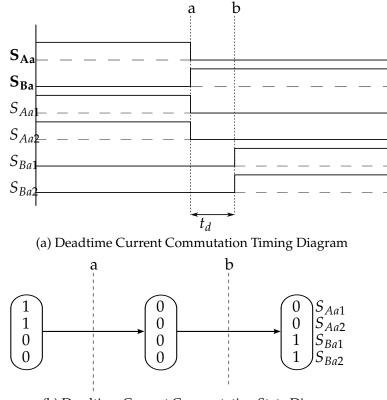

| 4.3 | Deadtime Current Commutation                                                                     | 38 |

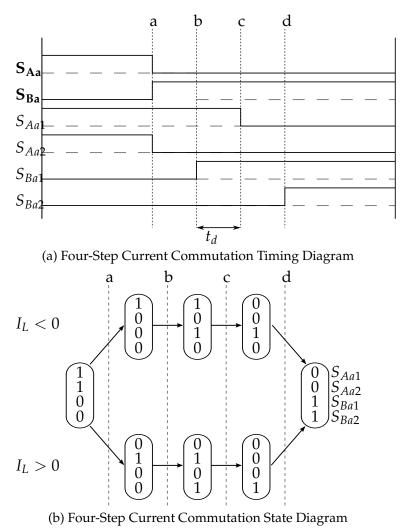

| 4.4 | Four-Step Current Commutation                                                                    | 40 |

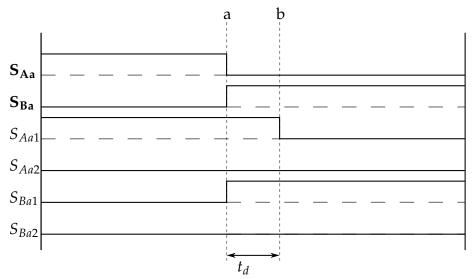

| 4.5 | Threshold 2-Step Current Commutation                                                             | 41 |

| 4.6 | Threshold 2-Step with Low Current Deadtime Commuta-                                              | 42 |

| 4.7 |                                                                                                  | 43 |

| 4.8 | Voltage Sensed Current Commutation                                                               | 44 |

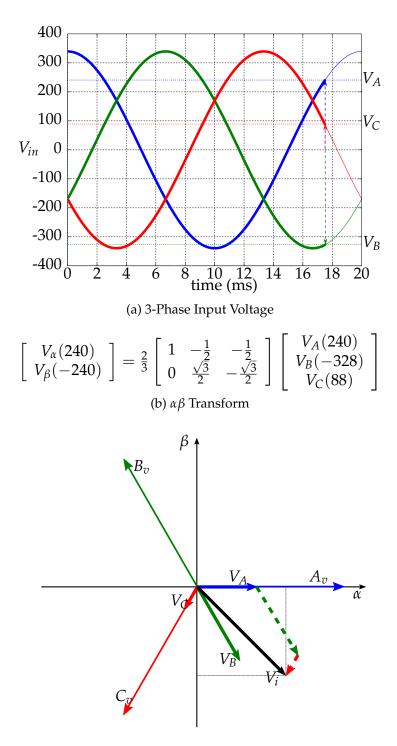

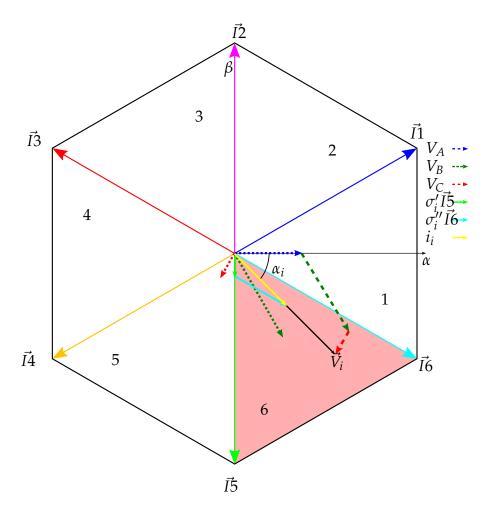

| 5.1 | Input $\alpha\beta$ space showing the 3 primary input voltage vectors                            | 47 |

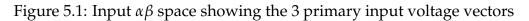

| 5.2 | Input $\alpha\beta$ space showing the 3 primary input current vectors                            | 49 |

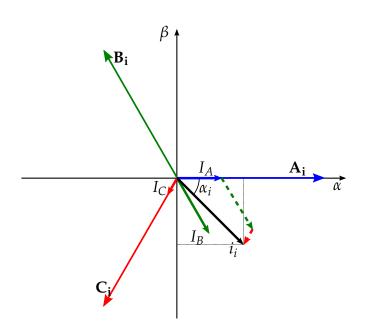

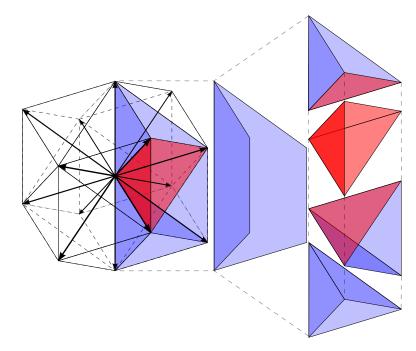

| 5.3 | Output $\alpha\beta\gamma$ space showing the 4 primary output voltage vectors                    | 51 |

| 5.4 | 3x3 Matrix Converter stationary vectors                                                          | 53 |

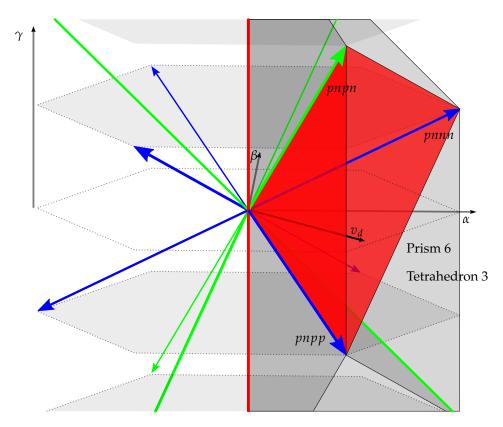

| 5.5 | Stationary vectors plotted in $\alpha\beta\gamma$ space                                          | 57 |

| 5.6 | Stationary vectors plotted in $\alpha\beta\gamma$ space                                          | 60 |

| 5.7 | Stationary Current vectors plotted in $\alpha\beta$ space                                        | 61 |

| 5.8 | Projection of the $\alpha\beta\gamma$ Vector Space onto the $\alpha\beta$ plane                  | 62 |

| 5.9 | Exploded Diagram of how the Tetrahedrons make up a Prism                                         | 63 |

| 5.1 | 0 Input Current Plane showing input current vector $i_i$                                         | 67 |

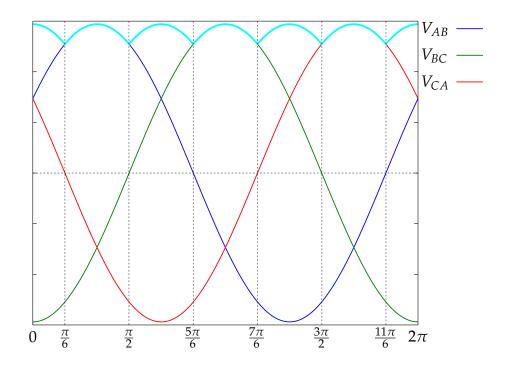

|     | 1 Line and Phase Voltage plots showing current sector                                            | 69 |

| 5.1 | 2 Demand Vector generation from the 3 Space Vectors                                              | 70 |

| 5.1 | 3 Input Current Vector generation from the 2 Space Vectors .                                     | 72 |

| 5.1 | 4 Distance of the vector $\vec{v_d}$ from the plane $Ov_2v_3$                                    | 75 |

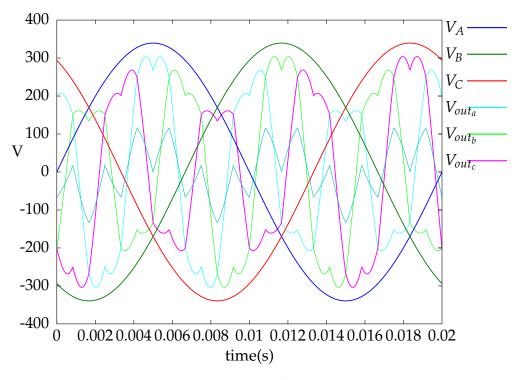

| 5.1 | 5 Input Phase Voltage waveforms with the Output Voltage<br>Waveforms contained with the envelope | 81 |

| 5.1 | 6 Line-Line Input Voltage waveforms, showing the enve-<br>lope of the rectified waveforms        | 84 |

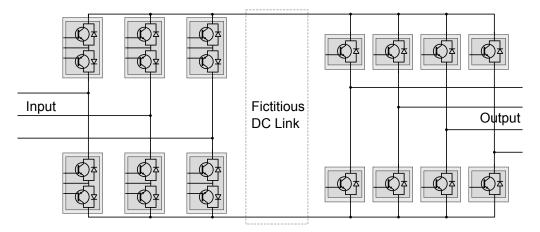

| 5.1 | 7 Circuit Diagram of the 4-Leg Matrix Converter using the 'Fictitious DC Link'                   | 89 |

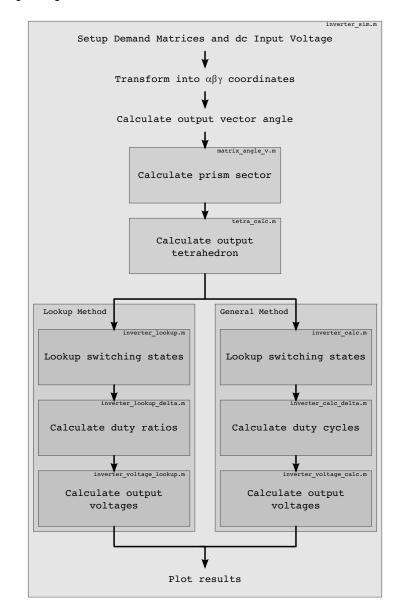

| 6.1  | Block Diagram for the Matlab simulation for the 4-LegInverter92                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------|

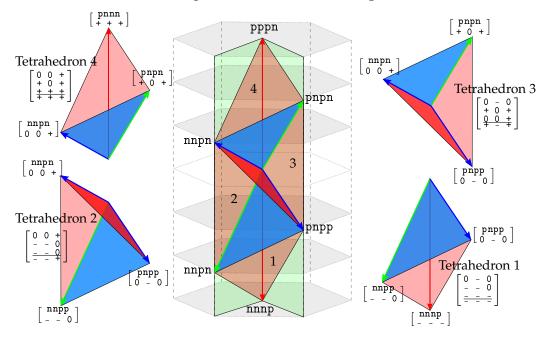

| 6.2  | Exploded view of a single prism, showing the 4 tetrahedrons 95                                                                    |

| 6.3  | Closeup view of a single prism, showing the Demand Vector 96                                                                      |

| 6.4  | Output from the 4-Leg Inverter Simulation, showing the Calculated and Demand Output Voltages                                      |

| 6.5  | Output Voltage Vector angle, Tetrahedron and Prism for<br>the 4-Leg Inverter Simulation                                           |

| 6.6  | Line and Phase Output Voltages from the 4-Leg Inverter<br>Simulation, showing the results from the Lookup and Gen-<br>eral Method |

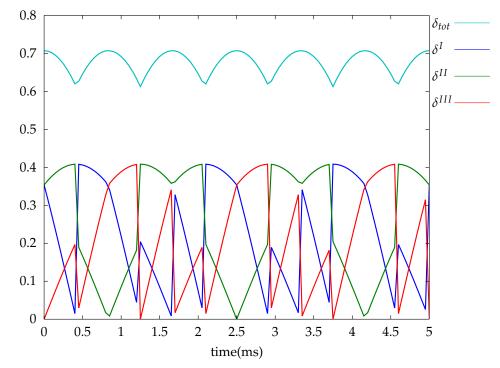

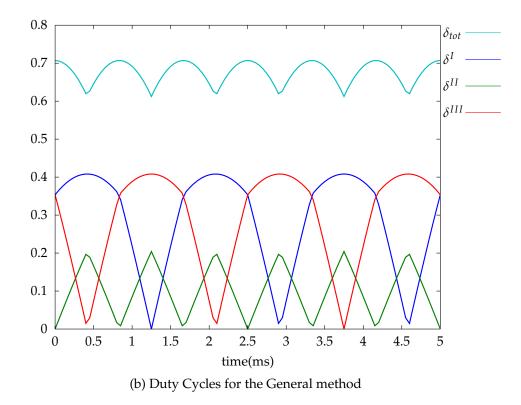

| 6.7  | Duty cycle plots for the Lookup and General methods of 4-Leg Inverter Simulation                                                  |

| 6.8  | Output Phase Voltage for a 4-leg Inverter when following<br>a complex set of demand voltages                                      |

| 6.9  | Block Diagram of the 4-Leg Matrix Converter Matlab Sim-<br>ulation                                                                |

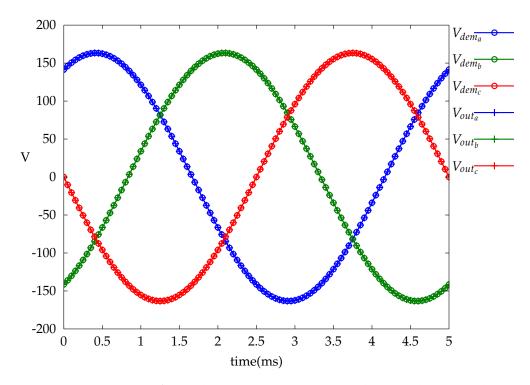

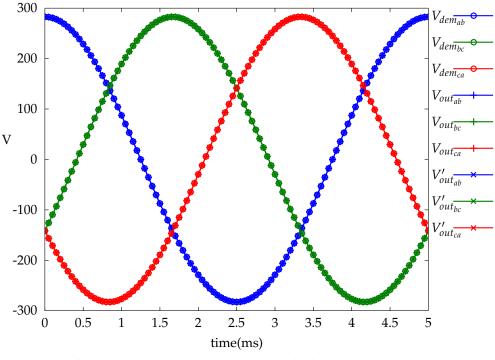

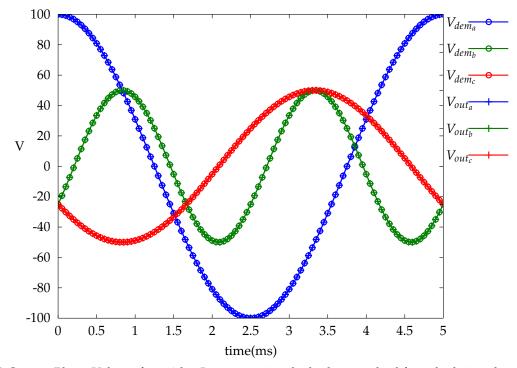

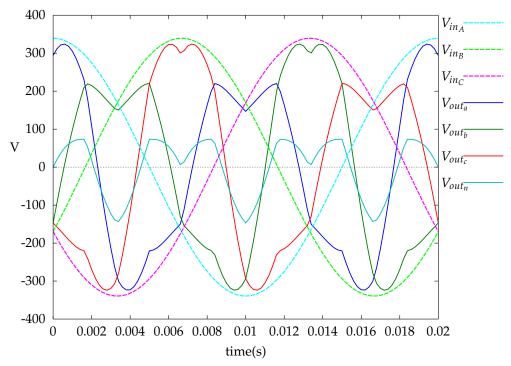

| 6.10 | 4-Leg Matrix Converter output voltages for the original derived duty cycle equations                                              |

| 6.11 | 4-Leg Matrix Converter output voltages for the simplified duty cycle equations                                                    |

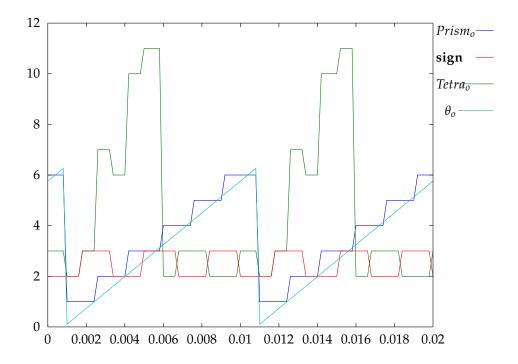

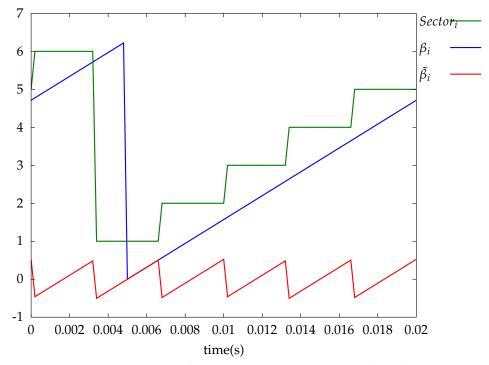

| 6.12 | 4-Leg Matrix Converter Simulation Internal Variables 122                                                                          |

| 6.13 | 4-Leg Matrix Converter Output Voltages when operating with q                                                                      |

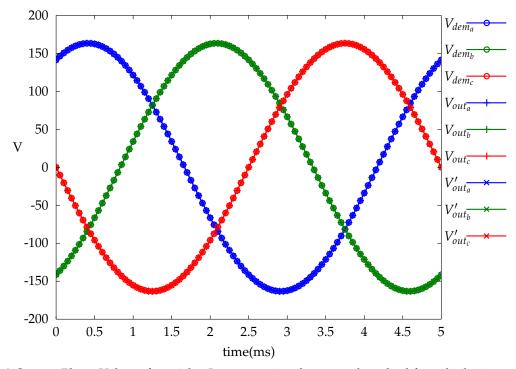

| 6.14 | 4-Leg Matrix Converter Simulation Results when operat-<br>ing with q and voltages synchronised                                    |

| 6.15 | 4-Leg Matrix Converter Simulation Results when operat-<br>ing with q and voltages unsynchronised                                  |

| 6.16 | Bi-directional Switch Circuit                                                                                                     |

| 6.17 | Circuit Diagram used for the Bi-Directional Switch block<br>in the Saber simulations                                              |

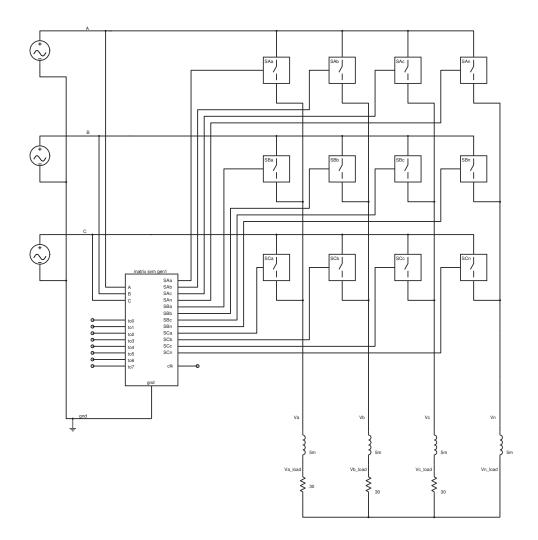

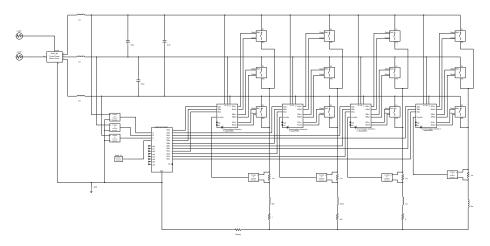

| 6.18 | Circuit Diagram used for the Saber simulations                                                                                    |

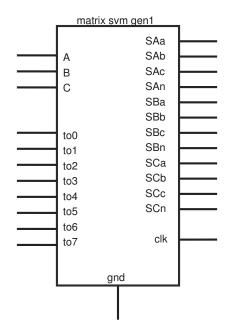

| 6.19 | Control Block for Saber simulation                                                                                                |

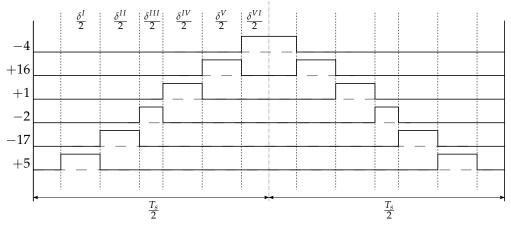

| 6.20 | A Basic Switching Sequence                                                                                                        |

| 6.21 | 4-Leg Matrix Converter Switching Sequences                                                                                        |

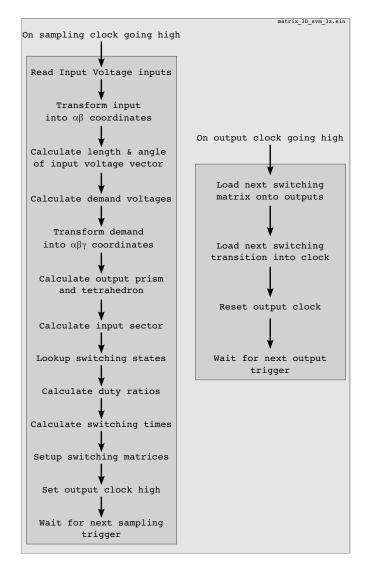

| 6.22 | Block Diagram of the MAST template for the Control Block 137                                                   |

|------|----------------------------------------------------------------------------------------------------------------|

| 6.23 | Circuit Diagram of the 4-Leg Matrix Converter for simulating the effects of the Input Filter                   |

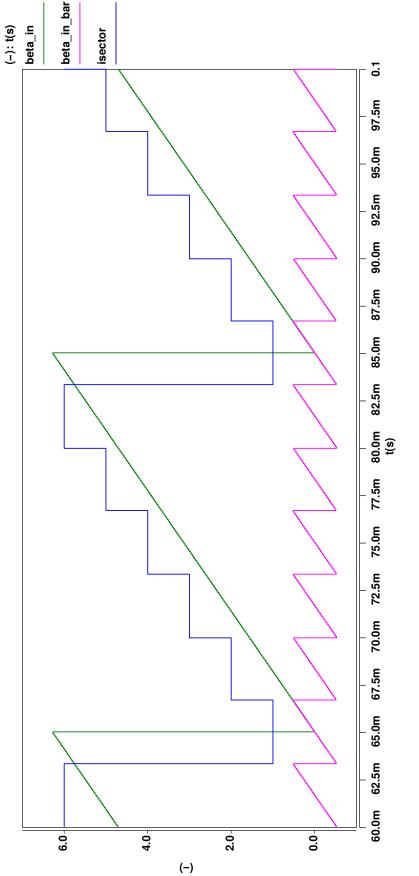

| 6.24 | Plot of Control Block Internal Input Variables                                                                 |

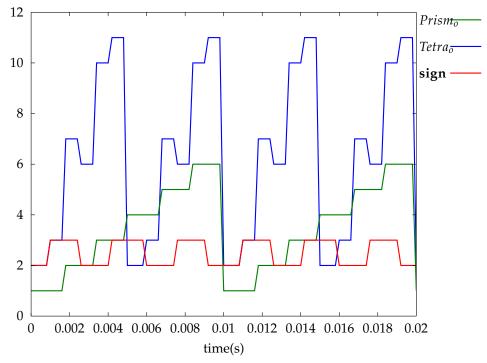

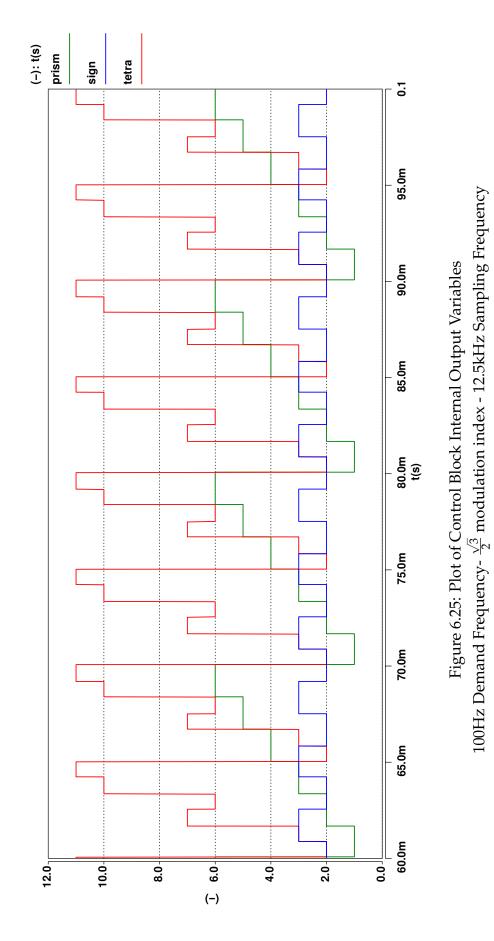

| 6.25 | Plot of Control Block Internal Output Variables 157                                                            |

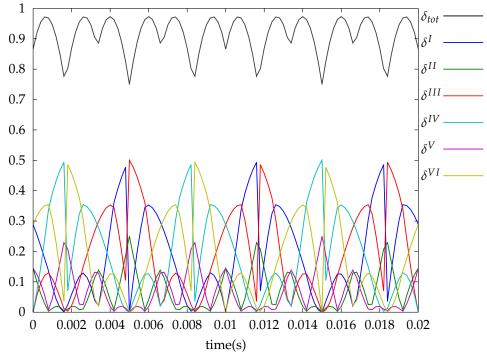

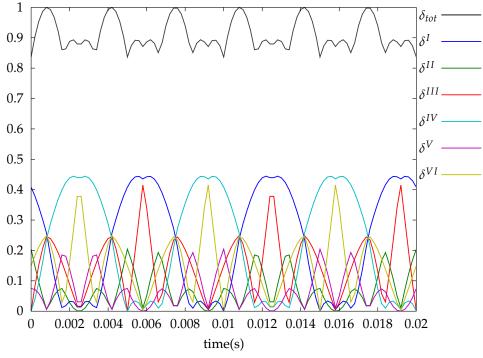

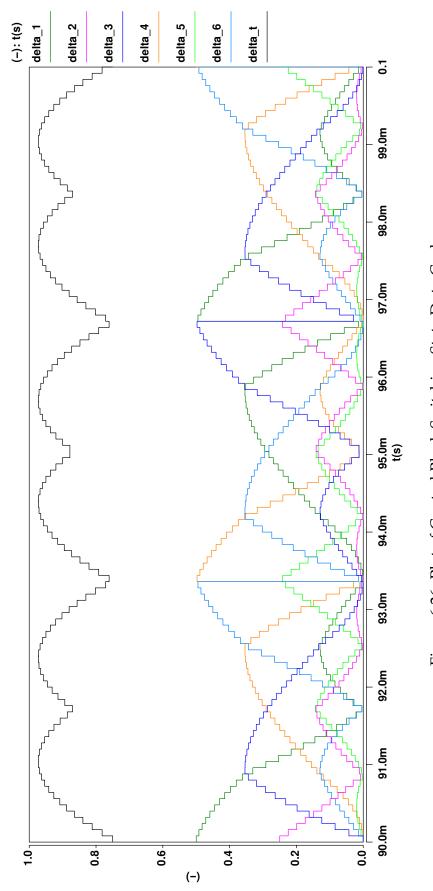

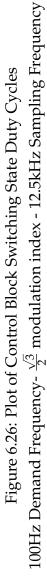

| 6.26 | Plot of Control Block Switching State Duty Cycles 158                                                          |

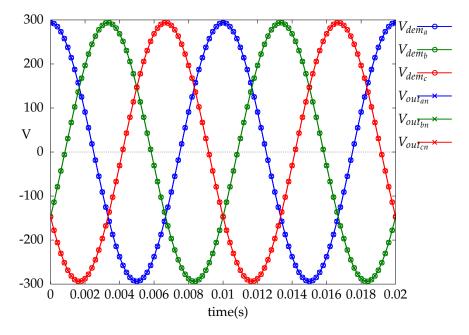

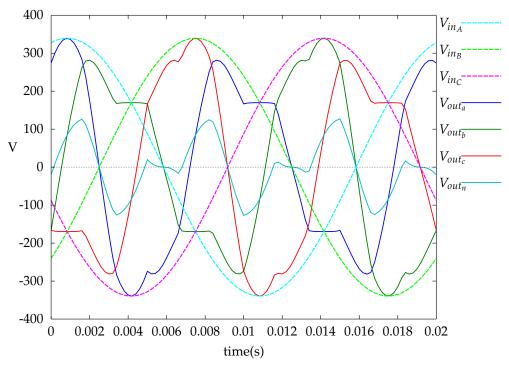

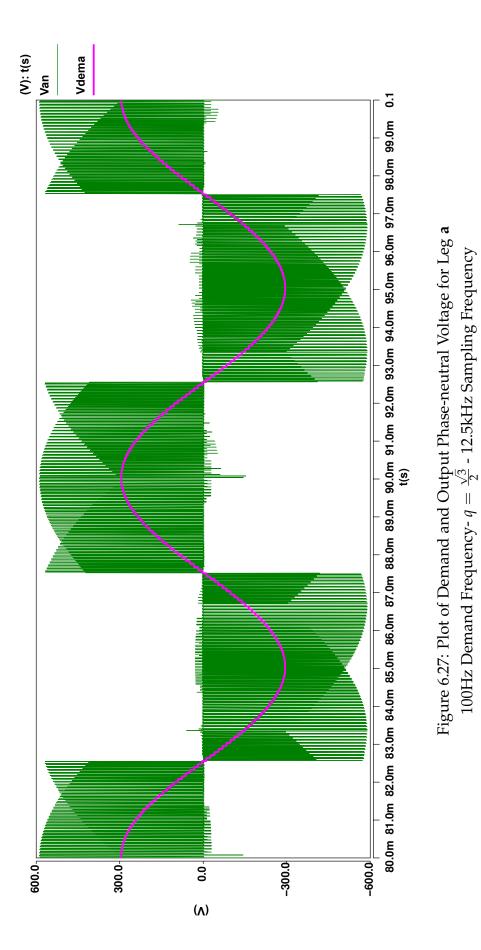

| 6.27 | Plot of Demand and Output Phase-neutral Voltage for Leg a159                                                   |

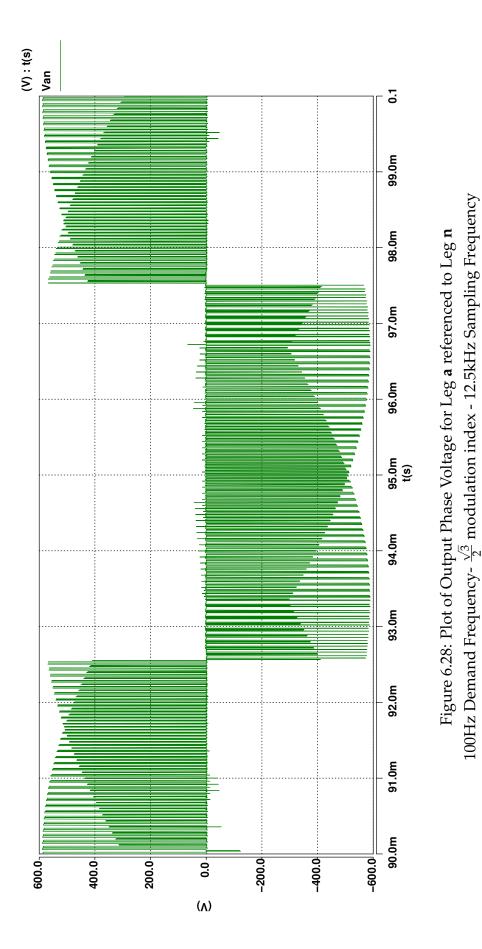

| 6.28 | Plot of Output Phase-neutral Voltage for Leg <b>a</b> 160                                                      |

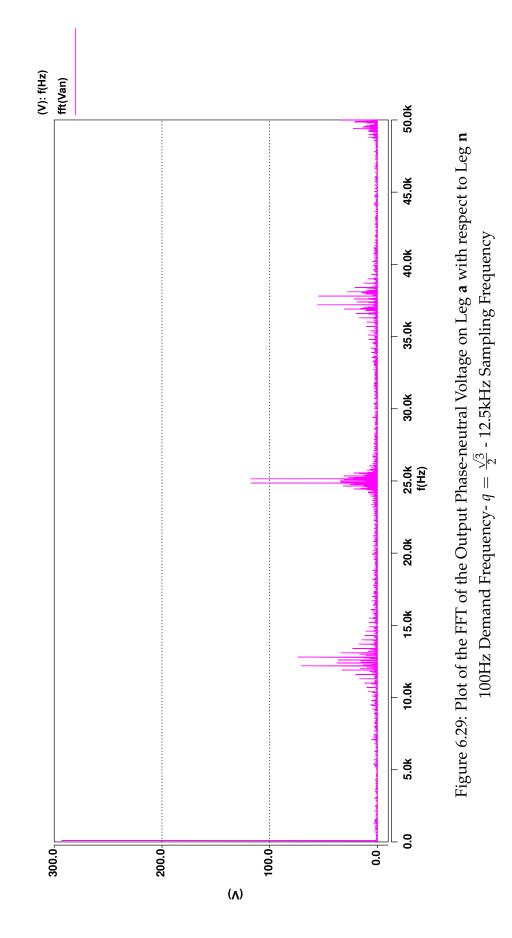

| 6.29 | Plot of the FFT of the Output Phase-neutral Voltage on Leg <b>a</b> 161                                        |

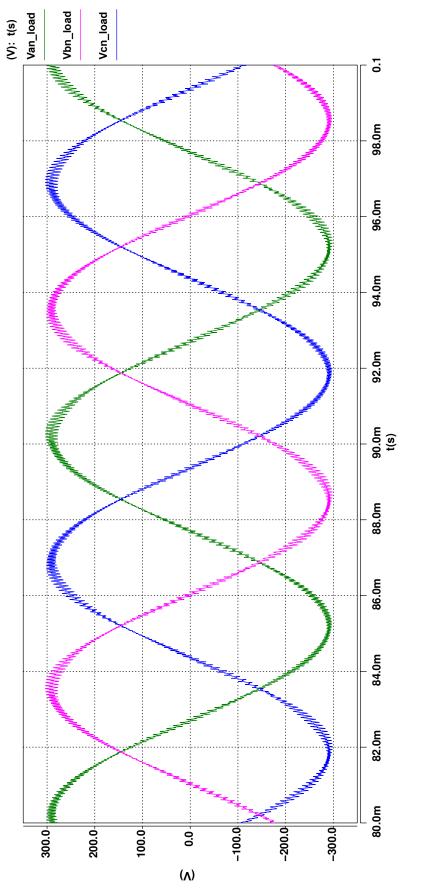

| 6.30 | Plot of the 3 Output Phase-neutral Voltages at the load 162                                                    |

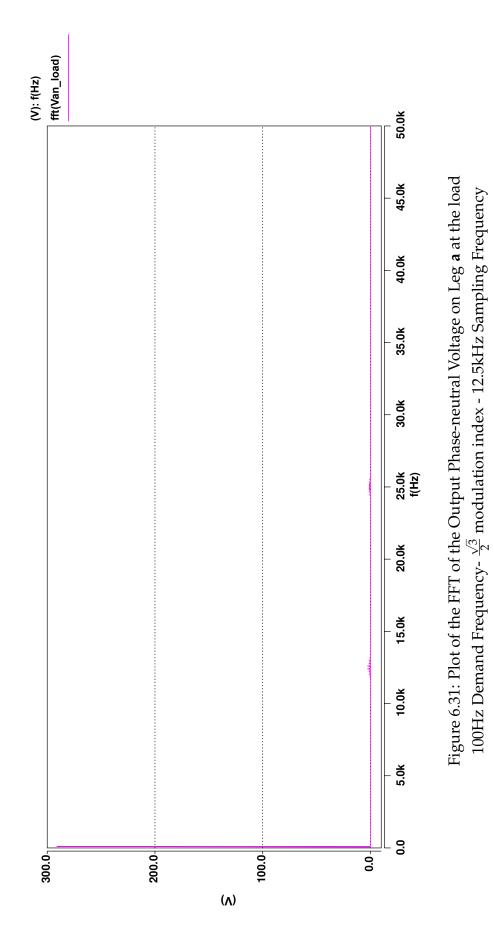

| 6.31 | Plot of the FFT of the Output Phase-neutral Voltage on Leg<br><b>a</b> at the load                             |

| 6.32 | Plot of the Gate Control Signals                                                                               |

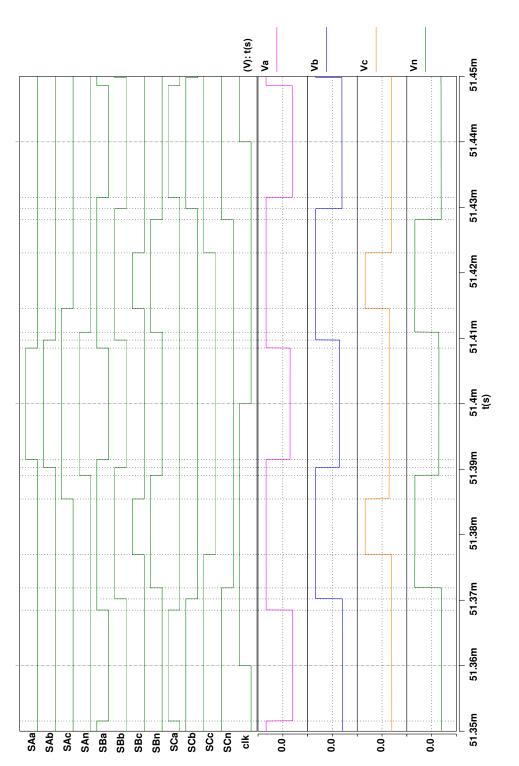

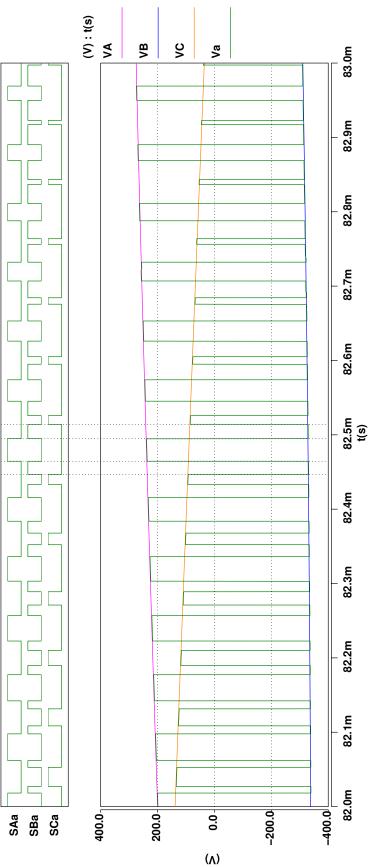

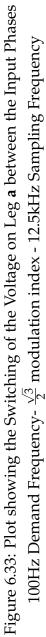

| 6.33 | Plot showing the Switching of the Voltage on Leg <b>a</b> 165                                                  |

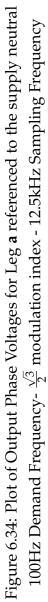

| 6.34 | Plot of Output Phase Voltages for Leg <b>a</b>                                                                 |

| 6.35 | Plot of the Input Current and Voltage for Supply Phase A . 167                                                 |

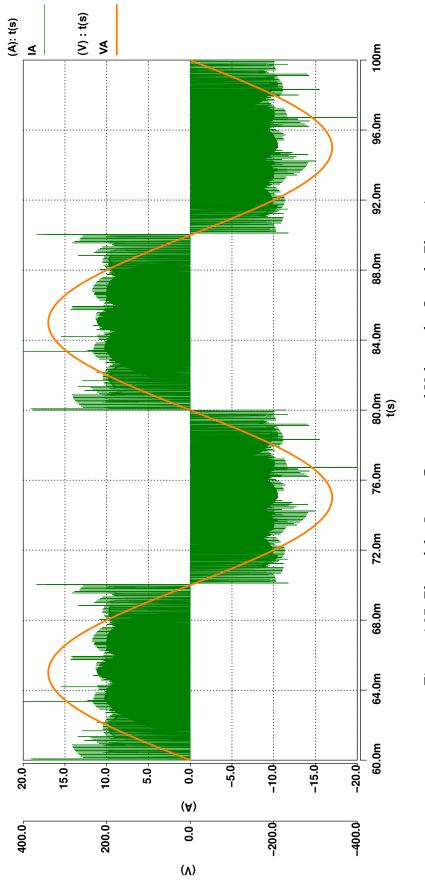

| 6.36 | Plot of the FFT of Input Current for Supply Phase A 168                                                        |

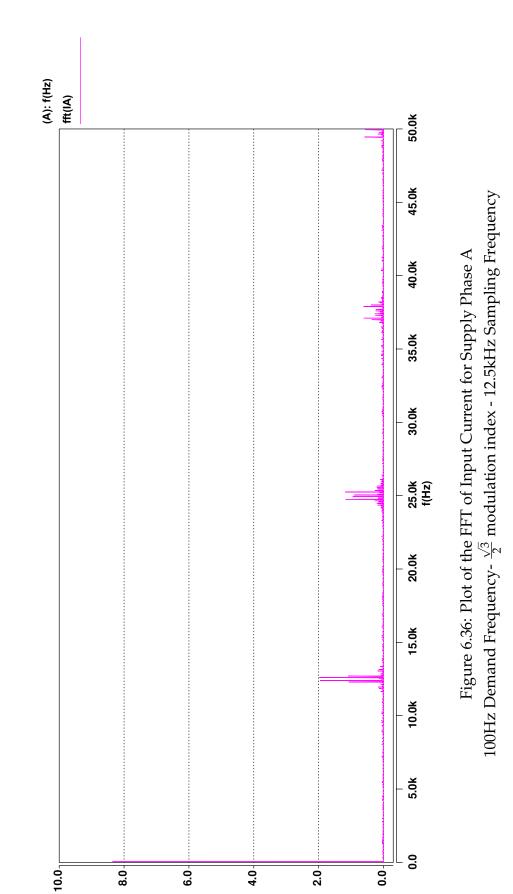

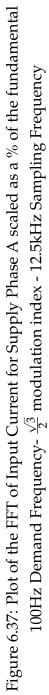

| 6.37 | Plot of the FFT of Input Current for Supply Phase A scaled<br>as a % of the fundamental                        |

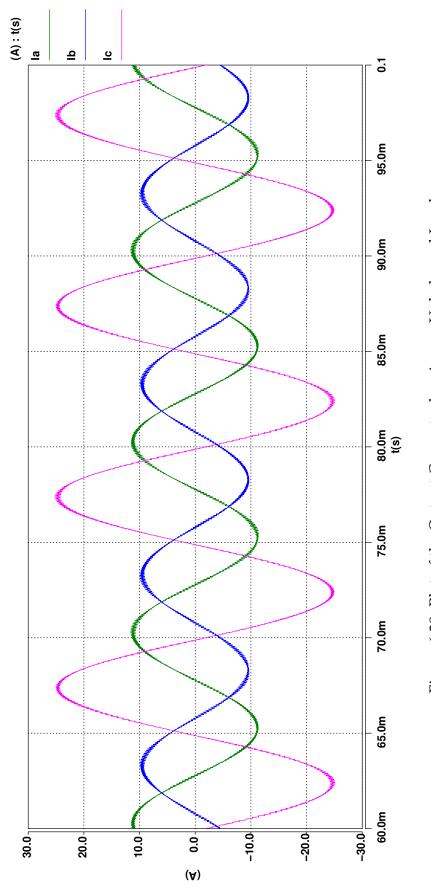

| 6.38 | Plot of the Output Currents showing an Unbalanced Load 170                                                     |

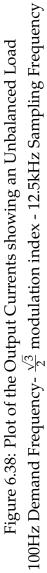

| 6.39 | Plot of the FFT of Output Phase-neutral Voltages with an Unbalanced Load                                       |

| 6.40 | Plot of the Input Current and Voltage for Supply Phase A with an Unbalanced Load                               |

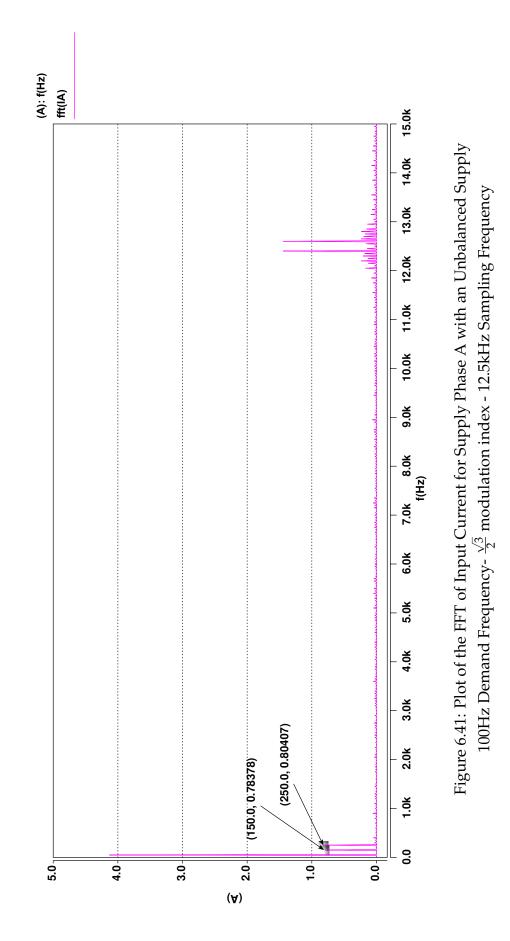

| 6.41 | Plot of the FFT of Input Current for Supply Phase A with<br>an Unbalanced Supply                               |

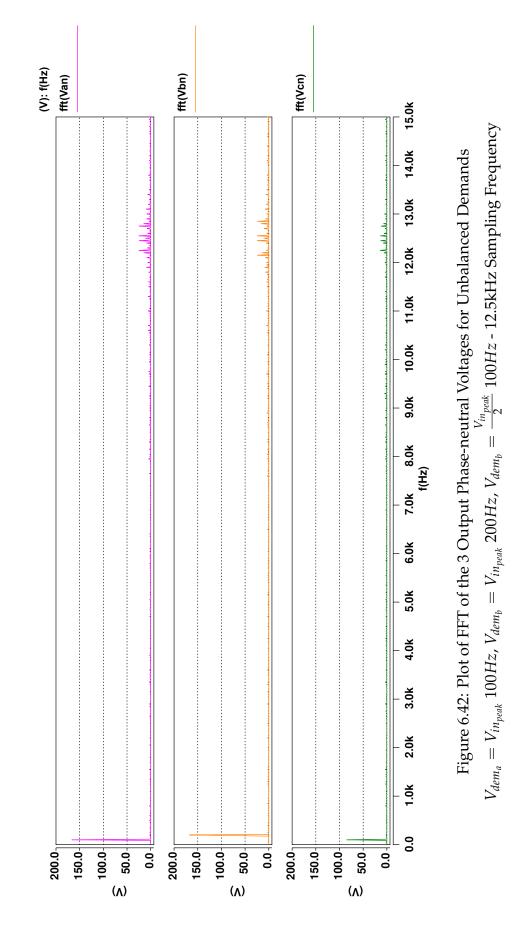

| 6.42 | Plot of FFT of the 3 Output Phase-neutral Voltages for<br>Unbalanced Demands                                   |

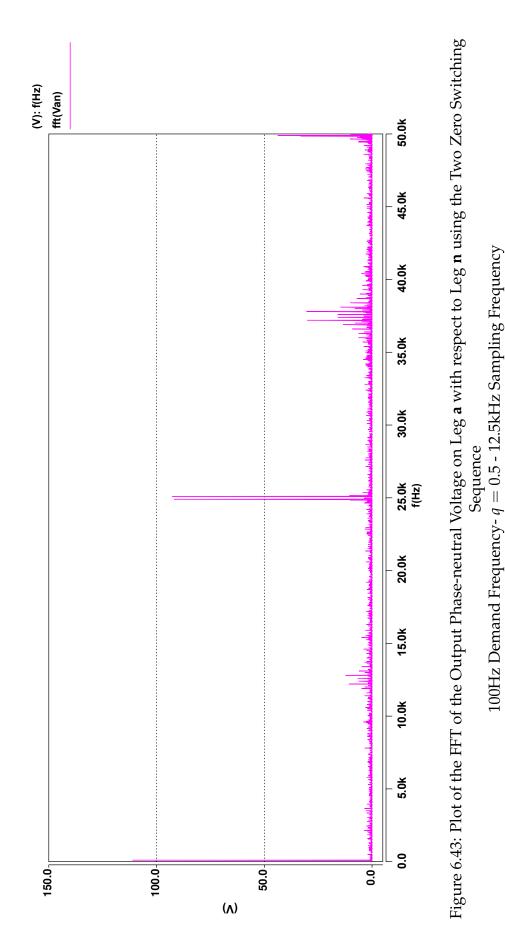

| 6.43 | Plot of the FFT of the Output Phase-neutral Voltage on Leg<br><b>a</b> using Two Zero                          |

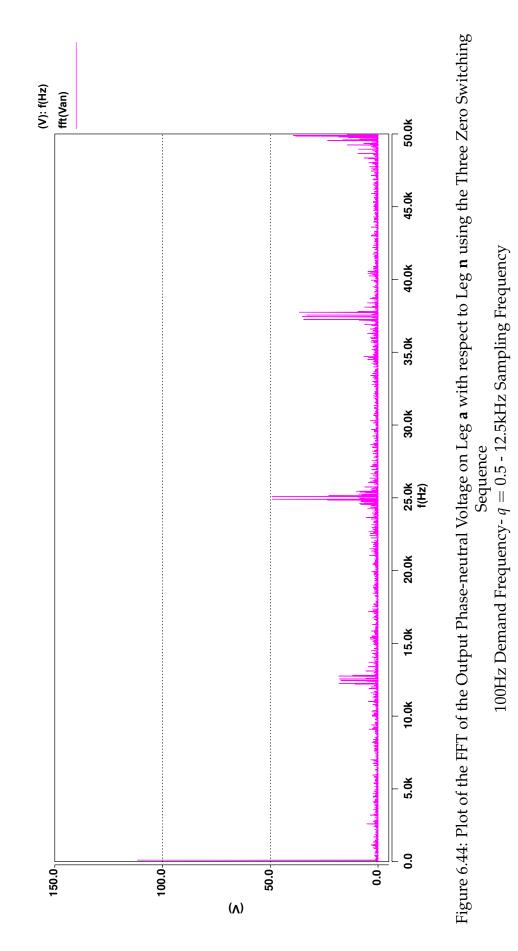

| 6.44 | Plot of the FFT of the Output Phase-neutral Voltage on Leg<br><b>a</b> using Three Zero                        |

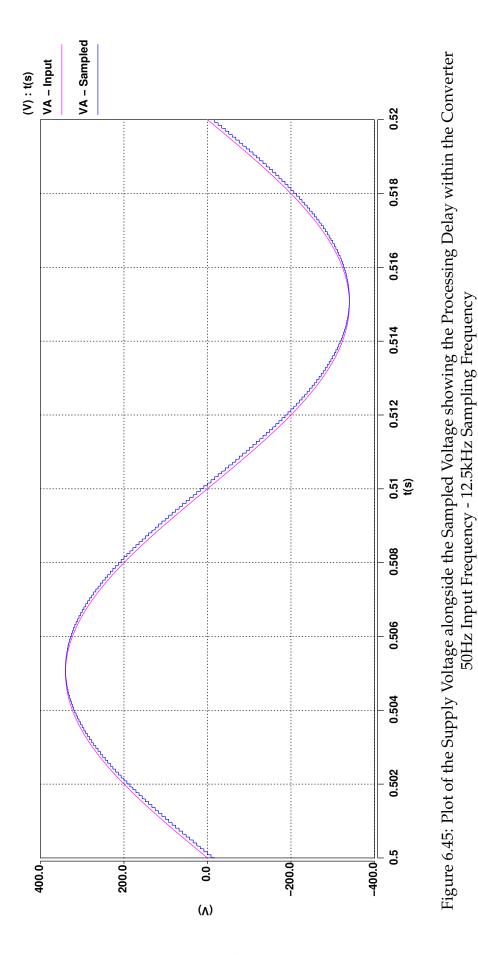

| 6.45 | Plot of the Supply Voltage alongside the Sampled Voltage showing the Processing Delay within the Converter 177 |

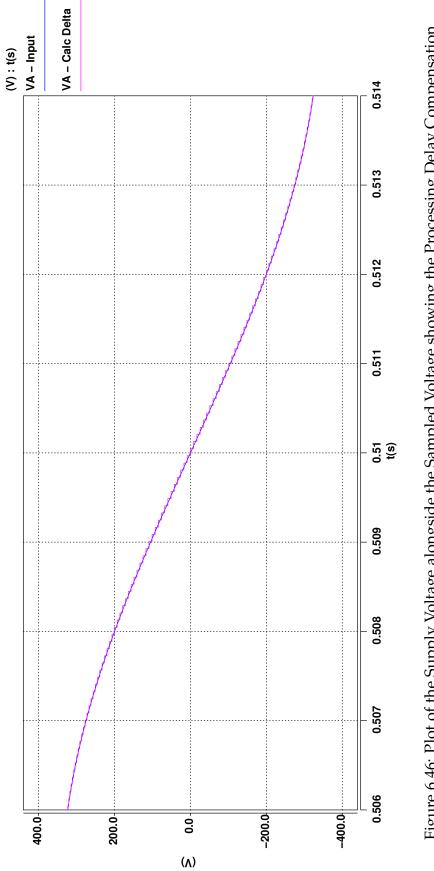

| 6  | .46 | Plot of the Supply Voltage alongside the Sampled Voltage showing the Processing Delay Compensation                                                                      |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

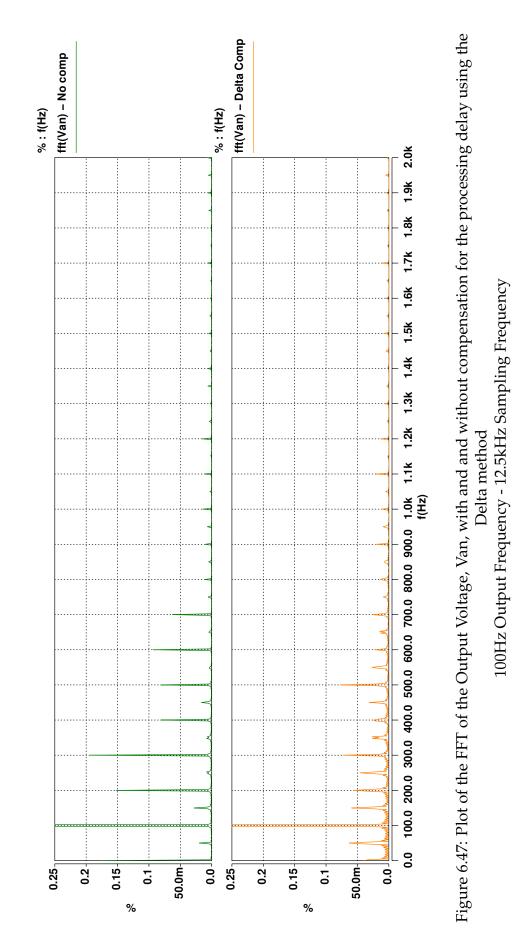

| 6  | .47 | Plot of the FFT of the Output Voltage, Van, with and and without compensation for the processing delay using the Delta method                                           |

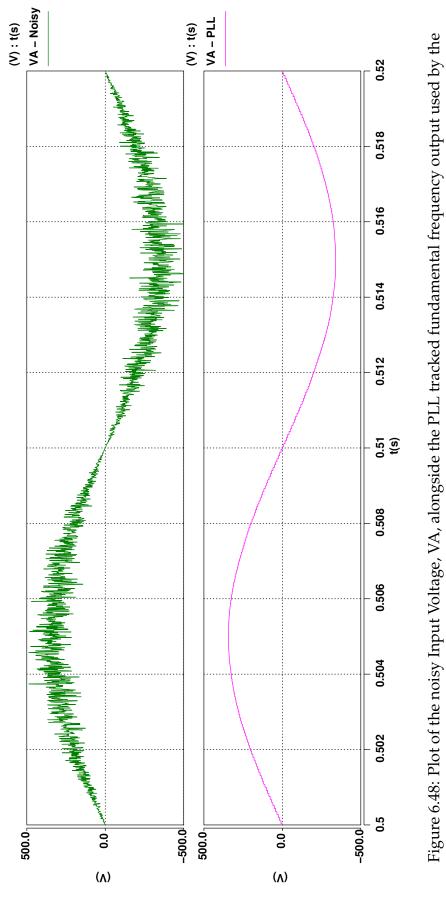

| 6  | .48 | Plot of the noisy Input Voltage, VA, alongside the PLL tracked fundamental frequency output used by the converter                                                       |

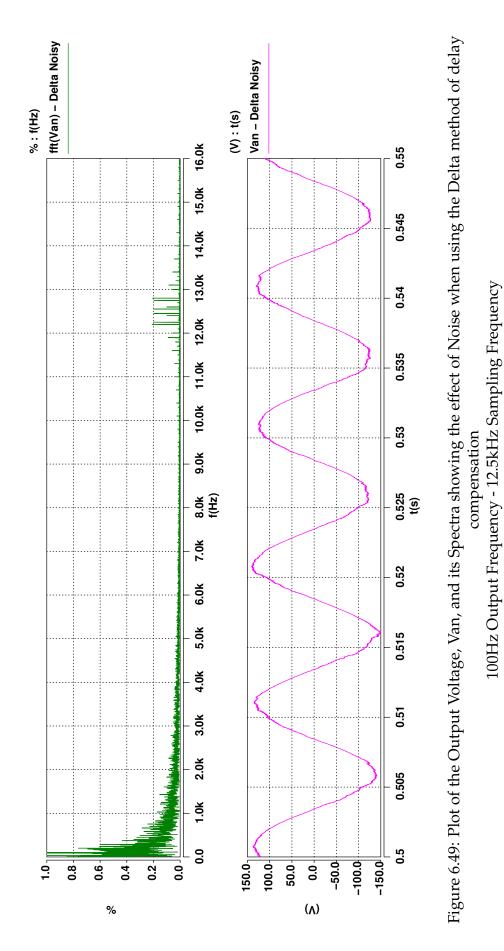

| 6  | .49 | Plot of the Output Voltage, Van, and its Spectra showing the effect of Noise when using the Delta method 181                                                            |

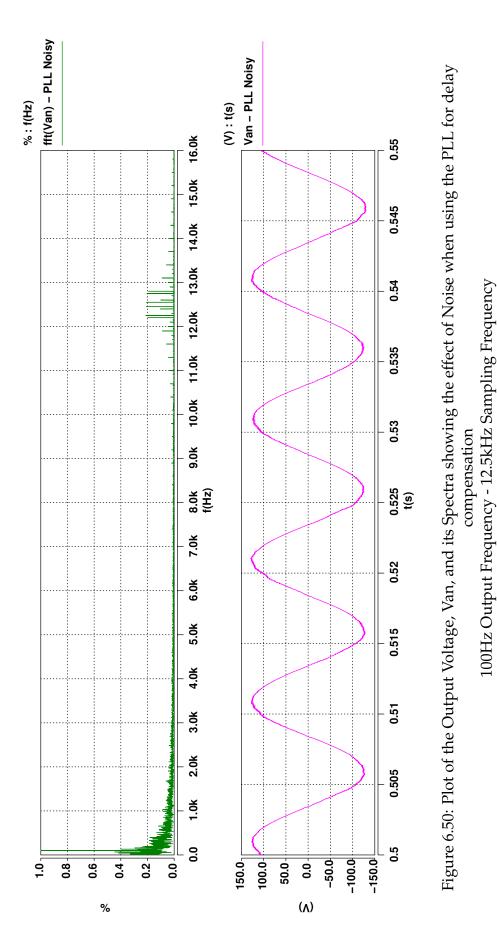

| 6  | .50 | Plot of the Output Voltage, Van, and its Spectra showing<br>the effect of Noise when using the PLL                                                                      |

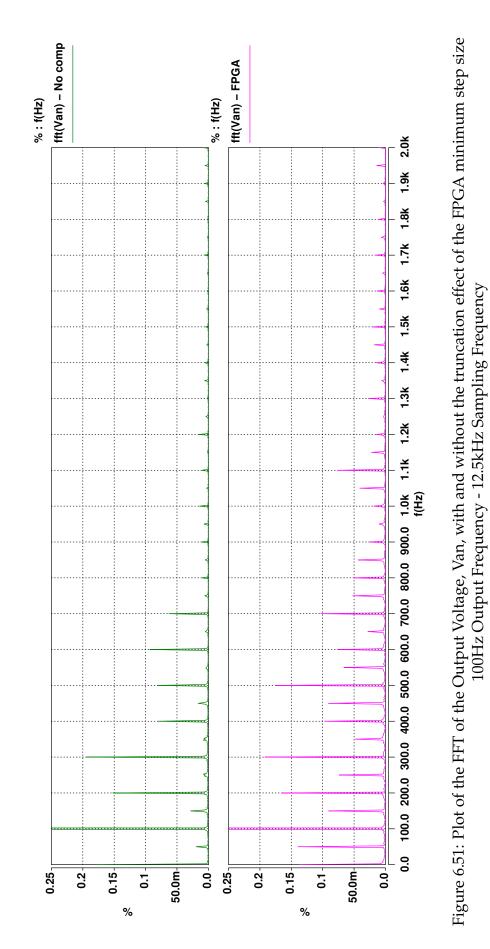

| 6  | .51 | Plot of the FFT of the Output Voltage, Van, with and with-<br>out the truncation effect of the FPGA minimum step size . 183                                             |

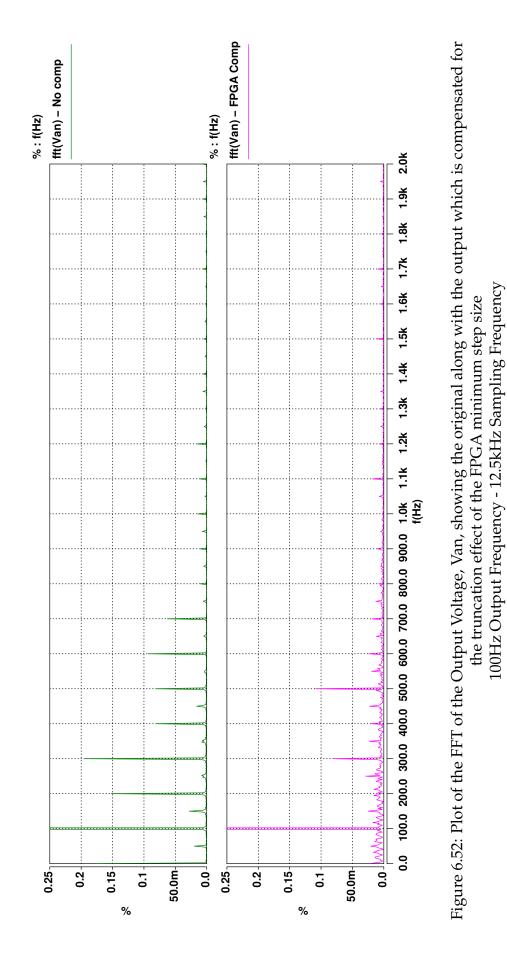

| 6  | .52 | Plot of the FFT of the Output Voltage, Van, showing the original along with the output which is compensated for the truncation effect of the FPGA minimum step size 184 |

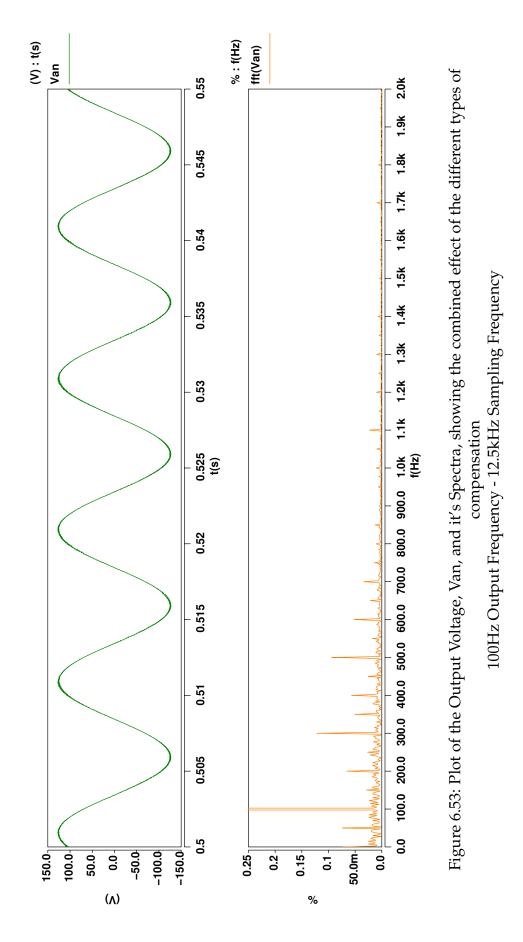

| 6  | .53 | Plot of the Output Voltage, Van, and it's Spectra, showing<br>the combined effect of the different types of compensation 185                                            |

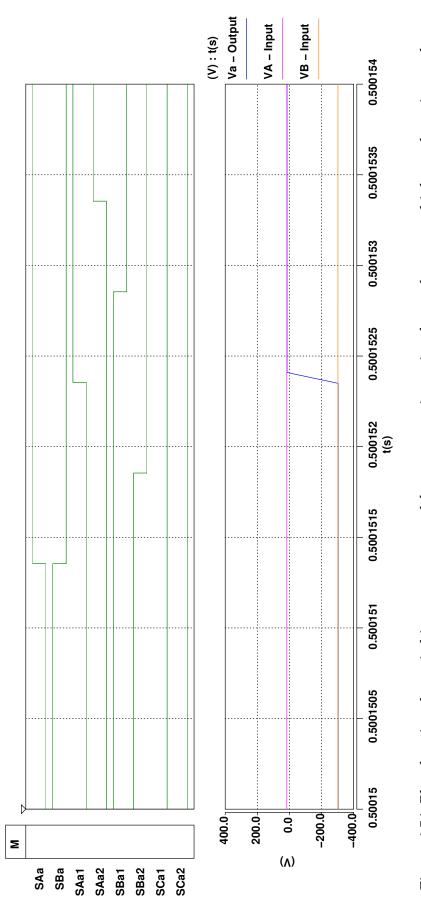

| 6  | .54 | Plot showing the switching sequence used for commuta-<br>tion going from a lower to a higher voltage input phase 186                                                    |

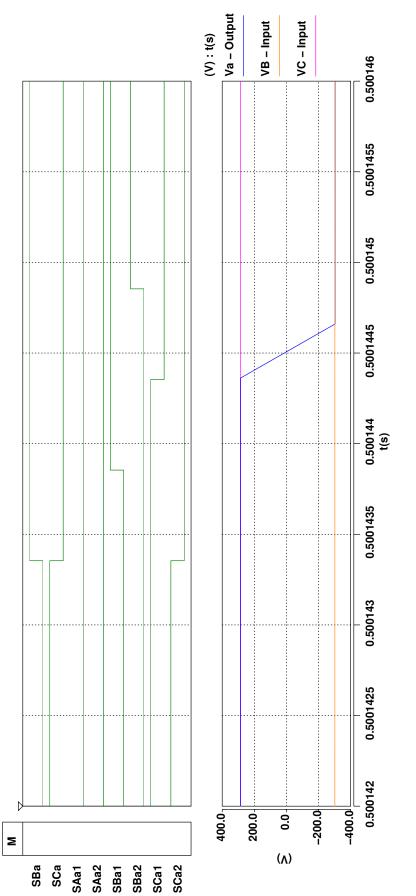

| 6  | .55 | Plot showing the switching sequence used for commuta-<br>tion going from a higher to a lower voltage input phase 187                                                    |

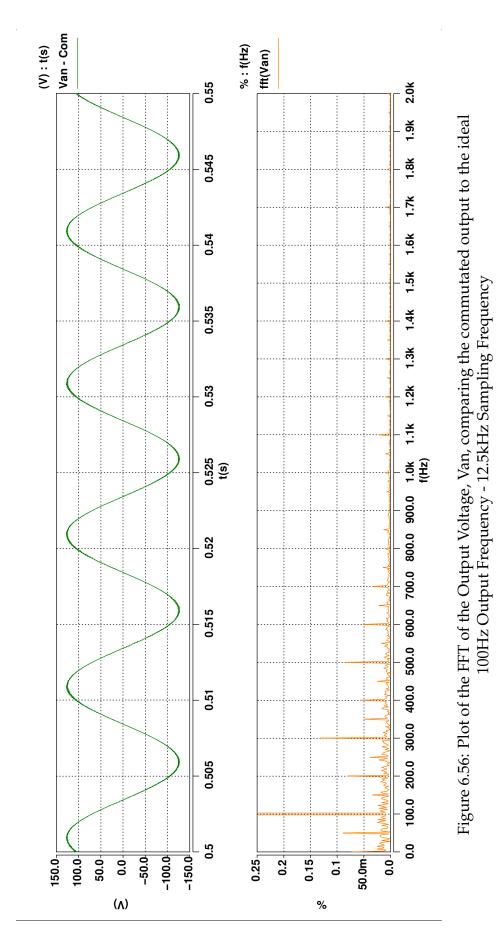

| 6  | .56 | Plot of the FFT of the Output Voltage, Van, comparing the commutated output to the ideal                                                                                |

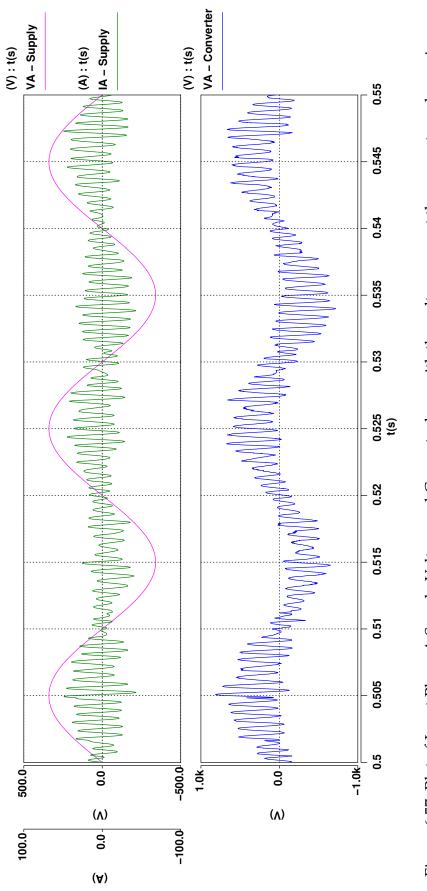

| 6. | .57 | Plot of Input Phase A Supply Voltage and Current, along with the voltage seen at the converter, when using a $1mH/3\mu 3F$ Input Filter with no PLL                     |

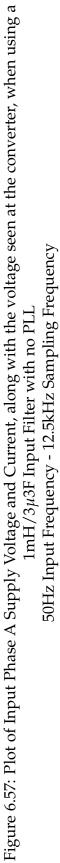

| 6  | .58 | Plot of Input Phase A Supply Voltage and Current, along with the voltage seen at the converter, when using a $1\text{mH}/47\mu\text{F}$<br>Input Filter with no PLL     |

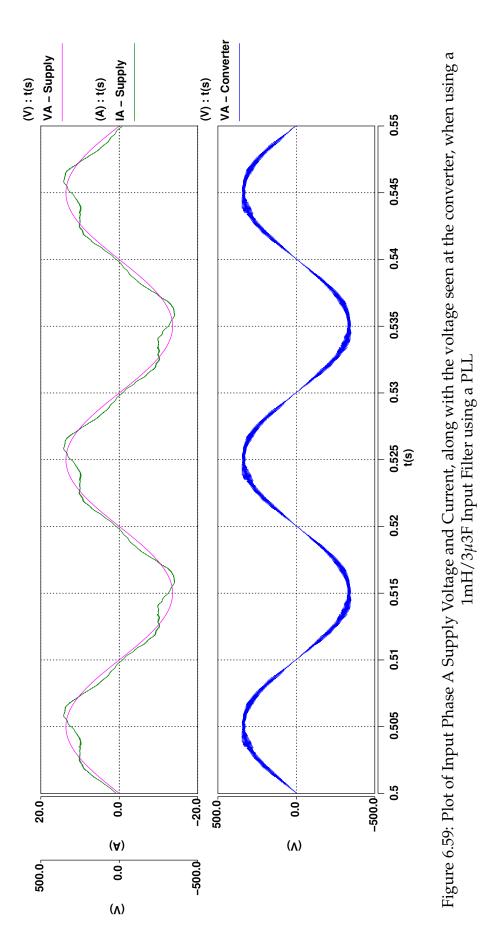

| 6  | .59 | Plot of Input Phase A Supply Voltage and Current, along with the voltage seen at the converter, when using a $1mH/3\mu 3F$ Input Filter using a PLL                     |

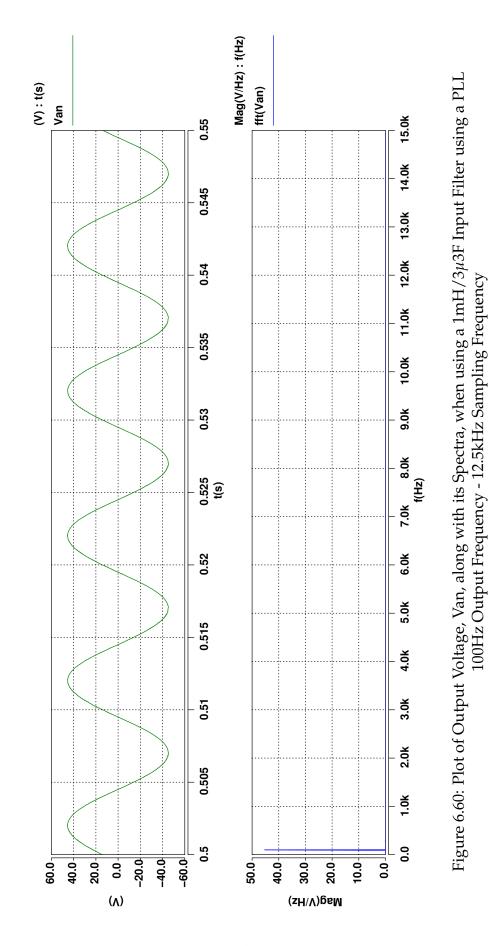

| 6  | .60 | Plot of Output Voltage, Van, along with its Spectra, when using a $1\text{mH}/3\mu$ 3F Input Filter using a PLL                                                         |

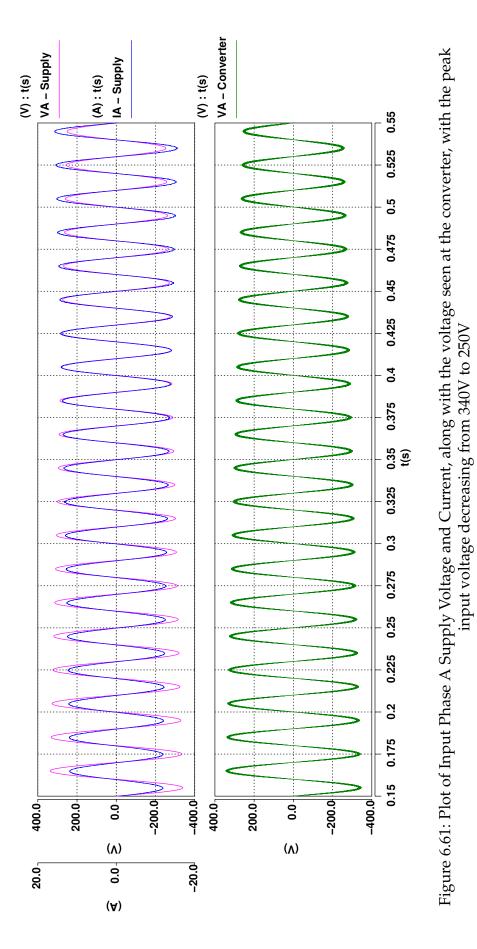

| 6.61 | Plot of Input Phase A Supply Voltage and Current, along<br>with the voltage seen at the converter, with a changing<br>input voltage                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

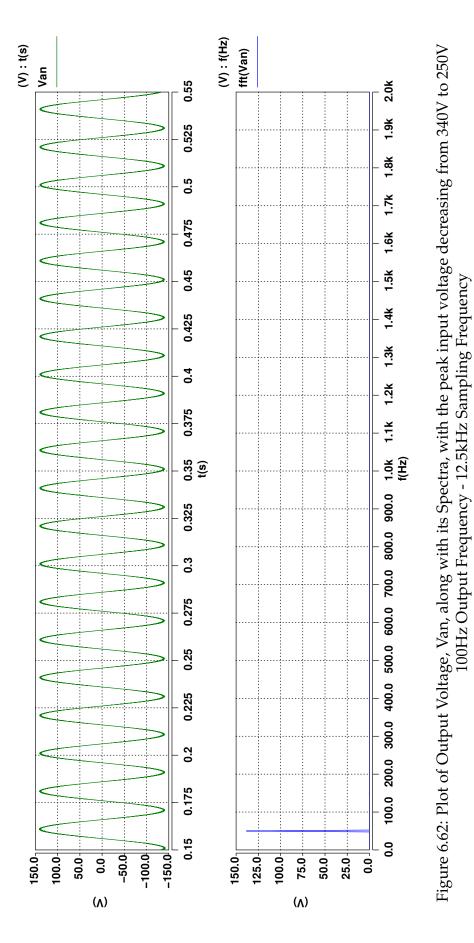

| 6.62 | Plot of Output Voltage, Van, along with its Spectra, with a changing input voltage                                                                                                  |

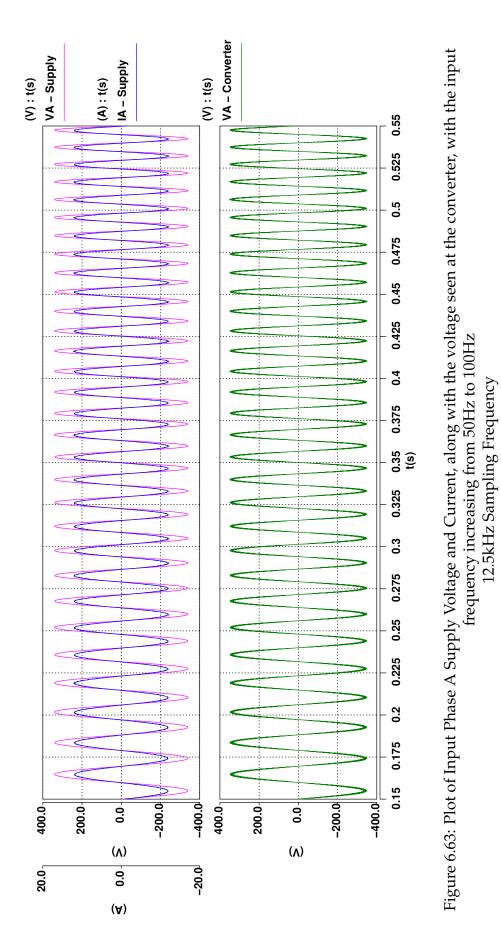

| 6.63 | Plot of Input Phase A Supply Voltage and Current, along<br>with the voltage seen at the converter, with a changing<br>input frequency                                               |

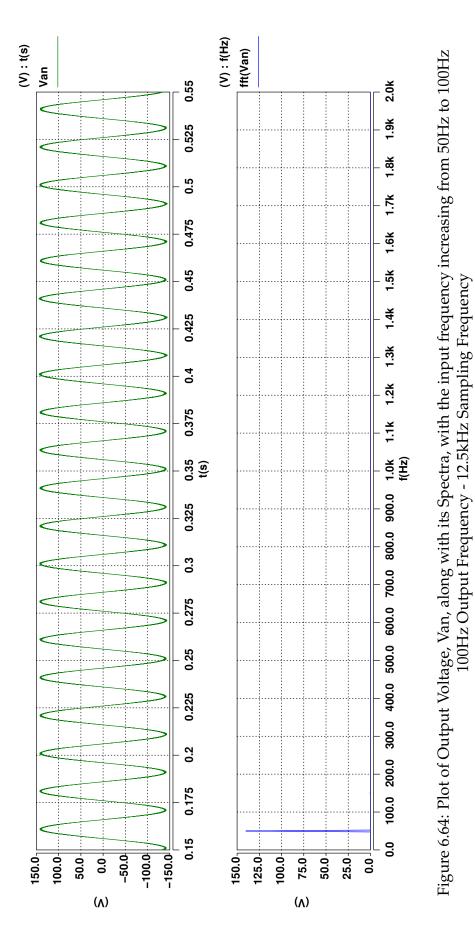

| 6.64 | Plot of Output Voltage, Van, along with its Spectra, with a changing input frequency                                                                                                |

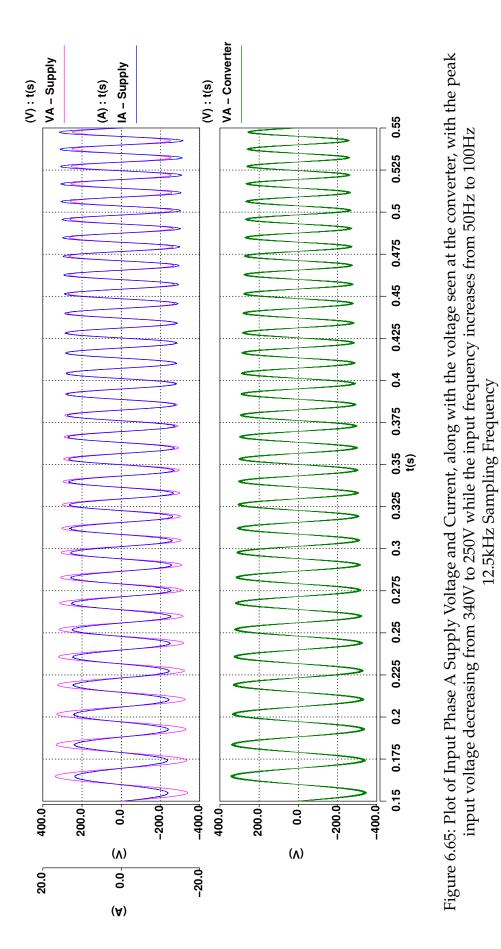

| 6.65 | Plot of Input Phase A Supply Voltage and Current, along<br>with the voltage seen at the converter, with a changing<br>input voltage and frequency                                   |

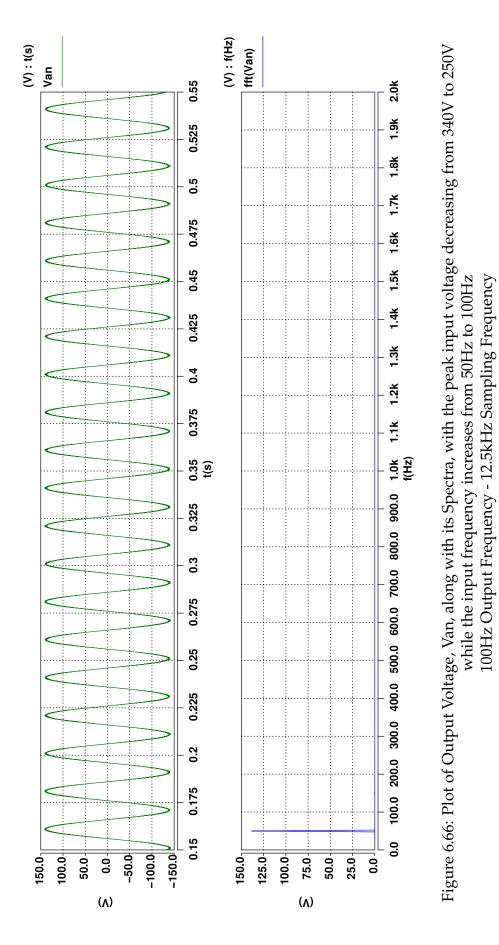

| 6.66 | Plot of Output Voltage, Van, along with its Spectra, with a changing input voltage and frequency                                                                                    |

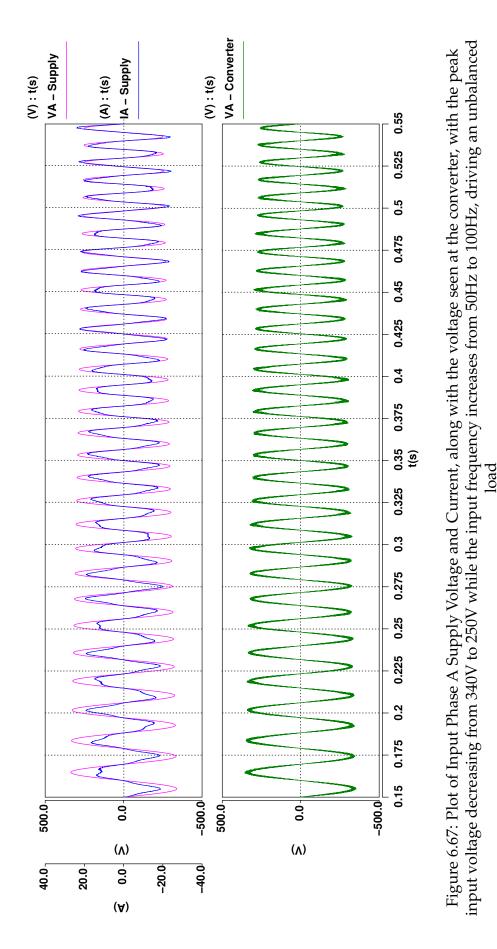

| 6.67 | Plot of Input Phase A Supply Voltage and Current, along<br>with the voltage seen at the converter, with a changing<br>input voltage and frequency, driving an unbalanced load . 199 |

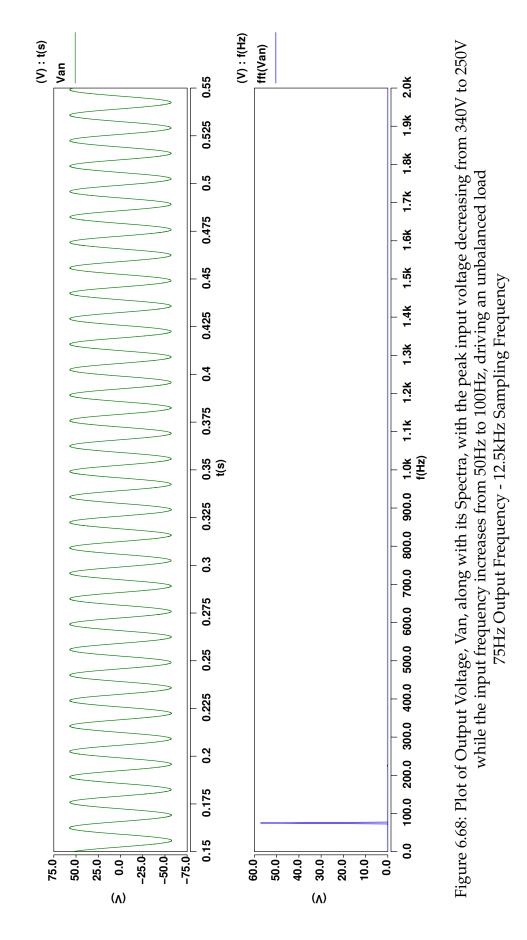

| 6.68 | Plot of Output Voltage, Van, along with its Spectra, with a changing input voltage and frequency, driving an unbal-<br>anced load                                                   |

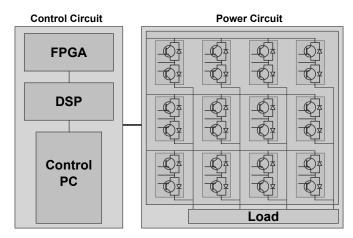

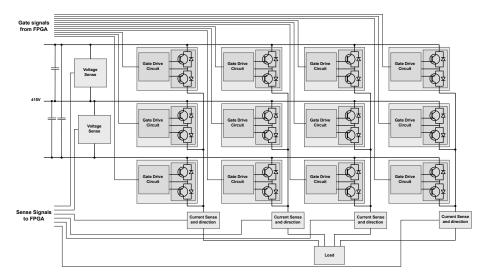

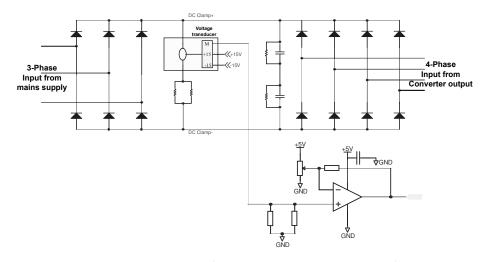

| 7.1  | Broad Overview of the different areas in a Matrix Converter202                                                                                                                      |

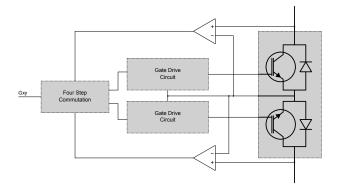

| 7.2  | Block Diagram of the Matrix Converter Power Circuit 203                                                                                                                             |

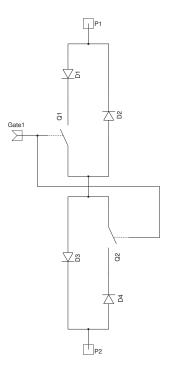

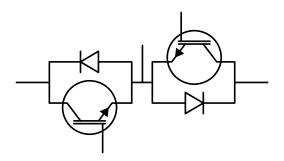

| 7.3  | A Single Bi-directional Switch                                                                                                                                                      |

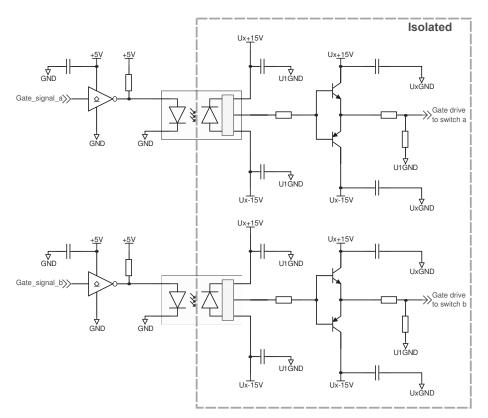

| 7.4  | Circuit Diagram of the Gate Drive Circuit for a single Bi-<br>directional Switch                                                                                                    |

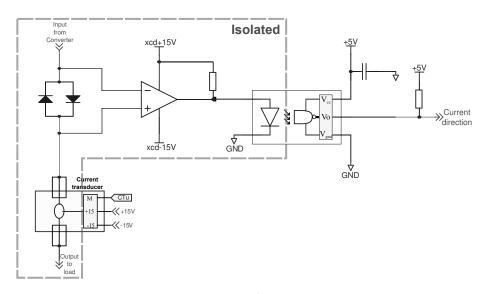

| 7.5  | Circuit Diagram of the Current Sense Circuit                                                                                                                                        |

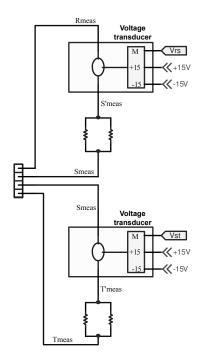

| 7.6  | Circuit Diagram of the Voltage Sensing Circuit 209                                                                                                                                  |

| 7.7  | Circuit Diagram of the Voltage Clamp used for Converter<br>Protection                                                                                                               |

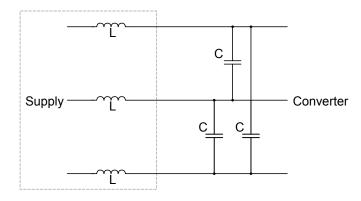

| 7.8  | Circuit Diagram of the Supply and Input Filter for the 4-<br>Leg Matrix Converter                                                                                                   |

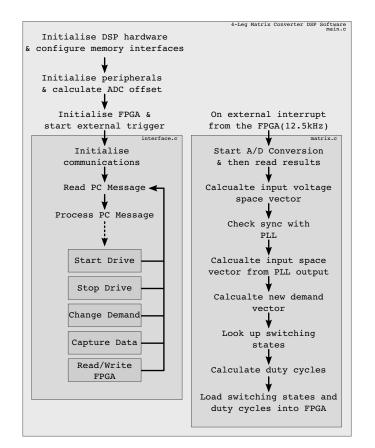

| 7.9  | Block Diagram for the DSP Software for the 4-Leg Matrix<br>Converter                                                                                                                |

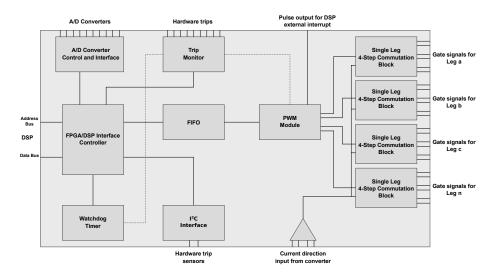

| 7.10 | Block Diagram showing the main components of the FPGA 218                                                                                                                           |

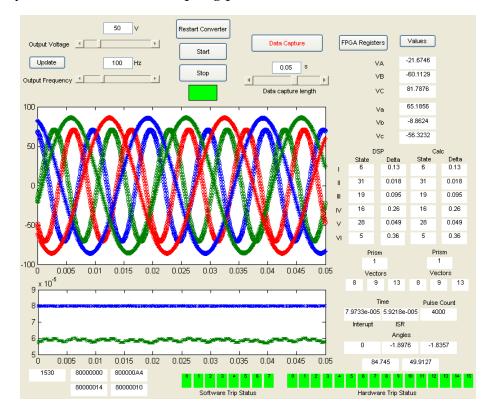

| 7.11 | The Main Control Interface for the 4-Leg Matrix Converter                                                      | 222 |

|------|----------------------------------------------------------------------------------------------------------------|-----|

| 7.12 | The FGPA Registers Display Window                                                                              | 223 |

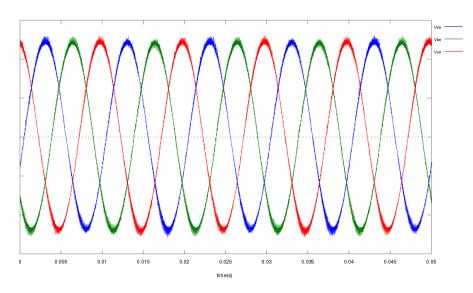

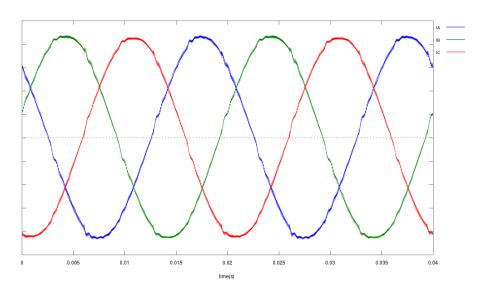

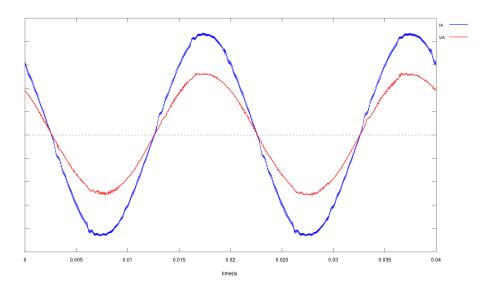

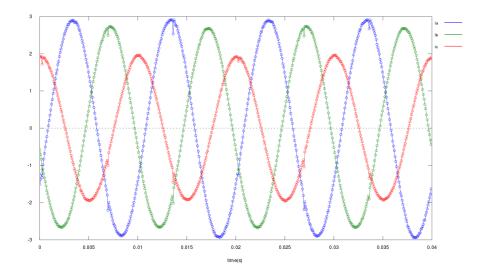

| 8.1  | Plot of the 4-Leg Matrix Converter Output Phase-neutral Voltages at the Load                                   | 225 |

| 8.2  | Plot of the 4-Leg Matrix Converter Output Phase-neutral Voltages at the Load                                   | 226 |

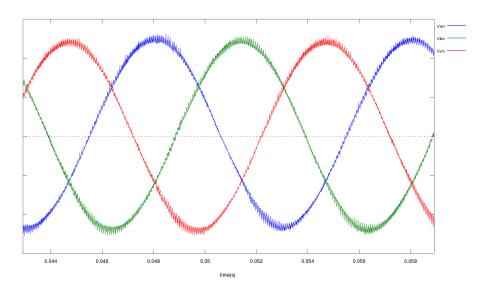

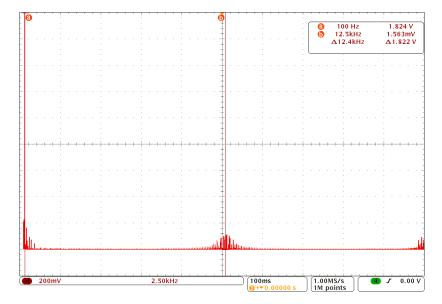

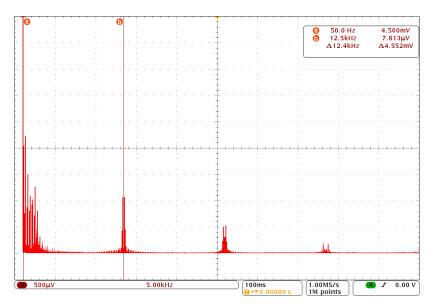

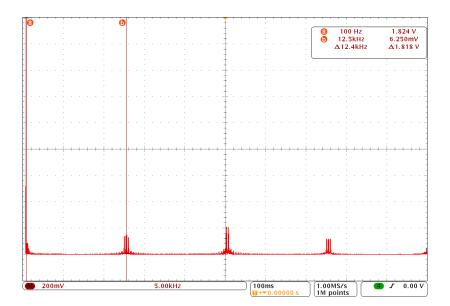

| 8.3  | Plot of the FFT of the Output Phase-neutral Voltage on Leg <b>a</b> at the Load                                | 226 |

| 8.4  | Closeup of the FFT of the Output Phase-neutral Voltage on Leg <b>a</b> at the Load                             | 227 |

| 8.5  | Plot of the FFT of the Output Phase-neutral Voltage on Leg <b>a</b> at the Converter                           | 228 |

| 8.6  | Plot of the 4-Leg Matrix Converter Input Currents                                                              | 228 |

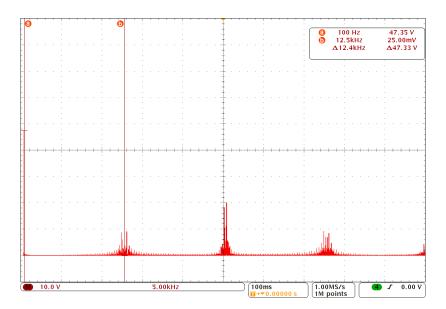

| 8.7  | Plot of the FFT of the Input Current of Phase A                                                                | 229 |

| 8.8  | Closeup of the FFT of the Input Current of Phase $\mathbf{A}$                                                  | 229 |

| 8.9  | Plot of the 4-Leg Matrix Converter Input Current and Voltage for Phase <b>A</b>                                | 230 |

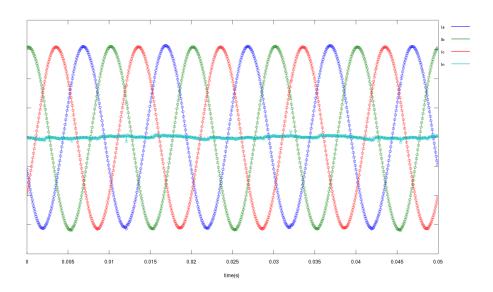

| 8.10 | Plot of the 4-Leg Matrix Converter Output Leg Currents for Balanced Operation                                  | 231 |

| 8.11 | Plot of the 4-Leg Matrix Converter Duty Cycles during Balanced Operation                                       | 231 |

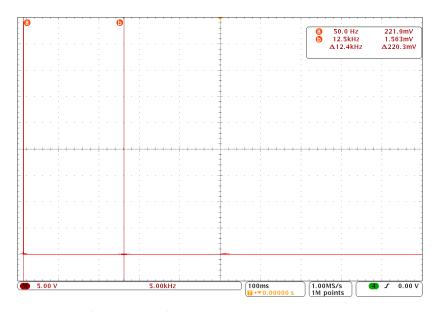

| 8.12 | Plot showing $T_i$ , the time taken to process the DSP inter-<br>rupt routine, alongside the SVM Period, $T_s$ | 232 |

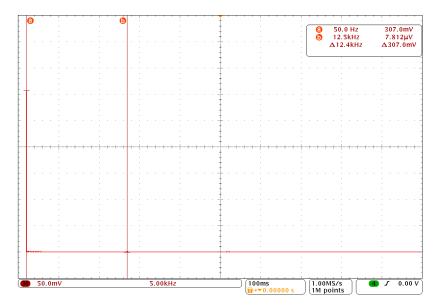

| 8.13 | Plot of the Input Current of Phase <b>A</b> with an Unbalanced Load                                            | 233 |

| 8.14 | Plot of the FFT of the Input Current of Phase <b>A</b> with an Unbalanced Load                                 | 234 |

| 8.15 | Close-up of the FFT of the Input Current of Phase <b>A</b> with an Unbalanced Load                             | 234 |

| 8.16 | Plot of the FFT of the Output Phase-neutral Voltage for Leg <b>c</b> at the Converter for an Unbalanced Load   | 235 |

| 8.17 | Plot of the FFT of the Output Phase-neutral Voltage for Leg <b>c</b> across the Load for an Unbalanced Load    | 235 |

| 8.18 | Close-up of the FFT of the Output Phase-neutral Voltage                    |

|------|----------------------------------------------------------------------------|

|      | for Leg $c$ across the Load for an Unbalanced Load $\ . \ . \ . \ . \ 236$ |

| 8.19 | Plot of the 4-Leg Matrix Converter Output Leg Currents                     |

|      | for an Unbalanced Load 236                                                 |

# List of Tables

| 2.1 | 3-Leg Inverter Switching Combinations                                                                    |

|-----|----------------------------------------------------------------------------------------------------------|

| 2.2 | 3-Leg Inverter Switching Combinations in $\alpha\beta$ Space 14                                          |

| 2.3 | 4-Leg Inverter Switching Combinations                                                                    |

| 2.4 | 4-Leg Inverter Switching Combinations in $\alpha\beta\gamma$ Space 16                                    |

| 3.1 | 3x3 Matrix Converter Stationary and Zero Switching Com-<br>binations                                     |

| 3.2 | $3x3$ Matrix Converter Stationary and Zero Switching Combinations transformed in the $\alpha\beta$ Plane |

| 5.1 | Rotating Switching States for the 4-Leg Matrix Converter . 54                                            |

| 5.2 | Stationary and Zero Switching States for the 4-Leg MatrixConverter56                                     |

| 5.3 | Tetrahedron Lookup Table                                                                                 |

| 5.4 | Switching state selection example                                                                        |

| 5.5 | The Base Vectors for the stationary space vectors 71                                                     |

| 6.1 | Switching state and Duty-Cycle selection for the 4-Leg Inverter                                          |

| 6.2 | Switching States for a 4-Leg Inverter                                                                    |

| 6.3 | Switching state and Duty-Cycle selection for the 4-Leg Inverter                                          |

| 6.4 | Switching state selection example                                                                        |

| 6.5 | Tetrahedron Lookup                                                                                       |

| 6.6 | Switching state selection example                                                                        |

| 6.7 | Switching state selection example                                                                        |

| 6.8  | Switching state selection example                                              |

|------|--------------------------------------------------------------------------------|

| 6.9  | Switching state output leg input phase                                         |

| 6.10 | Modified switching state order to minimise the number of switching transitions |

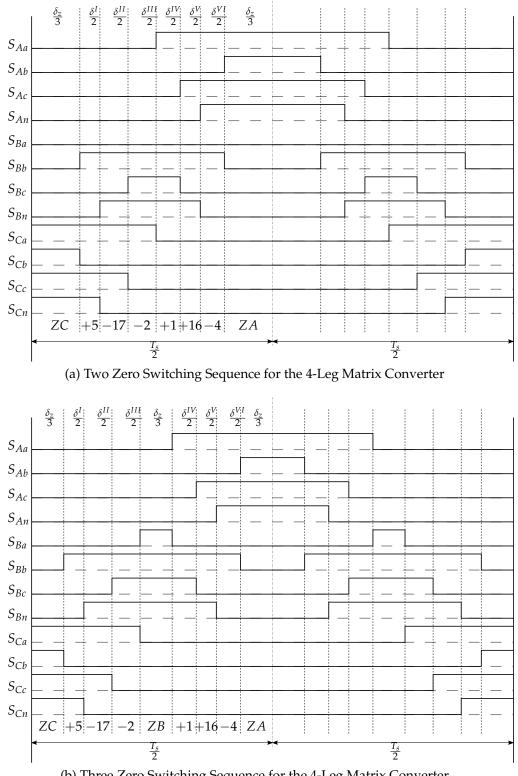

| 6.11 | Two Zero Switching State Sequence                                              |

| 6.12 | Three Zero Switching State Sequence                                            |

# Acronyms

- **DSP** digital signal processor.

- FCC force-commutated cycloconverter.

- FET field effect transistor.

- **FFT** fast Fourier transform.

- FIFO First-In First-Out.

- **FPGA** field programmable gate array.

- **GPU** ground power supply unit.

- **GTO** gate turn-off thyristor.

- **GUI** graphical user interface.

- HPI Host Port Interface.

- **IGBT** insulated gate bipolar transistor.

- MEX Matlab executable.

- NCC naturally commutated cycloconverter.

- **PCB** printed circuit board.

- **PEMC** Power Electronic and Machine Control.

- PLL phase-locked loop.

- **PWM** pulse-width modulation.

- SCR silicon controlled rectifier.

- **SVM** space vector modulation.

ACRONYMS

**UPS** uninterruptible power supply.

**USB** Universal Serial Bus.

### CHAPTER 1

# Introduction

Over recent years there has been an increased interest in static power converters, and this has led to a rapid improvement in their technology. The use of such converters in various AC power supply applications has also grown, and still continues to do so, with static power converters now being a common part in many different systems, from uninterruptible power supplies (UPSs), power converters in submarines through to ground power supply units (GPUs) for aircraft. One other typical application is for mobile power generation, and such a system is shown in Figure 1.1. This is an outline of a complete standalone system for providing a three-phase power supply wherever it is needed using a variable speed generator. The particular setup shown, uses the variable speed generator connected to a power converter, which allows the engine driving the generator to operate over a wide range of engines speeds and loads, with the power converter then providing a fixed frequency fixed voltage supply[1].

The power converter used in the scheme shown in Figure 1.1 could be a standard 3-phase rectifier/inverter setup, although this is a good setup where a matrix converter could be used. There is a problem with both of these types of converter, and it is that, while capable of generating a balanced three-phase supply, they are not able to operate with unbalanced, non-linear, or single-phase loads. To enable the system to generate an AC supply capable of supplying single-phase or unbalanced three-phase loads the converter needs to be able to deal with the unbalanced neutral, or zero-sequence, current. One method for doing this with an inverter is to increase the number of converter output legs to include a neutral connection[2]. Extending this in the case of the matrix converter would result in a 3x4, or four-leg, matrix converter as shown in Figure 1.2. This shows a simplified version of Figure 1.1 with a four-leg matrix converter attached to the generator.

Figure 1.1: An Example of a Standalone Power Supply System using a variable speed generator

Figure 1.2: A 4-Leg Matrix Converter as part of a Standalone Power Generation System

With the introduction of the fourth leg, this adds another output variable that needs to be controlled, and so the modulation techniques why apply to the 3x3 matrix converter[3–6] are no longer valid, and so a new modulation strategy needs to be formulated for this new arrangement. After the work by Huber and Borojevic [7–10] and later Casadei[3, 4] on adapting space vector modulation (SVM) for use with the 3x3 matrix converter, and then Ryan and De Doncker [11, 12] along with Zhang at al[2, 13, 14] for the work on 3-dimensional SVM for the 4-leg inverter, these both proved as useful pointers towards how a successful technique could be derived for the 4-leg Matrix Converter. Therefore, this work

sets out to explore the design of a Space Vector Modulation technique that is capable of controlling a 4-leg matrix converter, and then goes on to detail the building and testing of such a converter.

The basis of the space vector modulation strategy for the 3x3 matrix converter[3, 7] was derived from the techniques for both the controlled rectifier, and the inverter. This new technique will mirror this, and so be derived from the modulation method used for a 3-phase rectifier and a four-leg inverter[12, 14]. This will use a space vector representation in a three-dimensional  $\alpha\beta\gamma$  space to describe the output voltage and switching states[11, 12, 14]. This modulation technique will enable the inverter, and thus the matrix converter, to provide any set of output lineto-neutral voltages, balanced or unbalanced, that may be required. This three-dimensional approach will then be combined with the standard two-dimensional SVM method for the input side of the matrix converter, in a similar way to that performed for the 3x3 matrix converter[3, 4]. The resulting SVM method will be a way of controlling the modulation of the four-leg matrix converter so as to produce any set of line-to-neutral voltages whilst also independently controlling the phase of the input current waveforms.

## **1.1** The Matrix Converter

Matrix converters are a class of converters which perform direct AC-AC power conversion and themselves are part of the larger class of converter which are called cycloconverters. The process is called direct conversion to differentiate them from the more well known rectifier and inverter pairing as there is no intermediate DC link, and no energy storage devices within the converter. Cycloconverters first appeared in the 1920s and 1930s using mercury arc rectifiers[15–17] and are still in use today[17, 18], although now using devices such as the silicon controlled rectifier (SCR) and gate turn-off thyristor (GTO), in very high power industrial applications such a rolling mills.[19]. An example of 3-phase cycloconverter is shown in Figure 1.3.

The cycloconverters themselves fall into two main groups:-

- those which use the supply line voltage to perform the current commutation between the devices, which are known as naturally commutated cycloconverters (NCCs)

- those in which the current commutation is forced between devices,

and are known as force-commutated cycloconverters (FCCs)

The naturally commutated cycloconverters use devices such as thyristors and SCRs to be able to control the point at which the device starts conducting, thus, by choosing the correct phases from the input voltage, an output voltage can be synthesised. However, due to the nature of the devices they require the current in the device to reach zero before the device can be turned off, so while it is possible to control the turn on of each device, the turn off happens as the current naturally falls within the device due to the changes in input voltage. Being able to control only the device turn on means that the range output frequency is limited to being below the input frequency[15–17].

Figure 1.3: A 3-phase Cycloconverter

With the advance in the capability of switching devices, most notably insulated gate bipolar transistors (IGBTs), and due to its relative complexity, which can be seen in Figure 1.3, this type of cycloconverter now tends to only be used in high power applications, above the 1MW level, where the low frequency output is able to be used effectively, for example, like driving induction motors in large industrial processes, or for thrusters for large navel vessels[17, 18].

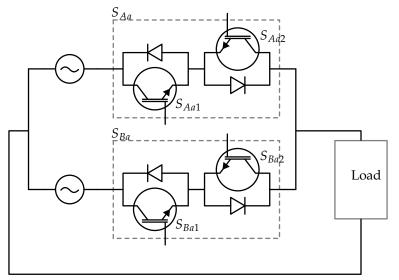

The force-commutated cycloconverters on the other hand, use devices which are capable of being switched off while current is still flowing through them, and so can be turned off at any point in the conduction cycle, instead of having to wait for the current through the device to drop to zero. This allows the force-commutated cycloconverter to overcome the largest drawback of the naturally commutated one, and be able to produce outputs at any frequency required, regardless of the input frequency[5].

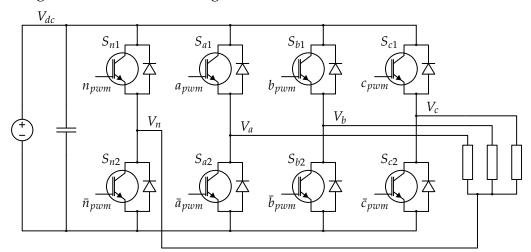

Figure 1.4: A 3-Leg Matrix Converter

A 3x3 matrix converter is shown in Figure 1.4, and due to using switches that have the ability to be turned of, this allows the circuit to be simpler. Although the concept of matrix converters had been around for a number of years it was not until Alesina and Venturini published a paper at the beginning of the 1980s[5] that there become a way of controlling them which allowed both the input current and the output voltage to be

The initial Alesina and Venturini method had a disadvantage though, that the output voltage was restricted to be a maximum of only 0.5 of the input. However, towards the end of the 1980s they published a number of papers which first showed that the theoretically maximum output voltage was  $\frac{\sqrt{3}}{2}$ [20] and then went on to show how this was possible with their optimum method[6]. Lipo produced a similar result in 1989, while also succeeding in building a working converter[21] to demonstrate this.

At around the same time, a number of papers by Huber and Borojevic were published, which presented a new space vector modulation technique for the matrix converter [7–10]. This like the Alesina\Venturini Optimum method, was able to produce the theoretical maximum output voltage. Space Vector Modulation is a well known technique for controlling inverters, and it uses a technique which transforms the input and output voltages and currents into a 2-dimensional plane where they can then be easily manipulated. This is as opposed to the method Alesina and Venturini used which is based around the use and theory of sine waves.

Later on the space vector modulation technique was refined further by Casadei[3, 4], and while more recent matrix converter configurations

and modulation strategies have been proposed[22, 23], it is the technique proposed by Casadei which this project seeks to extend onto the 4-Leg Matrix Converter.

## **1.2 The 4-leg Inverter**

The four-leg inverter first appeared in the early 1990's[24] when a solution was sought to allow the standard 3-leg inverter to drive unbalanced and non-linear loads[24–27]. Due to the nature of these loads they cause an imbalance in the current drawn from each phase of the supply, which then requires an extra neutral connection to deal with the zero sequence current which then results. While the use of a split capacitors to provide this neutral point was investigated[26, 28], this arrangement only works well if the imbalance, or non-linearity, is small. Instead of the split capacitors, the 4-legged inverter uses an extra inverter leg to provide this connection, and Figure 1.5 shows an example.

Figure 1.5: A 4-Leg Inverter

The initial attempts at controlling the 4-leg inverter were based around controlling the fourth leg separately, and using it to reduce any deviation in the neutral voltage[24, 26]. It was then in the late 1990's that Space Vector Modulation techniques for these inverters were introduced[25]. This was around the same time that Zhang et al[2, 13] introduced a new 3-Dimensional Space Vector Modulation technique which allowed the independent control of each of the 3 main output phases with respect to the neutral. The concepts which were introduced by Zhang were then later expanded upon by Ryan, Lorenz and De Doncker[11, 12] who produced a mathematical grounding for this new SVM technique.

Later in 2002, Zhang et al presented a fuller version of their original approach[14], and it is this work that this project seeks to extend in

conjunction with the SVM technique for matrix converters which was proposed by Casadei[4].

# 1.3 The 4-leg Matrix Converter

The 4-leg Matrix Converter was, at the start of this project, a novel circuit which had yet to see any work published about it, although this may not be surprising with the majority of research effort in the matrix converter field being concentrated on the practical side to converter implementation, and the relative lack of appreciable applications.

Figure 1.6: A 4-Leg Matrix Converter

It is, quite simply a 3x3 matrix converter with a fourth output leg added to act as the neutral leg, with Figure 1.6 showing the basic layout. The idea being that as with the 4-leg inverters, the extra output leg would enable the converter to be able to power non-linear and unbalanced loads.

At the beginning of this work, although presumed possible, it was unknown as to the ability to control one of these converters by using either the Space Vector Modulation principles, or the Alesina\Venturini methods. The Space Vector Modulation SVM method was chosen to be the basis of the work as it looked to be the most promising due to the existence of similar methods for both the matrix converter and the 4-leg inverter.

# 1.4 Applications and Limitations

One major application for this type of converter is as part of a field power supply, which is the type of system briefly described above and shown in

#### **CHAPTER 1: INTRODUCTION**

Figure 1.1, and which has since entered development by the University of Nottingham[29, 30]. In this application it is able to demonstrate its main advantage over other types of converter in that it is able to supply power for not only balanced 3-phase sources, but also unbalanced and single phase loads. So, along with the advantages that comes from being a matrix converter, so it being compact and able to achieve high power densities due to not requiring a DC link capacitor, means that it is highly suited to this task.

Having the converter in this configuration, running directly from a generator also helps mitigate the biggest drawback of this converter, and that is the quality of the input current when drawing an unbalanced load. As will be demonstrated, once the load becomes unbalanced, due to the direct nature of the converter with it having no energy storage elements unlike a normal inverter, there is no way to buffer the supply from the irregular power drawn, which, if the load is highly unbalanced can lead to distortion of the supply voltage. However, with the standalone setup above these harmonic currents will be drawn from the generator, and by careful speed control of the engine the worst effects of this imbalance can be moderated.

One characteristic that this converter has, is the ability to individually alter its output phase voltages, and frequencies, independently of one another. While this might not immediately appear to have an application, it might be of some use when dealing with fault situations on the load, where the converter would be able to balance the load power per phase individually in order to not affect the supply, however such work fell outside the scope of this project and so will need to be investigated separately.

# 1.5 Objectives

The objective of this project was simple, to investigate the use of Space Vector Modulation to enable the control a 4-Leg Matrix converter. To this end it would have a number of outcomes:

Firstly, as this is a novel implementation of SVM on a new converter, it would involve the understanding and analysis of the two similar types of space vector modulation that previously existed, that of the 4-leg inverter and the matrix converter, and only from this point would it be possible to extent both methods to cover the 4-leg matrix converter. Then once the theory behind the operation of those converters was under-

#### **CHAPTER 1: INTRODUCTION**

stood, it would then be possible to understand the rules which would govern the behaviour of the 4-leg matrix converter. At this point it would then be possible to derive the equations which would govern its operation.

The next objective would be to then produce a set of simulations which would be able to accurately model the behaviour of the 4-leg matrix converter using the derived equations. This would lead to a set of Matlab programs which however this would first require the implementation of the two other converters to prove that the

The final objective in this project is to build and run a working demonstration model of the 4-leg matrix converter. This would involve the evolution of a pre-existing matrix converter design to add the extra output leg, and then require a new set of software to be able to operate and control the converter.

# 1.6 Thesis Overview

In Chapter 1 the concept of the matrix converter is discussed along with a brief history of the circuit, followed by a short discussion on the 4-leg inverter. This will then follow on to an introduction of the concept of the 4-Leg Matrix converter, followed by short look at a possible implementation, and also a look at its possible drawback.

Chapter 2 then looks into the detail of how a number of different modulation schemes work for the 4-leg inverter, most importantly, it sets out the basis for and the equations which govern the use of space vector modulation with the circuit.

Chapter 3 looks at the other important relative of the 4-leg matrix converter, the normal matrix converter and goes on to examine the two major different methods which enable its control, finishing on the implementation of space vector modulation for the converter.

Chapter 4 then takes a brief look into the different possible commutation strategies which are employed in switched power converters, and matrix converters specifically.

In Chapter 5 the basis behind Space Vector Modulation of a 4-Leg Matrix converter is derived. Starting by looking at both the input and outputs vector spaces, this chapter goes on to see how they are linked together, demonstrating the symmetry between the two and produces the calculations which will select the required switching states and calculate the

#### duty cycles.

Chapter 6 then builds on the work of the previous chapter, taking the derived equations and then initially simulates them mathematically within Matlab, before moving on to perform a number of circuit based simulations within the Saber simulation software. These simulations will be used to validate the derivation, while also becoming a good base for the code which will be required to build an actual converter.

Chapter 7 describes the build of a demonstration converter based on an existing 3x3 matrix converter design. This chapter briefly looks at each of the main parts that goes into building a converter, describing its operation and going into detail where it is required.

Chapter 8 gives a summary of the results from testing the converter. It shows how the output from the converter is very well matched with that expected after the simulations, but then goes on to describe the issues which the converter had during testing, which ultimately meant that the converter failed and stopped testing short of the ideal, but still with enough information to demonstrate that the concept worked well.

Chapter 9 then follows with the conclusions on the work presented here.

#### CHAPTER 2

# **Four-Leg Inverter Modulation**

The four-leg inverter is an evolution of the standard three-leg inverter, and was bought about by the need to run non-linear and unbalanced three-phase loads, a fourth-wire as the neutral connection to the load. This was initially configured so that the fourth wire was held at the midpoint of a pair of capacitors[28], with Figure 2.1 showing an example of this layout.

Figure 2.1: 3-Leg 4-Wire Inverter with a Split dc Neutral Connection

As can be seen the pair of capacitors, when charged, hold the voltage of the fourth wire at the midpoint of the DC voltage, with any neutral current being passed to one or the other of these. This arrangement works well when the level of unbalance is low, and so neutral currents are relatively low, as the technique relies upon the capacitors holding the neutral point voltage steady at the mid-point of the DC-link. But as loads become more non-linear or unbalanced then the neutral current can become large, with this current needing to flow through the capacitors and so requiring large value capacitors capable of handling high ripple currents to avoid shifting the neutral point, which if allowed to occur will distort the output voltages.

This is actually a relatively simple circuit to control however, with each of the three switched legs effectively operating as a stand-alone halfbridge single phase inverter, switching its output about the clamped DC mid-point. This means that a simple carrier based pulse-width modulation (PWM) technique can be employed as shown below in Figure 2.10. In this technique, each of the three output phases is driven by a separate voltage demand signal and these are then compared to a triangular carrier waveform. The results of these comparisons are then fed into the respective gate drive circuits, which in turn drive the IGBTs.

Figure 2.2: 3-Leg 4-Wire Inverter PWM

However, using such a simple technique shows another drawback of this topology, in that it only allows a maximum voltage transfer ratio of  $0.5V_{dc}$  per phase. Techniques which are used in 3-phase 3-wire inverters to increase the maximum voltage transfer ratio, such as Third Harmonic Injection, are now not really applicable. For example, with third harmonic injection, the injected harmonics present in the output phases will force a shift in the neutral point voltage, at the third harmonic frequency, and so generate a respective neutral current through the capacitors.

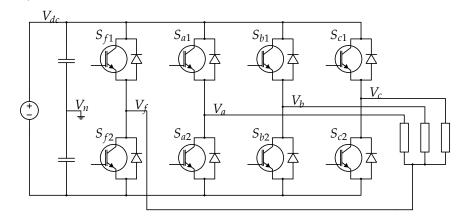

# 2.1 Space Vector Modulation of the 4-Leg 4-Wire Inverter

To overcome the limitations with the above circuit, instead of generating the neutral voltage using a split DC link the neutral voltage can be generated by using a fourth inverter leg[24, 25, 27], leading to the actual 4-leg inverter as shown in Figure 2.3.

Figure 2.3: 4-Leg 4-Wire Inverter

Now while it is possible to independently control the neutral voltage to mimic that generated by the split capacitor circuit above, this does not make full use of the ability of the extra leg to control the neutral point to any voltage up to the DC link voltage. However, once the neutral voltage is shifted from its mid point the simple PWM control of the 3-Leg 4-wire inverter is no longer enough, as and shift in the neutral voltage needs to be reflected in changes to all 3 phase voltages. As such, the Space Vector Modulation technique which is commonly used in 3-wire inverters was extended by Zhang et al in 1997[2, 13] to allow the control of the 4-Leg inverter. This method is briefly described below, after a short introduction to how Space Vector Modulation on a more normal 3-leg inverter.

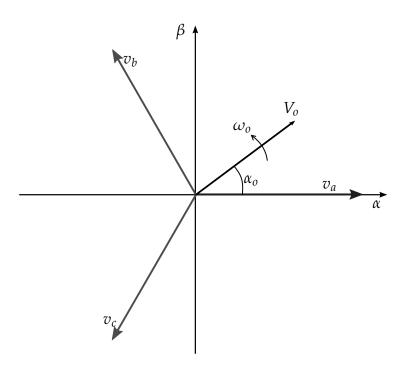

So, consider first a standard 3-leg inverter where the relationship between the three phase voltages  $V_a$ ,  $V_b$  and  $V_c$  defined by

$$V_a + V_b + V_c = 0 (2.1.1)$$

This constraint means that only 2 of the phase voltage variables are actually independent. Using this means that the three phase voltages can be transformed into a 2-dimensional space, in this case the  $\alpha\beta$  space using (2.1.2)

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{a} \\ V_{b} \\ V_{c} \end{bmatrix}$$

(2.1.2)

With a 3-leg inverter, each leg has only got two possible switching states during operation, that is to switch that output leg to either the positive or the negative of the DC link. With 3 legs, each with 2 possible switching states, this gives 8 possible switching states that can be generated and these are shown in Table 2.1 below.

Table 2.1: 3-Leg Inverter Switching Combinations

|       | ppp                 | nnn                  | pnn                  | ppn                  | npn                  | npp                  | nnp                  | pnp                  |

|-------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Va    | $\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $\frac{1}{2}V_{dc}$  | $\frac{1}{2}V_{dc}$  | $-\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $\frac{1}{2}V_{dc}$  |

| $V_b$ | $\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $\frac{1}{2}V_{dc}$  | $\frac{1}{2}V_{dc}$  | $\frac{1}{2}V_{dc}$  | $-\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ |

| $V_c$ | $\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $-\frac{1}{2}V_{dc}$ | $\frac{1}{2}V_{dc}$  | $\frac{1}{2}V_{dc}$  | $\frac{1}{2}V_{dc}$  |

Transforming the information in Table 2.1 into the 2-dimensional  $\alpha\beta$  space using (2.1.2) then gives the results shown in Table 2.2

Table 2.2: 3-Leg Inverter Switching Combinations in  $\alpha\beta$  Space

|   |              | ppp | nnn | pnn                 | ppn                        | npn                        | npp                  | nnp                         | pnp                         |

|---|--------------|-----|-----|---------------------|----------------------------|----------------------------|----------------------|-----------------------------|-----------------------------|

|   | $V_{\alpha}$ | 0   | 0   | $\frac{2}{3}V_{dc}$ | $\frac{1}{3}V_{dc}$        | $-\frac{1}{3}V_{dc}$       | $-\frac{2}{3}V_{dc}$ | $-\frac{1}{3}V_{dc}$        | $\frac{1}{3}V_{dc}$         |

| Ì | $V_{\beta}$  | 0   | 0   | 0                   | $\frac{1}{\sqrt{3}}V_{dc}$ | $\frac{1}{\sqrt{3}}V_{dc}$ | 0                    | $-\frac{1}{\sqrt{3}}V_{dc}$ | $-\frac{1}{\sqrt{3}}V_{dc}$ |

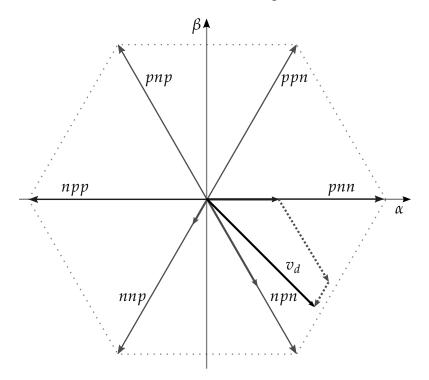

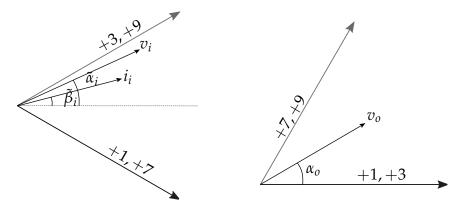

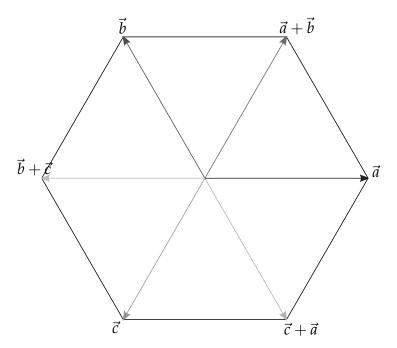

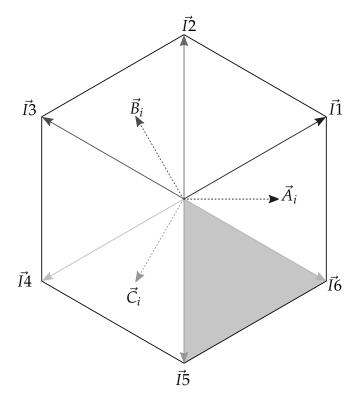

The vectors resulting from these 8 switching states can then be plotted onto an Argand diagram, giving the well known result shown in Figure 2.4. This plot shows 6 space vectors placed equidistant from each other around the origin, and these are created by the non-zero switching states. The remaining two vectors, *ppp* and *nnn*, switch the same voltage to each of the three output legs, and as such they are known as the zero voltage states and do not produce a vector within the  $\alpha\beta$  space.

Next, consider the demand voltages which are required as an output from the inverter, now because this is a 3-leg inverter this will be a 3-phase set of voltages which meet the requirement set out in equation (2.1.1). Converting this demand voltage into  $\alpha\beta$  space using (2.1.2) produces a vector,  $v_d$ , as can be seen in Figure 2.4.

Figure 2.4: 3-Leg Inverter Demand Vector

The basic assumption behind Space Vector Modulation is that this demand vector,  $v_d$ , within  $\alpha\beta$  space can be synthesised by using the two adjacent space vectors created by the converter switching states. So, in the example shown in Figure 2.4, the demand vector,  $v_d$  can be generated using the space vector 1 and 6, which correspond to the switching states *pnn* and *npn*.

Now, consider an inverter with an added fourth leg, as shown in Figure 2.3. By adding this extra leg it means that the equation (2.1.1) above is no longer necessarily valid as

$$V_a + V_b + V_c + V_n = 0 (2.1.3)$$

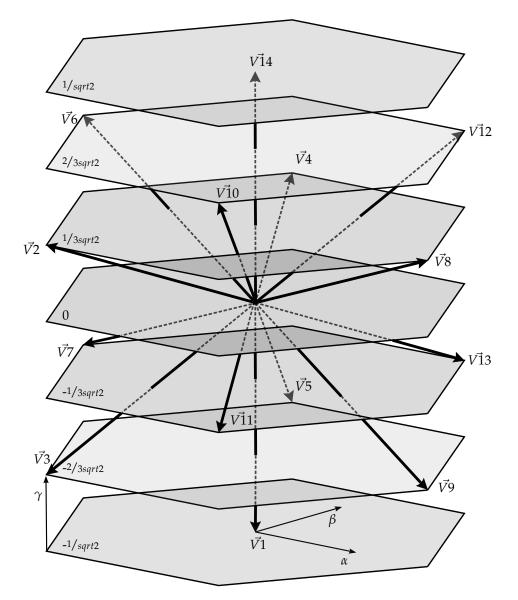

This means that all three phase voltages can now be considered to be truly independent of each other, and so the 2-dimensional  $\alpha\beta$  space does not have enough degrees of freedom to be able to describe them fully. To cater for the extra independent variable another degree of freedom needs

to be added, and so this is instead transformed into a 3-dimensional space. For this case it is the  $\alpha\beta\gamma$  space using (2.1.4)

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \\ V_{\gamma} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} & 0 \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} & 0 \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} & -\frac{3}{2} \end{bmatrix} \begin{bmatrix} V_{a} \\ V_{b} \\ V_{c} \\ V_{n} \end{bmatrix}$$

(2.1.4)

Now, due to inclusion of the extra neutral leg, instead of the 8 possible switching combinations shown in Table 2.1 above for the 3-leg inverter, there are now 16 different ones, which are shown in Table 2.3 below

|                 | pppp     | nnnp      | pnnp      | ppnp      | npnp      | nppp            | nnpp      | pnpp      |

|-----------------|----------|-----------|-----------|-----------|-----------|-----------------|-----------|-----------|

| Van             | 0        | $-V_{dc}$ | 0         | 0         | $-V_{dc}$ | $-V_{dc}$       | $-V_{dc}$ | 0         |

| V <sub>bn</sub> | 0        | $-V_{dc}$ | $-V_{dc}$ | 0         | 0         | 0               | $-V_{dc}$ | $-V_{dc}$ |

| V <sub>cn</sub> | 0        | $-V_{dc}$ | $-V_{dc}$ | $-V_{dc}$ | $-V_{dc}$ | 0               | 0         | 0         |

|                 | pppn     | nnnn      | pnnn      | ppnn      | npnn      | nppn            | nnpn      | pnpn      |

| Van             | $V_{dc}$ | 0         | $V_{dc}$  | $V_{dc}$  | 0         | 0               | 0         | $V_{dc}$  |

| V <sub>bn</sub> | $V_{dc}$ | 0         | 0         | $V_{dc}$  | $V_{dc}$  | $V_{dc}$        | 0         | 0         |

| V <sub>cn</sub> | $V_{dc}$ | 0         | 0         | 0         | 0         | V <sub>dc</sub> | $V_{dc}$  | $V_{dc}$  |

Table 2.3: 4-Leg Inverter Switching Combinations

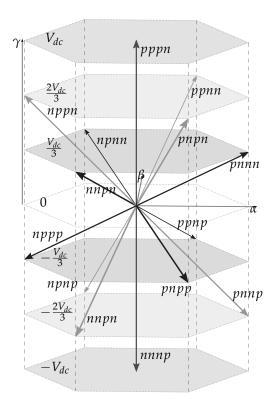

Transforming this into the  $\alpha\beta\gamma$  space using (2.1.4) then gives the results shown in Table 2.4.

|                                                                      | pppp   | nnnp      | pnnp                 | ppnp                       | npnp                                     | nppp                                     | nnpp                                     | pnpp                        |

|----------------------------------------------------------------------|--------|-----------|----------------------|----------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-----------------------------|

| $V_{\alpha}$                                                         | 0      | 0         | $\frac{2}{3}V_{dc}$  | $\frac{1}{3}V_{dc}$        | $-\frac{1}{3}V_{dc}$                     | $-\frac{2}{3}V_{dc}$                     | $-\frac{1}{3}V_{dc}$                     | $\frac{1}{3}V_{dc}$         |

| $V_{\beta}$                                                          | 0      | 0         | 0                    | $\frac{1}{\sqrt{3}}V_{dc}$ | $\frac{1}{\sqrt{3}}V_{dc}$               | 0                                        | $-\frac{1}{\sqrt{3}}V_{dc}$              | $-\frac{1}{\sqrt{3}}V_{dc}$ |

| $V_{\gamma}$                                                         | 0      | $-V_{dc}$ | $-\frac{2}{3}V_{dc}$ | $-\frac{1}{3}V_{dc}$       | $-\frac{2}{3}V_{dc}$                     | $-\frac{1}{3}V_{dc}$                     | $-\frac{2}{3}V_{dc}$                     | $-\frac{1}{3}V_{dc}$        |

|                                                                      | nnnn   | nnnn      | <b>n</b> nnn         | <b>n</b> nnn               |                                          |                                          |                                          |                             |

|                                                                      | pppn   | nnnn      | pnnn                 | ppnn                       | npnn                                     | nppn                                     | nnpn                                     | pnpn                        |

| $V_{\alpha}$                                                         | 0      | 0         | $\frac{2}{3}V_{dc}$  | $\frac{1}{3}V_{dc}$        | $\frac{\text{npnn}}{-\frac{1}{3}V_{dc}}$ | $\frac{\text{nppn}}{-\frac{2}{3}V_{dc}}$ | $\frac{\text{nnpn}}{-\frac{1}{3}V_{dc}}$ | pnpn<br>$\frac{1}{3}V_{dc}$ |

| $\begin{array}{ c c }\hline V_{\alpha}\\\hline V_{\beta}\end{array}$ | 0<br>0 | 0         | 1                    | 1                          | 1                                        | 217                                      | 1 1 7 7                                  | 117                         |

Table 2.4: 4-Leg Inverter Switching Combinations in  $\alpha\beta\gamma$  Space

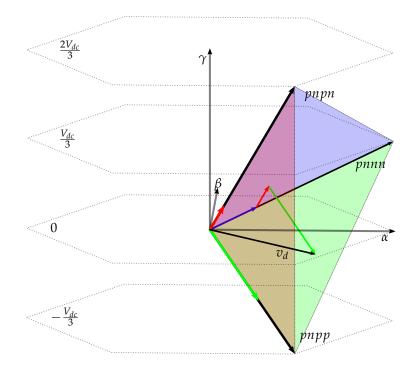

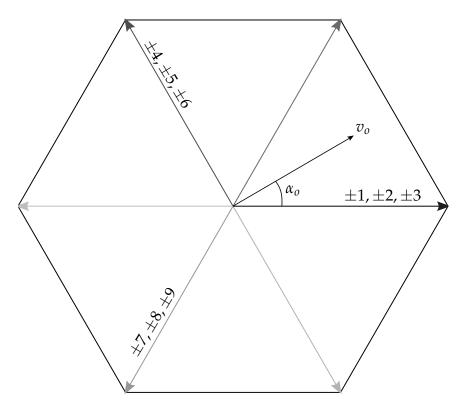

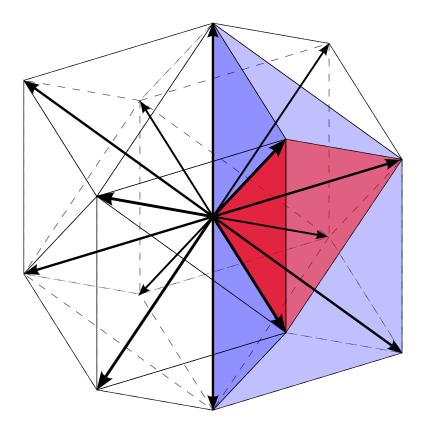

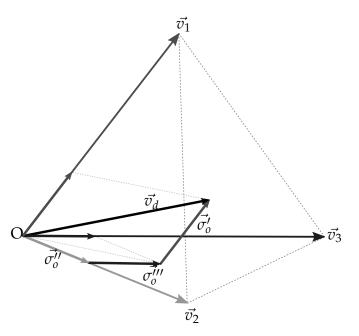

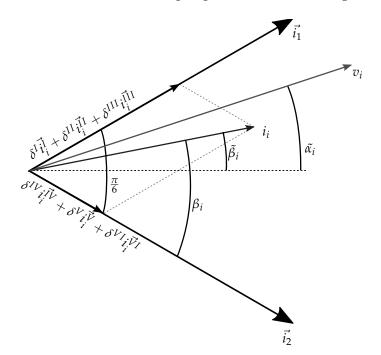

The vectors resulting from the 14 non-zero switching states can then be plotted in the  $\alpha\beta\gamma$  space as shown in Figure 2.5. The remaining 2 vectors, *pppp* and *nnnn*, switch the same voltage to each of the four output legs, and so they are known as the zero vectors as they do not produce a voltage across the output. As with the vectors for the 3-leg inverter shown in Figure 2.4, the vectors for the 4-leg inverter are all positioned equidistantly from each other within the  $\alpha\beta\gamma$  space, and the shape they describe is a type of icositetrahedron (24-faced polyhedron).

Figure 2.5: 4-Leg Inverter Switching Vectors

Next, consider a set of demand voltages which are required as the output from the inverter. Now, because this is a 4-leg inverter this can be any set of voltages which meet the requirement set out in equation (2.1.3) however, taking the example for the 3-leg inverter above, and applying (2.1.3) now gives

$$V_a = 240.00$$

(2.1.5)

$V_b = -327.85$

$V_c = 87.84$

$V_n = 0$

Converting this demand voltage into  $\alpha\beta\gamma$  space using (2.1.4) produces a vector,  $v_d$ ,

$$V_{\alpha} = 240.00$$

(2.1.6)

$V_{\beta} = -240.00$

$V_{\gamma} = 0$

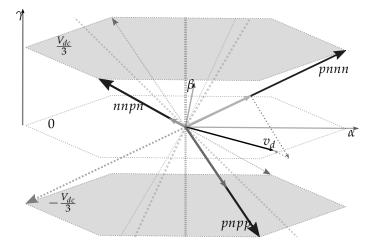

This vector can be seen in Figure 2.6 labelled as the demand vector,  $v_d$ , along with the 3 space vectors required to generate this demand.

Figure 2.6: 4-Leg Inverter Demand Vector

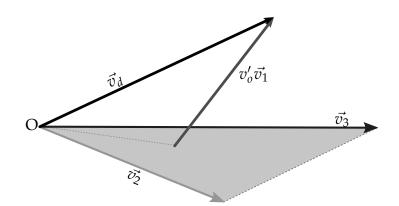

At any one time the demand vector,  $v_d$ , is bound in a space by 3 of the switching vectors, in the same way that the demand vector for the 2dimensional Space Vector Modulation is bounded by 2. These 3 switching vectors form the vertices of a tetrahedron, the base of which forms one face of the icositetrahedron in the  $\alpha\beta\gamma$  switching space. Just as the 3-leg inverter was able to synthesise the demand voltage by switching between the 2 adjacent switching vectors, the 4-leg inverter is able to synthesise its demand voltage by using these 3 switching vectors, which can be seen in Figure 2.7.

Now, while it is a relatively straightforward task to then calculate the duty cycles for those switching states for the 3-leg inverter, it becomes somewhat harder for the 4-leg inverter due to the number of different possible tetrahedrons. The solution proposed by Zhang is to use a look-up table which would define a matrix[2, 13] that could be used to directly calculate the duty cycles, so for the example shown in Figure 2.6, the demand vector would be in Prism IV and Tetrahedron 1, and the duty cycles would be calculated as

$$\begin{bmatrix} d_1 \\ d_2 \\ d_3 \end{bmatrix} = \frac{1}{V_{dc}} \begin{bmatrix} -\frac{1}{2} & -\frac{\sqrt{3}}{2} & 1 \\ \frac{1}{2} & -\frac{\sqrt{3}}{2} & -1 \\ \frac{3}{2} & \frac{\sqrt{3}}{2} & 0 \end{bmatrix} \begin{bmatrix} V_{\alpha}(240.00) \\ V_{\beta}(-240.00) \\ V_{\gamma}(0.00) \end{bmatrix}$$

(2.1.7)

$$d_z = 1 - d_1 - d_2 - d_3 \tag{2.1.8}$$

Once the duty cycles are known, it is a simple case to produce the re-

Figure 2.7: 4-Leg Inverter Demand Vector Tetrahedron

spective PWM signals as shown in Figure 2.8 where each duty cycle is for a respective switching state.

Figure 2.8: 4-Leg Inverter Space Vector Modulation PWM Output

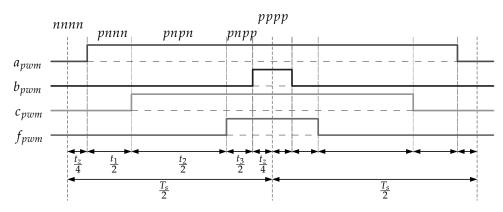

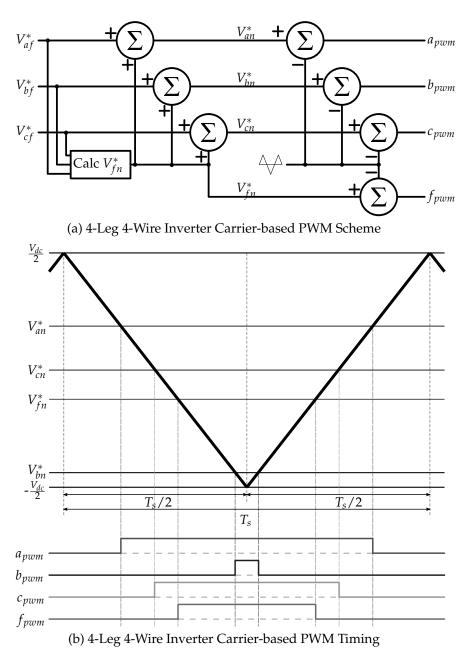

## 2.2 Carrier Based Pule-Width Modulation of the 4-Leg 4-Wire Inverter

Alongside the Space Vector Modulation technique shown above, a complete carrier based implementation of the 4-leg inverter has been proposed by Kim and Sul[31] in 2004. This technique uses an 'offset voltage' concept to be able to generate the three independent voltages  $V_{af}$ ,  $V_{bf}$  and  $V_{cf}$ .

Figure 2.9: 4-Leg 4-Wire Inverter

Using the circuit of the 4-leg inverter as shown in Figure 2.9 the method states that the output line to neutral voltages are constrained by the following equation

$$-V_{dc} \le V_{af}, V_{bf}, V_{cf} \le V_{dc} \tag{2.2.1}$$

where each of the output voltages  $V_{af}$ ,  $V_{bf}$  and  $V_{cf}$  are defined by

$$V_{af} = V_{an} - V_{fn}$$

$$V_{bf} = V_{bn} - V_{fn}$$

$$V_{cf} = V_{cn} - V_{fn}$$

(2.2.2)

This allows the use of  $V_{fn}$ , the fourth inverter output leg, as an offset voltage which can be manipulated to control the other 3 output leg voltages where

$$-\frac{V_{dc}}{2} \le V_{an}, V_{bn}, V_{cn} \le \frac{V_{dc}}{2}$$

(2.2.3)

and

$$-\frac{V_{dc}}{2} \le V_{fn} \le \frac{V_{dc}}{2} \tag{2.2.4}$$

It can then be shown that while  $V_{fn}$  is required to meet the constraints shown in (2.2.4), in fact  $V_{fn}$  rarely falls outside the following limits

$$-\frac{V_{dc}}{2} - V_{min} \le V_{fn} \le \frac{V_{dc}}{2} - V_{max}$$

(2.2.5)

where

$$V_{min} = \min(V_{af}, V_{bf}, V_{cf})$$

(2.2.6)

$$V_{mid} = \operatorname{mid}(V_{af}, V_{bf}, V_{cf})$$

(2.2.7)

$$V_{max} = \max(V_{af}, V_{bf}, V_{cf})$$

(2.2.8)

and this should be limited to

$$V_{max} - V_{min} < V_{dc} \tag{2.2.9}$$

as this would limit the possible offset voltages if the difference between the maximum and minimum output voltages is equal to or greater than the DC link voltage.

The optimum level for  $V_{fn}$  is then be calculated as

$$V_{fn} = \operatorname{mid}\left(-\frac{V_{max}}{2}, -\frac{V_{min}}{2}, -\frac{V_{max}+V_{min}}{2}\right)$$

(2.2.10)

and the switching times for each leg calculated as

$$T_{a} = \frac{T_{s}}{2} + \frac{V_{an}}{V_{dc}}T_{s}$$

$$T_{b} = \frac{T_{s}}{2} + \frac{V_{bn}}{V_{dc}}T_{s}$$

$$T_{c} = \frac{T_{s}}{2} + \frac{V_{cn}}{V_{dc}}T_{s}$$

$$T_{f} = \frac{T_{s}}{2} + \frac{V_{fn}}{V_{dc}}T_{s}$$

(2.2.11)

(2.2.12)

As demonstrated by Kim and Sul[31], this method gives equivalent performance to the 3-dimensional Space Vector Modulation method as described above.

Figure 2.10: 4-Leg 4-Wire Inverter Carrier-based PWM

#### CHAPTER 3

# **Matrix Converter Modulation**

The basic premise behind the matrix converter is that you have a set of nxp bi-directional switches arranged to connect n input phases to p output legs so that it is possible to connect any output leg to input phase. The most common configuration for this is the 3-phase to 3phase matrix converter which is shown in Figure 1.4. Due to the inherent bi-directional nature of the converter, with power able to flow in both directions, the labelling of the input and output is essentially arbitrary. However, due to the general modes of operation of the converter it has become the normal convention that the voltage stiff port is designated the input and the current stiff port the output. This designation does however impose a fundamental restriction on how the converter can be switched. This restriction is that no two input phases can be shorted together due to their voltage stiff characteristic, and no output legs can be left open circuit due to their current stiff behaviour.

Prior to the start of this work, the 3x3 matrix converter was the largest matrix converter for which a solution had been proposed, and this chapter will investigate the different modulation strategies which were common at that time, and which were used as the basis of this investigation.

Since the initial publication of the basic derivation on the 4-leg matrix converter [32] there have since been a number of different modulation methods for the 4-leg matrix converter proposed. Since these were not available at the time the work on this started they have not been included in this chapter, however a summary of the different methods will be discussed at the end of the Chapter 5.

#### 3.1 **Basic theory**

If we define the input and output voltages of the converter as the vectors (3.1.1) and (3.1.2) respectively

$$\mathbf{V_i}(t) = \begin{bmatrix} V_A(t) \\ V_B(t) \\ V_C(t) \end{bmatrix}$$

(3.1.1)

$$\mathbf{V_o}(t) = \begin{bmatrix} V_a(t) \\ V_b(t) \\ V_c(t) \end{bmatrix}$$

(3.1.2)

then a switching function  $\mathbf{S}(t)$  can be defined as

$$\mathbf{S}(t) = \begin{bmatrix} s_{Aa}(t) & s_{Ba}(t) & s_{Ca}(t) \\ s_{Ab}(t) & s_{Bb}(t) & s_{Cb}(t) \\ s_{Ac}(t) & s_{Bc}(t) & s_{Cc}(t) \end{bmatrix}$$

(3.1.3)

where a switch  $s_{np}$  in its on-state is represented by a 1 and in its off-state by a 0. This relates the output voltages  $\mathbf{V}_{\mathbf{o}}(t)$  to the input voltages  $\mathbf{V}_{\mathbf{i}}(t)$ so that

$$\mathbf{V_o}(t) = \mathbf{S}(t) \cdot \mathbf{V_i}(t) \tag{3.1.4}$$

To satisfy the restriction that no inputs can be shorted together and no outputs can be open circuit the following must always be true

$$\sum_{n=A,B,C} s_{na}(t) = \sum_{n=A,B,C} s_{nb}(t) = \sum_{n=A,B,C} s_{nc}(t) = 1$$

(3.1.5)

In a similar way the relationship for the input current is given by

$$\mathbf{I}_{\mathbf{i}}(t) = \mathbf{S}^{\mathbf{T}}(t) \cdot \mathbf{I}_{\mathbf{o}}(t)$$

(3.1.6)

where the matrix  $\mathbf{S}^{T}$  is the transpose of the matrix  $\mathbf{S}$ .

The switching matrix **S** gives us the switching function at any particular instant but as the switches are operated in sequence over a set sampling period, a more useful value is a modulation index. This states that for

each sampling period each input is switched to each output for a time  $t_{np}$ , so that

$$m_{np} = \frac{t_{np}}{T_{samp}} \tag{3.1.7}$$

Taking this set of modulation indexes the modulation matrix  $\mathbf{M}(t)$  can be constructed such that

$$\mathbf{V_o}(t) = \mathbf{M}(t) \cdot \mathbf{V_i}(t) \tag{3.1.8}$$

and

$$\mathbf{I}_{\mathbf{i}}(t) = \mathbf{M}^{\mathrm{T}}(t) \cdot \mathbf{I}_{\mathbf{o}}(t)$$

(3.1.9)

which expand to give

$$\begin{bmatrix} V_{a}(t) \\ V_{b}(t) \\ V_{c}(t) \end{bmatrix} = \begin{bmatrix} m_{Aa}(t) & m_{Ba}(t) & m_{Ca}(t) \\ m_{Ab}(t) & m_{Bb}(t) & m_{Cb}(t) \\ m_{Ac}(t) & m_{Bc}(t) & m_{Cc}(t) \end{bmatrix} \begin{bmatrix} V_{A}(t) \\ V_{B}(t) \\ V_{C}(t) \end{bmatrix}$$

(3.1.10)

and

$$\begin{bmatrix} I_A(t) \\ I_B(t) \\ I_C(t) \end{bmatrix} = \begin{bmatrix} m_{Aa}(t) & m_{Ab}(t) & m_{Ac}(t) \\ m_{Ba}(t) & m_{Bb}(t) & m_{Bc}(t) \\ m_{Ca}(t) & m_{Cb}(t) & m_{Cc}(t) \end{bmatrix} \begin{bmatrix} I_a(t) \\ I_b(t) \\ I_c(t) \end{bmatrix}$$

(3.1.11)

Once again, to satisfy the requirement that no input phase is short circuited and no output leg is open circuit

$$\sum_{n=A,B,C} m_{na}(t) = \sum_{n=A,B,C} m_{nb}(t) = \sum_{n=A,B,C} m_{nc}(t) = 1$$

(3.1.12)

where  $0 \le m_{np} \le 1$ .

These are the basic starting assumptions on which the different modulation strategies as based.

## 3.2 Alesina/Venturini Method

This scheme is was proposed by Alesina and Venturini in 1981[5], and it is a modulation method which allows direct control over the output voltage and input power factor.

It states that with a given set of sinusoidal input voltages  $\mathbf{V}_i(t)$  i, and assuming that the output currents are also sinusoidal and given by  $\mathbf{I}_o(t)$

$$V_{i}(t) = \begin{bmatrix} v_{i}\cos(\omega_{i}t) \\ v_{i}\cos(\omega_{i}t + \frac{2}{3}\pi) \\ v_{i}\cos(\omega_{i}t + \frac{4}{3}\pi) \end{bmatrix}$$

(3.2.1)

$$I_{o}(t) = \begin{bmatrix} i_{o} \cos(\omega_{o}t + \phi_{o}) \\ i_{o} \cos(\omega_{o}t + \frac{2}{3}\pi + \phi_{o}) \\ i_{o} \cos(\omega_{o}t + \frac{4}{3}\pi + \phi_{o}) \end{bmatrix}$$

(3.2.2)

From this a suitable modulation matrix  $\mathbf{M}(t)$  can be determined such that the required set of input currents  $\mathbf{I}_i(t)$  and output voltages  $\mathbf{V}_o(t)$  are both sinusoidal, while also being constrained by the modulation restriction stated in (3.1.12).

$$V_{o}(t) = \begin{bmatrix} v_{o}\cos(\omega_{o}t) \\ v_{o}\cos(\omega_{o}t + \frac{2}{3}\pi) \\ v_{o}\cos(\omega_{o}t + \frac{4}{3}\pi) \end{bmatrix}$$

(3.2.3)

$$I_{i}(t) = \begin{bmatrix} i_{i}\cos(\omega_{i}t + \phi_{i}) \\ i_{i}\cos(\omega_{i}t + \frac{2}{3}\pi + \phi_{i}) \\ i_{i}\cos(\omega_{i}t + \frac{4}{3}\pi + \phi_{i}) \end{bmatrix}$$

(3.2.4)

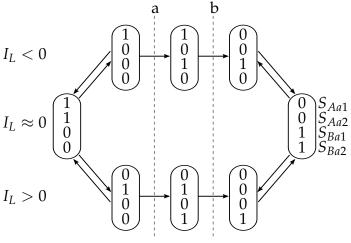

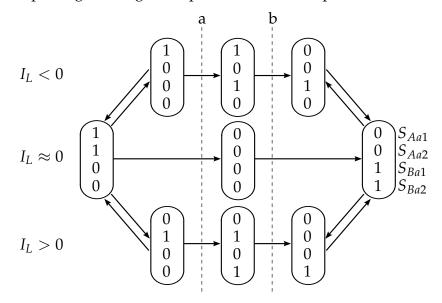

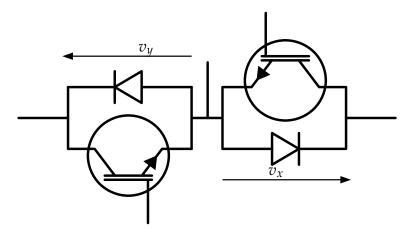

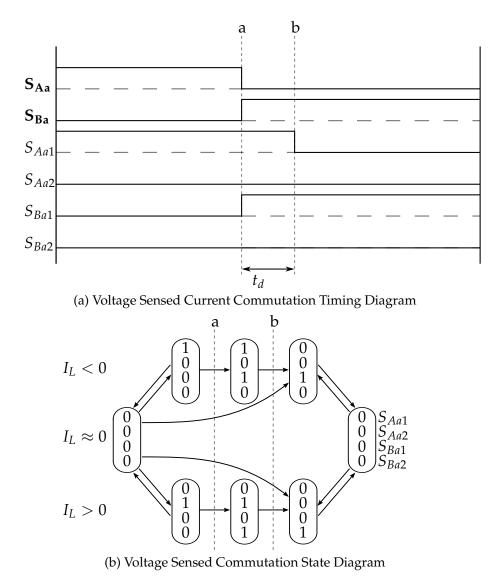

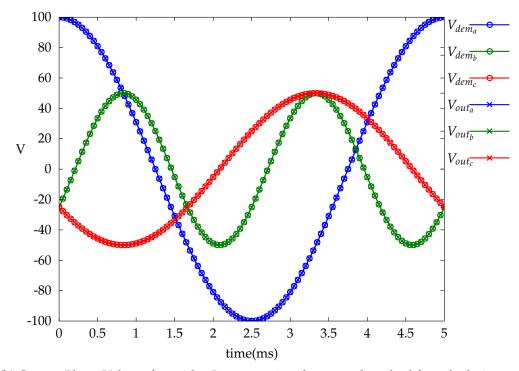

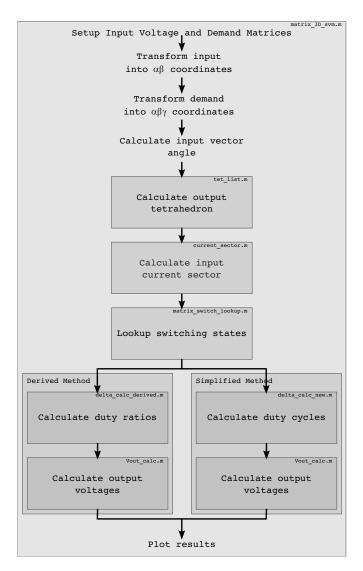

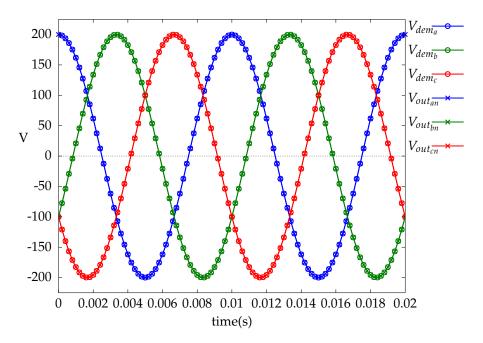

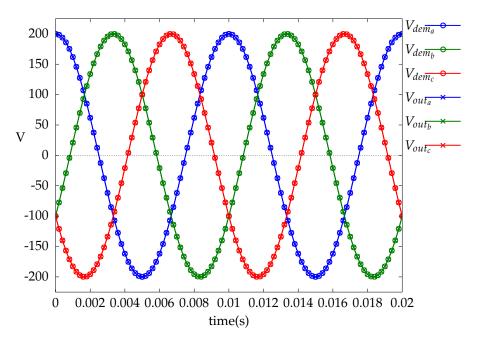

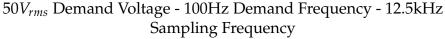

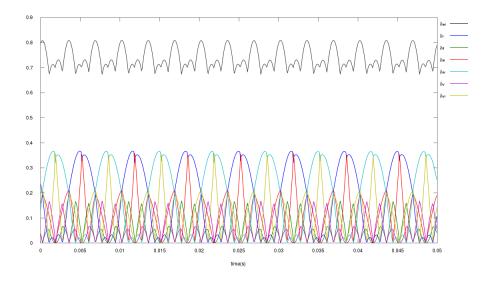

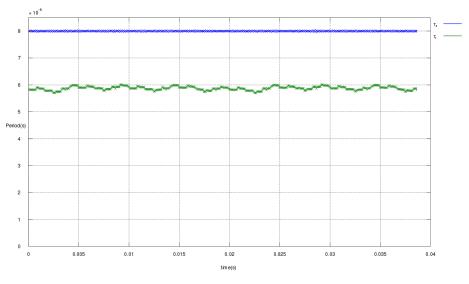

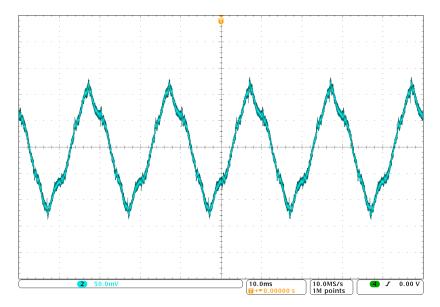

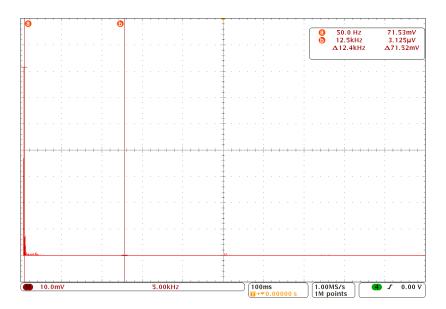

The solution to this the generalised equation for the modulation function  $\mathbf{M}(t)$  as