### Sliding Mode Observation of Capacitor Voltage in Multilevel Power Converters

Masoud Almaleki, M.Sc., B.Sc.

Submitted to the University of Nottingham for the degree of Doctor of Philosophy,

September 2010

### Abstract

Smart power supply grids may be required to link future energy production and consumers. Multilevel converters are a building block for smart grids. There are several structures of multilevel converters, for example the Neutral Point Clamped (NPC), the Flying Capacitor Circuit and the Cascaded H-Bridge (CHB) converter. The modular structure of the CHB multilevel converter makes it one of the best options for smart grids. Using modular converter structures reduces production and maintenance costs.

Implementation of efficient and fast controllers for multilevel converters requires accurate measurement of the voltages and currents for the system feedback loops. Knowledge of the DC link voltages is necessary to construct voltage control loops. In a typical CHB multilevel converter there are many DC links which means that a lot of voltage transducers maybe required. Voltage transducers at medium voltage are not easy to implement and add to system cost.

This thesis presents an efficient way to observe the DC link voltages and hence eliminate the cost associated with voltage transducers. A "Sliding Mode Observer (SMO) using the Equivalent Control Method" has been chosen because of its robustness against system uncertainties. Simulation and practical work has been performed on a three-phase, three-cell multilevel converter to validate the use of this observer.

### Acknowledgements

I would like to express my sincere thanks to my supervisors, Prof. Pat Wheeler and Prof. Jon Clare for all their guidance, continuous support and patience throughout my study.

I would also like to thank my PhD examiners Professor Tim Green and Professor Greg Asher for their time and valuable comments on my thesis.

Thanks are also due to my colleagues in the PEMC group for their help and support. I would especially like to thank Dr. Alan Watson for his helps with practical issues of the project.

Thanks also go to my dear sister, her husband and my lovely niece, Kiana, for their help and being supportive.

Finally, I want to thank my dearest mother who has always been enriching my life with her love and support. Thank you mother for everything.

Nottingham, 2010 Masoud Alamleki

# Contents

| 1. | Introduction                                         |

|----|------------------------------------------------------|

|    | 1.1. Thesis Objectives                               |

|    | 1.2. Thesis plan                                     |

|    |                                                      |

| 2. | Converter Design and Simulation                      |

|    | 2.1. Introduction                                    |

|    | 2.2. Power converter structure                       |

|    | 2.3. H-Bridge converter                              |

|    | 2.4. Phase-Shifted Cascaded PWM                      |

|    | 2.5. Converter modeling and design                   |

|    | 2.6. Converter modeling and design                   |

|    | 2.6.1. The current control loop                      |

|    | 2.6.2. The voltage control loop                      |

|    | 2.6.3. The capacitor voltage balancer                |

|    | 2.7. The DC-DC converter                             |

|    | 2.8. Simulation results for two-port power converter |

|    | 2.9. Summary                                         |

|    |                                                      |

| 3. | Sliding Mode Observers                               |

|    | 3.1. Introduction                                    |

|    | 3.2. History of observer                             |

|    | 3.3. Variable structure systems                      |

|    | 3.4. Sliding mode observer                           |

|    | 3.4.1. Traditional sliding mode observer             |

| 3.4.2. Sliding mode observer using the equivalent control method 55 |

|---------------------------------------------------------------------|

| 3.5. Observer robustness against system uncertainty                 |

| 3.6. Simulation results                                             |

| 3.6.1. Observer using sat function                                  |

| 3.6.2. Observer for the systems with uncertain terms                |

| 3.7. Summary                                                        |

| 4. | Sliding Mode Observer Implementation                                   | .74  |

|----|------------------------------------------------------------------------|------|

|    | 4.1. Introduction                                                      | . 74 |

|    | 4.2. SMO design for a single H-bridge converter                        | , 75 |

|    | 4.3. SMO design for the cascaded H-bridge (CHB) converter              | . 79 |

|    | 4.4. SMO design for the three-phase CHB multilevel converter           | 86   |

|    | 4.5. SMO design for the back-to-back converter topology                | 90   |

|    | 4.6. SMO design for the back-to-back topology with a DC-DC converter . | 94   |

|    | 4.7. The SMO for the complete two-port power converter                 | 99   |

|    | 4.8. Summary                                                           | 104  |

|    |                                                                        |      |

| 5. | Experimental Power Converter                                           | .05  |

|    | 5.1. Introduction                                                      | 105  |

|    | 5.2. Layout of experimental power converter                            | 105  |

|    | 5.3. Current and voltage transducers                                   | 108  |

|    | 5.4. Power converter module                                            | 110  |

|    | 5.5. The digital control unit                                          | 118  |

|    | 5.6. The Tustin method                                                 | 122  |

|    | 5.7. Practical results                                                 | 124  |

|    | 5.8. Summary                                                           | 129  |

|    |                                                                        |      |

| 6. | Sliding Mode Observer-Practical Implementation 1                       | .30  |

|    | 6.1. Introduction                                                      | 130  |

| 6.2. Observer equations for experimental power converter | 130   |

|----------------------------------------------------------|-------|

| 6.3. Observer equations in discrete form                 | . 135 |

| 6.4. Observer equations in fixed-point.                  | 142   |

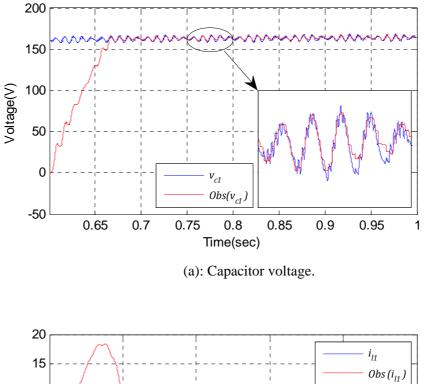

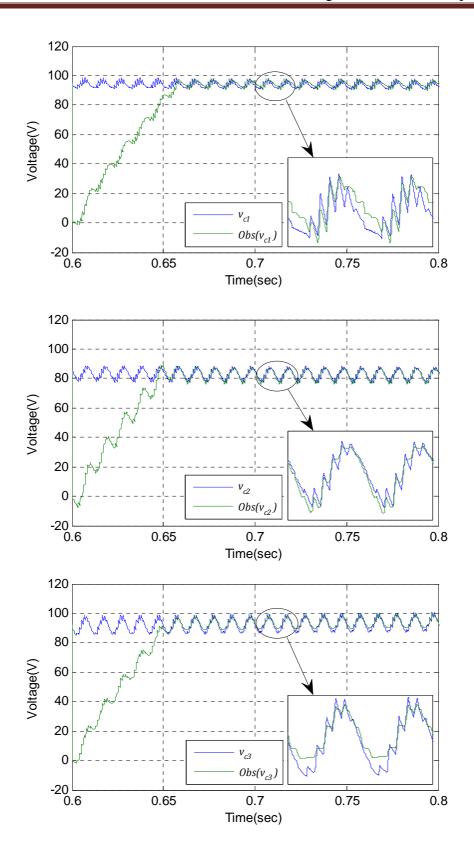

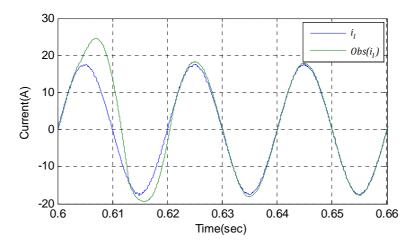

| 6.5. Practical results of observer                       | 156   |

| 6.6. Summary                                             | 159   |

|                                                          |       |

| 7. Conclusion                                            | . 160 |

| 7.1. Achievements and new contributions                  | 162   |

| 7.2. Further work                                        | 163   |

| Published Papers.                                        | 165   |

|                                                          |       |

### Chapter 1

## Introduction

Today's electric power generation systems convert about 33 percent of fuel energy into electricity [1]. The other 67 percent is dissipated as heat without recovery. Eight percent of this power is dissipated in the transmission lines. Twenty percent of the generation capacity is only for peak load demand, which is only five percent of the time [1].

Hydro, thermal and nuclear power generation are three major types currently being used. Hydro power plants have no pollution during operation but they cause significant environmental and often societal impacts during construction. Possible locations for hydro power plants depend on river locations. Significant construction and operational cost, as well as high pollution mean that thermal power plants are becoming a major problem. Nuclear power plants with existing technology are soon to be retired and they are not currently being replaced at a significant rate [2].

Environmental concerns mandate that thermal and nuclear power plants must be located far away from cities. This requires the construction of large, complex and expensive power transmission lines that causes ecological and environmental problems [2]. Construction of hydro, thermal and nuclear power plants are time consuming and very expensive. In today's competitive energy market only a few corporations are capable of spending such an amount of money with pay-back period measured in decades.

Most of fossil fuels are located in limited areas on earth. Extraction and transportation of fossil fuels to other areas is costly and polluting. The depletion of fossil fuel stocks threatens the security and sustainability of future electric energy.

Commercial, environmental and security problems are primary drivers for the growth of distributed generation (DG). Any electric power production technology that is integrated within distribution network can be classified as DG. DG units can either be grid connected or independent of the grid. DG can be categorized into nonrenewable and renewable types. Internal combustion engines, combined cycle engines, combustion turbines, micro turbines and fuel cells are all nonrenewable forms of DG production technologies.

Solar, wind, geothermal and ocean are all renewable forms of DG production technologies. Renewable energy sources are inexhaustible, nonpolluting, diverse in resources and available almost everywhere so they may be the best option for a secure and sustainable energy supply infrastructure. Construction of renewable DG units is fast and cheap compared to central power plants and this choice limits the green house gas (GHG) emissions. The use of local renewable energy sources also eliminates the need for construction of new transmission circuits and large central power plants in some cases. This is not always the case as for large offshore wind farms, it is necessary to have long transmission lines.

DG is a cost effective way to improve the power quality and the reliability of power network. DG can be distributed around distribution network and failure of one unit therefore has limited impact on whole system. However there are still some economical and technical challenges in the integration of DG with distribution power network. Electricity from renewable sources is still generally more expensive than energy from fossil fuel sources, but it may be less expensive if we consider the environmental costs, health costs and energy security costs. The electric energy produced by renewable sources often fluctuates, which can have a bad effect on grid. Therefore there is a need for additional power electronic based interfaces to enable connection. Optimal location of DG units in existing distribution networks is another important issue for active network design. Stability studies were not usually considered in design of existing passive distribution networks because they will remain stable under most conditions assuming that the transmission network is stable [2][3][4][5].

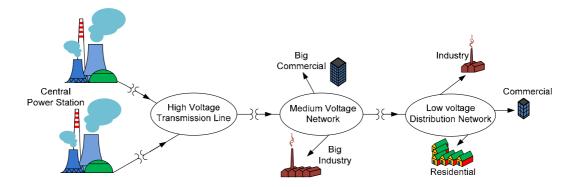

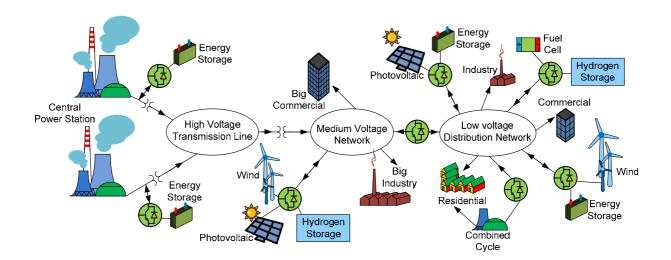

Figure 1.1 shows a diagram of an existing power system. Power flow is unidirectional from source to consumer. In an active network the power flow could be bi-directional. Figure 1.2 shows a possible structure for a future active network. In such a network new integrated active management (AM) schemes, as well as new distribution and protection technologies, are required.

System monitoring, communications and data management will play an important role in future grids. Power electronic converters using fast semiconductor switches and high speed real time controllers are capable of implementing integrated, advanced and complex control algorithms making them a good choice for deployment in a modern distribution system [6][7][8].

Figure 1.1: Existing passive electric power system with unidirectional power flow

The majority of power system problems occur in the distribution network, so it is necessary to make distribution networks smart to achieve a secure electricity supply [9].

One project leading towards the realization of a power electronic based substation is UNIFLEX-PM (Advanced Power Converters for *Universal* and *Flex*ible *P*ower *M*anagement in future electricity network) [10].

Figure 1.2: Next generation active network structure

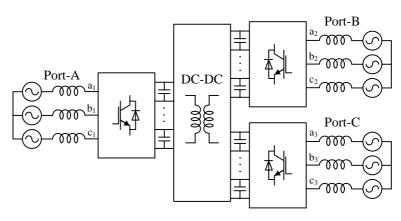

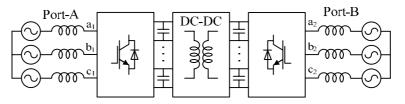

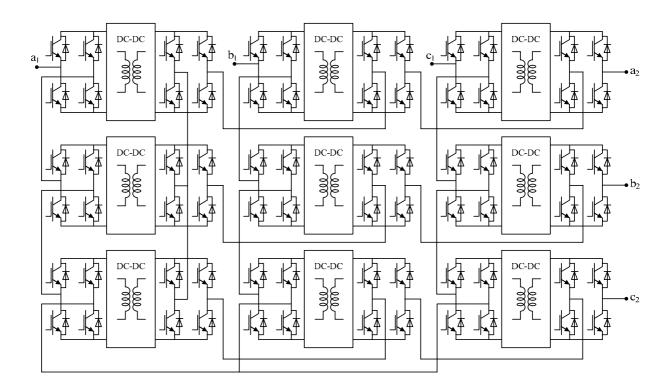

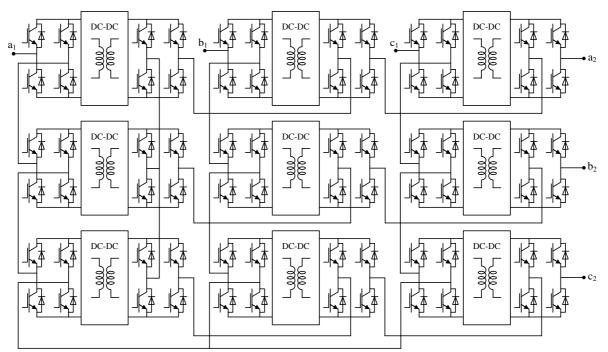

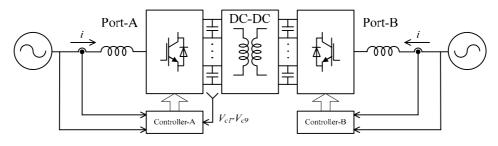

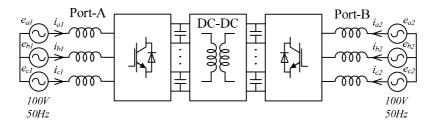

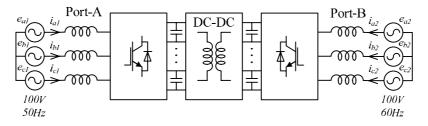

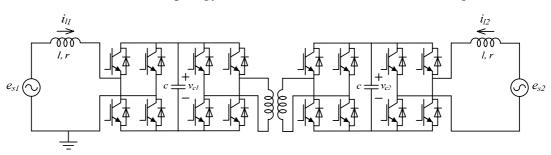

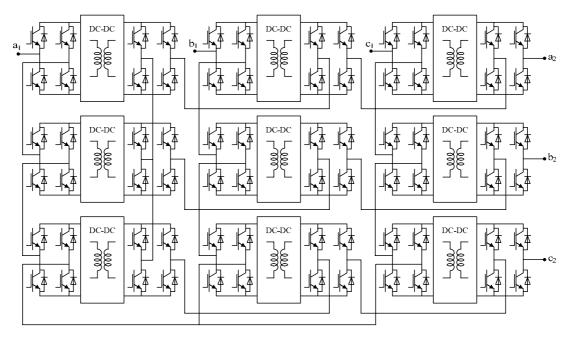

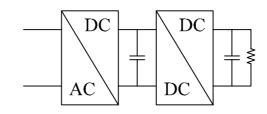

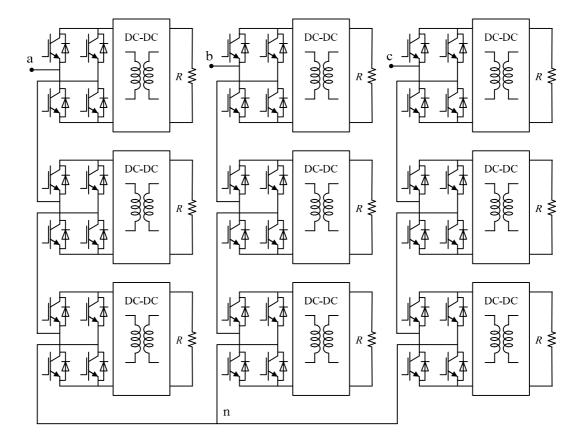

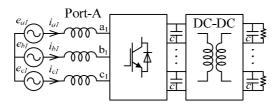

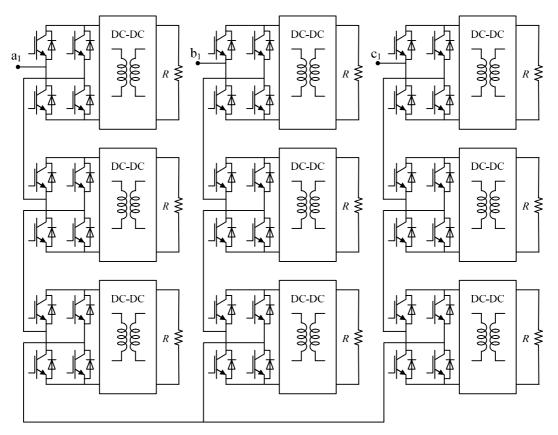

The strategic objective of UNIFLEX-PM is to help to secure clean, economic and sustainable electrical energy. One of the suggested topologies for the UNIFLEX-PM concept is shown in figure 1.3. The objective of the multi-cellular, multilevel power converter is to develop advanced power conversion technique to meet future needs of electricity networks.

The power converter also can assist in the optimized connection of distributed energy sources, integration and management of energy storage, optimized utilization of the transmission and distribution infrastructure, maintaining a high quality of supply and coordinated control across the network. The main characteristics that make this topology a unique choice for power system applications is the modular structure and the interleaved connection between phases at the different ports.

(a): Grid connection of three-port Uniflex-PM converter

(b): Converter topology

Figure 1.3: The 3-port UNIFLEX-PM converter

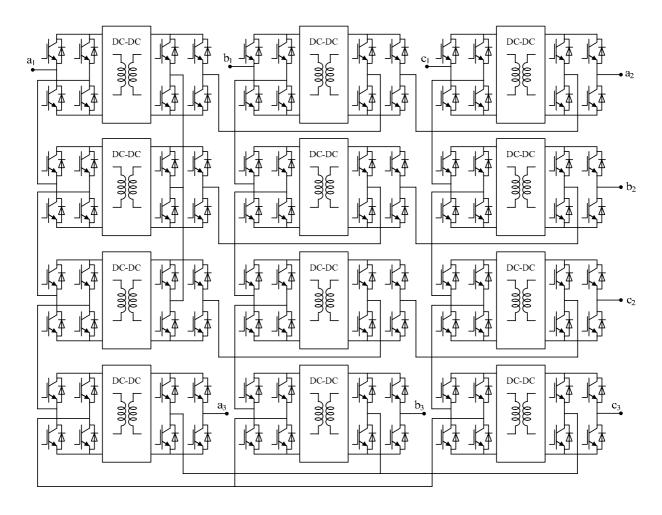

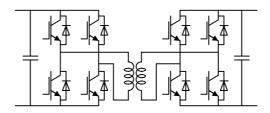

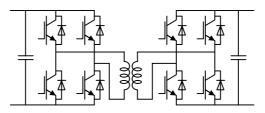

By having an interleaved connection between phases, this converter is able to operate under unbalanced conditions on one port while maintaining balance on the other ports. There are 12 AC-DC-DC-AC modules in the example three-phase three-port structure shown in figure 1.3. The DC-DC converters provide galvanic isolation through a medium frequency transformer. The structure of a DC-DC converter is shown in figure 1.4.

Figure 1.4: The DC-DC converter module

The 3-port power converter structure in figure 1.3 could be capable of providing the following functions in a power network [11]:

- Voltage ratio adjustment

- Frequency changing

- Phase changing

- Asymmetric load current cancellation

- Voltage asymmetry cancellation

- Reactive power control

- Active power control

- Harmonic cancellation

- UPFC like functionality

To achieve any of these functions, a number of control loops are required. These control loops include a current control loop, voltage control loop and capacitor balance loop implemented at port-A, a current control loop implemented at port-B and a current control loop at port-C. To implement the voltage control and capacitor balance loops a knowledge of all DC link voltages are necessary. At port-A in figure1.3 there are 12 capacitors, so 12 voltage transducers are required. Voltage transducers at medium voltage ratings are not easily to

implement and they can be expensive. This thesis presents an observation method for measuring the capacitor voltages to eliminate the need for DC link voltage measurements.

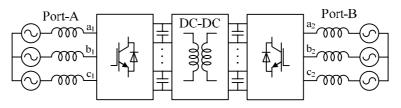

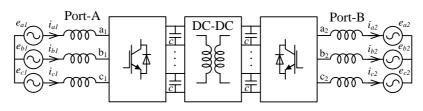

(a) The grid connection

(b) The two-port power converter topology

Figure 1.5: The two-port UNIFLEX-PM converter

#### 1.1 Thesis Objectives

The main objective of this thesis is to choose and practically implement an efficient and robust dc-link voltage observer for the two-port power converter. Several observers including Luenberger Observer, Standard Kalman Filter (SKF), Extended Kalman Filter (EKF), Sliding Mode observer (SMO) and Sliding mode observer using the equivalent control method have been considered to be used in the two-port power converter. The main contribution of this thesis is to address the challenges of the capacitor voltage observation in the two-port power converter that are:

- Complex structure of the power converter doesn't allow having exact mathematical model of the system hence an approximated model of system has been used to construct the observer equations.

- The magnetizing and core loss currents in the medium frequency transformers of the DC-DC converters introduce error in the output current measurements.

- In practical cases the capacitance value are different from the nominal value and there is always uncertainty in capacitance.

- The system observability depends on the power converter switching states. The dclink voltages are observable during a very small fraction of a switching period. The duration of observable states decreases as the number of cascaded H-bridges increases.

Therefore it is necessary to use an observer which is robust to uncertainties in the system model and parameter as well as measurement error. Several papers have been published in the field of dc-link voltage observation in multilevel power converters. An example of the dc-link voltage observation in a multicell power converter has been presented in [68]. The structure of a multicell power converter isn't complex and an exact mathematical model of the system can be used to develop the observer equations. Also there is no transformer in the structure of a multicell inverter to have magnetizing and core loss currents. Therefore in a multicell power converter there is no uncertainty in system model or parameters.

In order to select and implement an efficient observer for power converter, the performance of each type of observer in presence of uncertainty in the system model or parameters should be studied. The Luenberger observer isn't robust to uncertainty in the system model or parameters. The Kalman filter robustness to parameter uncertainty depends on the accurate value of the process and the measurement noise covariance matrices. Incorrect covariance matrices will reduce the robustness to parameter uncertainty and external noise [69]. The practical implementation of Extended Kalman Filter (EKF) involves significant numerical complexity [69]. The traditional sliding mode observer has no robustness to uncertainty in system parameters. The SMO using the equivalent control method is robust against some uncertainty in system model or parameters and it is easy to implement.

In [68] a traditional sliding mode observer has been used for dc-link voltage observation in a multicell inverter as there is no uncertainty in system model or parameters. Obviously traditional SMO would not be a good choice for the two-port power converter. In this thesis a "Sliding Mode Observer (SMO) via Equivalent Control Method" has been chosen and implemented on a two-port configuration, shown in figure 1.5. The selected observer generates precise observer results in presence of model uncertainty introduced by DC-DC converters.

The circuit in figure 1.5 is a subset of the full UNIFLEX-PM topology and has been chosen to demonstrate the functionality of the observer and this will be justified in chapters two and five.

#### 1.2 Thesis plan

Chapter two presents the complete converter design and simulation results. Implementation of voltage and current control loops, as well as the design of the capacitor voltage balancer, is described in this section. The converter modulation technique is also presented. The design of the DC-DC converter and control is explained. Finally simulation results are presented.

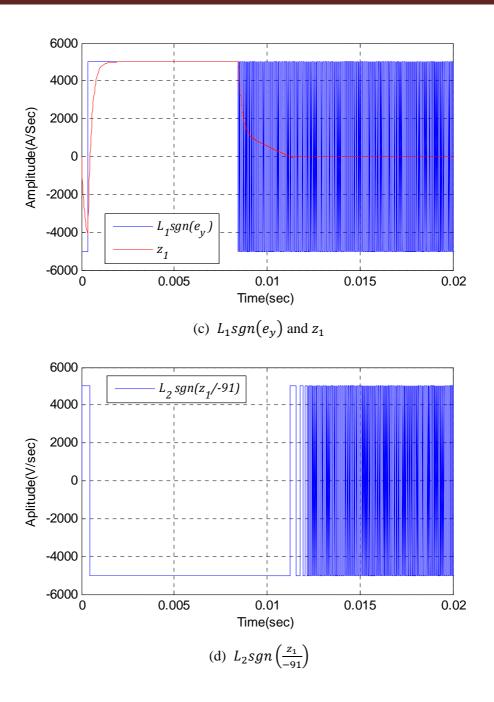

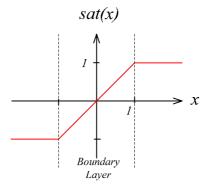

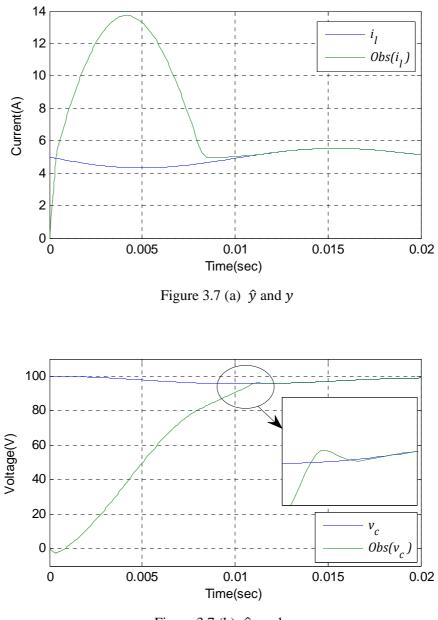

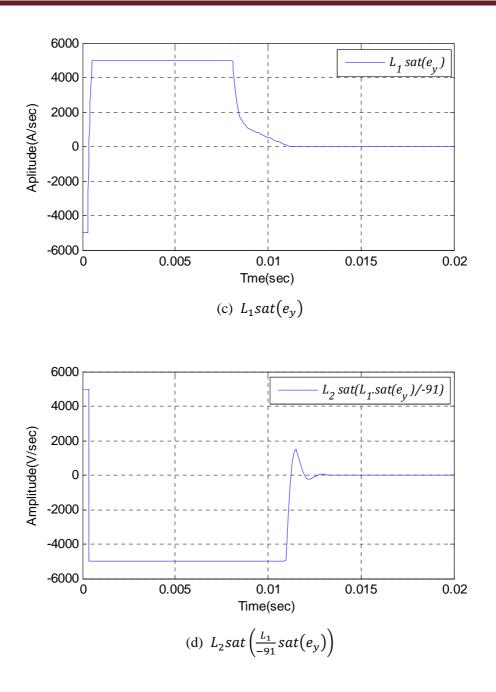

Chapter three presents a theoretical study on sliding mode observers. The sliding mode observer via equivalent control method is introduced. A comparison is made between sliding

mode observers using *sgn()* and *sat()* functions. A stability study is presented on the observer in sliding mode and finally simulation results are presented for the observer operation.

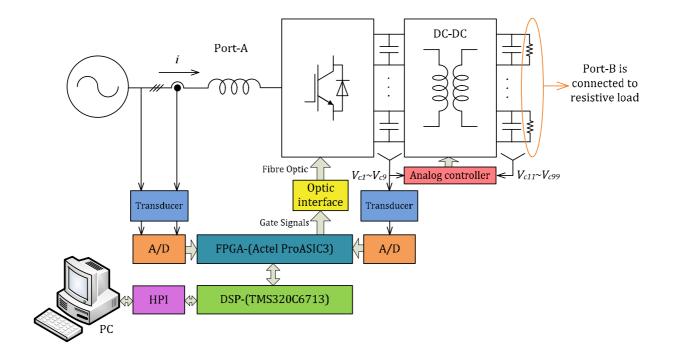

Chapter four presents the simulation results of sliding mode observer applied to the UNIFLEX-PM power converter. The converter observable states are considered and presented based on converter switching states. The effect of DC-DC converters on system and observer equations is examined. Sliding mode observer equations for the two port converter is developed and simulation results are presented.

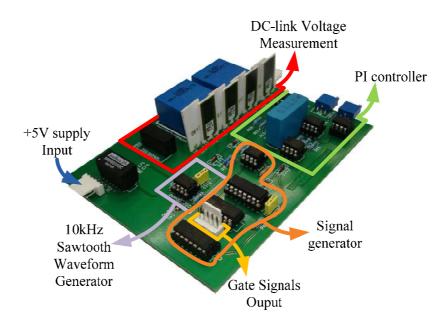

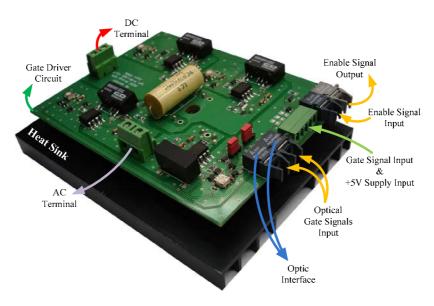

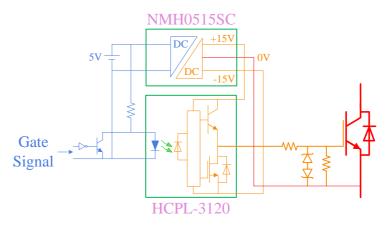

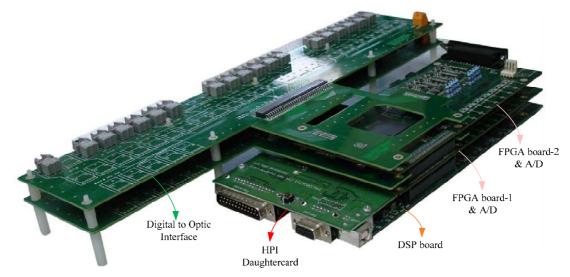

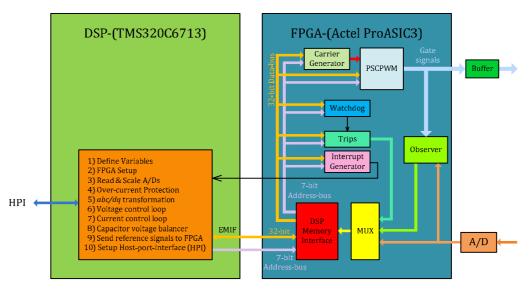

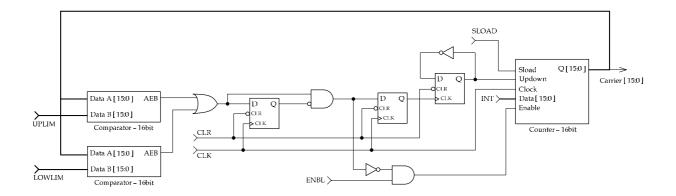

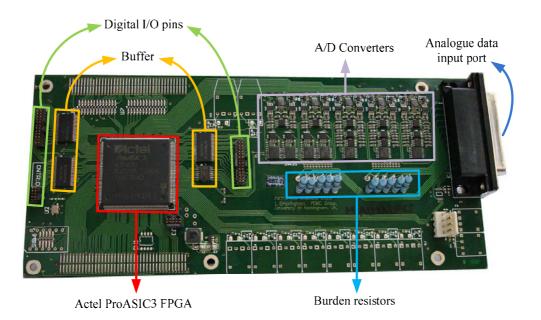

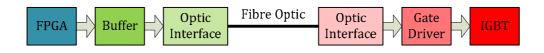

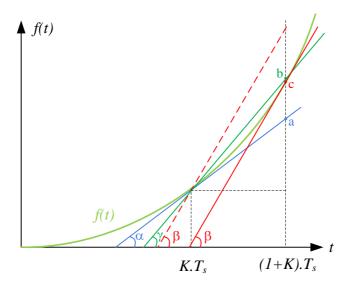

Chapter five describes the experimental power converter and associated control platform. Details of the H-bridge power circuit cards and selected IGBT devices are presented. Design of the high frequency analog controller card for DC-DC converter is also described. Details of the optical interface card used between FPGA and H-bridge cards, as well as voltage and current transducers are presented. The structure of the control platform including the DSP, FPGA and HPI-daughtercard are described. The implementation of the controller and observer equation on DSP and FPGA are presented. Finally the practical results of converters are presented.

Chapter six presents the experimental implementation of the sliding mode observer on power converter. Finally the practical results of power converter DC voltage observation are presented.

Chapter seven presents a conclusion for whole project including the observer design and implementation.

### Chapter 2

# **Converter Design and Simulation**

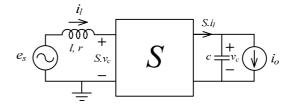

#### 2.1. Introduction

This chapter presents the design and simulation of the converter and associated control for the two-port power converter. The converter modelling and the implementation of the control loops are described. A controller is used to control both active and reactive power flow at the ports of the power converter. PI regulators are used in voltage and current control loops, as well in the control of the capacitor voltage balancers. DQ transformations are used to decouple the system equations. The converter is modulated using a Phase Shifted Cascaded PWM technique. A brief introduction for the DC-DC converter and associated control is also presented. Finally, simulation results for the complete converter are presented.

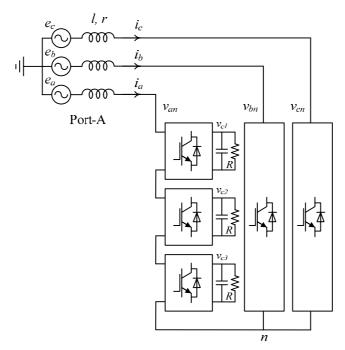

#### 2.2. Power converter structure

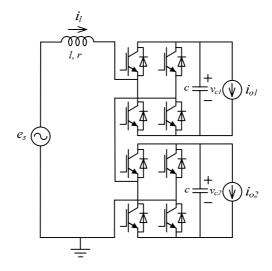

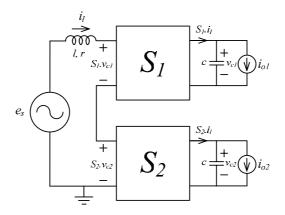

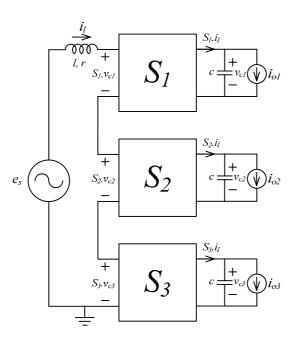

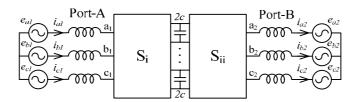

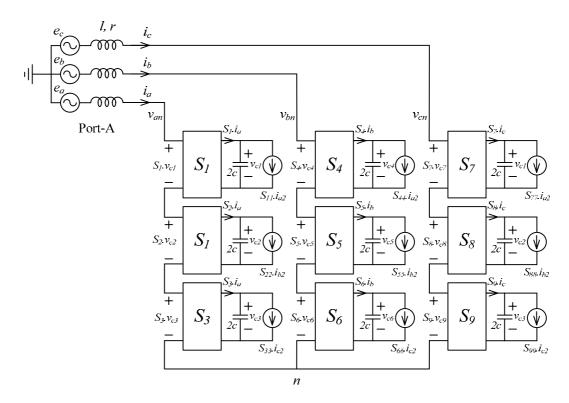

The structure of the two-port power converter is shown in figure 2.1. The main characteristic of this power converter is the modular structure and the interleaved connection between

#### Chapter 2

phases at the different ports. Maintenance and control of modular structure is relatively easy, fast and cost effective. Also, by having an interleaved connection between phases, this converter is able to operate under unbalanced conditions on one port while maintaining balance on the other ports.

(a) The power converter diagram.

b) The two-port power converter topology.

(c) The DC-DC converter topology.

Figure 2.1: The 2-port power converter

Out of the main multilevel power converter structures (Diode-Clamped Inverter, Capacitor-Clamped inverter, Cascaded H-Bridge Inverter and M2C), are the M2C and cascaded H-bridge multilevel converter that have a modular structure [12][13][14][15][64][65][66][67].

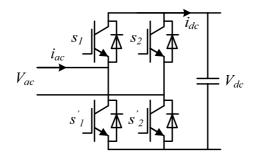

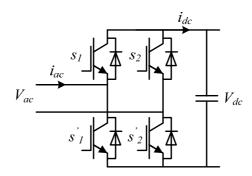

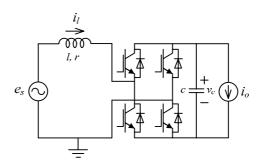

### 2.3. H-Bridge converter

The H-bridge converter topology is shown in figure 2.2. The power flow in an H-bridge converter is bi-directional and the H-bridge converter can be used as both ac-to-dc rectifier and dc-to-ac inverter.

Figure 2.2: The H-Bridge converter

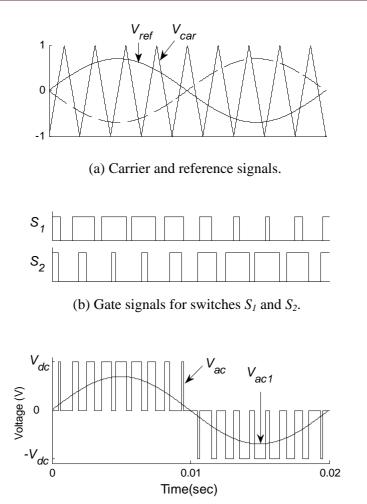

Pulse width modulation (PWM) is one of the most widely used strategies for controlling the AC output of power converters [16]. Both the amplitude and the frequency of AC output can be controlled by PWM technique. The basic naturally sampled PWM technique is based on comparing a reference signal  $V_{ref}$  with a triangular waveform  $V_{car}$ , which is also known as carrier waveform. The PWM strategy with a unipolar voltage switching technique [16][17] is selected as modulation technique for the H-bridge converter in this work. The PWM technique is shown in figure 2.3. Consider the following reference signal:

$$V_{ref} = M\sin(\omega t - \theta) \tag{2.1}$$

Where 0 < M < 1. The switches are controlled by following rule:

| <i>s</i> <sub>1</sub> | <i>s</i> ′ <sub>1</sub> |                     | <i>s</i> <sub>2</sub> | <i>s</i> ′ <sub>2</sub> |                     |

|-----------------------|-------------------------|---------------------|-----------------------|-------------------------|---------------------|

| ON                    | OFF                     | $V_{ref} > V_{car}$ | ON                    | OFF                     | $-V_{ref} > V_{ca}$ |

| OFF                   | ON                      | $V_{ref} < V_{car}$ | OFF                   | ON                      | $-V_{ref} < V_{ca}$ |

(c) H-bridge output voltage  $V_{ac}$  and its fundamental component  $V_{ac1}$

Figure 2.3: The unipolar voltage switching PWM technique for an H-bridge module.

The amplitude modulation ratio or modulation index is defined as the peak value of  $V_{ref}$  divided by the peak value of the  $V_{car}$ . If the peak value of  $V_{car}$  is set to 1 then:

Modulation Index

$$= \frac{M}{1} = M$$

(2.2)

Where *M* is the peak value of  $V_{ref}$ . Figure 2.3 (c) shows the  $V_{ac}$  waveform and its fundamental-frequency component  $V_{ac1}$ . The relation between fundamental-frequency component  $V_{ac1}$  and dc-link voltage  $V_{dc}$  is:

$$V_{ac1} = V_{ref} \times V_{dc} = M. V_{dc} \sin(\omega t - \theta)$$

(2.3)

equation 2.3 described the relation between the AC and DC side voltages. In order to find the relation between the AC and DC sides currents it is assumed that the AC side current is sinusoidal:

$$i_{ac} = I_m \sin(\omega t) \tag{2.4}$$

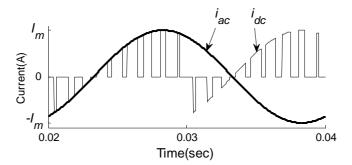

Figure 2.4 presents the AC current  $i_{ac}$  and the DC current  $i_{dc}$ .

Figure 2.4: The  $i_{ac}$  and  $i_{dc}$  current waveforms.

The input power into an ideal, lossless converter is equal to the output power, therefore:

$$V_{dc} \times i_{dc} = V_{ac} \times i_{ac} \tag{2.5}$$

In order to simplify the calculations, all the harmonic components of  $i_{dc}$  and  $V_{ac}$  are neglected.  $V_{ac1}$  is the fundamental-frequency component of ac voltage  $V_{ac}$ . Combining equations 2.3 and 2.4 with equation 2.5 gives:

$$V_{dc} \times i_{dc1} = V_{ac1} \times i_{ac}$$

=  $M.V_{dc} \sin(\omega t - \theta) \times I_m \sin(\omega t)$

=  $\frac{M.V_{dc}.I_m}{2} \times (\cos \theta - \cos(2\omega t - \theta))$  (2.6)

$i_{dc1}$  is the dc current  $i_{dc}$  without harmonics and can be calculated as:

$$i_{dc1} = \frac{M.I_m}{2} \times (\cos\theta - \cos(2\omega t - \theta))$$

(2.7)

Chapter 2

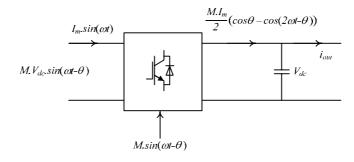

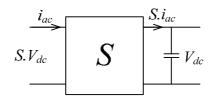

The average model of H-bridge converter has been constructed using equations 2.1 to 2.7 and is shown in figure 2.5.

Figure 2.5: The average model of H-bridge converter.

The ac voltage and dc current are controlled by modulation index. The dc current has an average value and a sinusoidal component with double line frequency. The ac voltage fundamental component is equal to reference modulation signal multiplied by dc-link voltage.

#### 2.4. Phase-Shifted Cascaded PWM

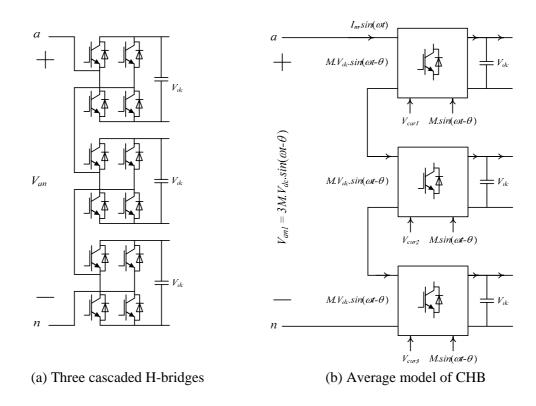

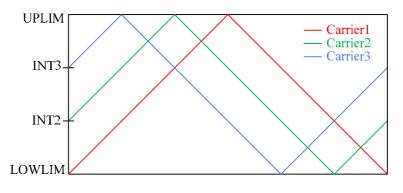

The phase-shifted cascaded PWM (PSCPWM) technique is one of modulation strategies used for cascaded multilevel converters. The multilevel cascaded H-bridge converter comprises of a series of connected single H-bridge converters. The PWM modulation technique for a single H-bridge converter is explained in the previous section. In the PSCPWM technique the same reference signal is applied to all the H-bridges and the carrier signal of each H-bridge is phase shifted by  $\pi/N$  where N is the number of cascaded H-bridges in the chain. It has been shown that optimum harmonic cancellation in the generated waveform can be achieved by phase shifting carrier signals by  $\pi/N$  radians [16]. The structure of a three cascaded H-bridges is shown in figure 2.6(a) and the average model is shown in figure 2.6(b).

Figure 2.6: The cascaded H-bridge converter structure

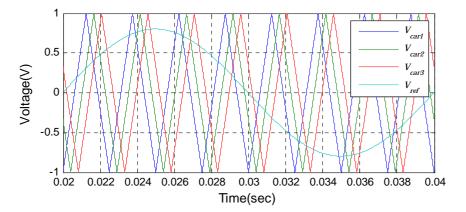

The multilevel converter ac voltage is equal to sum of ac voltage produced by each H-bridge. Figure 2.7 presents the output AC voltage and the carrier signals for three cascaded H-bridge converter which phase shifted by  $\pi/3$  radians.

Figure 2.7: The phase shifted cascaded PWM technique for multilevel converters

The output ac voltage  $V_{an}$  can be a 7-level voltage and the fundamental component is:

$$V_{an1} = 3M. V_{dc} \sin(\omega t - \theta)$$

(2.8)

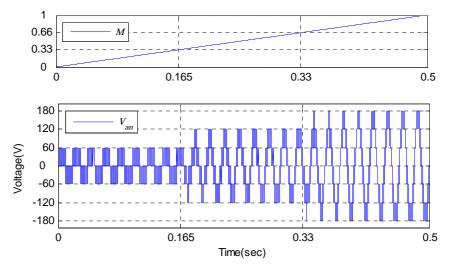

Where  $V_{dc}$  is the DC-link voltage and  $M.\sin(\omega t - \theta)$  is the modulation reference signal. In an N cascaded H-bridges, the AC voltage levels can be up to (2N + 1) levels depending on the modulation index M. Figure 2.8 shows the output ac voltage variation with modulation index.

Figure 2.8: The ac voltage variation in PSCPWM technique with Modulation index

In a three cascaded H-bridges the ac voltage is three level for 0 < M < 0.33, five level for 0.33 < M < 0.66 and seven level for 0.66 < M < 1.

#### 2.5. Converter modeling and design

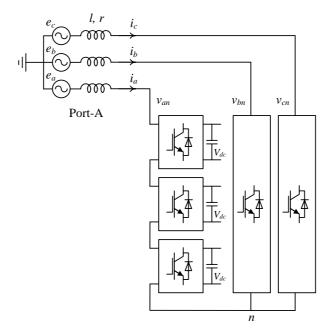

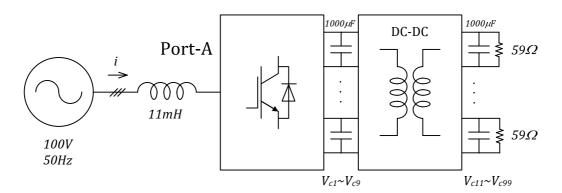

In this section the important equation for converter design has been derived. The prototype converter design and details are presented in chapter 5. It is assumed that the system operates under unity power factor condition. System rated power and voltage are two important factors in converter design. The grid connection of 2-port converter at port-A is shown in figure 2.9. The system rated power is P = 1kW and the supply voltage peak value is  $V_m = 100V$ . The supply frequency is 50Hz. The rated line current peak value  $I_m$  can be calculated as:

$$I_m = \frac{2P}{3V_m} = \frac{2 \times 1000}{3 \times 100} = 6.7A \tag{2.9}$$

The first step is to calculate the DC-link voltages. The relation between total dc-link voltage and source voltage is [17]:

$$total(V_{dc}) > \sqrt{2} V_m \tag{2.10}$$

There are three dc-link voltages in each phase, therefore:

$$V_{dc} > \frac{\sqrt{2} V_m}{3} \tag{2.11}$$

Figure 2.9: The grid connection of 2-port converter at port-A

The dc-link voltage  $V_{dc}$  is set to 60V. Consider the phase-A voltage and current as:

$$e_a = V_m \sin(\omega t) \tag{2.12}$$

$$i_a = I_m \sin(\omega t) \tag{2.13}$$

$$V_{an} = 3M. V_{dc} \sin(\omega t - \theta)$$

(2.14)

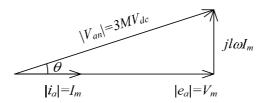

Where  $V_m$  is the supply peak amplitude,  $I_m$  is the line current peak amplitude,  $V_{dc}$  is the DClink voltage and M is the modulation index. Therefore the phasor-diagram of system operating under unity power factor condition will be:

Figure 2.10: Phase-A phasor-diagram of power converter

The relation between the peak values of the source voltage, line current and converter voltage is:

$$(V_m)^2 + (l\omega I_m)^2 = (3MV_{dc})^2$$

(2.15)

Where  $\omega$  is the supply angular frequency. The linear range for *M* in PSCPWM technique is 0 < M < 1 however the minimum operating *M* for this example occurs when line current is zero.

$$M_{min} = \frac{V_m}{3V_{dc}} = \frac{100}{3 \times 60} = 0.55 \tag{2.16}$$

The maximum modulation index is 1 and it is desirable to place the nominal modulation index in the middle, therefore the nominal modulation index can be taken as M = 0.77. The line inductance for this operating point can be calculates as:

$$l = \frac{\sqrt{(3MV_{dc})^2 - (V_m)^2}}{\omega I_m} = \frac{\sqrt{(3 \times 0.77 \times 60)^2 - (100)^2}}{100\pi \times 6.7} = 45.6mH$$

(2.17)

The available line inductance in the lab is 11mH and also it is large enough to filter the line current harmonics. The nominal modulation index for a 11mH inductance can be calculated as:

$$M = \frac{\sqrt{(V_m)^2 + (l\omega I_m)^2}}{3V_{dc}} = \frac{\sqrt{(100)^2 + (0.011 \times 100\pi \times 6.7)^2}}{3 \times 60} = 0.57$$

(2.18)

The dc-link capacitance is designed in such a way to result in a reasonable DC-link voltage ripple. The dc-link input current is given in equation 2.7. It is assumed that the output current  $i_{out}$  is a constant dc current. During steady state the average value of input current will be

equal to output current and the sinusoidal component of input current causes capacitor voltage ripple. The capacitor equation during steady-state is:

$$c\frac{dV_{dc}}{dt} = \frac{M.I_m}{2}\cos(2\omega t - \theta)$$

(2.19)

The peak value of capacitor voltage ripple can be calculated as:

$$(\Delta V_{dc})_{peak} = \frac{M.I_m}{4c\omega}$$

(2.20)

For this example a  $1000\mu f$  capacitor at nominal operating condition will give a 3V peak capacitor voltage ripple.

$$(\Delta V_{dc})_{peak} = \frac{0.57 \times 6.7}{4 \times 0.001 \times 100\pi} = 3V$$

(2.21)

$$\%(\Delta V_{dc})_{peak} = \frac{(\Delta V_{dc})_{peak}}{V_{dc}} = \frac{3}{60} = 5\%$$

(2.22)

The dc-link voltage ripple is 5% and is less than maximum limit.

### 2.6. Control loops modeling and design

The power converter diagram considered in this investigation and associated controllers at each port are shown in figure 2.11. Active and reactive power flow controllers can be used for each port of power converter and can be operate independently.

Figure 2.11: The power converter diagram with grid connection.

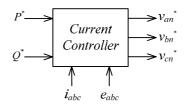

The active and reactive power flow can be controlled by controlling the line currents. The line current can be controlled by converter voltages. Therefore the current control loop should generate references for converter voltages. The diagram of current controller is shown in figure 2.12.

Figure 2.12: Current controller

The demanded active and reactive powers are the reference values for current controller. The supply voltage and line current are the feedback signals. The current controller output is the references for converter voltages. Based on the reference converter voltages the PSCPWM generates reference modulating signals for H-bridges. The current controller design process is described in detail in section 2.6.1.

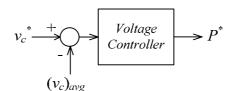

The objective of active power flow controller at port-A is to maintain dc voltages of all the capacitors at a specified, fixed value. The dc-link voltages are controlled by active power flow between supply and converter. Therefore voltage controller should generate reference for active power in order to maintain average dc-link voltages at a reference value. Figure 2.13 shows the diagram of voltage controller.

Figure 2.13: Voltage controller

The voltage controller output is the reference for port-A active power. The design details are explained in section 2.6.2.

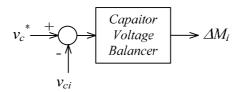

The dc-link voltage of each H-bridge in multilevel converter would diverge under any unbalance conditions in network. In order to equalize all dc-link voltages a capacitor voltage balancer can be used at port-A. As explained in section 2.3, each individual capacitor voltage can be controlled by the average value of current flowing into the capacitor. The dc current in each H-bridge converter is described by equation 2.7. The average value of dc current is proportional to the modulation index and line current amplitude. The capacitor voltage balancer generates modified modulation index for each H-bridge converter. Figure 2.14 shows the capacitor voltage balancer.

Figure 2.14: Capacitor voltage balancer

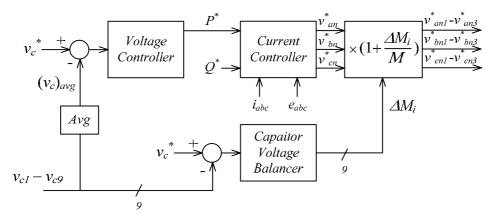

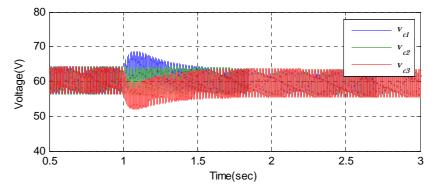

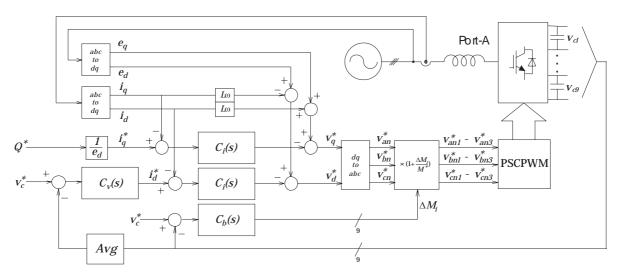

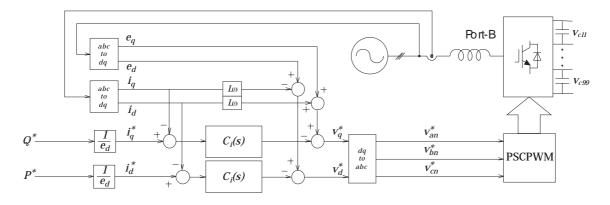

The controller at port-A comprises of a voltage control loop, a current control loop and a capacitor voltage balancer. At port-B there is only a current control loop to deliver the demanded active and reactive power to the network. Figure 2.15 shows the port-A controller structure.

Figure 2.15: Port-A controller.

Signals  $v_{an1}^* - v_{an3}^*$ ,  $v_{bn1}^* - v_{bn3}^*$  and  $v_{cn1}^* - v_{cn3}^*$  are used by PSCPWM to generated reference modulating signals for three H-bridges in phase-A, phase-B and phase-C respectively. Three mathematical models are developed for current control loop, voltage

control loop and capacitor voltage balancer. PI regulators are used in the control loops and are tuned using the MATLAB sisotool GUI [18]. The modelling and design of each controller is described in the following sections.

#### 2.6.1. The current control loop

The objective of the current control loop is to set the amplitude and phase of three-phase line currents to reference values. The current control loop should generate references for  $v_{an}$ ,  $v_{bn}$  and  $v_{cn}$  in order to achieve these desired line currents. A mathematical model of the circuit in figure 2.9 is used to design the current loop. The voltage equations for the three-phase system are:

$$[e]_{abc} = (r+ls)[i]_{abc} + [v]_{abc} + [v_n]$$

(2.23)

With:

$$[e]_{abc} = \begin{bmatrix} e_a \\ e_b \\ e_c \end{bmatrix} \qquad [v]_{abc} = \begin{bmatrix} v_{an} \\ v_{bn} \\ v_{cn} \end{bmatrix} \qquad [i]_{abc} = \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} \qquad [v_n] = \begin{bmatrix} v_n \\ v_n \\ v_n \end{bmatrix}$$

(2.24)

Where r is the line resistance. If the three-phase supply is balanced and free from harmonic then the voltage of point n will be:

$$v_n = \frac{-(v_{an} + v_{bn} + v_{cn})}{3} \tag{2.25}$$

Replacing the  $v_n$  in equation 2.23 will result in following equation in matrix form:

$$[e]_{abc} = (r+ls)[i]_{abc} + [B][v]_{abc}$$

(2.26)

Where:

$$[B] = \begin{bmatrix} \frac{2}{3} & \frac{-1}{3} & \frac{-1}{3} \\ \frac{-1}{3} & \frac{2}{3} & \frac{-1}{3} \\ \frac{-1}{3} & \frac{-1}{3} & \frac{2}{3} \end{bmatrix}$$

(2.27)

Equation 2.26 contains ac variables that are not decoupled. It is much easier to analyze a decoupled system with dc variables. Applying  $\alpha\beta$  and dq transformations to equation 2.26 will result in a decoupled system equation with dc variables [19][20]. The  $\alpha\beta$  and dq transformations are explained below [21][22][23]. Consider a balanced three-phase voltage source defined by:

$$e_a = V_m \cos(\omega_e t) \tag{2.28-a}$$

$$e_b = V_m \cos(\omega_e t - 120^\circ) \tag{2.28-b}$$

$$e_c = V_m \cos(\omega_e t - 240^\circ) \tag{2.28-c}$$

Where  $\omega_e$  is the supply angular frequency. These voltage waveforms can be transformed into  $\alpha - \beta$  coordinates as follows [21]:

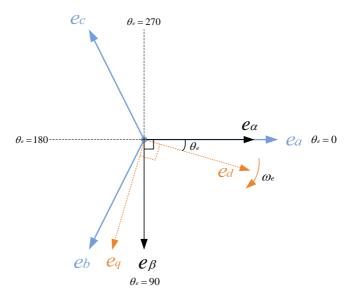

These voltages can be defined in a new reference frame which is rotating at the same speed as the AC supply frequency. Figure 2.16 shows the  $\alpha - \beta$  voltages in this rotating reference frame.

Figure 2.16: Stationary and rotating reference frames

The instantaneous angle between rotating voltages and  $\alpha$  axis is:

$$\theta_{e} = \tan^{-1} \left( \frac{e_{\beta}}{e_{\alpha}} \right)$$

$$= \tan^{-1} \left( \frac{\sin(\omega_{e}t)}{\cos(\omega_{e}t)} \right)$$

$$= \tan^{-1}(\tan(\omega_{e}t))$$

$$= \omega_{e}t \qquad (2.30)$$

The projection of  $e_{\alpha}$ ,  $e_{\beta}$  onto the rotating reference frame will result in new imaginary variables  $e_d$ ,  $e_q$ . The relation between  $[e]_{abc}$  and  $[e]_{dq0}$  coordinates is:

$$[e]_{dq0} = T[e]_{abc} = \begin{bmatrix} \sqrt{3/2} V_m \\ 0 \\ 0 \end{bmatrix}$$

(2.31)

Where

$$T = (T^{-1})^T = \sqrt{\frac{2}{3}} \times \begin{bmatrix} \cos \theta_e & \cos \left(\theta_e - \frac{2\pi}{3}\right) & \cos \left(\theta_e + \frac{2\pi}{3}\right) \\ \sin \theta_e & \sin \left(\theta_e - \frac{2\pi}{3}\right) & \sin \left(\theta_e + \frac{2\pi}{3}\right) \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}$$

(2.32)

The three phase currents can be transformed to rotating reference frame.

$$[i]_{dq0} = T[i]_{abc} (2.33)$$

Application of dq transformation from equation 2.26, results in equation 2.34.

$$T^{-1}[e]_{dq0} = (r+ls)T^{-1}[i]_{dq0} + [B]T^{-1}[v]_{dq0}$$

(2.34)

The simplified form of equation 2.34 in the dq rotating reference frame is presented in equations 2.35 and 2.36.

$$e_d = v_d + r.\,i_d + l\frac{d}{dt}i_d + l.\,\omega_e.\,i_q \tag{2.35}$$

$$0 = v_q + r.i_q + l\frac{d}{dt}i_q - l.\omega_e.i_d$$

(2.36)

The  $i_d$  and  $i_q$  are decoupled and can be controlled independently. Rearranging the above equations results in:

$$i_d = \frac{v_d - (e_d - l.\,\omega_e.\,i_q)}{-(r + ls)}$$

(2.37)

$$i_q = \frac{v_q - (e_q + l.\,\omega_e.\,i_d)}{-(r + ls)}$$

(2.38)

The current control loop should generate reference for  $v_d$  and  $v_q$  in order to control  $i_d$  and  $i_q$  to the desired value.

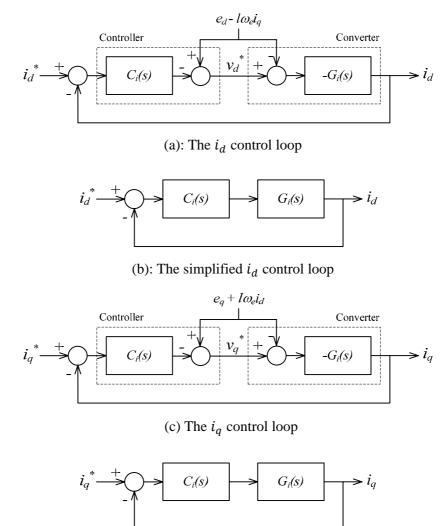

(d) The simplified  $i_q$  control loop

Figure 2.17: Current control loops

The plant dynamic  $G_i(s)$  for current control loop is:

$$G_i(s) = \frac{1}{(ls+r)}$$

(2.39)

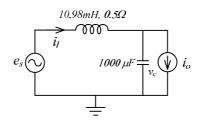

The current control loops are shown in figure 2.17. The plant  $G_i(s)$  can be controlled by a PI controller. The root locus design method can be used to design the PI controller [24]. The maximum speed of current control loop is limited because of line inductor saturation. The speed of inductor current change depends on the voltage across the inductor. A fast current control loop, applies a big voltage on inductor, which may saturates the line inductor. Therefore a bandwidth of 95*Hz* is chosen for closed loop current control system to avoid any possible saturation of inductor. The current controller has been designed for an example circuit shown in figure 2.9 with the following parameters:

| The peak supply voltage | $V_m$                 | 100V         |

|-------------------------|-----------------------|--------------|

| The peak line current   | <i>I</i> <sub>m</sub> | 6.7 <i>A</i> |

| The DC link voltage     | $V_{dc}$              | 60V          |

| The supply frequency    | f                     | 50 <i>Hz</i> |

| The line resistance     | r                     | 0.5Ω         |

| The line inductance     | l                     | 11 <i>mH</i> |

| The DC-link capacitance | С                     | 1000µF       |

Table 2.1: system parameters

The plant dynamics is:

$$G_i(s) = \frac{1}{(0.011s + 0.5)} \tag{2.40}$$

The designed PI controller transfer function is:

$$C_i(s) = 1160 \left(\frac{0.0037s + 1}{s}\right) \tag{2.41}$$

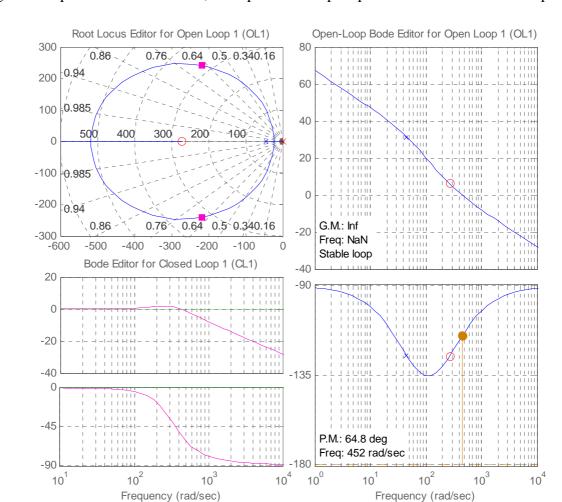

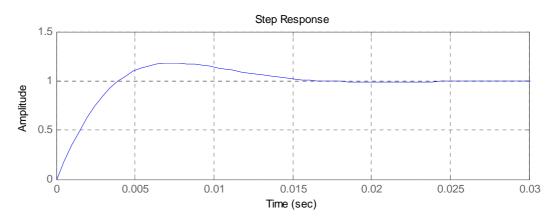

#### Figure 2.18 presents the root locus, bode plots and step response for current control loop.

Chapter 2

Figure 2.18(a): The root locus, bode plots for the current control loop

Figure 2.18(b): The step response for the current control loop

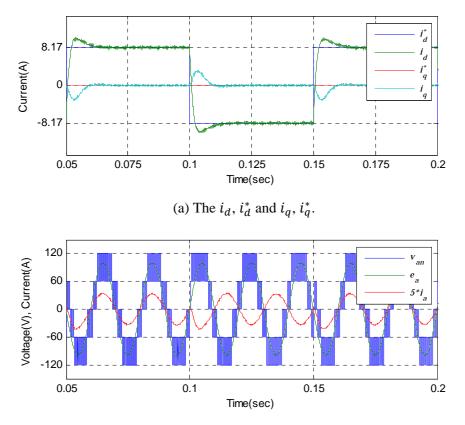

The poles of the closed-loop system are located at  $-217 \pm i241$  and have a natural frequency equal to  $325 \ rad/s$ . The damping ratio is set to be  $\zeta = 0.67$ . The open loop phase margin is 64.8° and gain margin is infinite. The simulation results of current control loops are presented in figure 2.19.

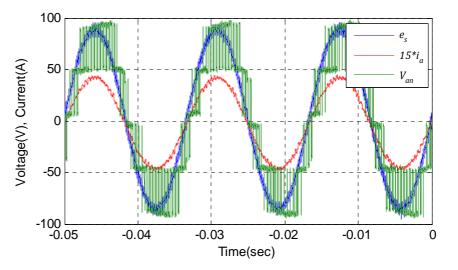

(b) Supply voltage  $e_a$ , line current  $i_a$  and converter voltage  $v_{an}$ .

Figure 2.19: Current control loop simulation results.

It is assumed that the dc-links are connected to constant dc voltage source. The reference and actual values of  $i_d$  and  $i_q$  currents are shown in figure 2.19(a) and supply voltage and current and converter voltage are shown in figure 2.19(b). The Active power flow direction has been changed at t = 50ms, t = 100ms and t = 150ms. During 50ms < t < 100ms the line current and supply voltage are in phase and power flow is from supply to converter and during 100ms < t < 150ms the power flow is from converter to supply. The simulation results confirm that the current control loop is stable in both direction of active power flow. Currents  $i_d$  and  $i_q$  can be controlled independently. The time for full current reversal is as expected and is equal to settling-time of closed-loop step-response.

## 2.6.2. The voltage control loop

The objective of the voltage control loop is to control the amplitude of the average of the DC link voltages. A net active power flow into the power converter will charge the capacitors. The voltage control loop should generate a reference for the active power in order to achieve the desired average of the converter dc-link voltages. The simplified circuit of the 2-port converter shown in figure 2.20 is used to design the voltage control loop. The load that is delivered to port-B is modelled as a resistor R.

Figure 2.20: The simplified model of grid connection of 2-port converter at port-A

As shown in figure 2.1(b) there is nine modules in the 2-port converter. Assuming that all the modules in the power converter are symmetrical and lossless, the net active power supplied to each module will be one-ninth of the total active converter input power as given in equation 2.42.

$$\frac{1}{9}P = v_c(t)i_c(t) + \frac{v_c^2(t)}{R} = v_c\left(Csv_c + \frac{v_c}{R}\right)$$

(2.42)

Where  $P = e_d \cdot i_d$  is the active input power to the converter. Voltage  $e_d$  is constant and active power flow is controlled by  $i_d$ . Rearranging equation 2.42 results in:

Chapter 2

$$\boldsymbol{v}_{c} = \frac{\boldsymbol{e}_{D}}{9\boldsymbol{v}_{c}\left(\boldsymbol{C}\boldsymbol{s} + \frac{1}{R}\right)}\boldsymbol{i}_{D} \tag{2.43}$$

The plant dynamics for voltage control loop is:

$$G_{\nu}(s) = \frac{e_D}{9\nu_c \left(Cs + \frac{1}{R}\right)}$$

(2.44)

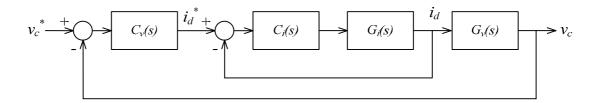

The voltage controller output is a reference for current  $i_d$ . The nested structure of voltage and current control loops is shown in figure 2.21.

Figure 2.21: The nested control loop including voltage control loop and current control loop

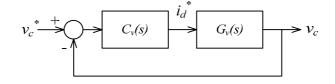

If the voltage controller is significantly slower than current controller, therefore the speed of  $i_d^*$  changes is slow and  $i_d$  can track  $i_D^*$  very closely and it can be assumed that  $i_d$  is identical to  $i_d^*$ . Therefore the block diagram of figure 2.21 can be simplified to figure 2.22.

Figure 2.22: The voltage control loop

The maximum speed of voltage control loop is limited by line current rating. A fast voltage control loop imposes big line current. Also voltage control loop should be much slower than current control loop so the response of the nested loop to a step input be virtually identical to the voltage control loop response alone. For a current control loop with a bandwidth of 95Hz the voltage control loop bandwidth can be 6Hz. The voltage controller has been designed for an example circuit shown in figure 2.20 with the following parameters:

| The peak supply voltage | $V_m$                 | 100V         |

|-------------------------|-----------------------|--------------|

| The peak line current   | <i>I</i> <sub>m</sub> | 6.7 <i>A</i> |

| The DC link voltage     | $V_{dc}$              | 60V          |

| The supply frequency    | f                     | 50 <i>Hz</i> |

| The line resistance     | r                     | 0.5Ω         |

| The line inductance     | l                     | 11 <i>mH</i> |

| The DC-link capacitance | С                     | 1000µF       |

| The load resistance     | R                     | 32Ω          |

|                         |                       |              |

Table 2.3: system parameters

The plant dynamics is:

$$G_{\nu}(s) = \frac{226.5}{(s+31.25)} \tag{2.45}$$

The plant  $G_v(s)$  can be controlled by a PI controller. The root locus design method can be used to design the PI controller. The PI controller transfer function is:

$$C_{\nu}(s) = 5.3 \left(\frac{0.027s + 1}{s}\right) \tag{2.46}$$

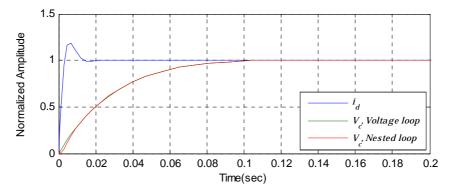

Figure 2.23 shows the step responses of the current, voltage and nested control loops. It can be seen that the response of nested control loop to a step input is virtually identical to the voltage control loop response alone.

Figure 2.23: Step response of the current, voltage and nested control loop.

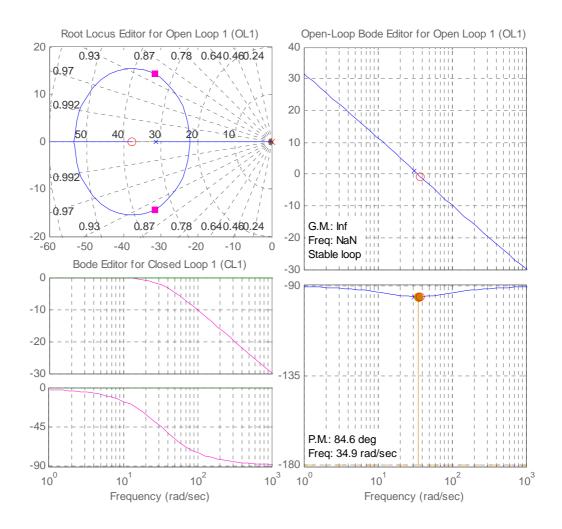

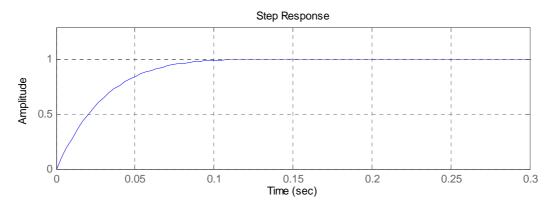

Figure 2.24(a): The root locus, bode plots for the voltage control loop

Figure 2.24(b): The step response for the voltage control loop

The root locus, bode plots and step response for voltage control loop are shown in figure 2.24. The poles of the closed-loop system are located at  $-31.6 \pm i14.3$  and have a natural

frequency equal to 34.6 *rad/s*. The damping ratio is set to  $\zeta = 0.91$ . The open loop phase margin is 34.9° and gain margin is infinite.

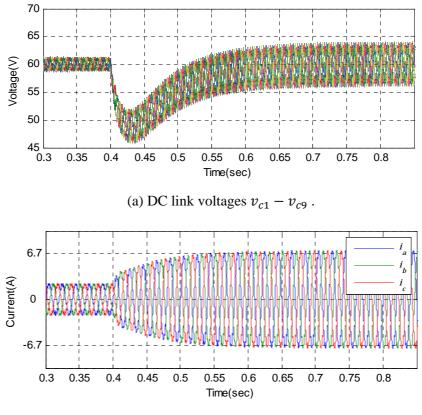

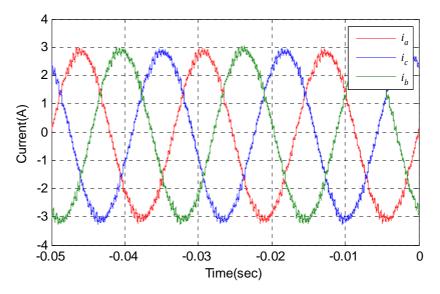

(b) Line currents  $i_a$ ,  $i_b$  and  $i_c$ .

Figure 2.25: Voltage control loop simulation results.

The simulation results are shown in figure 2.25. A step change in load resistance is applied at t = 0.4s. The load resistance is changed from  $100\Omega$  to  $32\Omega$ . Capacitor voltages are shown in figure 2.25(a). Simulation result confirms that voltage control loop is stable. After a step change in load the capacitor voltages converge to reference value in 20ms. There is no steady state error in capacitor voltage values. The line currents are shown in figure 2.25(b). There is no over current situation which means the dynamic of the designed voltage controller is not too fast.

#### 2.6.3. The capacitor voltage balancer

The objective of the capacitor voltage balancer is to equalize all the DC-link voltages in the H-bridges. Under any type of unbalance operating conditions the capacitor voltages would diverge without the capacitor voltage balancer control loop. The capacitor voltage balancer modifies the amplitude modulation ratio M of each cell to control the associated DC link voltage. The average model shown in figure 2.5 is used to design the capacitor voltage balancer voltage balancer loop. The capacitor voltage can be described by:

$$i_{dc} = i_c(t) + \frac{v_c(t)}{R} = Csv_c + \frac{v_c}{R}$$

(2.47)

The  $i_{dc}$  is described by equation 2.7. The average value of  $i_{dc}$  charges the capacitor. Placing the average value of  $i_{dc}$  in equation 2.47 results in:

$$\frac{MI_m}{2}\cos\theta = Csv_c + \frac{v_c}{R}$$

(2.48)

It is assumed that  $\cos \theta$  is close to one. Under unity power factor condition the relation between peak amplitude of line current  $I_m$  and rotating current  $i_d$  is:

$$I_m = \left(\sqrt{2/3}\right) i_d \tag{2.49}$$

Rearranging equation 2.48 and combining with equation 2.49 results:

$$v_c = \frac{1}{\sqrt{6}\left(Cs + \frac{1}{R}\right)} M.i_d \tag{2.50}$$

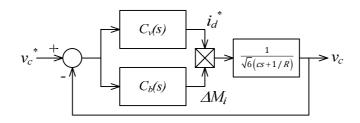

As explained in section 2.6.2, figure 2.22, the reference value for the rotating current  $i_d$  is determined by voltage control loop. Figure 2.26 shows a block diagram of mathematical model of a single H-bridge including voltage controller and capacitor voltage balancer.

Figure 2.26: The model of single H-bridge including voltage controller and capacitor voltage balancer

If the capacitor voltage balancer is significantly slower than voltage control loop therefore current  $i_d$  can be considered as a constant. Based on this assumption and by using equation 2.50 the plant transfer function to design capacitor voltage balancer is:

$$G_b(s) = \frac{i_d}{\sqrt{6}\left(Cs + \frac{1}{R}\right)} \tag{2.51}$$

The capacitor voltage balancer diagram is shown in figure 2.27.

Figure 2.27: The capacitor voltage balancer loop

The plant  $G_b(s)$  can be controlled by a PI controller. The root locus design method can be used to design the PI controller. The dynamic of capacitor voltage balancer should be significantly slower than voltage control loop. For a voltage control loop with a bandwidth of 6Hz the capacitor voltage balancer bandwidth can be 0.5Hz. The plant for capacitor voltage balancer in this example is:

$$G_b(s) = \frac{i_d}{\sqrt{6}\left(Cs + \frac{1}{R}\right)} = \left(\frac{3350}{s + 31.25}\right)$$

(2.52)

The corresponding controller can be designed as:

$$C_b(s) = 0.04 \left(\frac{1+0.1s}{s}\right) \tag{2.53}$$

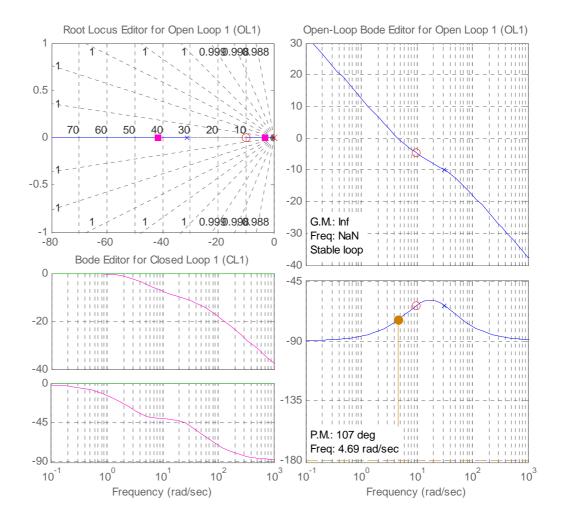

Figure 2.28(a): The root locus, bode plots for the capacitor voltage balancer loop

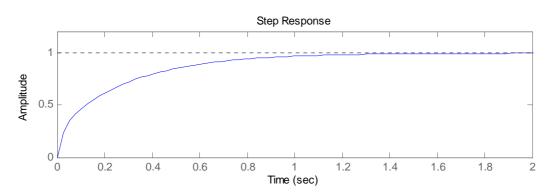

Figure 2.28(b): The step-response for the capacitor voltage balancer loop

The poles of the closed-loop system are located at -41.5 and -3.23. The settling time of step response is 1.2*sec*. The open loop phase margin is  $107^{\circ}$  and gain margin is infinite. The

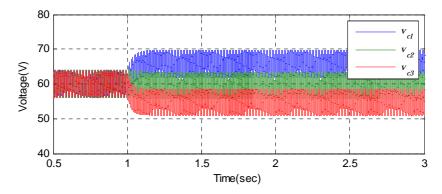

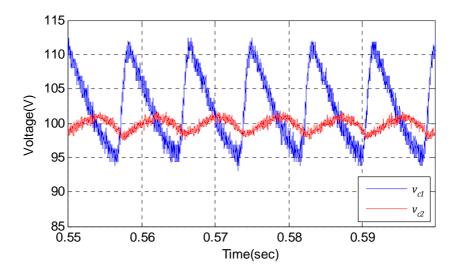

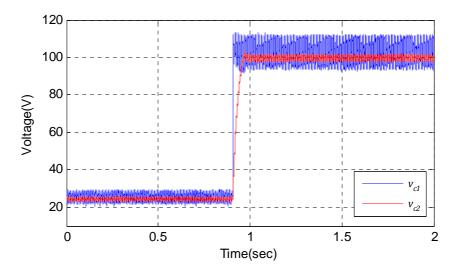

circuit shown in figure 2.20 is used to generate the simulation results for capacitor voltage balancer. The system parameters are listed in table 2.3. Step changes in load resistances  $R_1$  and  $R_3$  are applied at = 1s . The simulation results are presented in figure 2.29. Capacitor voltages  $v_{c1}$ ,  $v_{c2}$  and  $v_{c3}$  without capacitor voltage balancer are shown in figure 2.29(a). Capacitor voltages diverge under unbalanced load condition without balancer.

Figure 2.29 (a): voltage balancer loop (dc-link voltages  $v_{c1}$ ,  $v_{c2}$  and  $v_{c3}$  without balancer loop)

Figure 2.29 (b): voltage balancer loop (dc-link voltages  $v_{c1}$ ,  $v_{c2}$  and  $v_{c3}$  with balancer loop)

Figure 2.29(b) shows the capacitor voltages  $v_{c1}$ ,  $v_{c2}$  and  $v_{c3}$  under unbalanced load condition with capacitor voltage balancer. Simulation result confirms that capacitor voltage balancer is stable. There is no steady state error in capacitor voltage values.

The complete power converter and associated controllers for ports A and B are shown in figure 2.30. At port-A there is a current loop, a voltage loop and nine capacitor voltage balancers. There is only one current control loop for port-B, which controls the active and reactive power.

(a) Port-A controller diagram in detail.

(b) Port-B controller diagram in detail.

Figure 2.30: The complete controller diagram.

The controllers in figure 2.30 are designed under the assumption that the supply at both ports is balanced. The instantaneous angle of the rotating reference frame at each port is calculated using the supply voltage at that port therefore the converter can be connected to supplies with different frequencies and different phase angles. The reference value for the reactive power is set to zero to have unity power factor condition at both ports.

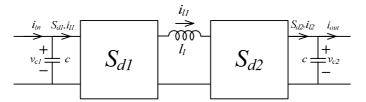

#### 2.7. The DC-DC Converter

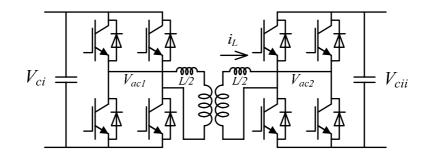

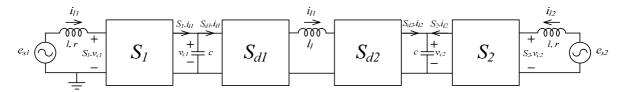

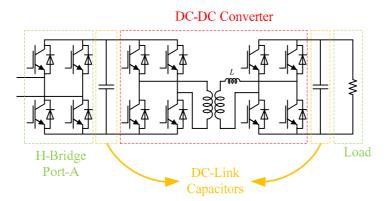

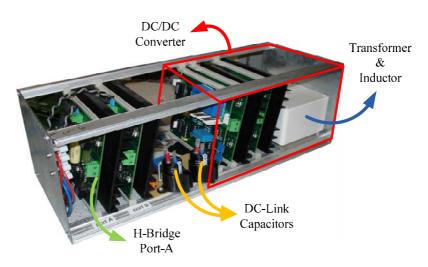

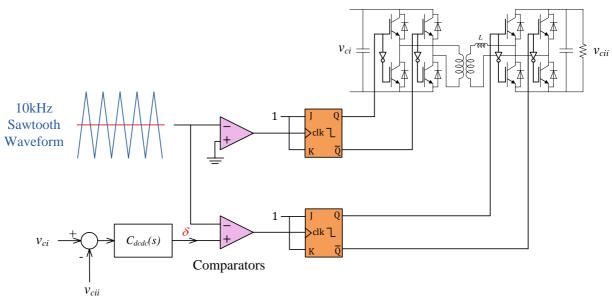

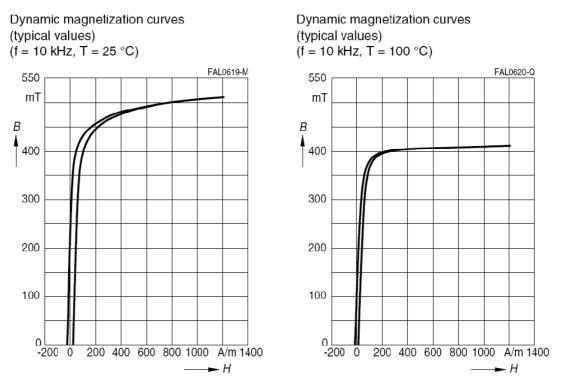

The DC-DC converter is used in the power converter structure to provide galvanic isolation between the H-bridges. The structure of the DC-DC converter is shown in figure 2.31. The DC-DC converter consists of two H-bridge converters and a medium frequency transformer. In this example the DC-DC converter is used to equalize the capacitor voltages  $v_{ci}$  and  $v_{cii}$ . The capacitor voltages are maintained and controlled by active power flow between the input and output of the DC-DC converter. The active power flow is controlled by controlling the phase shift between the square-wave voltages across transformer's leakage inductance *L*. The relation between active power flow and phase shift between the voltages is [25]:

$$P = \frac{v_{ci} \cdot v_{cii}}{\omega L} \left( \delta - \frac{\delta^2}{\pi} \right)$$

(2.54)

Where  $\omega$  is the angular frequency of square-wave voltages and the  $\delta$  is phase shift between the square-wave voltages across the leakage inductance of transformer.

Figure 2.31: The DC-DC converter circuit

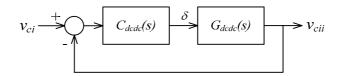

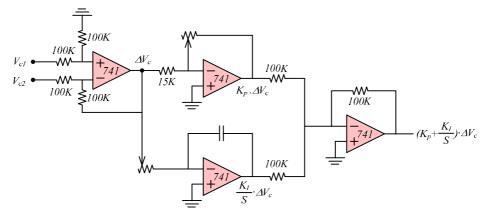

The DC-DC converter control diagram is shown in figure 2.32. The details of DC-DC converter and controller design used in this work can be found in [25].

Figure 2.32: The DC-DC controller diagram

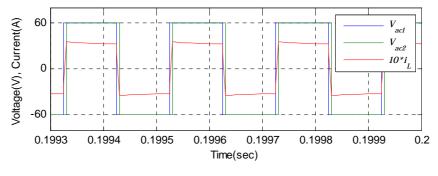

The voltages across transformer terminals and transformer current are shown in figure 2.33.

Figure 2.33: The DC-DC converter waveforms.

In this diagram  $V_{ac2}$  lags  $V_{ac1}$  which means that power flow is from left to right.

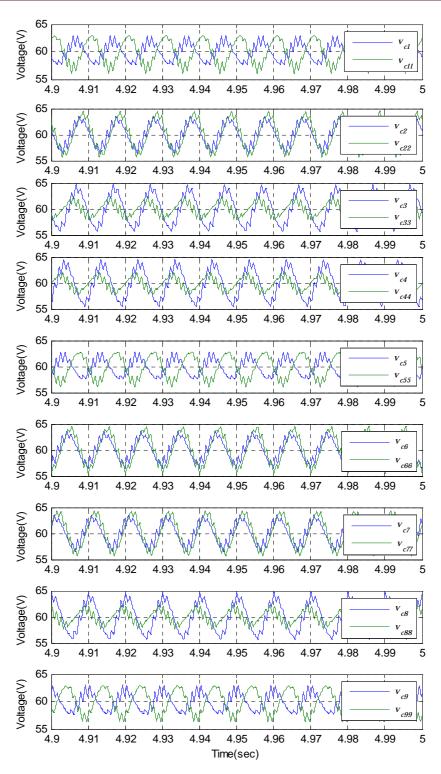

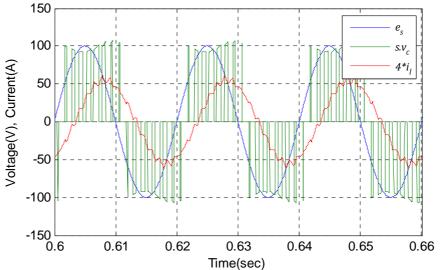

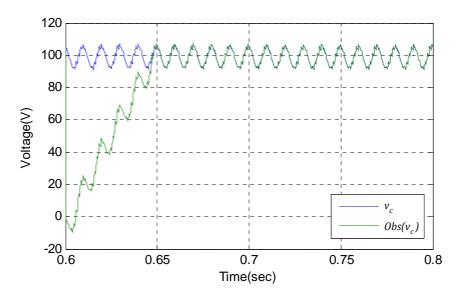

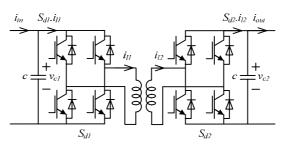

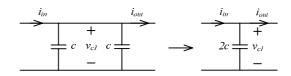

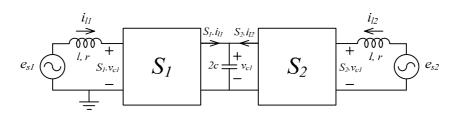

### 2.8. Simulation Results for the 2-Port Power Converter

In a two-port converter there are two capacitors in each module, either side of the DC-DC converters. By neglecting the dynamics of DC-DC converters it can be assumed that the two capacitors in each module will be in parallel and the equivalent capacitance will be doubled. Therefore the dynamics of a two port converter are different from a one-port converter and new voltage control loop and capacitor voltage balancer loop would need to be designed. However the current loop controller  $C_i(s)$  is the same for a two-port and a one-port converter. The PI controller design procedure has been explained in detail in the previous section. Figure 2.34 shows the complete power converter topology used in these simulations. The peak amplitude of the three-phase supply voltages at both ports is taken as 100V with a frequency of 50Hz. The line inductance is 11mH. The DC link capacitance is  $1000\mu F$  and the reference value for the DC link voltages is set to 60V.

Figure 2.34: Complete power converter circuit diagram

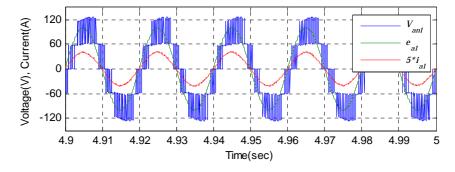

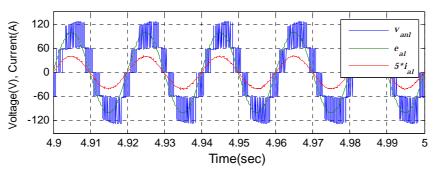

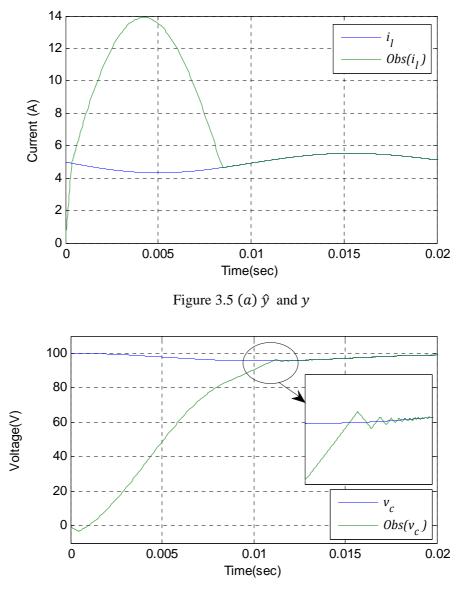

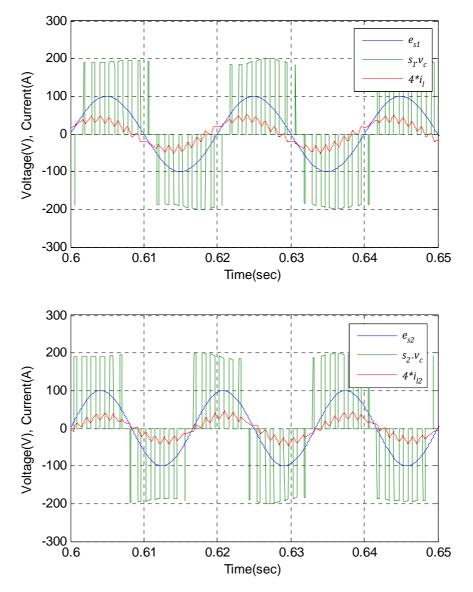

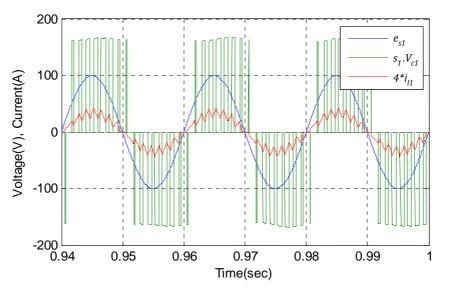

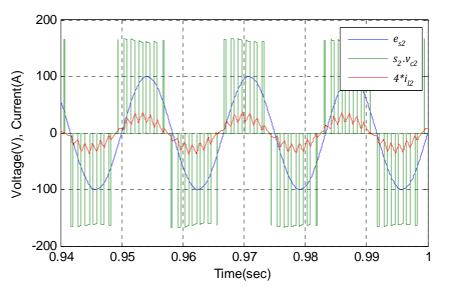

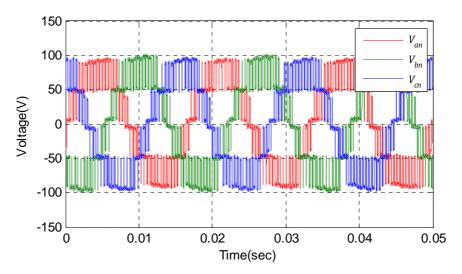

Figure 2.35 shows the simulated waveforms of the ac current and voltages at ports A and B.

(a) Supply voltage  $e_{a1}$ , Converter voltage  $v_{an1}$ , and line current  $i_{a1}$  at phase-a, Port-A.

(b) Supply voltage  $e_{a2}$ , Converter voltage  $v_{an2}$ , and line current  $i_{a2}$  at phase-a, Port-B

Figure 2.35: Two-port converter waveforms.

The line current and supply voltage at port-A are in phase, showing the converter is operating under unity power factor condition. Also converter voltage lags the supply voltage which means port-A is delivering active power to converter. The converter voltage leads the supply voltage at port-B, which means port-B is absorbing active power from power converter. The power-converter is operating under unity power factor conditions at port-B as well.

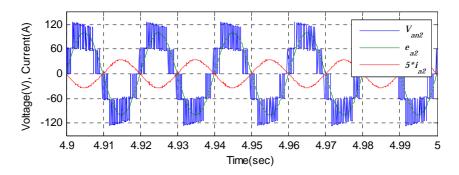

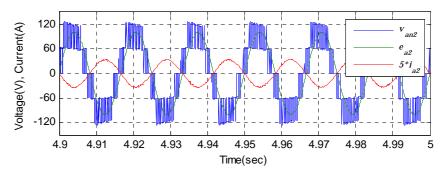

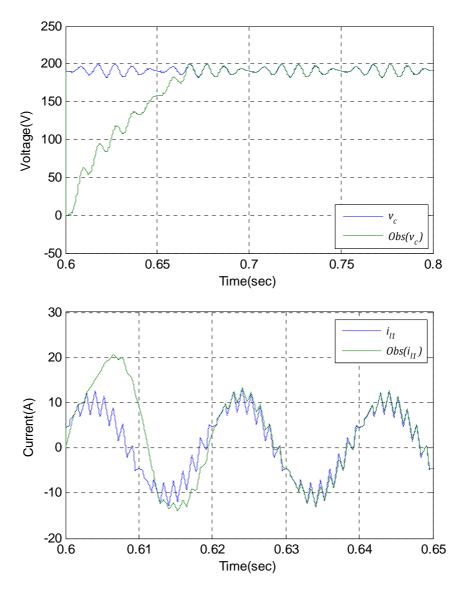

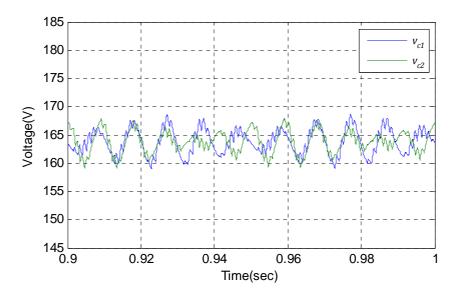

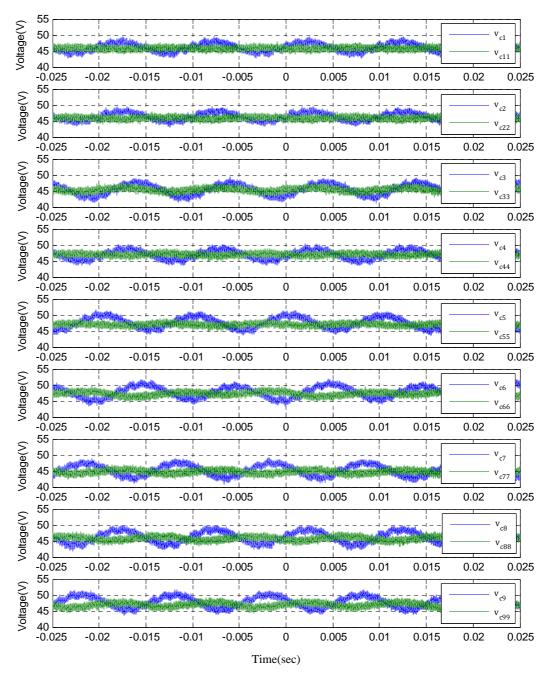

Figure 2.36 shows the capacitor voltages across the DC-DC converters, which is switching at 5*KHz*.

Figure 2.36: DC link voltages across DC-DC converters.

The average values of all capacitor voltages across the DC-DC converters are equal, which confirm the correct operation of DC-DC converter and capacitor voltage balancer.

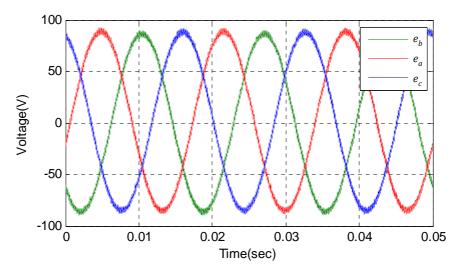

To demonstrate that the frequency of the power converter ports can be different the supply frequency at port-B is changed to 60Hz. Figure 2.37 shows the simulated power converter topology.

Figure 2.37: Complete power converter circuit diagram

Figure 2.38 shows the simulated waveforms for the current and voltage at ports A and B. The power flow is from port-A to port-B under unity power factor conditions.

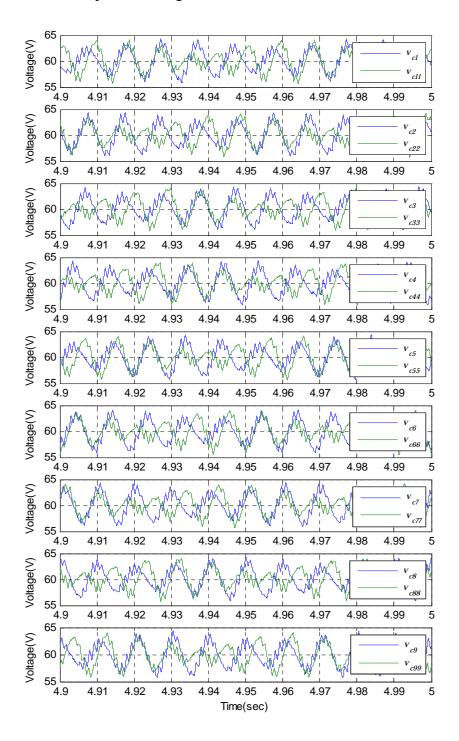

(a) Supply voltage  $e_a$ , Converter voltage  $v_{an}$ , and line current  $i_a$  at phase-a, Port-A at 50Hz.

(b) Supply voltage  $e_a$ , Converter voltage  $v_{an}$ , and line current  $i_a$  at phase-a, Port-B at 60Hz.

Figure 2.38: Two-port converter waveforms.

Simulation results in figure 2.38 confirm the correct operation of power converter while its ports are connected three-phase supplies with different frequencies.

Figure 2.39 shows the capacitor voltages across the DC-DC converters.

Figure 2.39: DC link voltages across DC-DC converters.

The capacitor voltages across each DC-DC converter have different ripple frequencies but the average value of all capacitor voltages are equal, which confirm the correct operation of DC-DC converter and capacitor voltage balancer.

#### 2.9. Summary

In this chapter the design method for the control loops for a multi-cellular two-port power converter has been presented. The *dq* transformation has been used to decouple the system equations for the AC waveforms. Three control models have been presented and used to design the current control loop, voltage control loop and capacitor voltage balancer. Phase-Shifted-Cascaded PWM has been selected and implemented as the power converter modulation technique. A complete control diagram has been presented for ports A and B of the converter. The structure and basic theory of the DC-DC converter has been presented. Finally, simulation results have been presented to show the complete operation of the two-port power converter.

# Chapter 3

## Sliding Mode Observers

### 3.1 Introduction

This chapter presents a review of sliding mode observers. First a history of the invention of observers is presented. Then a background of the variable structure system is given. The structure of the traditional sliding mode observer and the sliding mode observer using an equivalent control method are described. Finally, simulation results for the sliding mode observer using the equivalent control method are presented and discussed. The Luenberger observer and traditional SMO aren't robust to uncertainty in system model or parameters. The "SMO using the equivalent control method" has robustness to system parameter uncertainty. Therefore "SMO using the equivalent control method" has been selected to be applied to power converter.

### 3.2 History of observer

The idea of using a dynamic system, called an observer, to estimate system state vectors was introduced by Luenberger in 1964 [26][27][28] and further developed by him later in 1966

[29]. In many control system designs it is assumed that the system state vectors are available by direct measurement, however this is not the case in many practical cases. Application of theories like state feedback controllers, which assume that the state vectors are known, is limited in these cases. An observer generates an estimate of the system state vectors. The observer uses information from the input and output variables of the original system to estimate the system states [29]. The estimation of the system state variables can be used instead of the real state variables in feedback loops without loss of system stability. Consider a dynamic system defined by:

$$\begin{cases} \dot{x} = Ax + Bu\\ y = Cx \end{cases}$$

(3.1)

Where  $x \in \mathbb{R}^n$ ,  $u \in \mathbb{R}^p$ ,  $y \in \mathbb{R}^m$  and  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times p}$ ,  $C \in \mathbb{R}^{m \times n}$  are constant matrices. The mathematical model of the Luenberger observer will be [24]:

$$\begin{cases} \hat{x} = A\hat{x} + L(\hat{y} - y) + Bu\\ \hat{y} = C\hat{x} \end{cases}$$

(3.2)

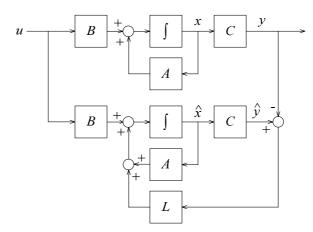

Where  $\hat{x}$  is the estimation of system state vector,  $\hat{y}$  is the estimation of the system output and L is the observer gain matrix. Figure 3.1 shows the diagram of a system and associated Luenberger observer.

Figure 3.1: Luenberger observer diagram

Subtracting equation 3.2 from equation 3.1 will give the dynamics of the error vector  $e_x$ :

$$\begin{cases} \dot{e_x} = Ae_x + Le_y \\ e_y = Ce_x \end{cases}$$

(3.3)

$$e_x = \hat{x} - x, \qquad e_y = \hat{y} - y$$

(3.4)

By choosing the proper value for L, the eigenvalues of (A + LC) can be placed in the lefthand half plane (LHP) to force the error vector  $e_x$  towards zero. As figure 3.1 shows, in order to construct the Luenberger observer one needs to accurately know the system parameters. Before designing the observer, it is necessary to check the observability of the system. The observability matrix of the system is defined as:

$$\mathcal{O} = \begin{bmatrix} C \\ CA \\ \vdots \\ CA^{n-1} \end{bmatrix}$$

(3.5)

The system described by equations 3.1 and 3.2 is observable if, and only, if the rank of the observability matrix is equal to n. This type of observer is only for linear systems with completely known parameters. Any modelling or measurement error leads to error in observation values and loss of observer action [30].

#### 3.3 Variable structure systems

The theory of variable structure system (VSS) was first introduced in Soviet literature in early 1950's by Emelyanov and other researchers [31][32]. VSS theory is based on the using discontinuous feedback control [33][34]. This feedback control is achieved using high speed switching control action between two distinctively different system structures, which forces the trajectory of the system onto a manifold or sliding surface [35][32][36][37]. Having reached the intersection, the trajectory will remain on the manifold and slides on it. This mode of the system is called sliding mode [35][36]. The VSS theory can be used for the design of feedback control laws for uncertain systems. During sliding mode the variable structure controllers are robust to parameter uncertainty and also disturbance [34][38]. VSS control has four main advantages [39]:

• The manifold (switching surface) can be selected in a way that system is robust to disturbances and parameter changes during the sliding mode.

- During the sliding mode the system emulates a reduced order system and if the system has bounded nonlinearities, then under some conditions system behaves like linear system.

- Control algorithm is very simple, and can even be implemented by using a comparator and relay.

- By varying the switching surface the problem of tracking can be addressed.

Although VSS theory has robustness properties against parametric uncertainty and disturbances, classical variable structure control has several drawbacks that limit its practical applicability [40][41]. Variable structure control involves large control authority and control chattering. Chattering is a oscillation with finite frequency and amplitude about the sliding mode manifold [42] which can be harmful and undesirable in some practical applications. This chattering can lead to low control accuracy and high stress on mechanical parts.

There are two possible causes of chattering [36][42][43]. First is the neglected fast dynamics of fast actuators, servomechanisms, sensors and data processors which can be excited by the high switching frequencies and will produce non-decaying oscillations with finite amplitude and frequency. Second is the practical issue of switches that are not capable of switching with infinite frequency and hence will cause chattering affects. Some solutions to improve the chattering problem are suggested in [44][42][45][46][47] but these are limited in application.

#### 3.4 Sliding mode observer

The theory of the sliding mode observer is based on the theory of variable structure systems [48][49]. Sliding mode observers can be applied to both linear and nonlinear systems. Several nonlinear sliding mode observers have been proposed by Misawa, Hedrick and Slotine [43][50][40] as well as Xiong and Saif [51]. Generally there are two methods of sliding mode observer implementation [52]. One method is based on equivalent control theory and the other is based on Lyapunov theory. Several sliding mode observers based on Lyapunov observer have been proposed by Walcott and Zak [53][54][55][56][39], Edwards and Spurgeon [57] as well as Zinober and Koshkouei [58].

Sliding mode observers using the equivalent control method have been published by Utkin and Drakunov [59][60], Hashimoto, Utkin, Xu, Suzuki and Harashima [61] and Haskara, Ozguner and Utkin [62][49]. Sliding mode observers using the equivalent control method are well established for linear systems and have good robustness against system disturbances.

The system studied in this thesis is linear so we are interested in sliding mode observers for linear system hence the main focus of this chapter is on the sliding mode observers based on the equivalent control method.

#### 3.4.1 Traditional sliding mode observers

Early sliding mode observers were introduced by Utkin [49]. In this type of observer the original system is transformed into a canonical form. In the canonical form the output variable appears as a part of state vector. The observed values converge to real states asymptotically. The traditional sliding mode observer is applicable to linear systems. It has no robustness against system uncertainty. Consider a dynamical system defined by:

$$\begin{cases} \dot{x} = Ax + Bu\\ y = Cx \end{cases}$$

(3.6)

Where  $x \in \mathbb{R}^n$ ,  $u \in \mathbb{R}^p$ ,  $y \in \mathbb{R}^m$  and  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times p}$ ,  $C \in \mathbb{R}^{m \times n}$  are constant matrices. This system can be transformed into the following canonical form:

$$\begin{bmatrix} \dot{y} \\ \dot{x}_1 \end{bmatrix} = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \begin{bmatrix} y \\ x_1 \end{bmatrix} + \begin{bmatrix} B_1 \\ B_2 \end{bmatrix} u$$

(3.7)

By a non-singular transformation:

$$\begin{bmatrix} y\\ x_1 \end{bmatrix} = Tx \tag{3.8}$$

*T* is a non-singular transformation matrix:

$$T = \begin{bmatrix} C \\ R_1 \end{bmatrix}$$

(3.9)

Where  $R_1 \in \mathbb{R}^{(n-m) \times n}$  is an arbitrary matrix as long as *T* remains non-singular and  $x_1 \in \mathbb{R}^{(n-m)}$  is equal to  $R_1 x$ . The corresponding sliding mode observer for equation 3.7 would be in the form given in equation 3.10 [47]:

$$\begin{bmatrix} \dot{\hat{y}} \\ \dot{\hat{x}}_1 \end{bmatrix} = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \begin{bmatrix} \hat{\hat{y}} \\ \hat{\hat{x}}_1 \end{bmatrix} + \begin{bmatrix} B_1 \\ B_2 \end{bmatrix} u + \begin{bmatrix} -1 \\ k \end{bmatrix} v$$

(3.10)

Where:

$$v = M.sgn(e_{\nu}) \tag{3.11}$$

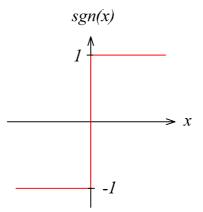

Where  $e_y$  is the measurement error and sgn is sign function, as shown in figure 3.2.

Figure 3.2: sgn() function

The dynamic error is obtained by subtracting equation 3.7 from equation 3.10.

$$\begin{bmatrix} \dot{e_y} \\ e_{x1} \end{bmatrix} = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \begin{bmatrix} e_y \\ e_{x1} \end{bmatrix} + \begin{bmatrix} -1 \\ k \end{bmatrix} v$$

(3.12)

Where:

$$e_{x1} = \hat{x}_1 - x_1, \qquad e_y = \hat{y} - y$$

(3.13)

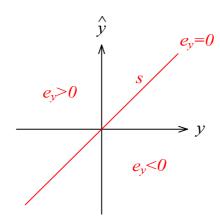

By appropriate choice of M, it is possible that  $e_y$  reaches on manifold  $S(e_y = 0)$  and slides on this surface. The manifold S is shown in figure 3.3.

Figure 3.3: Manifold S

In order to force  $e_y$  to reach on manifold *S* and slide on the surface,  $e_y$  and  $\dot{e_y}$  should have different signs [35].

$$e_y \, \dot{e_y} < 0 \tag{3.14}$$

But if the initial condition of  $e_y$  is far from manifold *S* then condition (3.14) cannot guarantee the reaching mode in a finite time. To make sure that the reaching mode finishes in a finite time the following condition is used [63]:

$$e_y \dot{e_y} < -\eta |e_y| , \qquad \eta > 0 \qquad (3.15)$$

Combining equations (3.12) with equation (3.15) results in the following equations:

$$e_{y}(A_{11}e_{y} + A_{12}e_{x1} - M.sgn(e_{y})) < -\eta |e_{y}|$$

(3.16)

Or

$$e_y > 0: \quad (A_{11}e_y + A_{12}e_{x1} - M) < -\eta$$

(3.17)

$$e_y < 0: \quad (A_{11}e_y + A_{12}e_{x1} - M) > +\eta$$

(3.18)

Combining equations 3.17 and 3.18 will result in equation 3.19.

$$|A_{11}e_y + A_{12}e_{x1}| + \eta < M \tag{3.19}$$

By choosing *M* to be large enough, the reaching mode will be achieved in a finite time and the sliding mode will be guaranteed. In the sliding mode  $e_y$  and  $\dot{e_y}$  are forced to zero. By replacing  $e_y$  and  $\dot{e_y}$  by zero in equation 3.12 the solution for equivalent value of discontinuous control input *v* can be derived:

$$A_{12}e_{x1} = v_{eq} \tag{3.20}$$

By replacing the  $v_{eq}$  in second line of equation 3.12, the dynamic of  $e_{x1}$  is derived as:

$$e_{x1}^{\cdot} = (A_{22} + kA_{12})e_{x1} \tag{3.21}$$

By choosing the appropriate value for k we can assign stable eigenvalues for  $A_{22} + kA_{12}$  and control the speed of convergence of  $e_{x1}$  to zero.

#### 3.4.2 Sliding mode observer using the equivalent control method

A sliding mode observer by using the equivalent control method is proposed by Utkin and Drakunov [59][60], Hashimoto, Utkin, Xu, Suzuki and Harashima [61] and Haskara, Ozguner and Utkin [49][62]. Consider a dynamical system defined by:

$$\begin{cases} \dot{x} = Ax + Bu\\ y = Cx \end{cases}$$

(3.22)

Where  $x \in \mathbb{R}^n$ ,  $u \in \mathbb{R}^p$ ,  $y \in \mathbb{R}^m$  and  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times p}$ ,  $C \in \mathbb{R}^{m \times n}$  are constant matrices. This system can be transformed into the following canonical form:

$$\begin{cases} \dot{y} = A_{11}y + A_{12}x_1 + B_1u \\ \dot{x}_1 = A_{21}y + A_{22}x_1 + B_2u \end{cases}$$

(3.23)

Using a non-singular transformation  $T \in \mathbb{R}^{n \times n}$ :

$$T = \begin{bmatrix} C \\ R_1 \end{bmatrix}$$

(3.24)

Where  $R_1 \in \mathbb{R}^{(n-m) \times n}$  is an arbitrary matrix as long as *T* remains non-singular.

$$Tx = \begin{bmatrix} y \\ x_1 \end{bmatrix}, \ TAT^{-1} = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix}, \ TB = \begin{bmatrix} B_1 \\ B_2 \end{bmatrix}$$

(3.25)

The rank of  $A_{12} \in \mathbb{R}^{m \times (n-m)}$  is  $m_1$ , where  $m_1 \leq m$ ,  $m_1 \leq n-m$ . There exist a matrix  $D_1 \in \mathbb{R}^{m_1 \times m}$  such that rank  $\{D_1A_{12}\} = m_1$ . At this stage a new variable  $y_1 \in \mathbb{R}^{m_1}$  is defined and is combined with the second line of equation 3.23:

$$\begin{cases} \dot{x}_1 = A_{21}y + A_{22}x_1 + B_2u \\ y_1 = D_1 A_{12}x_1 \end{cases}$$

(3.26)

This system can be transformed into the following canonical form:

$$\begin{cases} \dot{y}_1 = A_{31}y_1 + A_{32}x_2 + A_{33}y + B_3u \\ \dot{x}_2 = A_{41}y_1 + A_{42}x_2 + A_{43}y + B_4u \end{cases}$$

(3.27)

Using a non-singular transformation  $T_1 \in \mathbb{R}^{(n-m) \times (n-m)}$ :

$$T_1 = \begin{bmatrix} D_1 A_{12} \\ R_2 \end{bmatrix} \tag{3.28}$$

Where  $R_2 \in \mathbb{R}^{(n-m-m_1)\times(n-m)}$  is an arbitrary matrix as long as  $T_1$  remains non-singular.

$$T_1 x_1 = \begin{bmatrix} y_1 \\ x_2 \end{bmatrix}, \quad T_1 A_{22} T_1^{-1} = \begin{bmatrix} A_{31} & A_{32} \\ A_{41} & A_{42} \end{bmatrix}, \quad T_1 B_2 = \begin{bmatrix} B_3 \\ B_4 \end{bmatrix}$$

(3.29)

The rank of  $A_{32} \in \mathbb{R}^{m_1 \times (n-m-m_1)}$  is  $m_2$ . There exist a matrix  $D_2 \in \mathbb{R}^{m_2 \times m_1}$  such that rank  $\{D_2A_{32}\} = m_2$ .

At this stage a new variable  $y_2 \in \mathbb{R}^{m_2}$  is defined and is combined with the second line of equation 3.27.

$$\begin{cases} \dot{x}_2 = A_{41}y_1 + A_{42}x_2 + A_{43}y + B_4u \\ y_2 = D_2A_{32}x_2 \end{cases}$$

(3.30)

This system can be transformed into the following canonical form:

$$\begin{cases} \dot{y}_2 = A_{51}y_2 + A_{52}x_3 + A_{53}y + A_{54}y_1 + B_5u \\ \dot{x}_3 = A_{61}y_2 + A_{62}x_3 + A_{63}y + A_{64}y_1 + B_6u \end{cases}$$

(3.31)

by a non-singular transformation  $T_2 \in \mathbb{R}^{(n-m-m_1) \times (n-m-m_1)}$ :

$$T_2 = \begin{bmatrix} D_2 A_{32} \\ R_3 \end{bmatrix}$$

(3.32)

Where  $R_3 \in \mathbb{R}^{(n-m-m_1-m_2)\times(n-m-m_1)}$  is an arbitrary matrix as long as  $T_2$  remains non-singular.

$$T_2 x_2 = \begin{bmatrix} y_2 \\ x_3 \end{bmatrix}, \quad T_2 A_{42} T_2^{-1} = \begin{bmatrix} A_{51} & A_{52} \\ A_{61} & A_{62} \end{bmatrix}, \quad T_2 B_4 = \begin{bmatrix} B_5 \\ B_6 \end{bmatrix}$$

(3.33)

at step k the canonical form of system equations will be:

$$\begin{cases} \dot{y}_{k-1} = A_{2k-1,1}y_{k-1} + A_{2k-1,2}x_k + A_{2k-1,3}y + \dots + A_{2k-1,k+1}y_{k-2} + B_{2k-1}u \\ \dot{x}_k = A_{2k,1}y_{k-1} + A_{2k,2}x_k + A_{2k,3}y + \dots + A_{2k,k+1}y_{k-2} + B_{2k}u \end{cases}$$

(3.34)

Using a non-singular transformation  $T_{k-1} \in \mathbb{R}^{(n-m-\sum_{1}^{k-2}m_i)\times(n-m-\sum_{1}^{k-2}m_i)}$ :

$$T_{k-1} = \begin{bmatrix} D_{k-1}A_{2k-3,2} \\ R_k \end{bmatrix}$$

(3.35)

Where:

$$T_{k-1}x_{k-1} = \begin{bmatrix} y_{k-1} \\ x_k \end{bmatrix}$$

(3.36)

Where  $R_k \in \mathbb{R}^{(n-m-\sum_{i=1}^{k-1}m_i)\times(n-m-\sum_{i=1}^{k-2}m_i)}$  is an arbitrary matrix as long as  $T_{k-1}$  remains non-singular. At each step the dimension of dimension of the new system decreases. This procedure will be repeated until step r where  $n = m + \sum_{i=1}^{r} m_i$ . At step r a new variable  $y_r \in \mathbb{R}^{m_r}$  is defined and can be combined with an expression for  $\dot{x}_r$  as follows:

$$\begin{cases} \dot{x}_r = A_{2r,1}y_{r-1} + A_{2r,2}x_r + A_{2r,3}y + \dots + A_{2r,r+1}y_{r-2} + B_{2r}u\\ y_r = D_r A_{2r-1,2}x_r \end{cases}$$

(3.37)

$D_r$  is chosen in such a way that the rank of  $D_r A_{2r-1,2}$  is equal to  $m_r$ . Also  $y_r$  and  $x_r$  are related by a non-singular transformation  $T_r \in \mathbb{R}^{m_r \times m_r}$ :

$$T_r = \left[ D_r A_{2r-1,2} \right] \tag{3.38}$$

The complete set of system equations in canonical form will then be defined by:

$$\begin{cases} \dot{y} = A_{11}y + A_{12}x_1 + B_1u \\ \dot{y}_1 = A_{31}y_1 + A_{32}x_2 + A_{33}y + B_3u \\ \dot{y}_2 = A_{51}y_2 + A_{52}x_3 + A_{53}y + A_{54}y_1 + B_5u \\ \vdots \\ \dot{y}_{r-1} = A_{2r-1,1}y_{r-1} + A_{2r-1,2}x_r + A_{2r-1,3}y + \dots + A_{2r-1,r+1}y_{r-2} + B_{2r-1}u \\ \dot{y}_r = A_{2r+1,1}y_r + A_{2r+1,3}y + \dots + A_{2r+1,r+2}y_{r-1} + B_{2r+1}u \end{cases}$$

(3.39)

The complete set of observer equations for above system equations set will be:

$$\begin{cases} \dot{\hat{y}} = A_{11}\hat{\hat{y}} + A_{12}\hat{x}_{1} + B_{1}u - L_{1}sgn(\hat{\hat{y}} - y) \\ \dot{\hat{y}}_{1} = A_{31}\hat{y}_{1} + A_{32}\hat{x}_{2} + A_{33}\hat{y} + B_{3}u - L_{2}sgn(\hat{y}_{1} - y_{1}) \\ \dot{\hat{y}}_{2} = A_{51}\hat{y}_{2} + A_{52}\hat{x}_{3} + A_{53}\hat{y} + A_{54}\hat{y}_{1} + B_{5}u - L_{3}sgn(\hat{y}_{2} - y_{2}) \\ \vdots \\ \dot{\hat{y}}_{r-1} = A_{2r-1,1}\hat{y}_{r-1} + A_{2r-1,2}\hat{x}_{r} + A_{2r-1,3}\hat{y} + \dots + A_{2r-1,r+1}\hat{y}_{r-2} + B_{2r-1}u \\ -L_{r}sgn(\hat{y}_{r-1} - y_{r-1}) \\ \dot{\hat{y}}_{r} = A_{2r+1,1}\hat{y}_{r} + A_{2r+1,3}\hat{y} + \dots + A_{2r+1,r+2}\hat{y}_{r-1} + B_{2r+1}u - L_{r+1}sgn(\hat{y}_{r} - y_{r}) \end{cases}$$

(3.40)

Where  $L_{k+1} \in \mathbb{R}^{m_k \times m_k}$  is a diagonal matrix for the *k*th step and by choosing the elements to be large enough the sliding mode will take place at *k*th step on manifold;  $S_k(e_y = 0 \cap e_{y_1} = 0 \cap ... \cap e_{y_k} = 0)$ .

Where  $e_{y_k}$  is the error between observed value and system output values and can be defined as:

$$e_{y_k} = \hat{y}_k - y_k \tag{3.41}$$

By subtracting the equation set 3.39 from equation set 3.40 the errors can be defined as:

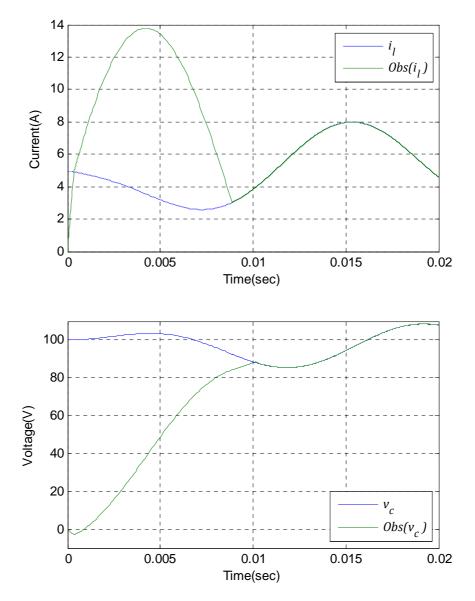

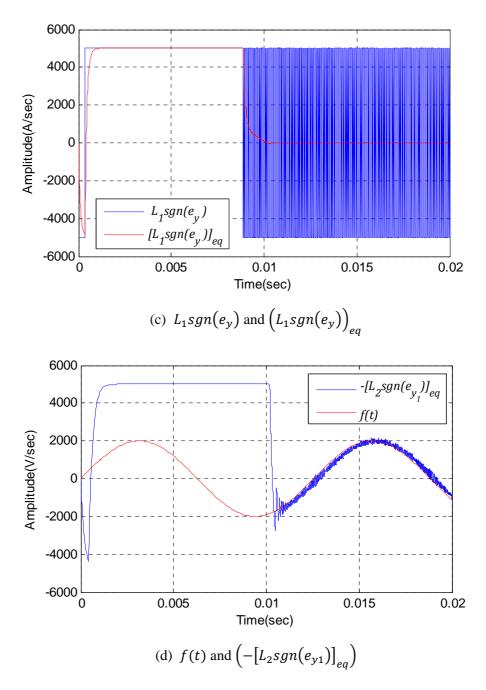

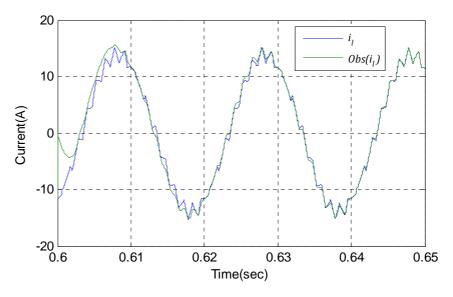

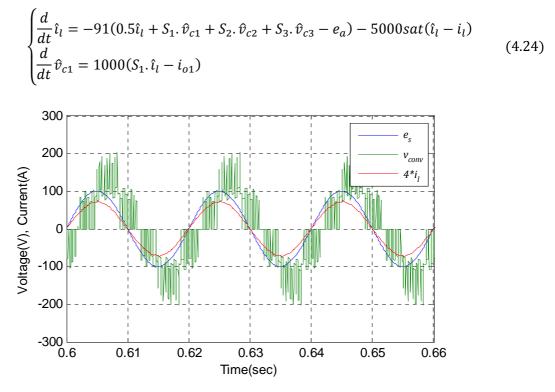

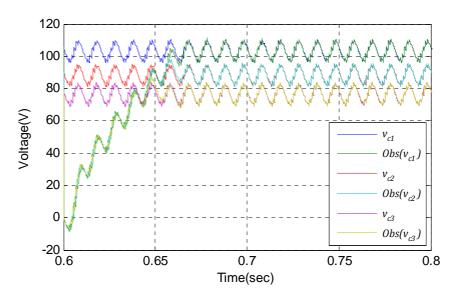

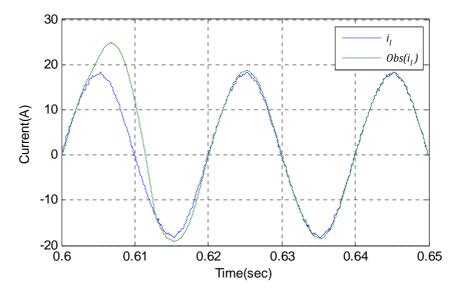

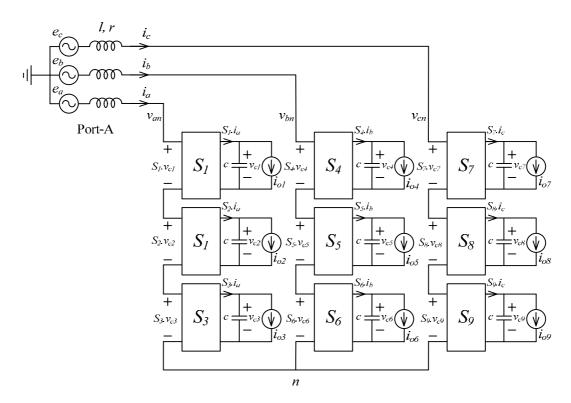

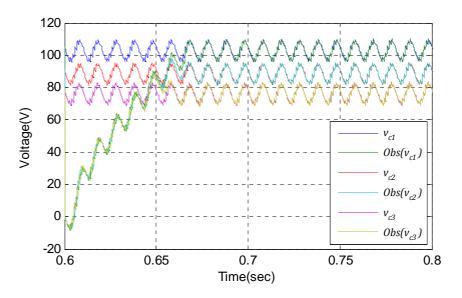

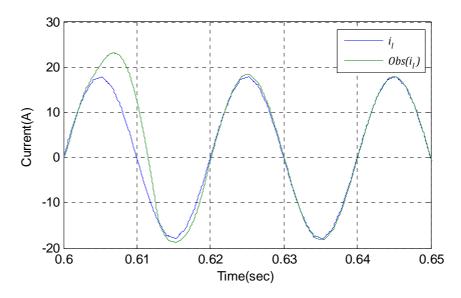

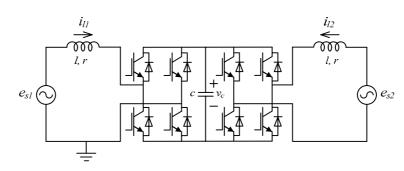

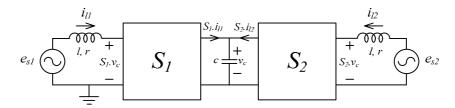

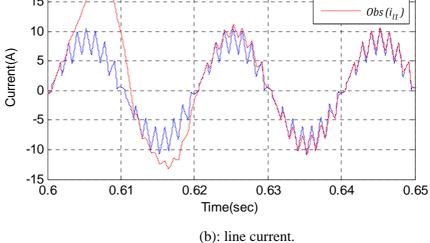

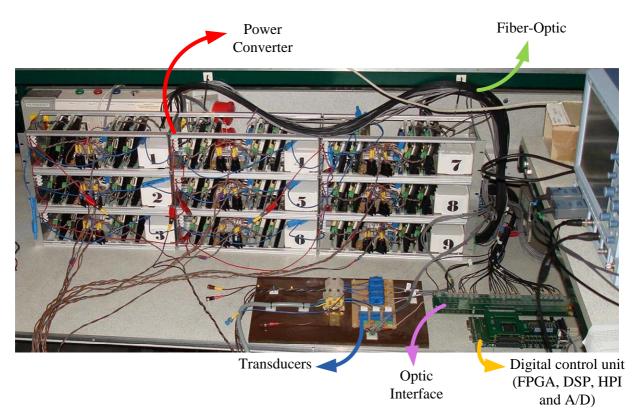

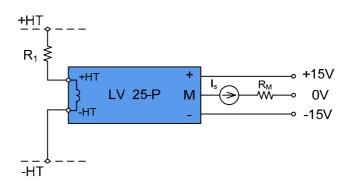

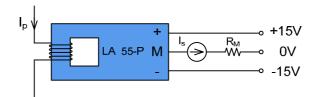

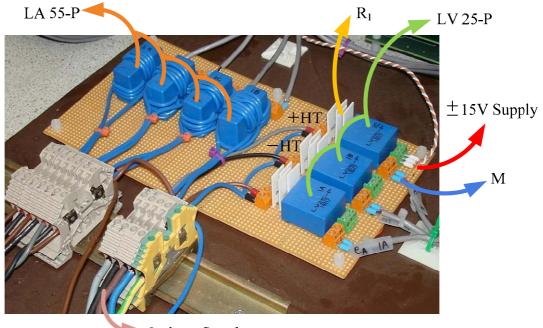

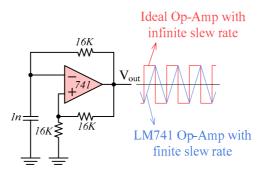

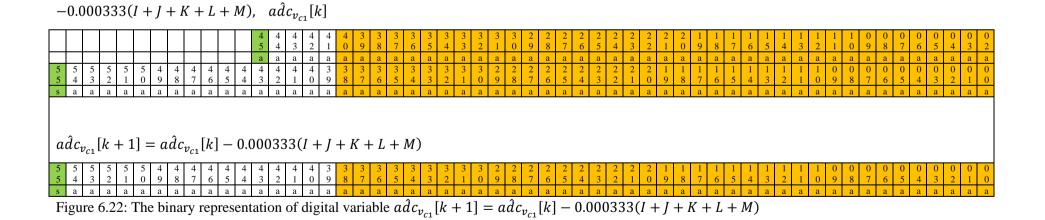

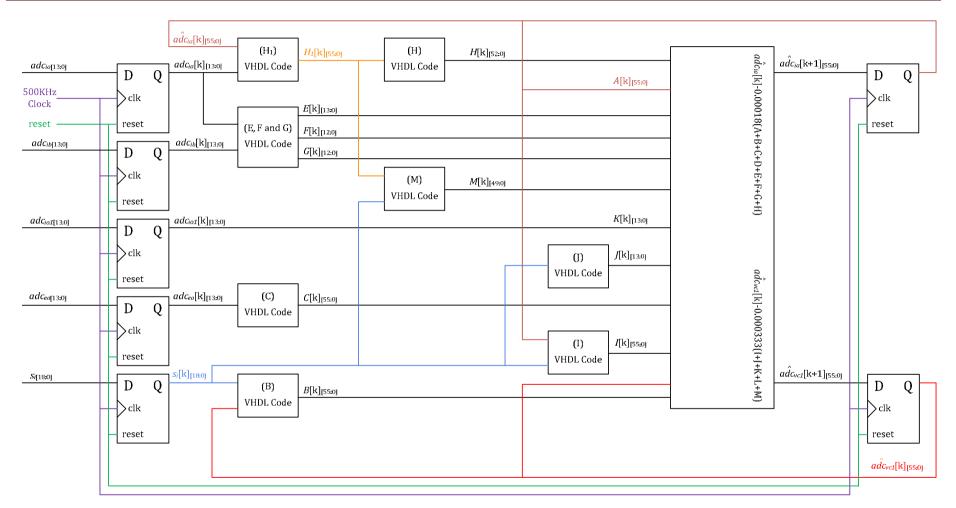

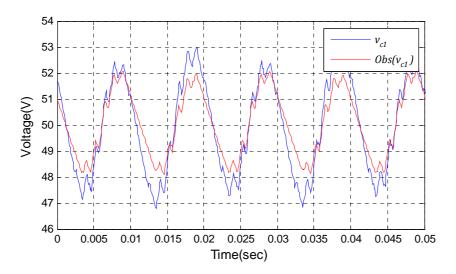

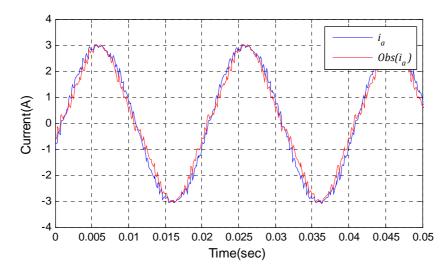

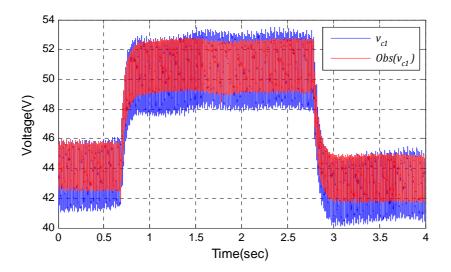

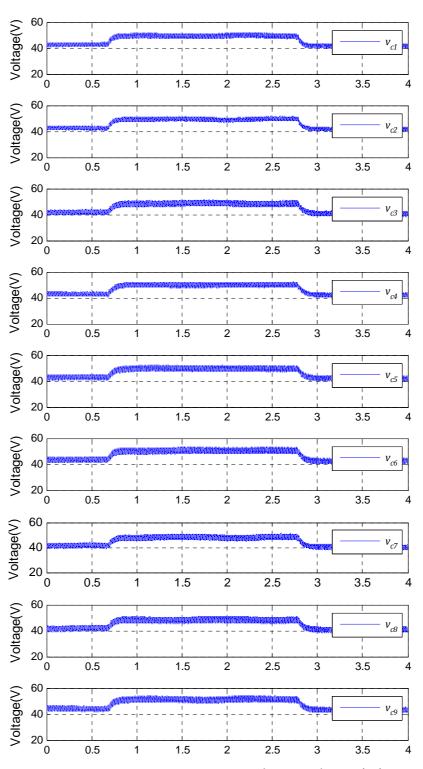

$$\begin{cases} \dot{e}_{y} = A_{11}e_{y} + A_{12}e_{x_{1}} - L_{1}sgn(e_{y}) \\ \dot{e}_{y_{1}} = A_{31}e_{y_{1}} + A_{32}e_{x_{2}} + A_{33}e_{y} - L_{2}sgn(e_{y_{1}}) \\ \dot{e}_{y_{2}} = A_{51}e_{y_{2}} + A_{52}e_{x_{3}} + A_{53}e_{y} + A_{54}e_{y_{1}} - L_{3}.sgn(e_{y_{2}}) \\ \vdots \\ \dot{e}_{y_{r-1}} = A_{2r-1,1}e_{y_{r-1}} + A_{2r-1,2}e_{x_{r}} + A_{2r-1,3}e_{y} + \dots + A_{2r-1,r+1}e_{y_{r-2}} \\ -L_{r}sgn(e_{y_{r-1}}) \\ \dot{e}_{y_{r}} = A_{2r+1,1}\hat{y}_{r} + A_{2r+1,3}\hat{y} + \dots + A_{2r+1,r+2}\hat{y}_{r-1} - L_{r+1}sgn(e_{y_{r}}) \end{cases}$$