# Direct Energy Converter Controllers for Switched Reluctance Motor Operation

Andrew Simon Goodman, MEng(Honours)

Submitted to the University of Nottingham for the degree of Doctor of Philosophy, April 2007.

#### **Abstract**

There is increasing demand for simple motor drives offering high reliability and fault tolerance in applications such as the aerospace actuator industry, with the development of 'more electric aircraft'.

This thesis presents a motor drive employing a switched reluctance motor, the novel single sided matrix converter, and a novel double band hysteresis based control scheme for control of the converter, implemented using a field programmable gate array (FPGA).

The single sided matrix converter is a direct energy converter, capable of supplying unidirectional currents from a multiphase AC voltage source. It is suitable for driving motors such as the switched reluctance motor and trapezoidal permanent magnet direct current (PMDC) machine. The use of a direct energy converter removes the DC link energy storage element usually found in switched reluctance motor drives, making practical implementation possible without the use of electrolytic capacitors. This is a requirement for applications in the aerospace industry. Controller implementation without the use of a digital signal processor (DSP) makes application of the converter in the aerospace industry easy as specific DSP approval is not required.

Simulations of the converter operation are presented, followed by a description of the practical implementation of the novel converter and control schemes. Practical results demonstrate the reliable operation of the converter, driving both switched reluctance and trapezoidal PMDC machines.

The work has been published in three conference papers, presenting both the topology of the drive and the applied control schemes, as well as analysing the fault tolerant capabilities of the drive.

#### Acknowledgements

I would like to thank Dr Keith Bradley for his wide ranging expertise, encouragement and trusting belief in me throughout this PhD. I would also like to thank Dr Pat Wheeler for his assistance with the hardware design, Xiaoyan Huang for her help with the PMDC machine, and Kevin Last, Colin Blackburn, Matt Cooper and the other workshop staff for the mechanical and electrical help needed in producing and testing the single sided matrix converter and setting up the motor loading system.

I also have to thank my friends both within and outside the Electrical and Electronic Engineering Department of the University of Nottingham, especially Paul Robson, Graham Stabler, Roderick MacKenzie, Edward Christopher, Ralph Feldman, Lee Empringham, Liliana de Lillio, Adam Docherty, Ashley Dobson and Ruth Staniforth, for their friendship, support and vital technical assistance throughout the different stages of this research.

Thanks also to the EPSRC for funding me, and to Switched Reluctance Drives for the loan of the switched reluctance motor used in the final stages of the SSMC testing.

Finally, but most importantly i'd like to thank my family. Firstly my parents, Richard and Rosemary Goodman, for providing me with a loving, stable and stimulating upbringing, and for supporting me in many ways throughout my PhD. I could never have dreamt of reaching this stage in my education without them. I am also very greatful to my sister, Emily Goodman, and her Fiancé Simon Talks for their support.

**Key to Acronyms, Abbreviations & Terminology**

|                        | Meaning                                                                                                                                            |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| $\omega$               | Rotational Speed                                                                                                                                   |

| $\theta$               | Angular position                                                                                                                                   |

| (V,I)A,B,C             | Input Phase (Voltages, Currents)                                                                                                                   |

| (V,I)u,v,w,x,y         | Output Phase (Voltages, Currents)                                                                                                                  |

| A, B, C, U             | Required Input Phase Connections                                                                                                                   |

|                        | (A,B,C) with polarity (U)                                                                                                                          |

| A/D                    | Analogue to digital Converter                                                                                                                      |

| AC                     | Alternating Current                                                                                                                                |

| CARAD                  | Civil Aircraft and Technology Demonstration                                                                                                        |

| D                      | Current Direction of Change                                                                                                                        |

| DB                     | Double Band                                                                                                                                        |

| DC                     | Direct Current                                                                                                                                     |

| DSP                    | Digital Signal Processor                                                                                                                           |

| DTI                    | Department of Trade and Industry                                                                                                                   |

| ЕНА                    | Electro hydraulic Actuator                                                                                                                         |

| EMA                    | Electro Mechanical Actuator                                                                                                                        |

| EMF                    | Electro Motive Force                                                                                                                               |

| EPSRC                  | Engineering and Physical Sciences Research Council                                                                                                 |

| FPGA                   | Field Programmable Gate Array                                                                                                                      |

|                        | Cymant                                                                                                                                             |

| I,i                    | Current                                                                                                                                            |

| I,i<br>IC              | Integrated circuit                                                                                                                                 |

| ŕ                      |                                                                                                                                                    |

| IC                     | Integrated circuit                                                                                                                                 |

| IC<br>IGBT             | Integrated circuit Insulated Gate Bipolar Transistor                                                                                               |

| IC<br>IGBT<br>IPC      | Integrated circuit Insulated Gate Bipolar Transistor Association Connecting Electronics Industries                                                 |

| IC<br>IGBT<br>IPC<br>L | Integrated circuit Insulated Gate Bipolar Transistor Association Connecting Electronics Industries Inductance                                      |

| IC<br>IGBT<br>IPC<br>L | Integrated circuit Insulated Gate Bipolar Transistor Association Connecting Electronics Industries Inductance Magnetically Linear, Non Saturating, |

Continued on Next Page...

| Notation         | Meaning                                              |

|------------------|------------------------------------------------------|

| PMDC             | Permanent Magnet Direct Current                      |

| PWM              | Pulse Width Modulation                               |

| R                | Resistance                                           |

| RL               | Resistive and Inductive                              |

| rms              | Root Mean Square                                     |

| rpm              | Revolutions per Minute                               |

| SAa, SBa, SCa    | SSMC Output Current High Side Switches connecting to |

|                  | input phase A, B, C respectively                     |

| SAb, SBb, SCb    | SSMC Output Current Low Side Switches connecting to  |

|                  | input phase A, B, C respectively                     |

| SATOW            | Surface Actuation of Thin and Optimised Wings        |

| SB               | Single Band                                          |

| sec              | Seconds                                              |

| Scope            | Oscilloscope                                         |

| SR               | Switched Reluctance (Motor)                          |

| SSMC             | Single Sided Matrix Converter                        |

| SVM              | Space Vector Modulation                              |

| t                | Time                                                 |

| U1,U2,U3,U4      | Output Current with respect to Hysteresis            |

|                  | Band Logic Signals                                   |

| V                | Voltage                                              |

| V+3, V+2, V+1    | Positive Input Voltage Level Bands                   |

| V0               | Voltage Level zero                                   |

| V-1, V-2, V-3    | Negative Input Voltage Level Bands                   |

| V1,V2,V3         | Required Voltage Level (without polarity)            |

| VHDL             | Very-High-Speed Integrated Circuit                   |

|                  | Hardware Description Language                        |

| X, Y, Z, A, B, C | Input Voltage State Logic Signals                    |

| X-X              | Switched Reluctance Motor Pole Numbers               |

# **Contents**

| 1 | Intr | oductio  | n                                                 | 1  |

|---|------|----------|---------------------------------------------------|----|

|   | 1.1  | Thesis   | Structure                                         | 4  |

| 2 | Pow  | er Elect | tronic Converters including the Matrix Converter  | 6  |

|   | 2.1  | Power    | Electronic Converters Overview                    | 6  |

|   |      | 2.1.1    | The PWM Current Source Rectifier                  | 8  |

|   | 2.2  | Direct   | Power Converters (AC Input)                       | 9  |

|   |      | 2.2.1    | The Cycloconverter                                | 10 |

|   |      | 2.2.2    | The Matrix Converter                              | 11 |

|   | 2.3  | The Co   | onventional Matrix Converter                      | 12 |

|   |      | 2.3.1    | Circuit Structure                                 | 13 |

|   |      | 2.3.2    | Mathematical Model and Modulation Strategies      | 14 |

|   |      |          | 2.3.2.1 The Modulation Problem and Basic Solution | 18 |

CONTENTS vi

|   |                 |                     | 2.3.2.2                          | The Opti                            | imum Amplitude Algorithm              | 20                                                    |

|---|-----------------|---------------------|----------------------------------|-------------------------------------|---------------------------------------|-------------------------------------------------------|

|   |                 |                     | 2.3.2.3                          | Scalar M                            | Iodulation Approach                   | 22                                                    |

|   |                 |                     | 2.3.2.4                          | Space Ve                            | ector Modulation Approach             | 24                                                    |

|   |                 |                     | 2                                | .3.2.4.1                            | Space Phasors                         | 24                                                    |

|   |                 |                     | 2                                | .3.2.4.2                            | Matrix Converter Output Space Phasors | 25                                                    |

|   |                 |                     | 2                                | .3.2.4.3                            | Selection of Switching States         | 25                                                    |

|   |                 |                     | 2.3.2.5                          | Indirect 1                          | Modulation Approach                   | 30                                                    |

|   | 2.4             | Summa               | ary                              |                                     |                                       | 31                                                    |

| • | ~.              |                     |                                  | ~                                   |                                       |                                                       |

| 3 | Sing            | le Sideo            | l Matrix (                       | Converter                           | DC Drive                              | 33                                                    |

| 3 | <b>Sing</b> 3.1 |                     |                                  |                                     | onverter                              |                                                       |

| 3 |                 |                     | ngle Sided                       | d Matrix C                          |                                       | 33                                                    |

| 3 |                 | The Si              | ngle Sideo                       | l Matrix C                          | onverter                              | 33                                                    |

| 3 |                 | The Si 3.1.1        | ngle Sideo                       | l Matrix C                          | onverter                              | 33<br>34<br>35                                        |

| 3 |                 | The Si 3.1.1        | Topology Control 3.1.2.1         | l Matrix C y                        | onverter                              | <ul><li>33</li><li>34</li><li>35</li><li>35</li></ul> |

| 3 |                 | The Si 3.1.1        | Topology Control 3.1.2.1 3.1.2.2 | d Matrix C  y  Control d  Control d | onverter                              | <ul><li>33</li><li>34</li><li>35</li><li>37</li></ul> |

| 3 |                 | The Si 3.1.1        | Topology Control 3.1.2.1 3.1.2.2 | Matrix C  y  Control I  Control A   | onverter                              | 33<br>34<br>35<br>37<br>37                            |

| 3 |                 | The Sin 3.1.1 3.1.2 | Topology Control 3.1.2.1 3.1.2.2 | Control A                           | Onverter                              | 33<br>34<br>35<br>37<br>37                            |

CONTENTS

|   |      | 3.2.1    | Switched Reluctance                           | 41 |

|---|------|----------|-----------------------------------------------|----|

|   |      | 3.2.2    | Trapezoidal Permanent Magnet DC               | 45 |

|   | 3.3  | Summ     | ary                                           | 51 |

| 4 | Sing | le Sided | l Matrix Converter Simulation                 | 52 |

|   | 4.1  | Switch   | ned Reluctance Motor Model                    | 53 |

|   | 4.2  | Trapez   | oidal PMDC Motor Model                        | 59 |

|   | 4.3  | Single   | Band Controller Model                         | 51 |

|   | 4.4  | Double   | e Band Controller Model                       | 55 |

|   | 4.5  | Inducti  | ive/Resistive Load                            | 58 |

|   |      | 4.5.1    | Pulsed Output Current                         | 59 |

|   |      | 4.5.2    | Continuous Output Current                     | 72 |

|   |      | 4.5.3    | Fourier Analysis of Pulsed Current in RL Load | 74 |

|   |      |          | 4.5.3.1 Single Band Control                   | 75 |

|   |      |          | 4.5.3.2 Double Band Control                   | 33 |

|   |      |          | 4.5.3.3 Summary                               | 36 |

|   |      | 4.5.4    | Device Loss Estimation and Comparison         | 91 |

|   | 4.6  | Switch   | ned Reluctance Motor Load                     | 92 |

|   |      | 4.6.1    | Speed - 530 rpm                               | 92 |

CONTENTS

|   |      | 4.6.2   | Speed - 3080 rpm                                       | <del>)</del> 6 |

|---|------|---------|--------------------------------------------------------|----------------|

|   | 4.7  | PMDC    | C (SATOW) Motor Load                                   | )1             |

|   | 4.8  | Summ    | ary                                                    | )5             |

| 5 | Prot | otype D | Orive - Construction and Control Implementation 10     | <b>)7</b>      |

|   | 5.1  | Conve   | rter Hardware                                          | )7             |

|   |      | 5.1.1   | FPGA Controller PCB                                    | )9             |

|   |      | 5.1.2   | Resolver Interface PCB                                 | 11             |

|   |      | 5.1.3   | Current Mirrors PCB                                    | 12             |

|   |      | 5.1.4   | Voltage Transducers and Clamp PCB                      | 14             |

|   |      |         | 5.1.4.1 Clamp Voltage Monitoring Circuit               | 15             |

|   |      | 5.1.5   | Matrix Power PCB                                       | 16             |

|   |      |         | 5.1.5.1 High Voltage/High Current Areas                | 17             |

|   |      |         | 5.1.5.1.1 High Voltage Implications                    | 21             |

|   |      |         | 5.1.5.1.2 High Current Implications                    | 22             |

|   |      |         | 5.1.5.1.2.1 Copper Area Required                       | 23             |

|   |      |         | 5.1.5.2 Gate Drive Circuit                             | 26             |

|   |      |         | 5.1.5.3 Low Voltage Control and Measurement Signals 12 | 28             |

|   |      |         | 5.1.5.4 Mechanical Considerations                      | 28             |

*CONTENTS* ix

|   | 5.2  | FPGA    | Controller Design                                                          |

|---|------|---------|----------------------------------------------------------------------------|

|   |      | 5.2.1   | FPGA Design Considerations                                                 |

|   |      |         | 5.2.1.1 Data Validity                                                      |

|   |      |         | 5.2.1.2 Numerical Manipulation                                             |

|   |      |         | 5.2.1.3 State Machines                                                     |

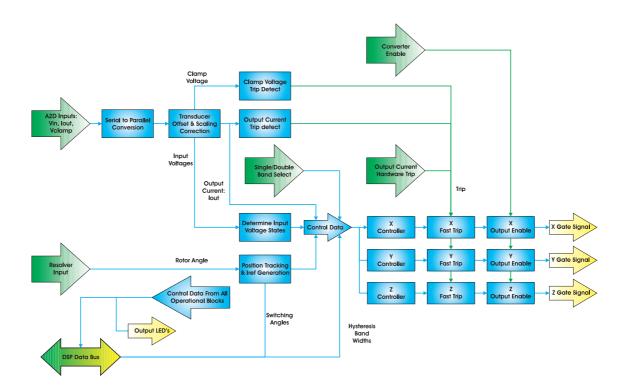

|   |      | 5.2.2   | Control Structure                                                          |

|   |      |         | 5.2.2.1 Transducer Data Acquisition and Processing 134                     |

|   |      |         | 5.2.2.2 Input Voltage State Determination                                  |

|   |      |         | 5.2.2.3 Resolver Data Processing, Filtering and Current Reference Creation |

|   |      |         | 5.2.2.4 Phase Current Controllers                                          |

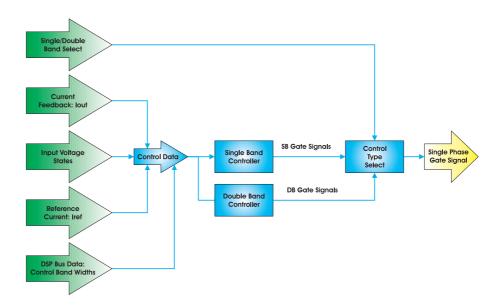

|   |      |         | 5.2.2.4.1 Single Band Current Controller                                   |

|   |      |         | 5.2.2.4.2 Double Band Current Controller                                   |

|   |      |         | 5.2.2.5 Trip Handling                                                      |

|   |      |         | 5.2.2.6 Data Extraction                                                    |

|   | 5.3  | Summ    | ary                                                                        |

| Ó | Prot | otype P | Practical Results 149                                                      |

|   | 6.1  | Basic   | Control Data Required for Both Control Schemes                             |

CONTENTS

|   | 6.2  | Three    | Phase SSMC driven Switched Reluctance Motor             | . 151 |

|---|------|----------|---------------------------------------------------------|-------|

|   |      | 6.2.1    | Single Band Current Control - Low Speed                 | . 154 |

|   |      | 6.2.2    | Double Band Current Control - Low Speed                 | . 158 |

|   |      | 6.2.3    | Single & Double Band Current Control - High Speed       | . 165 |

|   | 6.3  | Five Pl  | hase SSMC driven Trapezoidal PMDC Motor (SATOW Project) | . 168 |

|   | 6.4  | Summ     | ary                                                     | . 171 |

| 7 | Con  | clusion  |                                                         | 173   |

|   | 7.1  | Furthe   | r work                                                  | . 176 |

| A | Pape | ers Pub  | lished                                                  | 178   |

| В | Sing | le Band  | l Controller Logic                                      | 179   |

| C | Dou  | ble Ban  | d Controller Logic                                      | 180   |

| D | Inpu | ıt Volta | ge Identifier Mealy State Machine VHDL Code             | 199   |

| E | 5-Ph | ase SSI  | MC Photos                                               | 207   |

| F | Mat  | rix PCF  | B Layers & Photos                                       | 212   |

# **List of Figures**

| 2.1  | PWM Current Source Rectifier                                                                                 | 8  |

|------|--------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Cycloconverter Topology. a,6-Pulse. b,12-Pulse                                                               | 10 |

| 2.3  | Cycloconverter Single Output Phase Voltage - Resistive Load                                                  | 11 |

| 2.4  | Cycloconverter Single Output Phase Voltage - Resistive & Inductive Load .                                    | 11 |

| 2.5  | Conventional AC Matrix Converter Topology                                                                    | 13 |

| 2.6  | Common Emitter Bidirectional Switch Cell used in Conventional AC Matrix Converters                           | 14 |

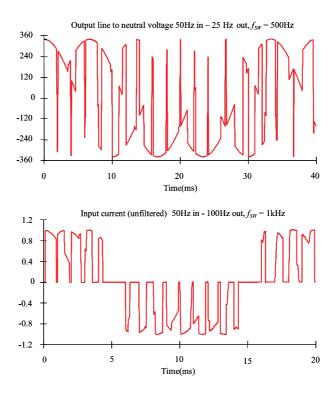

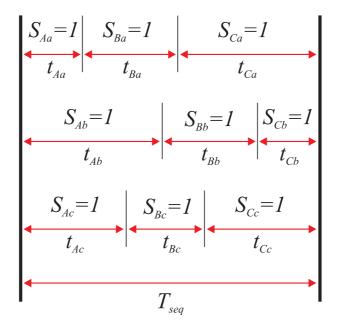

| 2.7  | Typical Matrix Converter waveforms a,Output Voltage. b,Input Current                                         | 17 |

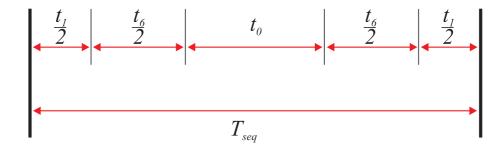

| 2.8  | General Form of Matrix Converter Switching Pattern                                                           | 17 |

| 2.9  | Theoretical Waveforms Illustrating the 50% Voltage Ratio Limit                                               | 21 |

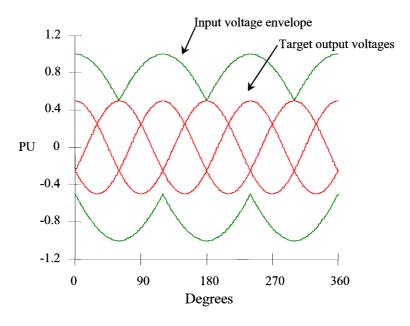

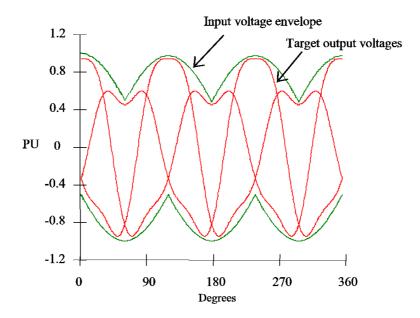

| 2.10 | Theoretical Waveforms Illustrating the Third Harmonic Addition to Obtain the 87% Optimum Voltage Ratio Limit | 21 |

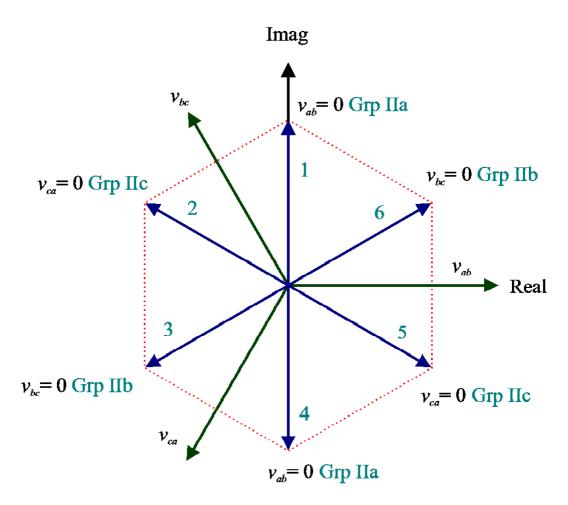

| 2.11 | Output Voltage Space Vectors                                                                                 | 28 |

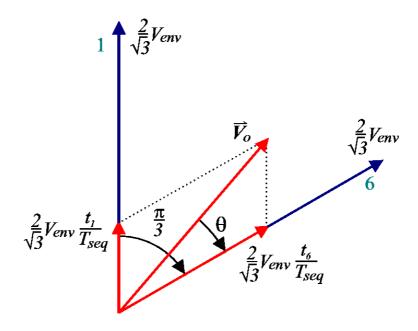

| 2.12 | Synthesis of output voltage space phasor                                                                     | 29 |

LIST OF FIGURES xii

| 2.13 | Possible Arrangement of Switching States within the Switching Sequence . | 29 |

|------|--------------------------------------------------------------------------|----|

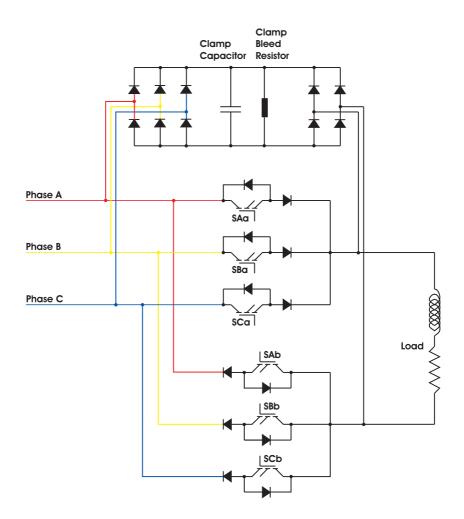

| 3.1  | Single Sided Matrix Converter Topology - Single Output Phase             | 34 |

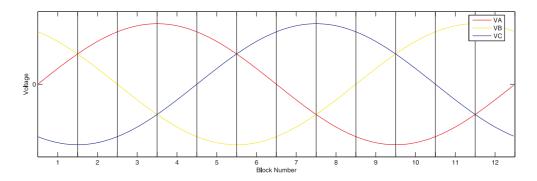

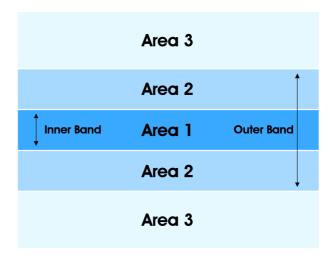

| 3.2  | The 12 Blocks of a 3-phase AC Cycle                                      | 38 |

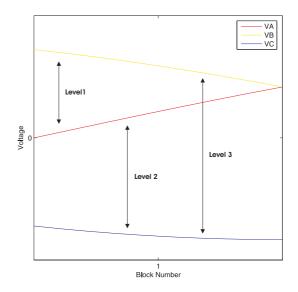

| 3.3  | The 3 Voltage Levels Available From a 3-phase AC Supply - Block 1        | 38 |

| 3.4  | Phase to Phase Supply Voltage Levels Available From a 3-phase AC supply  | 39 |

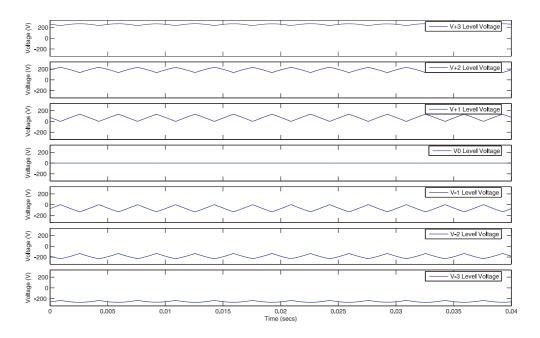

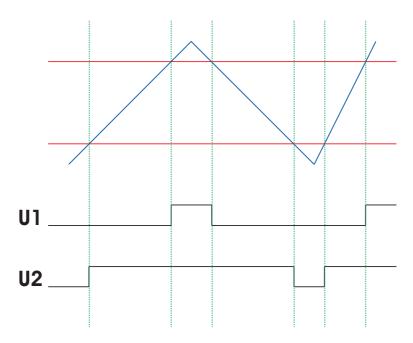

| 3.5  | Double Bands                                                             | 40 |

| 3.6  | 2-2 SR Motor                                                             | 42 |

| 3.7  | 6-4 SR Motor                                                             | 43 |

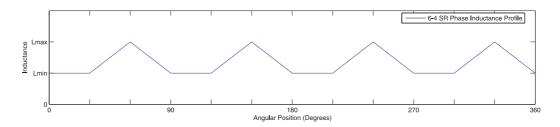

| 3.8  | 6-4 SR Motor Phase Inductance                                            | 43 |

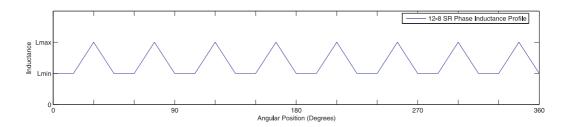

| 3.9  | 12-8 SR Motor                                                            | 44 |

| 3.10 | 12-8 SR Motor Phase Inductance                                           | 44 |

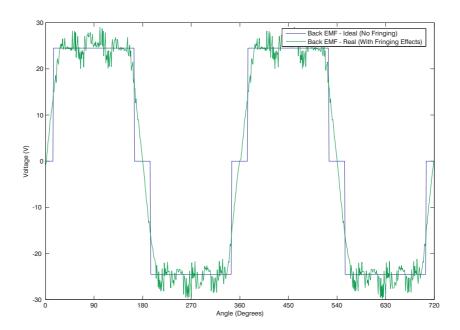

| 3.11 | PMDC Motor Back EMF (Phase A)                                            | 48 |

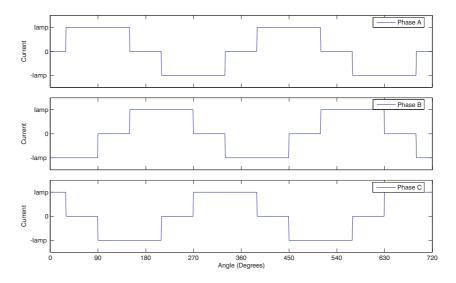

| 3.12 | 3 Phase PMDC Motor Phase Conduction Periods                              | 48 |

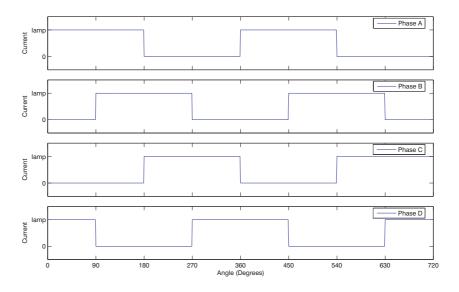

| 3.13 | 4 Phase PMDC Conduction Periods                                          | 49 |

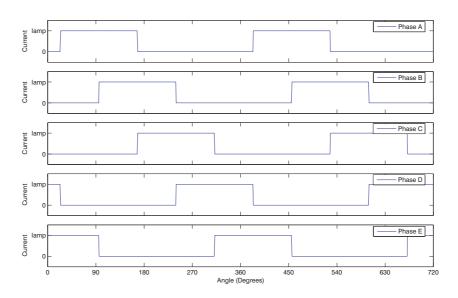

| 3.14 | 5 Phase PMDC Conduction Periods                                          | 50 |

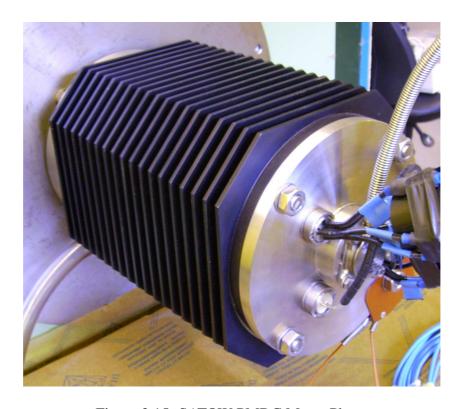

| 3.15 | SATOW PMDC Motor Photo                                                   | 50 |

| 4.1  | Simulated SR Motor Photo                                                 | 53 |

| 4.2  | Linear Switched Reluctance Motor Model                                   | 55 |

LIST OF FIGURES xiii

| 4.3  | Linear Switched Reluctance Motor Model - Controlled Inductance                                                                                                                 | 55 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4  | Linear Switched Reluctance Motor Model - Back EMF                                                                                                                              | 56 |

| 4.5  | Flux Linkage against Current Curve for Simulated Motor                                                                                                                         | 57 |

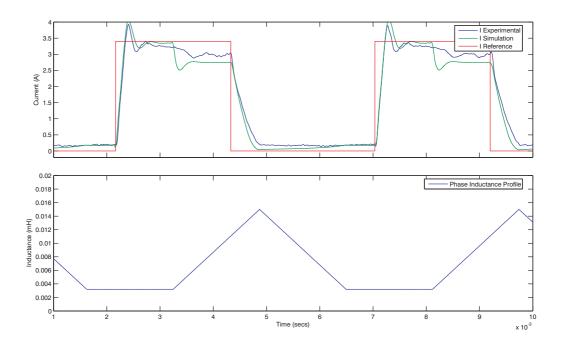

| 4.6  | Linear Switched Reluctance Motor Model Verification - 530 rpm                                                                                                                  | 58 |

| 4.7  | Linear Switched Reluctance Motor Model Verification - 3080 rpm                                                                                                                 | 59 |

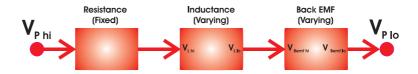

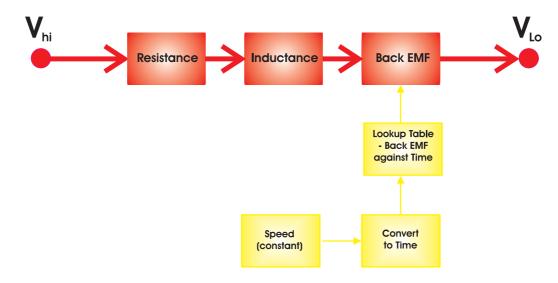

| 4.8  | Trapezoidal PMDC Motor Model Schematic                                                                                                                                         | 60 |

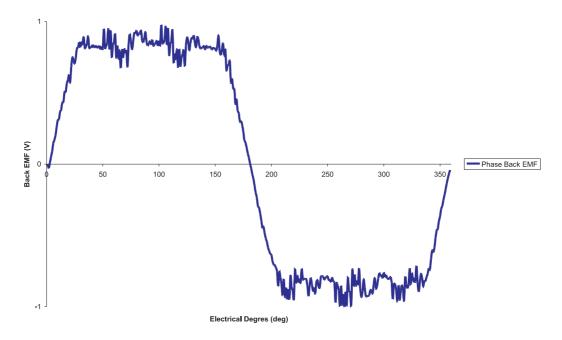

| 4.9  | Trapezoidal PMDC motor Back EMF Profile from MagNet Simulation                                                                                                                 | 61 |

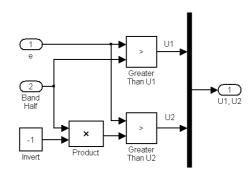

| 4.10 | Single Band Controller - Top Level                                                                                                                                             | 63 |

| 4.11 | Single Band Controller - Hysteresis Band                                                                                                                                       | 63 |

| 4.12 | Single Band Controller - Voltage Level Identifier                                                                                                                              | 63 |

| 4.13 | Single Band Controller - Gating Signal Circuit                                                                                                                                 | 64 |

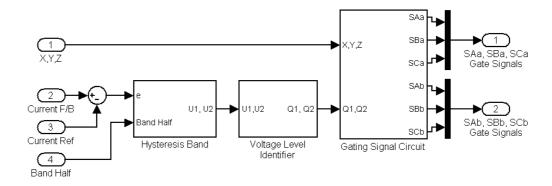

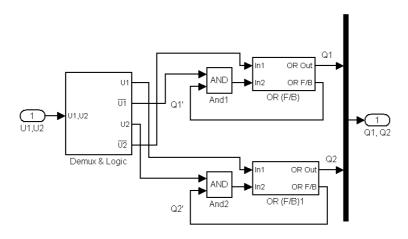

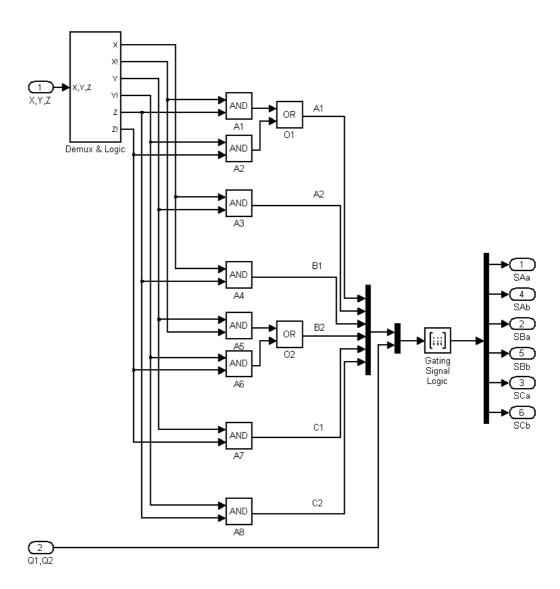

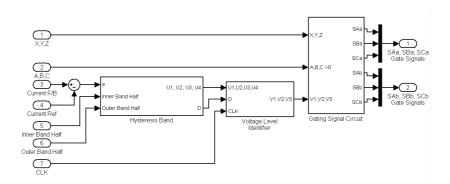

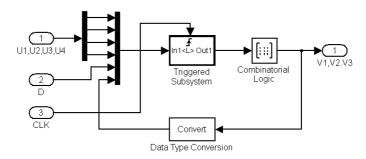

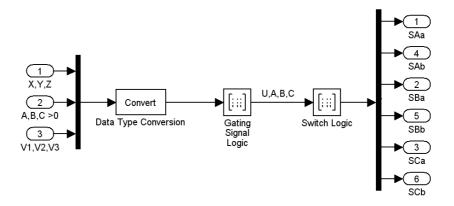

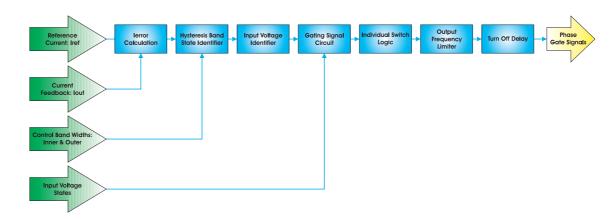

| 4.14 | Double Band Controller - Top Level                                                                                                                                             | 65 |

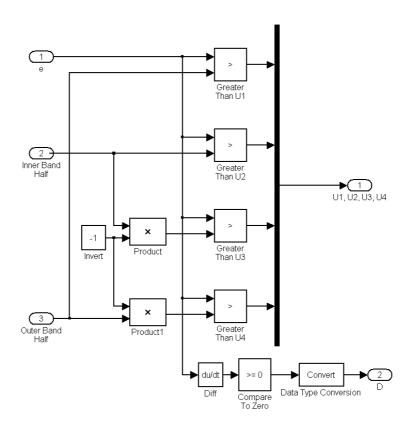

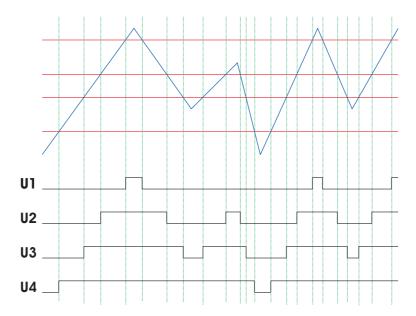

| 4.15 | Double Band Controller - Hysteresis Band                                                                                                                                       | 66 |

| 4.16 | Double Band Controller - Voltage Level Identifier                                                                                                                              | 67 |

| 4.17 | Double Band Controller - Gating Signal Circuit                                                                                                                                 | 68 |

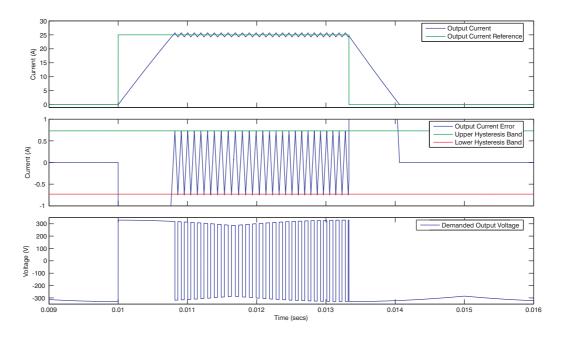

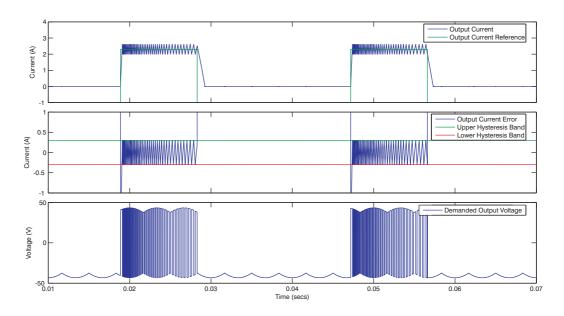

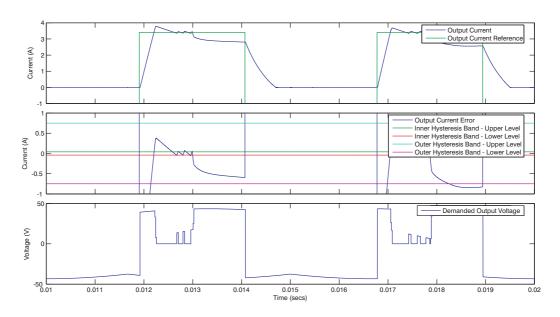

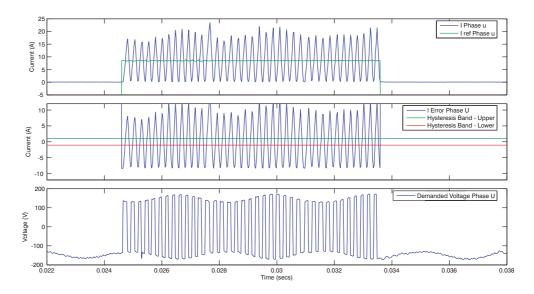

| 4.18 | RL Load, SB Control, Pulsed Output a, Output Current with Reference. b, Output Current Error with Hysteresis Band. c, Demanded Output Voltage                                  | 70 |

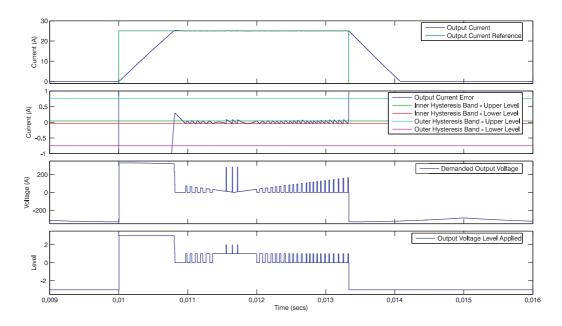

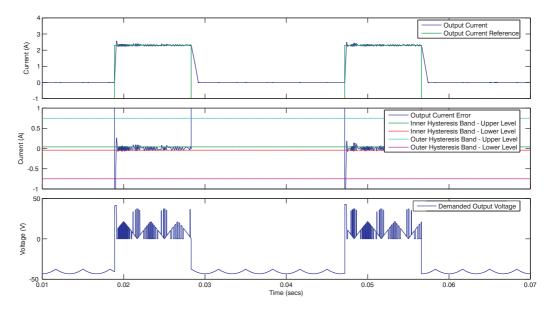

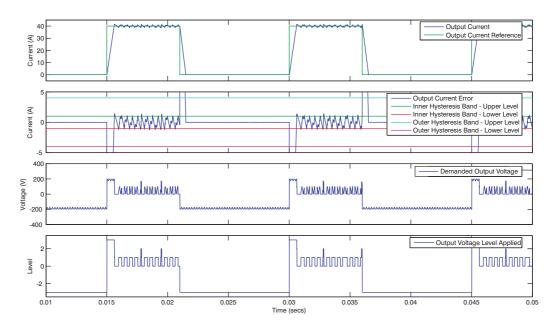

| 4.19 | RL Load, DB Control, Pulsed Output a, Output Current with Reference. b, Output Current Error with Hysteresis Bands. c, Applied Output Voltage. d, Applied Output Voltage level | 72 |

LIST OF FIGURES xiv

| 4.20 | Control                                                                                                                                                                                                                               | 73 |

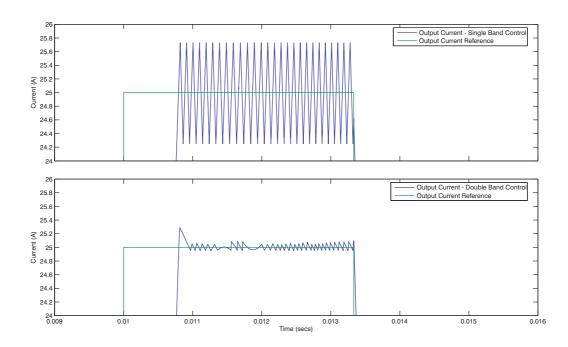

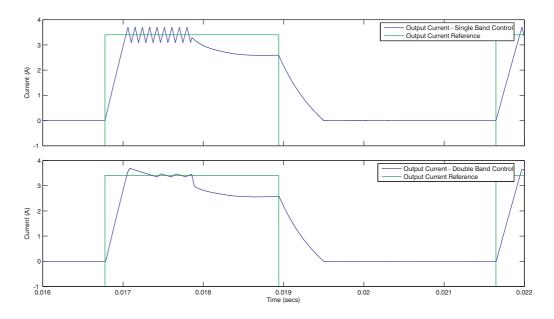

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.21 | RL Load, Continuous Output Current with Reference a, SB Control. b, DB Control                                                                                                                                                        | 73 |

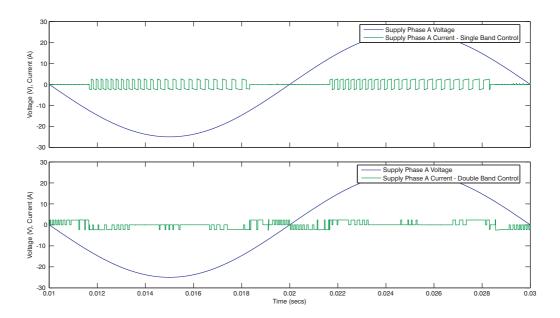

| 4.22 | RL Load, Continuous Output Current, Input Voltage and Current a, SB Control. b, DB Control                                                                                                                                            | 74 |

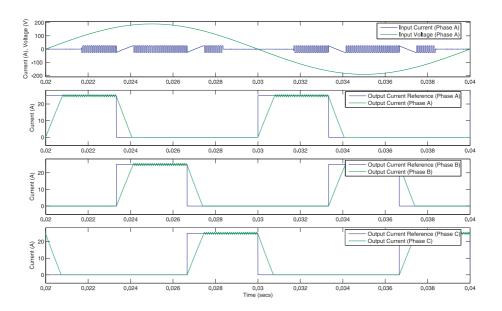

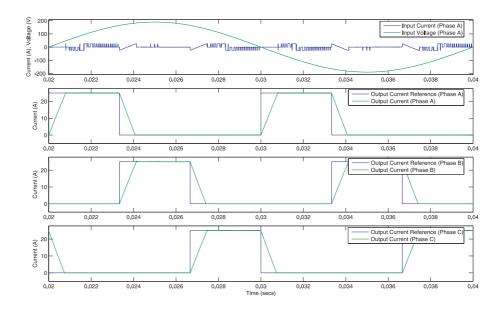

| 4.23 | RL Load, SB Control, Pulsed Output Current (Period 3.33ms), Band 1.46A, a, Input Voltage and Current. b, Output Current and Reference (Phase A). c, Output Current and Reference (Phase B). d, Output Current and Reference (Phase C) | 76 |

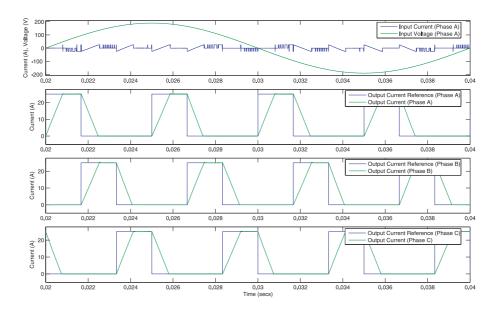

| 4.24 | RL Load, SB Control, Pulsed Output Current (Period 1.67ms), Band 1.46A, a, Input Voltage and Current. b, Output Current and Reference (Phase A). c, Output Current and Reference (Phase B). d, Output Current and Reference (Phase C) | 76 |

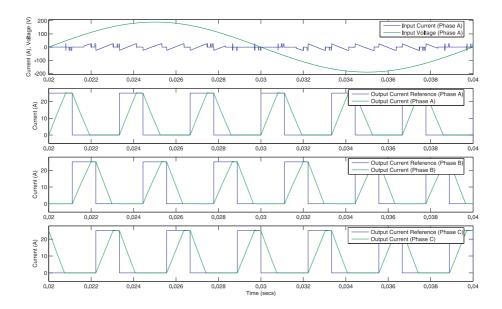

| 4.25 | RL Load, SB Control, Pulsed Output Current (Period 1.11ms), Band 1.46A, a, Input Voltage and Current. b, Output Current and Reference (Phase A). c, Output Current and Reference (Phase B). d, Output Current and Reference (Phase C) | 77 |

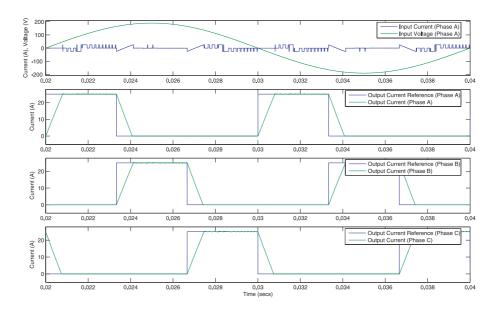

| 4.26 | RL Load, SB Control, Pulsed Output Current (Period 3.33ms), Band 2.92A, a, Input Voltage and Current. b, Output Current and Reference (Phase A). c, Output Current and Reference (Phase B). d, Output Current and Reference (Phase C) | 77 |

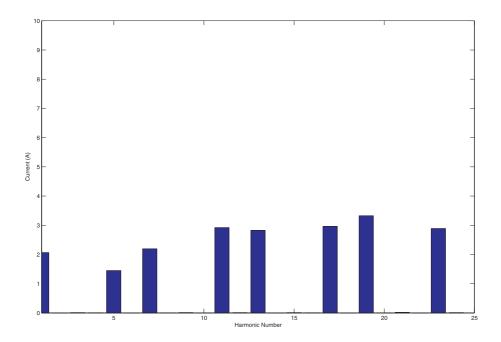

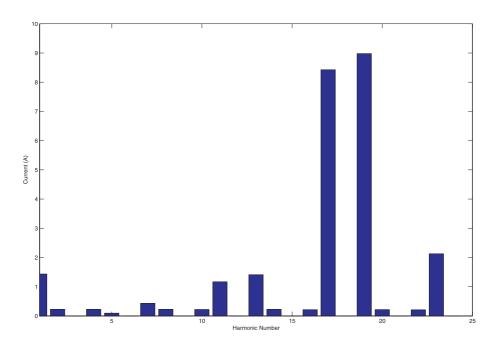

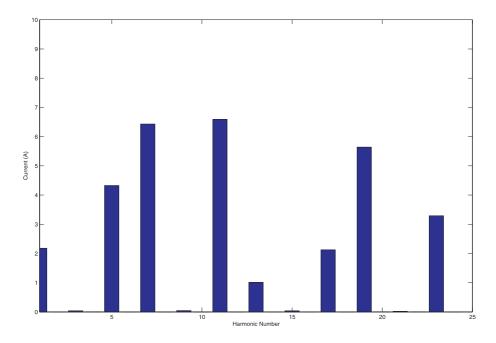

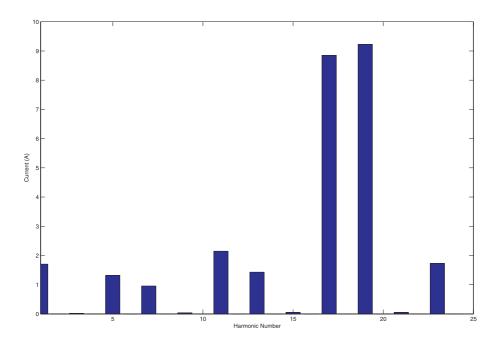

| 4.27 | RL Load, SB Control, Pulsed Output Current (Period 3.33ms), Band 1.46A, Fourier Analysis (25 Harmonics), Fundamental Frequency 50Hz                                                                                                   | 79 |

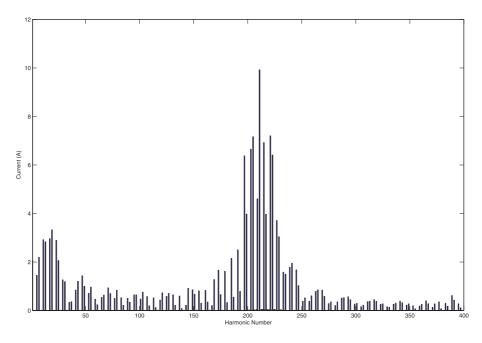

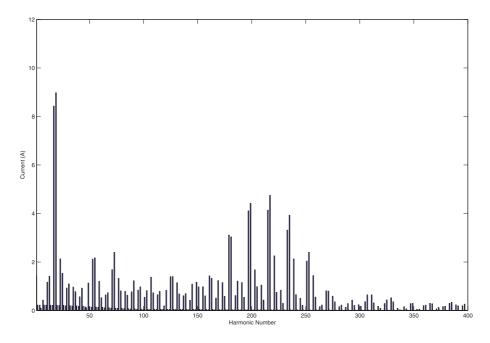

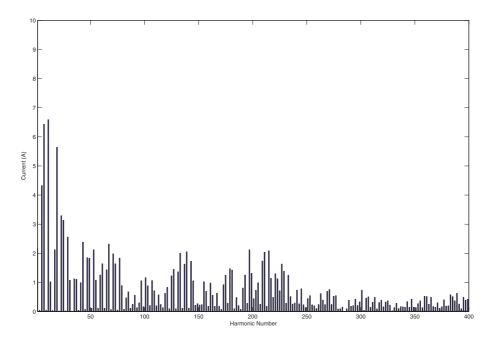

| 4.28 | RL Load, SB Control, Pulsed Output Current (Period 3.33ms), Band 1.46A, Fourier Analysis (400 Harmonics), Fundamental Frequency 50Hz .                                                                                                | 79 |

LIST OF FIGURES xv

| 4.29 | RL Load, SB Control, Pulsed Output Current (Period 1.67ms), Band         |    |

|------|--------------------------------------------------------------------------|----|

|      | 1.46A, Fourier Analysis (25 Harmonics), Fundamental Frequency 50Hz       | 80 |

| 4.30 | RL Load, SB Control, Pulsed Output Current (Period 1.67ms), Band         |    |

|      | 1.46A, Fourier Analysis (400 Harmonics), Fundamental Frequency 50Hz .    | 80 |

| 4.31 | RL Load, SB Control, Pulsed Output Current (Period 1.11ms), Band         |    |

|      | 1.46A, Fourier Analysis (25 Harmonics), Fundamental Frequency 50Hz       | 81 |

| 4.32 | RL Load, SB Control, Pulsed Output Current (Period 1.11ms), Band         |    |

|      | 1.46A, Fourier Analysis (400 Harmonics), Fundamental Frequency 50Hz .    | 81 |

| 4.33 | RL Load, SB Control, Pulsed Output Current (Period 3.33ms), Band         |    |

|      | 2.92A, Fourier Analysis (25 Harmonics), Fundamental Frequency 50Hz       | 82 |

| 4.34 | RL Load, SB Control, Pulsed Output Current (Period 3.33ms), Band         |    |

|      | 2.92A, Fourier Analysis (400 Harmonics), Fundamental Frequency 50Hz .    | 82 |

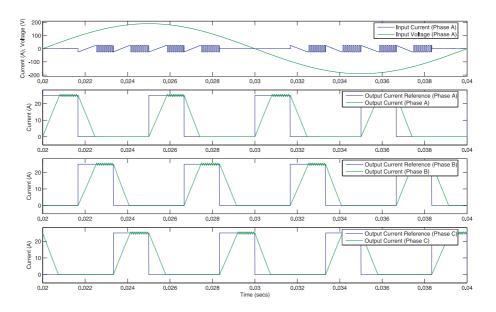

| 4.35 | RL Load, DB Control, Pulsed Output Current (Period 3.33ms), Inner Band   |    |

|      | 0.065A, Outer Band 0.5A, a, Input Voltage and Current. b, Output Current |    |

|      | and Reference (Phase A). c, Output Current and Reference (Phase B). d,   |    |

|      | Output Current and Reference (Phase C)                                   | 84 |

| 4.36 | RL Load, DB Control, Pulsed Output Current (Period 1.67ms), Inner Band   |    |

|      | 0.065A, Outer Band 0.5A, a, Input Voltage and Current. b, Output Current |    |

|      | and Reference (Phase A). c, Output Current and Reference (Phase B). d,   |    |

|      | Output Current and Reference (Phase C)                                   | 84 |

| 4.37 | RL Load, DB Control, Pulsed Output Current (Period 1.11ms), Inner Band   |    |

|      | 0.065A, Outer Band 0.5A, a, Input Voltage and Current. b, Output Current |    |

|      | and Reference (Phase A). c, Output Current and Reference (Phase B). d,   |    |

|      | Output Current and Reference (Phase C)                                   | 85 |

LIST OF FIGURES xvi

| 4.38 | RL Load, DB Control, Pulsed Output Current (Period 3.33ms), Inner Band  |    |

|------|-------------------------------------------------------------------------|----|

|      | 0.13A, Outer Band 0.5A, a, Input Voltage and Current. b, Output Current |    |

|      | and Reference (Phase A). c, Output Current and Reference (Phase B). d,  |    |

|      | Output Current and Reference (Phase C)                                  | 85 |

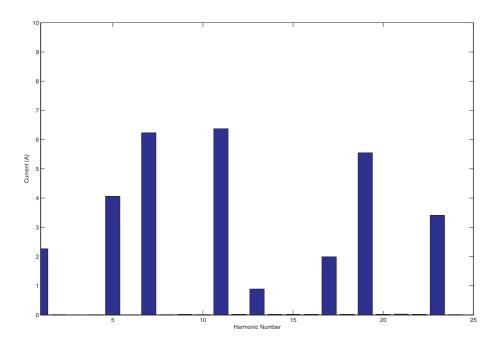

| 4.39 | RL Load, DB Control, Pulsed Output Current (Period 3.33ms), Inner Band  |    |

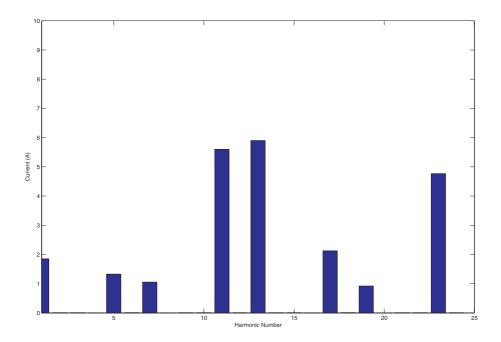

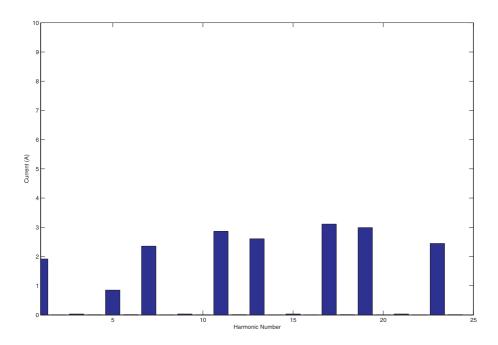

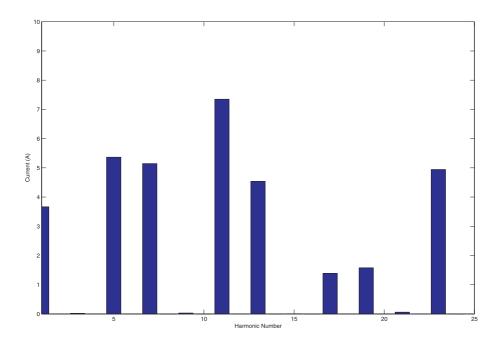

|      | 0.065A, Outer Band 0.5A, Fourier Analysis (25 Harmonics), Fundamental   |    |

|      | Frequency 50Hz                                                          | 87 |

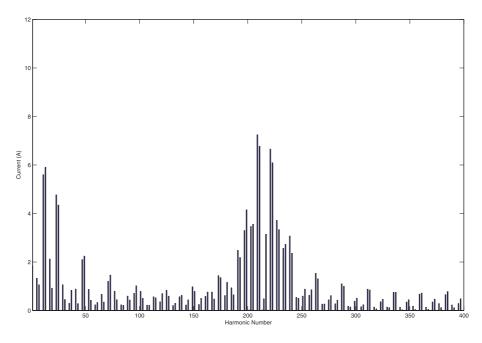

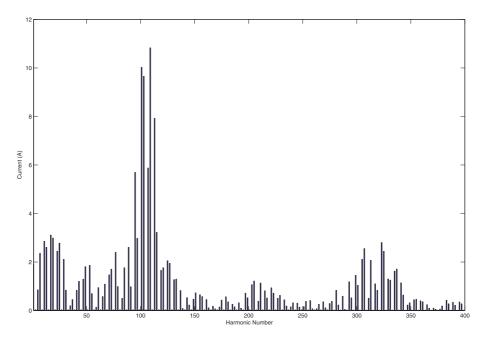

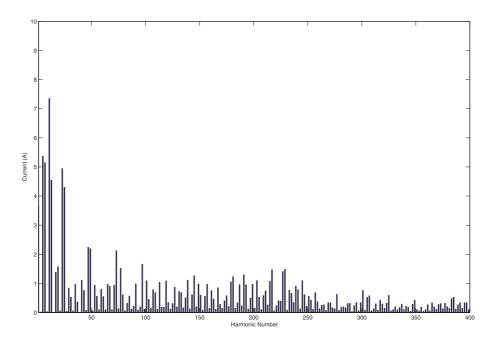

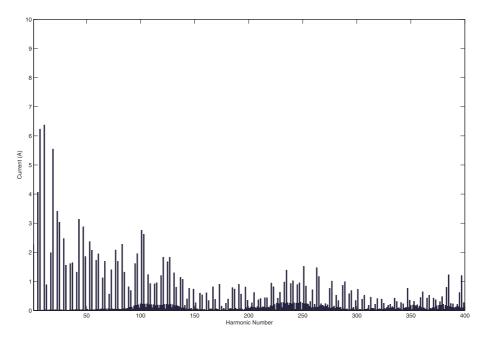

| 4.40 | RL Load, DB Control, Pulsed Output Current (Period 3.33ms), Inner Band  |    |

|      | 0.065A, Outer Band 0.5A, Fourier Analysis (400 Harmonics), Fundamen-    |    |

|      | tal Frequency 50Hz                                                      | 87 |

| 4.41 | RL Load, DB Control, Pulsed Output Current (Period 1.67ms), Inner Band  |    |

|      | 0.065A, Outer Band 0.5A, Fourier Analysis (25 Harmonics), Fundamental   |    |

|      | Frequency 50Hz                                                          | 88 |

| 4.42 | RL Load, DB Control, Pulsed Output Current (Period 1.67ms), Inner Band  |    |

|      | 0.065A, Outer Band 0.5A, Fourier Analysis (400 Harmonics), Fundamen-    |    |

|      | tal Frequency 50Hz                                                      | 88 |

| 4.43 | RL Load, DB Control, Pulsed Output Current (Period 1.11ms), Inner Band  |    |

|      | 0.065A, Outer Band 0.5A, Fourier Analysis (25 Harmonics), Fundamental   |    |

|      | Frequency 50Hz                                                          | 89 |

| 4.44 | RL Load, DB Control, Pulsed Output Current (Period 1.11ms), Inner Band  |    |

|      | 0.065A, Outer Band 0.5A, Fourier Analysis (400 Harmonics), Fundamen-    |    |

|      | tal Frequency 50Hz                                                      | 89 |

| 4.45 | RL Load, DB Control, Pulsed Output Current (Period 3.33ms), Inner Band  |    |

|      | 0.13A, Outer Band 0.5A, Fourier Analysis (25 Harmonics), Fundamental    |    |

|      | Frequency 50Hz                                                          | 90 |

LIST OF FIGURES xvii

| 4.46 | RL Load, DB Control, Pulsed Output Current (Period 3.33ms), Inner Band  |    |

|------|-------------------------------------------------------------------------|----|

|      | 0.13A, Outer Band 0.5A, Fourier Analysis (400 Harmonics), Fundamental   |    |

|      | Frequency 50Hz                                                          | 90 |

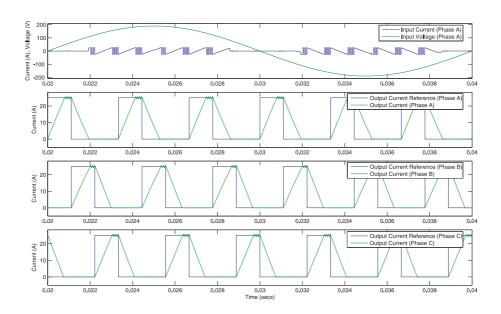

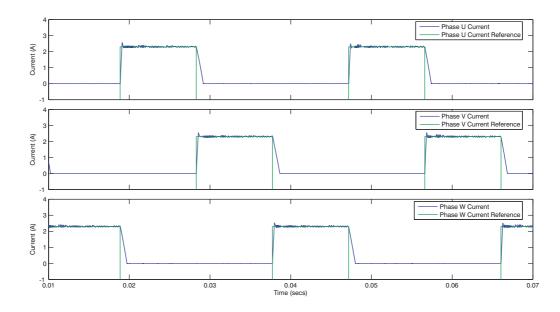

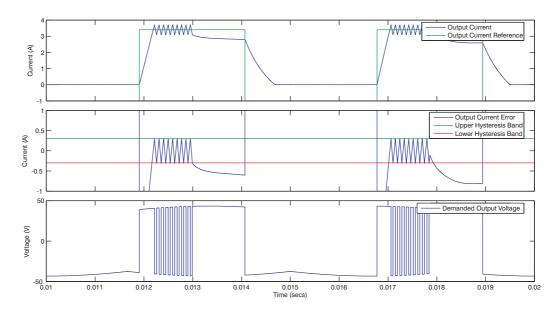

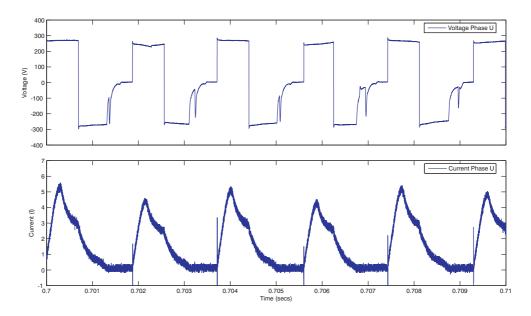

| 4.47 | Linear SRM Model (530 rpm), SB Control, Three Phase Output Currents     | 92 |

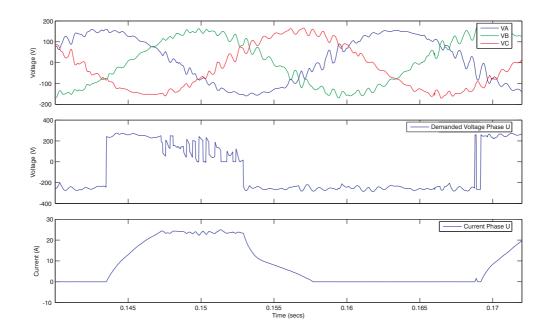

| 4.48 | Linear SRM Model (530 rpm), SB Control, Phase U a, Output Current with  |    |

|      | Reference. b, Output Current Error with Hysteresis Band. c, Demanded    |    |

|      | Output Voltage                                                          | 93 |

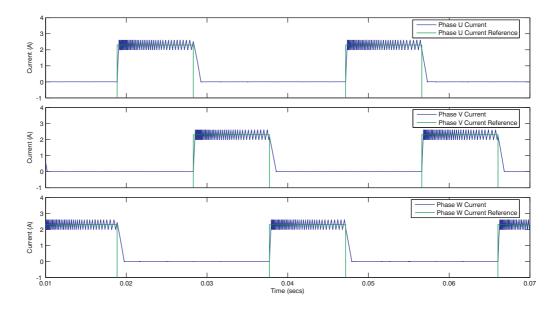

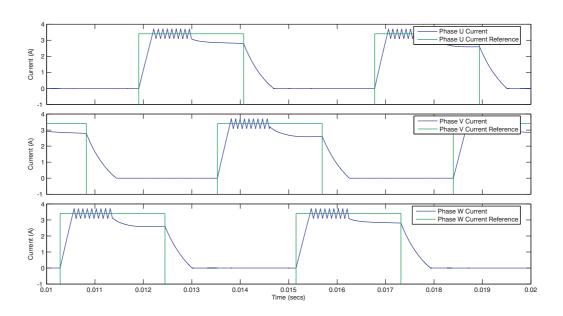

| 4.49 | Linear SRM Model (530 rpm), DB Control, Three Phase Output Currents     | 94 |

| 4.50 | Linear SRM Model (530 rpm), DB Control, Phase U a, Output Current with  |    |

|      | Reference. b, Output Current Error with Hysteresis Bands. c, Demanded   |    |

|      | Output Voltage                                                          | 94 |

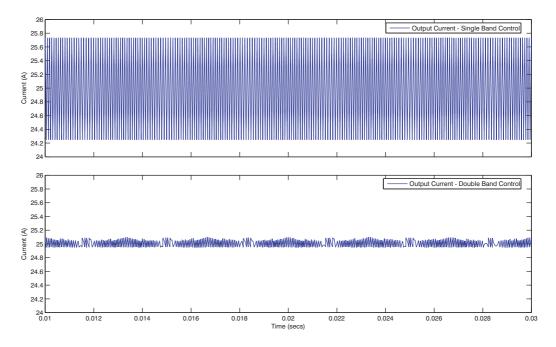

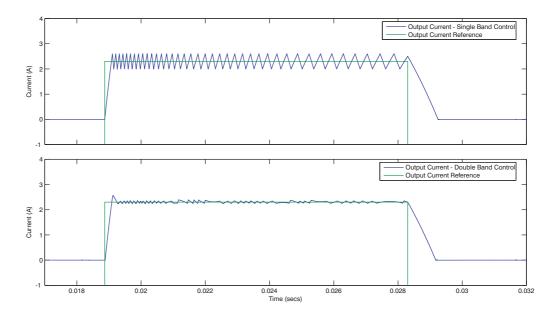

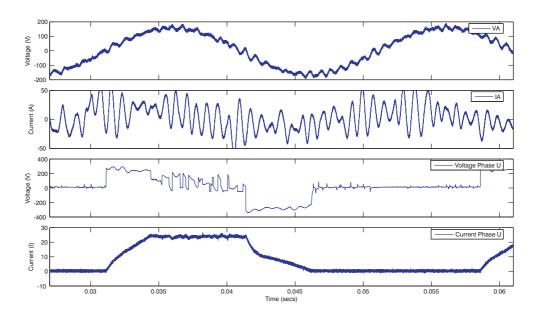

| 4.51 | Linear SRM Model (530 rpm) Output Current with Reference a, SB Con-     |    |

|      | trol. b, DB Control                                                     | 95 |

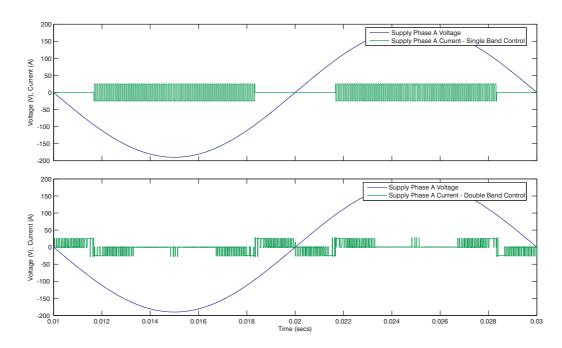

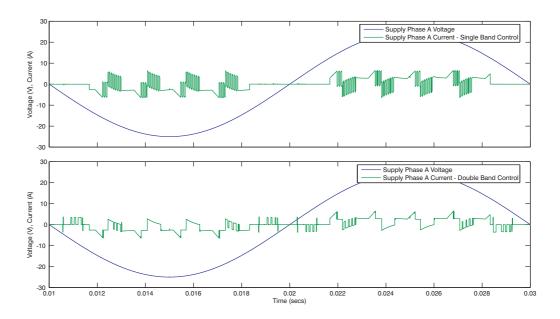

| 4.52 | Linear SRM Model (530 rpm), Input Voltage and Current a, SB Control. b, |    |

|      | DB Control                                                              | 96 |

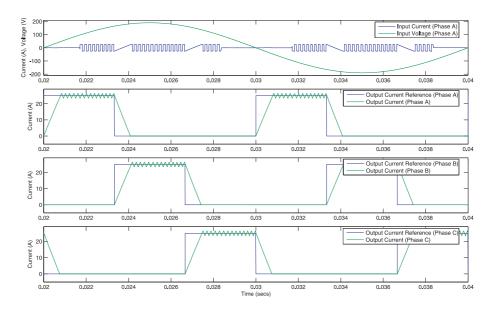

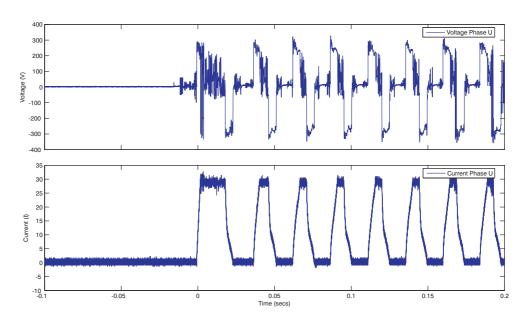

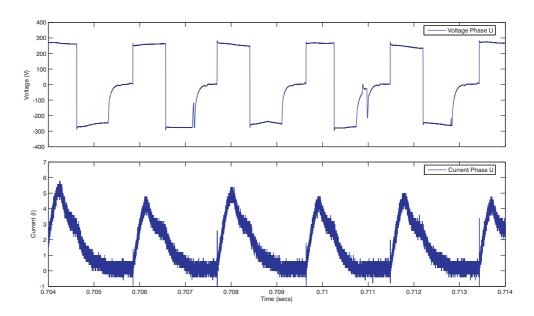

| 4.53 | Linear SRM Model (3080 rpm), SB Control, Three Phase Output Currents.   | 97 |

| 4.54 | Linear SRM Model (3080 rpm), SB Control, Phase U a, Output Current      |    |

|      | with Reference. b, Output Current Error with Hysteresis Band. c, De-    |    |

|      | manded Output Voltage.                                                  | 98 |

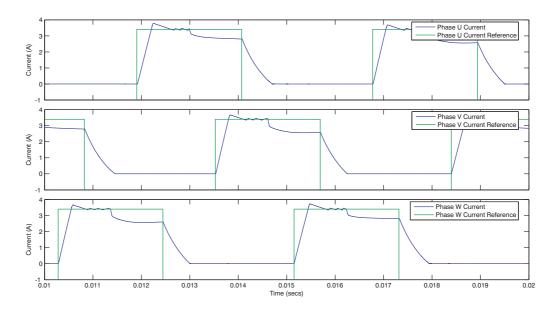

| 4.55 | Linear SRM Model (3080 rpm), DB Control, Three Phase Output Currents.   | 98 |

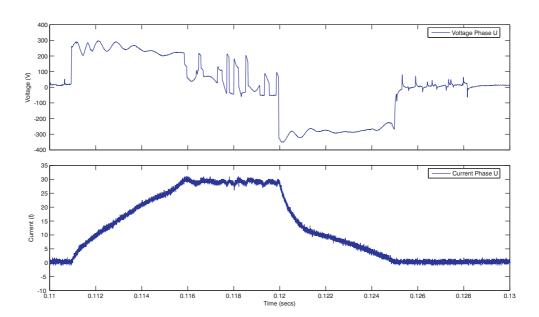

| 4.56 | Linear SRM Model (3080 rpm), DB Control, Phase U a, Output Current      |    |

|      | with Reference. b, Output Current Error with Hysteresis Bands. c, De-   |    |

|      | manded Output Voltage                                                   | 99 |

LIST OF FIGURES xviii

| 4.57 | Control. b, DB Control                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.58 | Linear SRM Model (3080 rpm), Input Voltage and Current a, SB Control.  b, DB Control                                                                                                            |

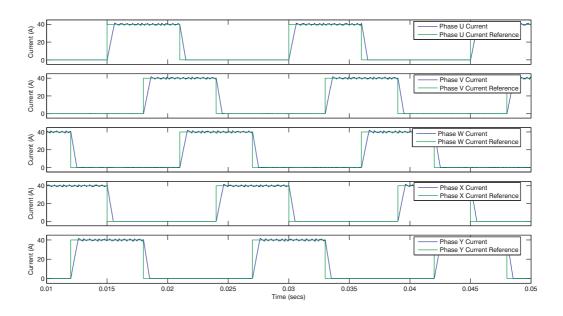

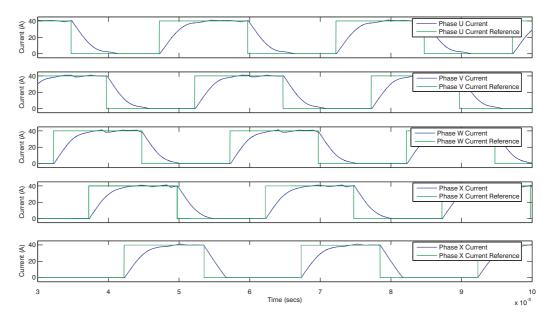

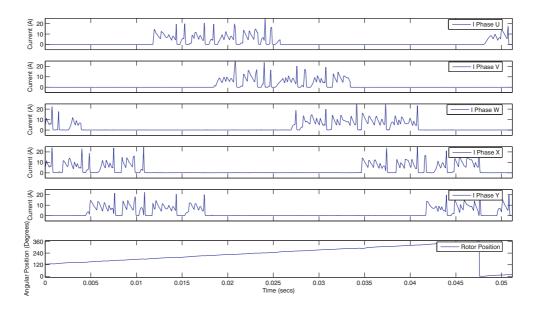

| 4.59 | SATOW PMDC Motor (2000 rpm), DB Control, Three Phase Output Currents                                                                                                                            |

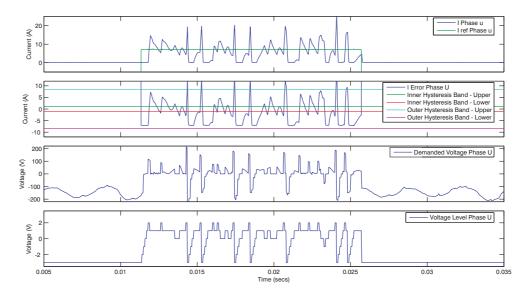

| 4.60 | SATOW PMDC Motor (2000 rpm), DB Control, Phase U a, Output Current with Reference. b, Output Current Error with Hysteresis Bands. c, Demanded Output Voltage. d, Applied Output Voltage Level   |

| 4.61 | SATOW PMDC Motor (12,000 rpm), DB Control, Three Phase Output Currents                                                                                                                          |

| 4.62 | SATOW PMDC Motor (12,000 rpm), DB Control, Phase U a, Output Current with Reference. b, Output Current Error with Hysteresis Bands. c, Demanded Output Voltage. d, Applied Output Voltage Level |

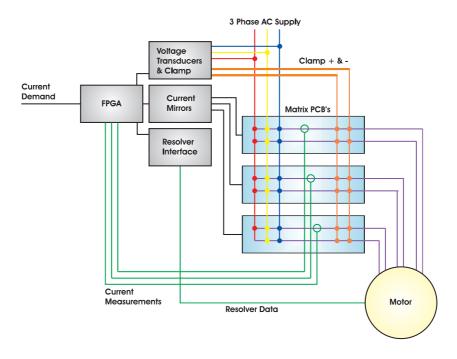

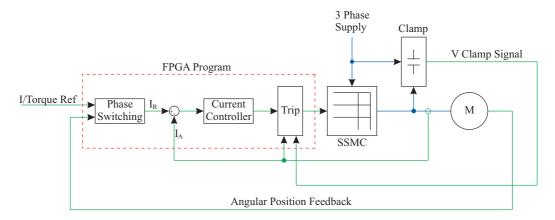

| 5.1  | Block Diagram Showing the Structure of the 3-Phase SSMC 108                                                                                                                                     |

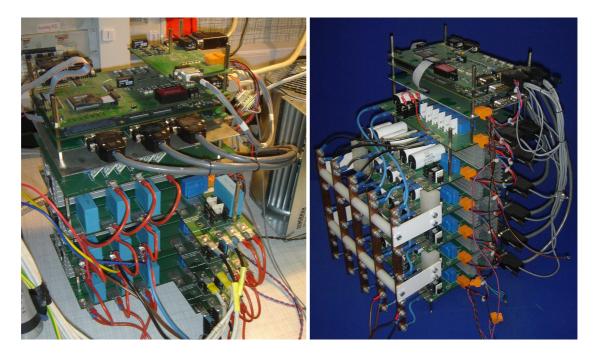

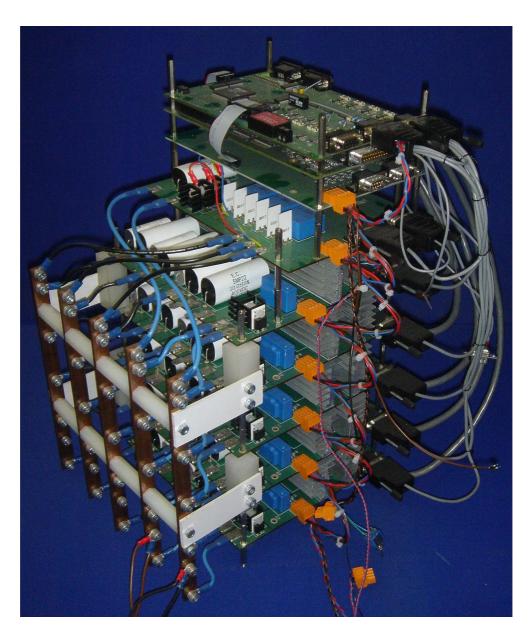

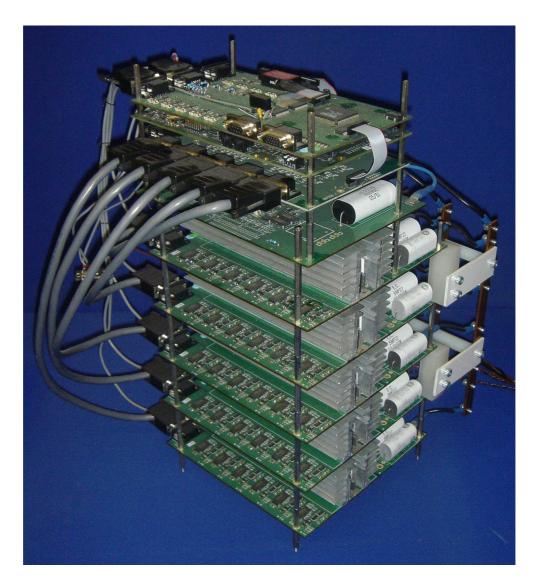

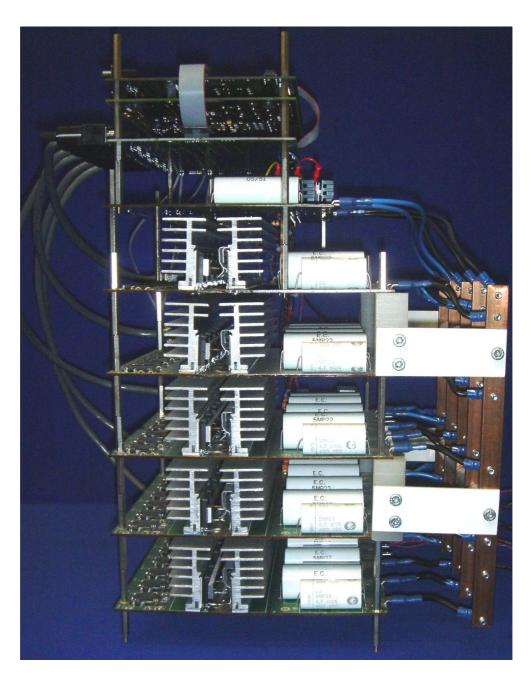

| 5.2  | Single Sided Matrix Converters. a,3-Phase. b,5-Phase                                                                                                                                            |

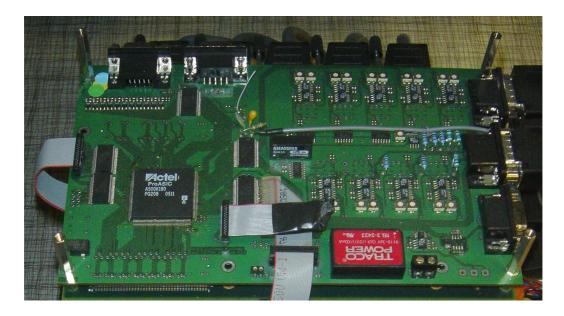

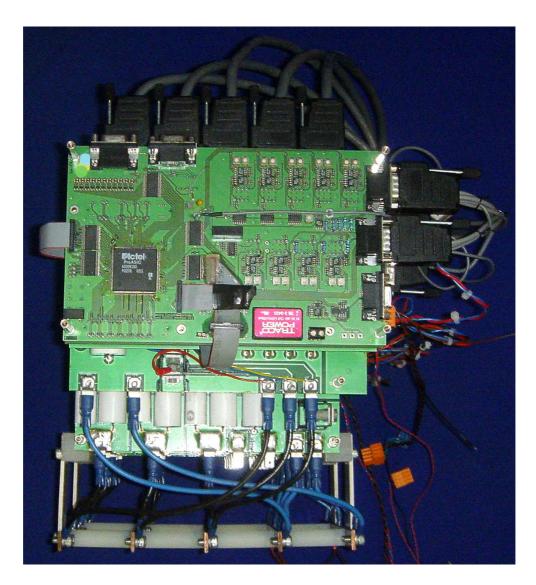

| 5.3  | FPGA Controller PCB                                                                                                                                                                             |

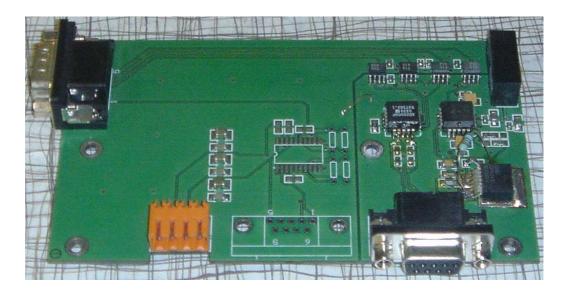

| 5.4  | Resolver Interface PCB                                                                                                                                                                          |

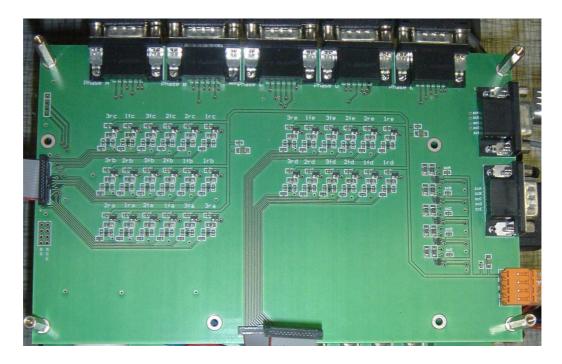

| 5.5  | Current Mirrors PCB                                                                                                                                                                             |

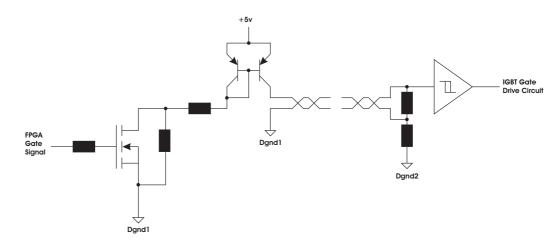

| 5.6  | Gate Drive Signal Transmission Circuit, employing Current Mirrors 114                                                                                                                           |

| 5.7  | Voltage Transducers and Clamp PCB                                                                                                                                                               |

LIST OF FIGURES xix

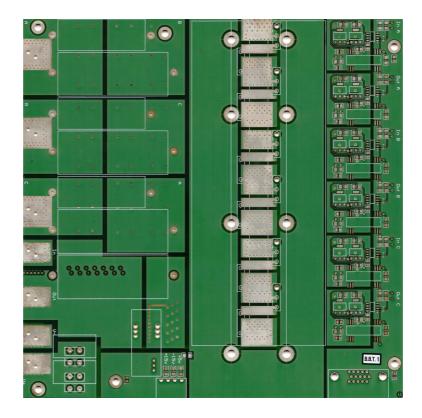

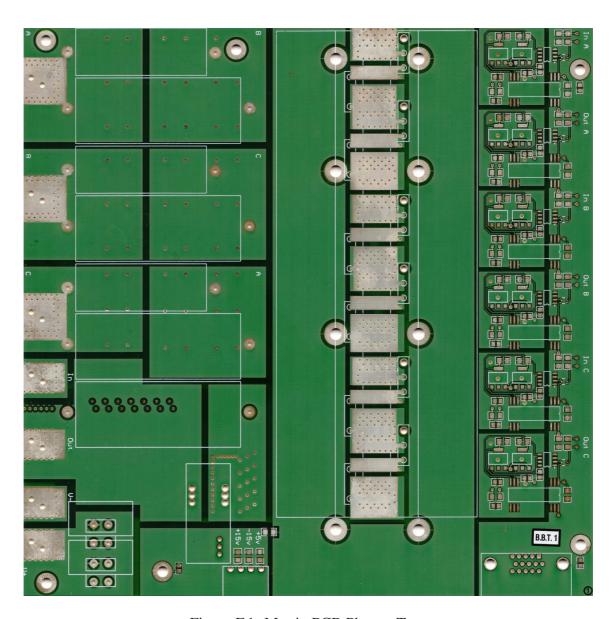

| 5.8  | Matrix Power PCB - Unpopulated                                                    |

|------|-----------------------------------------------------------------------------------|

| 5.9  | Matrix Power PCB - Populated                                                      |

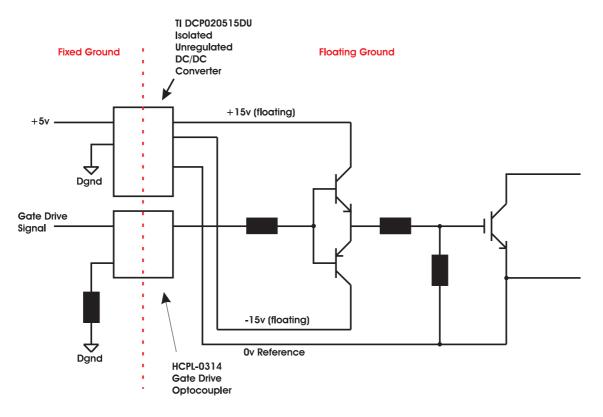

| 5.10 | IGBT Gate Drive Circuit                                                           |

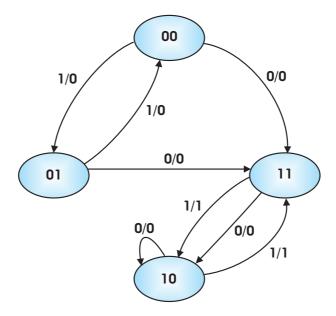

| 5.11 | Typical State Diagram                                                             |

| 5.12 | Control Structure                                                                 |

| 5.13 | FPGA Program Structure - Top Level                                                |

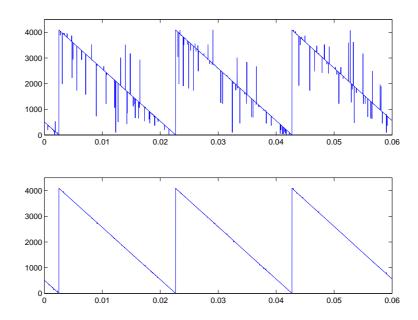

| 5.14 | Sampled resolver data, before and after filtering                                 |

| 5.15 | FPGA Program Structure - Phase Current Controller                                 |

| 5.16 | Logic Representation of Current Error With Respect to the Single Hysteresis Band  |

| 5.17 | FPGA Program Structure - Double Band Hysteresis Current Controller 144            |

| 5.18 | Logic Representation of Current Error With Respect to the Double Hysteresis Bands |

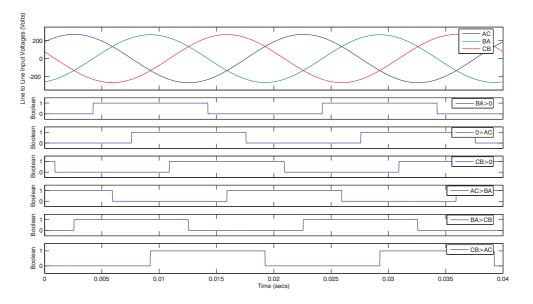

| 6.1  | Supply Phase to Phase Voltages with Supply State Logic                            |

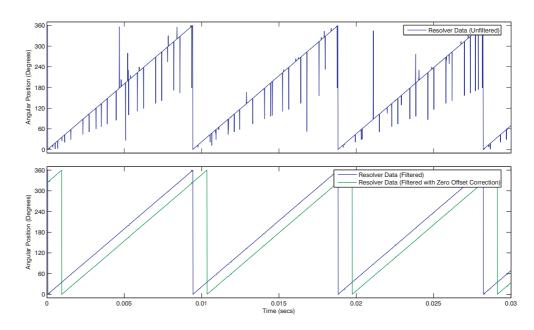

| 6.2  | Resolver Data: a,Unfiltered. b,Filtered. c,Zero Offset Corrected 151              |

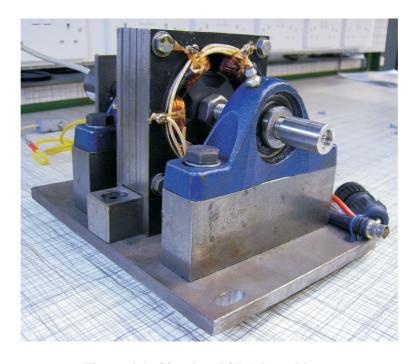

| 6.3  | Switched Reluctance Motor & Loading Rig                                           |

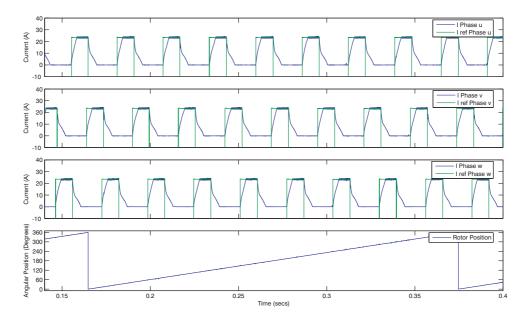

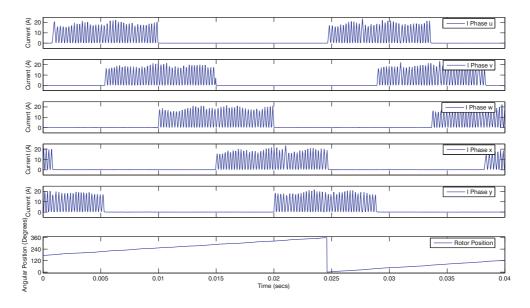

| 6.4  | SB Controlled Output Phase Currents with Rotor Position                           |

| 6.5  | SB Controlled Output Phase Currents with Rotor Position (Zoomed in) 155           |

LIST OF FIGURES xx

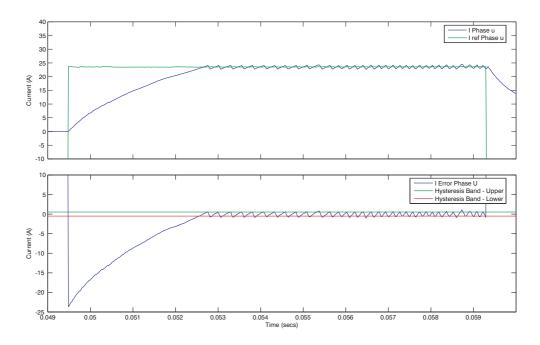

| 0.0  | Bands                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

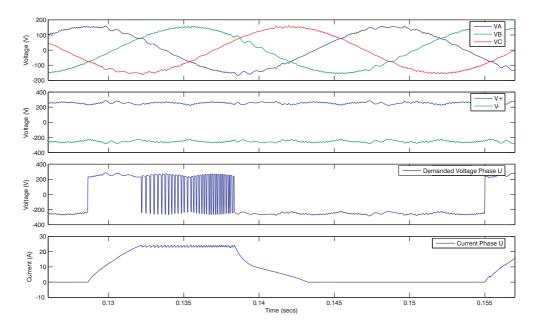

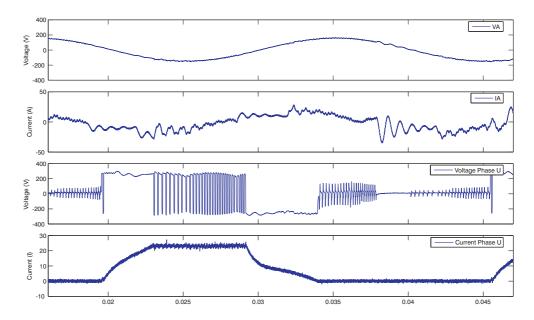

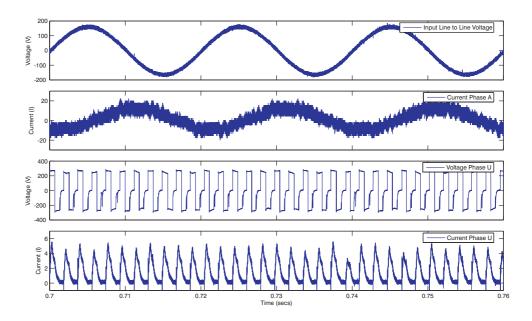

| 6.7  | DSP Data: a,Supply Line to Neutral Voltage. b,Voltage Available at Converter Output. c,Voltage Demanded at Converter Output (Phase U). d,Current Output (Phase U)  |

| 6.8  | Scope Data: a,Supply Line to Neutral Voltage (Phase A). b, Supply Current (Phase A). c,Voltage Applied at Converter Output (Phase U). d,Current Output (Phase U)   |

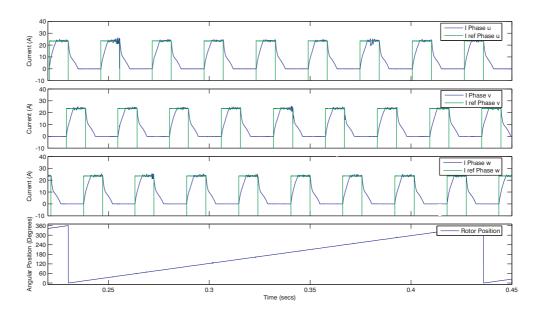

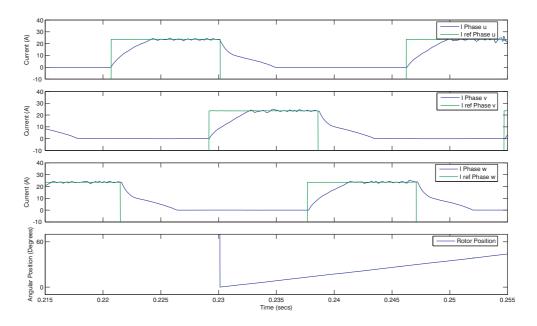

| 6.9  | DB Controlled Output Phase Currents with Rotor Position                                                                                                            |

| 6.10 | DB Controlled Output Phase Currents with Rotor Position (Zoomed in) 160                                                                                            |

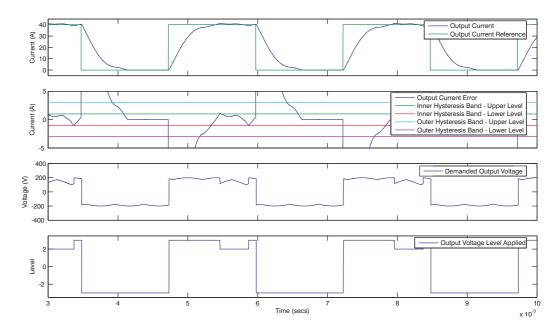

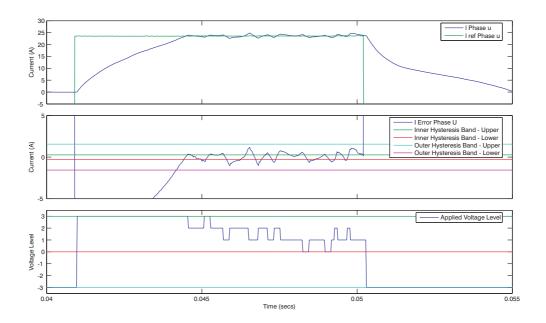

| 6.11 | DB Control, Phase U: a,Current Output. b,Current Error with Hysteresis  Bands. c,Applied Voltage Level                                                             |

| 6.12 | DSP Data: a,Supply Line to Neutral Voltages. b,Voltage Available at Converter Output. c,Voltage Demanded at Converter Output (Phase U). d,Current Output (Phase U) |

| 6.13 | Scope Data: a,Supply Line to Neutral Voltage (Phase A). b, Supply Current (Phase A). c,Voltage Applied at Converter Output (Phase U). d,Current Output (Phase U)   |

| 6.14 | Scope Data - 30amp Output Pulse (Phase U): a,Voltage Applied at Converter Output. b,Current Output                                                                 |

| 6.15 | Scope Data - 30amp Output Pulse (Phase U): a,Voltage Applied at Converter Output. b,Current Output                                                                 |

| 6.16 | Scope Data - SB Control (Phase U): a, Voltage Applied at Converter Output.  b, Current Output                                                                      |

LIST OF FIGURES xxi

| 6.17 | Scope Data - DB Control (Phase U): a,Voltage Applied at Converter Output. b,Current Output                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.18 | Scope Data - DB Control (Phase U): a,Voltage Applied at Converter Output. b,Current Output                                                                           |

| 6.19 | SB Controlled Output Phase Currents with Rotor Position                                                                                                              |

| 6.20 | SB Control (Phase U): a,Current Output. b,Current Error with Hysteresis  Bands. c,Voltage Demanded at Converter Output                                               |

| 6.21 | DB Controlled Output Phase Currents with Rotor Position                                                                                                              |

| 6.22 | DB Control (Phase U): a,Current Output. b,Current Error with Hysteresis  Bands. c,Voltage Demanded at Converter Output. d,Voltage Level Applied  at Converter Output |

| E.1  | SSMC Front                                                                                                                                                           |

| E.2  | SSMC Back                                                                                                                                                            |

| E.3  | SSMC End                                                                                                                                                             |

| E.4  | SSMC Top                                                                                                                                                             |

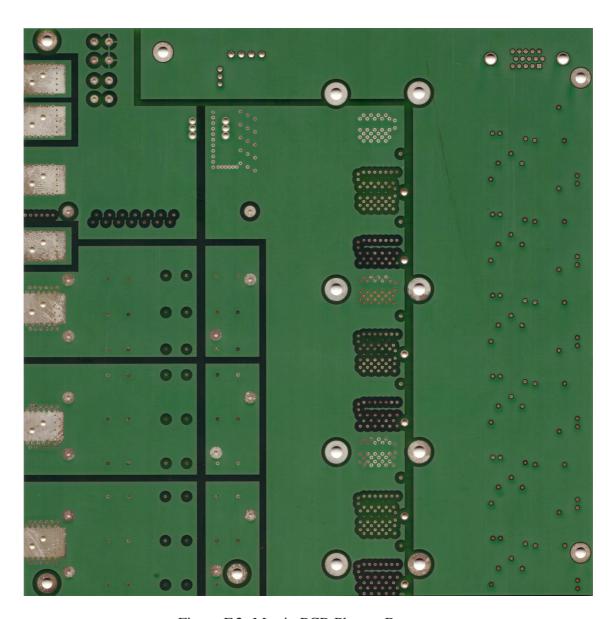

| F.1  | Matrix PCB Photo - Top                                                                                                                                               |

| F.2  | Matrix PCB Photo - Bottom                                                                                                                                            |

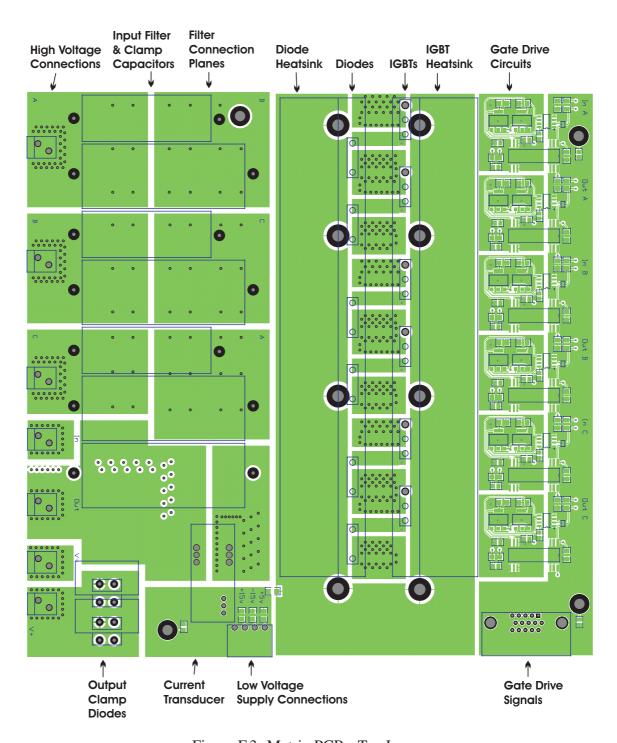

| F.3  | Matrix PCB - Top Layer                                                                                                                                               |

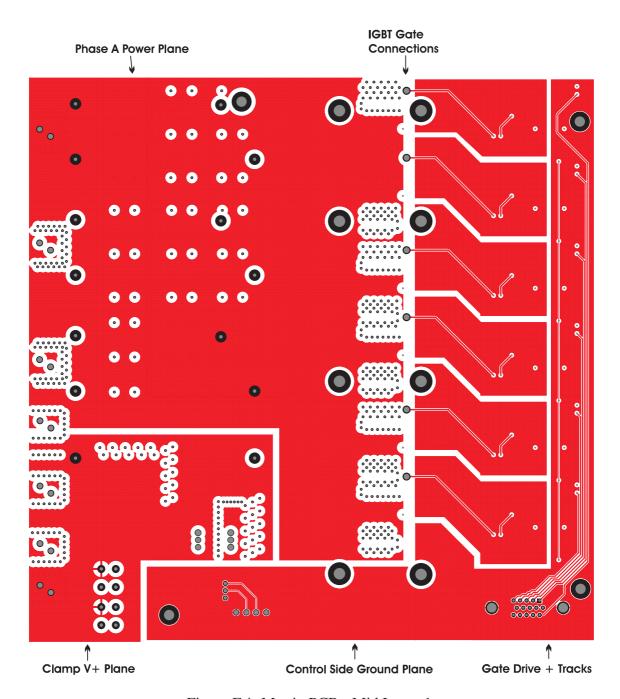

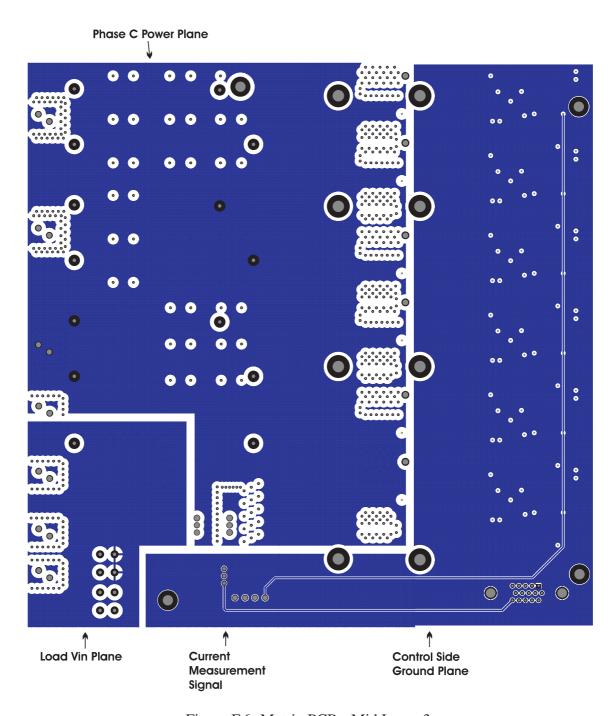

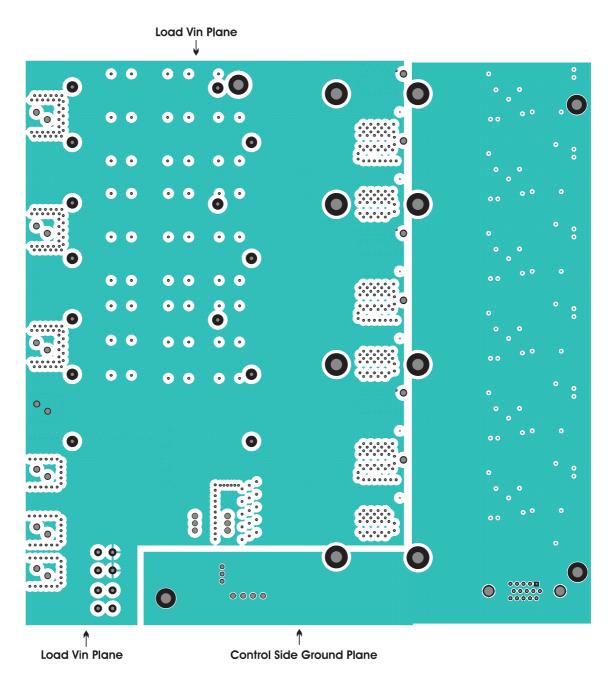

| F.4  | Matrix PCB - Mid Layer 1                                                                                                                                             |

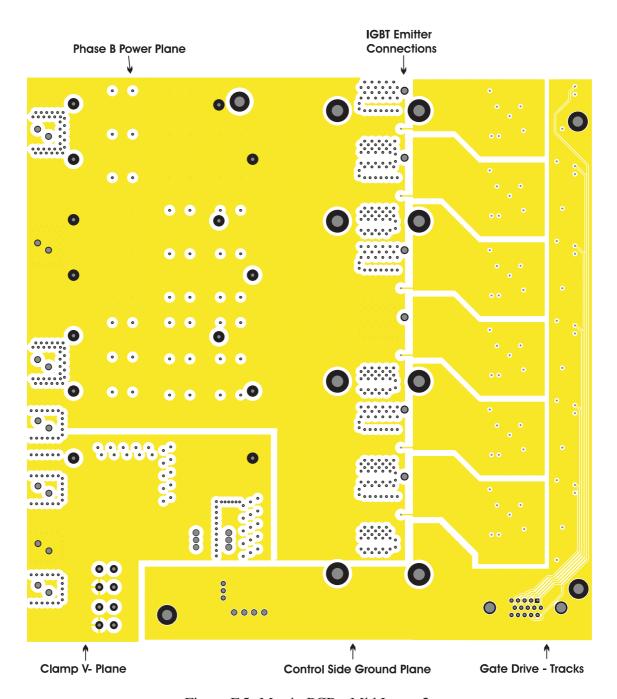

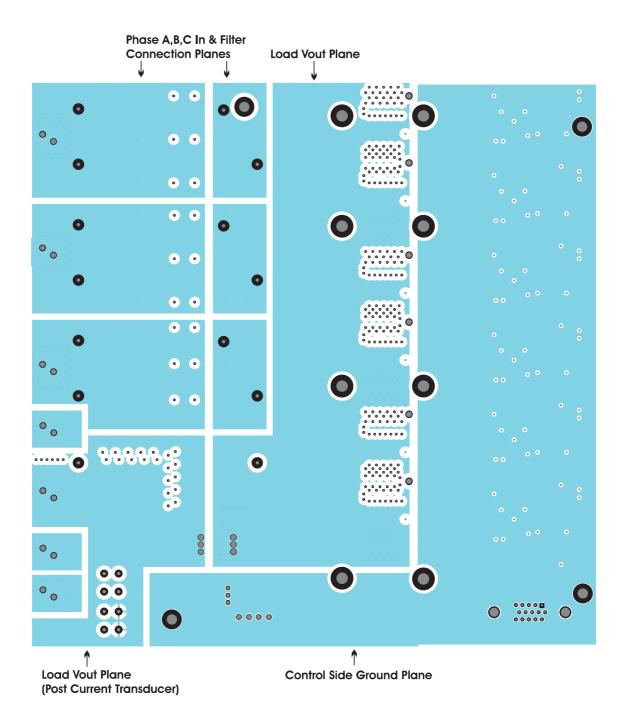

| F.5  | Matrix PCB - Mid Layer 2                                                                                                                                             |

| LIST OF FIGURES | xxi |

|-----------------|-----|

|                 |     |

| F.6 | Matrix PCB - Mid Layer 3  |

|-----|---------------------------|

| F.7 | Matrix PCB - Mid Layer 4  |

| F.8 | Matrix PCB - Bottom Layer |

# **List of Tables**

| 2.1 | AC input Direct Conversion Power Electronic Converters        | 9  |

|-----|---------------------------------------------------------------|----|

| 2.2 | Scalar Modulation input Phase Subscript Assignment            | 23 |

| 2.3 | Switching States for a 3-Phase to 3-Phase Matrix Converter    | 26 |

| 3.1 | Five Phase PMDC Motor Characteristics                         | 49 |

| 4.1 | Simulated Switched Reluctance Motor Characteristics           | 53 |

| 4.2 | Switched Reluctance Motor Experimental Data - Simulated Motor | 56 |

| 4.3 | SB - Hysteresis Band Block Output Signal States               | 62 |

| 4.4 | SB - Voltage Level Identifier Truth Table                     | 62 |

| 4.5 | DB - Hysteresis Band Block Output Signal States               | 67 |

| 4.6 | DB - Voltage Level Coding Logic                               | 67 |

| 4.7 | Inductive Load Characteristics                                | 69 |

| 4.8 | Fourier Analysis Single Band Simulation Conditions            | 75 |

LIST OF TABLES xxiv

| 4.9  | Fourier Analysis Single Band Simulation Conditions                                                  |

|------|-----------------------------------------------------------------------------------------------------|

| 4.10 | Loss Estimation Simulation Conditions                                                               |

| 4.11 | Switching and Conduction Loss Figures for Single Band and Double Band Control Schemes               |

| 5.1  | A/D Channel Assignments                                                                             |

| 5.2  | Matrix PCB Layer Usage                                                                              |

| 5.3  | Values Required to Calculate Clamp Capacitance                                                      |

| 5.4  | IPC-2221 Constants                                                                                  |

| 5.5  | Required PCB copper widths for SR Motor SSMC (using internal layer IPC values)                      |

| 5.6  | Required PCB copper widths for SATOW Trapezoidal PMDC Motor SSMC (using internal layer IPC values)  |

| 5.7  | Required number of PCB vias for SR Motor SSMC (using external layer IPC values)                     |

| 5.8  | Required number of PCB vias for SATOW PMDC Trapezoidal Motor SSMC (using external layer IPC values) |

| 5.9  | Typical State Table                                                                                 |

| 5.10 | Input Voltage state signals                                                                         |

| 5.11 | Resolver Offset Application                                                                         |

| 5.12 | Voltage Level Identifier Logic                                                                      |

LIST OF TABLES xxv

| 6.1         | Experimental Switched Reluctance Motor Characteristics - Final testing |

|-------------|------------------------------------------------------------------------|

|             | Motor                                                                  |

| 6.2         | Switched Reluctance Motor Experimental Data                            |

| B.1         | Single Band Controller - Gating Signal Logic                           |

| <b>C</b> .1 | Double Band Controller - Voltage Level Identifier Logic                |

| C.2         | Double Band Controller - Gating Signal Logic                           |

| C 3         | Double Band Controller - Switch Logic 198                              |

## **Chapter 1**

### Introduction

In many applications today simple, reliable, high performance motor drives are desired. This need is clear in the safety critical aerospace actuator industry more than any other, where there is considerable interest in replacing the conventional centralised hydraulic flight control system with electrically powered actuators located near to the control surface being moved [1] [2] [3]. Whilst simple systems may be the aim, simplicity rarely allows high performance, or optimisation of efficiency. The approach is therefore to design a system which uses simple elements where possible, and highly reliable elements where it is not possible. Unfortunately however, it is common that the more complicated a system is, the less reliable it becomes, as it has more potential failure modes. A third level to the systems design approach is therefore adopted, which encompasses fault tolerance and redundancy [4]. An analysis is performed to evaluate the local systems ability to continue functioning after the failure of an element within it, albeit in a non-ideal or lesser efficient way, in order that the larger system can continue to function until repairs can be made [5].

In the work of this thesis, the above design approach has been implemented in specifying a motor drive suitable for use in operability critical applications, such as the aerospace actuator industry.

One of the simplest and most reliable forms of motor is the switched reluctance (SR) motor

[6], which makes it highly suitable for use in aircraft actuators [7]. This motor has a simple construction, with a laminated rotor free of both windings and magnets. The stator is also a simple design, constructed again of steel laminations, and with a small number of poles carrying isolated phase windings. This simple construction makes the motor cheap to produce, and the simple laminated rotor makes it highly mechanically robust and suitable for operation over a very wide speed range. The isolated phase windings make this motor highly fault tolerant, as with the right numbers of poles and phases, it can continue to spin with a fault on one phase, without a danger of the fault affecting other phases. The switched reluctance motor has been acknowledged by Boeing as being the preferred motor for many aerospace applications, due to the built in redundancy, and the fundamental magnetic and electrical isolation of the design [8]. The absence of permanent magnets from the motor is also seen as an advantage, as there are no demagnetisation concerns at higher temperatures. A 25kW 16,000rpm switched reluctance motor was developed for an aerospace actuator by Glasgow University, with the design being favoured due to the inherent fault tolerant advantages [9].

The conventional way to drive a switched reluctance motor is using a simple asymmetric half-bridge switching converter, as was used in the Glasgow project [9]. This connects a DC voltage source in the required direction across the motor phases in alternate directions at high frequency, in order to produce the required change in current level. The switching is done using solid state power electronic switches such as MOSFET's or IGBT's. Other converter topologies have been proposed and are used where only low power or low speed operation is required, or where larger phase numbers are present [10]. Circuit topologies have also been developed that are better suited to high speed operation [11] [12]. The common feature of all of these circuits is that they are supplied from a DC voltage source, which is commonly a large capacitor, supplied from a rectified sinusoidal voltage source. This implies a multi-stage energy conversion process and has the disadvantage of the requirement for a large DC link capacitor between the input and output stages, such that a smooth DC link voltage is maintained despite the large power pulsations drawn by the switched reluctance motor. In order to achieve a large capacitance in a suitable volume, electrolytic capacitors are normally necessary. These still generally occupy a significant volume of the drive, and are unsuitable for aerospace applications due to the vulnerability of the fluid within them to large variations in pressure and temperature. The rectification stage normally also implies uni-directional power flow, making regenerative braking impossible. An active front end PWM voltage source rectifier can be used but adds a further level of complexity to the drive, and potential for reliability problems.

Presented in this thesis is a novel form of power electronic converter, termed the single sided matrix converter (SSMC). This is a direct energy converter, and switches input phases directly to output phases, without the use of an intermediary energy storage device. It is based on a standard matrix converter topology, but uses only unidirectional switch cells (implemented using an IGBT), as opposed to the conventional bidirectional switch cells. This means that only unidirectional currents can be supplied by the SSMC, as are required by the switched reluctance motor. The complex commutation problem seen in conventional matrix converters [13] remains a vulnerability of the drive, even though reliable commutation schemes have been tested at significant power levels [14] [15]. The use of unidirectional switch cells means that the commutation problem is greatly simplified, as the reduced number of power electronic switches and arrangement of diodes makes a short circuit between input phases impossible. Care must only be taken to ensure that an open circuit on the output side does not occur.

Control of the drive was to be achieved without the use of a digital signal processor (DSP), making it easily usable in the aerospace industry, without the need for approval of the specific DSP. Two simple hysteresis based control schemes were therefore proposed which would be suitable for implementation using a field programmable gate array (FPGA) chip. The first of these uses a single hysteresis band, and applies the most positive and most negative supply voltages available in order to control the motor phase currents. The second scheme uses a novel double hysteresis band configuration and applies different input line to line voltages across the motor phase terminals depending on the current change required.

A motor drive is therefore proposed which uses:

- a simple, inherently fault tolerant motor.

- a direct energy conversion power electronic converter which avoids the need for large

electrolytic capacitors, making it suitable for aerospace applications, and which is inherently simpler than a conventional matrix converter.

• a control scheme fully implemented on an FPGA, making its use in aerospace actuation systems a straightforward process.

Potential for use of the SSMC with a brushless trapezoidal PMDC motor was also recognised early in this PhD, and a second student, Xiaoyan Huang began work on the design of a novel 5-phase PMDC motor as part of her PhD. Two single sided matrix converters were therefore assembled and tested as part of this PhD work, with results presented for both applications.

#### 1.1 Thesis Structure

The remainder of this thesis is divided into chapters, covering different areas of the work carried out.

Chapter 2 provides an overview of some common power electronic converter types, including direct energy converters. A detailed review of the conventional matrix converter and its associated practical implementation problems, solutions and control methods is provided.

In chapter 3, the single sided matrix converter is introduced. Firstly the circuit topology is explained, followed by a look at the methods of control that are proposed. Consideration is also given to the most appropriate form of control platform to be used, bearing in mind the need for high reliability and potential application within the aerospace industry. A review is then provided of the types of motor which may be suitable for use with the SSMC, and the design considerations that should be taken into account to provide reliable, fault tolerant operation.

Presented in chapter 4 are simulations performed to verify the operation of the circuit

topology and the proposed control schemes. Firstly the models used are described, including the simple switched reluctance motor model that was developed. Simulation results are then provided for operation of both control schemes, applied to control of currents in an inductive/resistive load, the switched reluctance motor, and a trapezoidal PMDC motor.

Chapter 5 gives details of the practical implementation of the single sided matrix converter and its control. First the converter hardware is described, including the controller platform, and several PCB's. One of these was used to provide the laminated power planes required for safe operation of the matrix converter. The FPGA controller is then described. A review is provided of the program development suite, followed by a consideration of the procedures required to develop programmes for FPGA's. A description is then given of the FPGA control software developed, as well as the interfacing of a DSP, used to extract controller operation data.

In chapter 6, the practical results taken from the prototype SSMC are presented. Results for two converters were acquired, demonstrating operation of the SSMC with both the switched reluctance and trapezoidal PMDC motors. Results for both proposed control schemes are given.

Chapter 7 presents the conclusions drawn from the work, including advantages and disadvantages of the two proposed control techniques. This is followed by a look at areas recognised as requiring further research.

## Chapter 2

# Power Electronic Converters including the Matrix Converter

Throughout the majority of this thesis, the SSMC is considered as an electronic drive for an electric motor. In broader terms however, it is a power electronic converter, and fits into a family of power electronic converters, differentiated by their input and output current and voltage types and power flow capabilities. This chapter begins by summarising the general types of power conversion performed using power electronic converters, before a somewhat more detailed explanation of the operation of AC input direct power converters. The intention is to assist the reader in placing the SSMC within this family of power converters, whilst gaining an understanding of the relative advantages and disadvantages of each.

#### 2.1 Power Electronic Converters Overview

Power Electronic Converters are used when there is a need to modify the form of electrical energy. Semiconductor devices are used to switch the electrical supply, using a large number of circuit topologies. The energy conversions that are commonly implemented

using power electronic converters are:

- 1. DC to DC

- 2. AC to DC

- 3. DC to AC

- 4. AC to AC

Conversions 1 to 3 are commonly performed as direct conversion's, whereas conversion 4 is usually achieved using a two step process. The converters used to perform each of the conversions are mentioned briefly below.

DC to DC conversion is commonly performed by either a chopper for voltage reduction, or a boost converter where a higher output voltage is required.

AC to DC conversion is performed by a rectifier, either uncontrolled, using diodes, or controlled, using thyristors, where the output voltage is controllable. PWM rectifiers are also sometimes used where greater control over input current quality, or regeneration to the supply is required.

DC to AC conversion is performed using an inverter. There are two common forms of inverter. The first, the 'Six Step Square-Wave Inverter', outputs rectangular blocks of voltage at the required output frequency. A positive output voltage would be followed by a period of zero volts, and then a period of negative voltage, again followed by a period of zero volts. When connected across an inductive load this rectangular output voltage induces an approximately sinusoidal flow of current. The second common form of inverter is the 'Pulse Width Modulated (PWM) Inverter'. With this form of inverter, the DC voltage is switched across the output at a high frequency. By varying the on duration with respect to the off duration, and applying this across an inductive load, a sinusoidal current is induced.

AC to AC conversion is most commonly performed as a two step conversion, where the incoming AC is first rectified to produce DC, which is smoothed using a DC link capacitor

and then inverted, commonly using a PWM Inverter, to reproduce AC at a new voltage and frequency. This approach is widely used, and when using a PWM controlled rectifier and PWM inverter, is seen to produce very good results. Sinusoidal input and output currents are produced, assuming that the high frequency switching component of the waveform is filtered out by both the load inductance, and the supply side filter, and unity power factor at the input is possible. This form of AC to AC converter does however rely heavily on the use of a relatively large DC link capacitance in order to smooth the power flow between the input and output.

#### 2.1.1 The PWM Current Source Rectifier

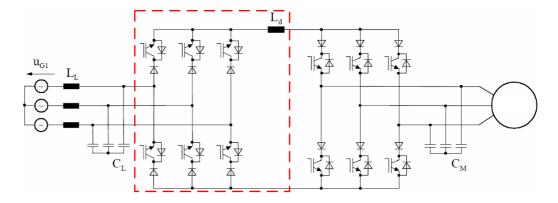

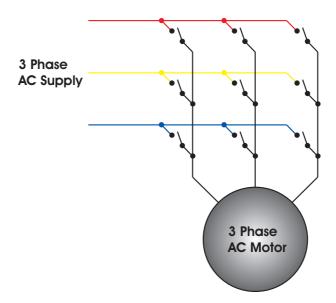

The PWM rectifier may be used as the front end in a back-to-back inverter arrangement, where regeneration to the supply and/or improved input current quality is required. Two topologies exist, the voltage source PWM rectifier and the current source PWM rectifier. A PWM rectifier is shown within the red dashing in figure 2.1, as part of a regenerative AC motor drive. Both the voltage and current source rectifiers output to a DC stage, this being a DC link capacitor in the case of the voltage source PWM rectifier, and a DC link inductor labelled Ld here, for the current source PWM rectifier.

Figure 2.1: PWM Current Source Rectifier

The circuit topology of the PWM current source rectifier is the same as that used in the single sided matrix converter, however its control and use are quite different. In the current

source PWM rectifier a continuous, but variable Ld current is required. This is fed to the output stage, which modulates the constantly flowing current between the AC load phases. In this type of balanced three phase AC application, constant output power will be drawn, implying constant input power. With the correct modulation of the input side switching devices, possibly using the space vector method [16], this constant power flow is inherently translated into sinusoidal input currents [17]. The use of the circuit to supply pulsed DC loads presents a new control problem, which is the focus of this work.

#### **2.2** Direct Power Converters (AC Input)

For the purposes of this thesis, the term 'direct power converter' refers to a power electronic converter which does not include an energy storage element between its input and output side. An example of a converter that does include an energy storage element is the PWM rectifier/inverter combination described in section 2.1. Also, as this research was concerned with drawing power from an AC supply, this chapter considers only direct power converters designed for use with an AC input. Most converters designed to supply power from a DC input are inherently direct power converters.

Referring to table 2.1, one can see how the SSMC compares with the Rectifier, the Cycloconverter and the Matrix Converter. Each is a direct power converter, however the Cycloconverter and Matrix Converter produce an AC output, whilst the Rectifier and Single Sided Matrix Converter produce a DC type output. However, considering the type of commutation, the Rectifier and Cycloconverter are naturally commutated, whilst the two forms of matrix converter are force commutated. An explanation of each converter topology and the way in which it is operated is provided in the remainder of this chapter.

|               | Commutation    |                               |

|---------------|----------------|-------------------------------|

|               | Natural        | Forced                        |

| Non-AC Output | Rectifier      | Single Sided Matrix Converter |

| AC Output     | Cycloconverter | Matrix Converter              |

Table 2.1: AC input Direct Conversion Power Electronic Converters

#### 2.2.1 The Cycloconverter

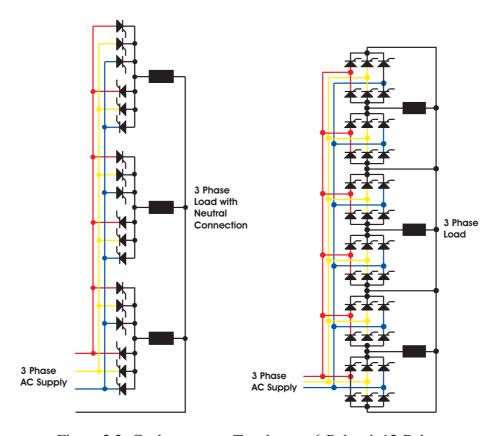

The Cycloconverter is a direct conversion static frequency changer. Two circuit topologies for a three phase input, three phase output Cycloconverter are shown in figure 2.2. The circuit uses thyristors, and by applying a varying delay to the appropriate thyristor firing signal, an output voltage can be produced which approximates a sine wave.

Figure 2.2: Cycloconverter Topology. a,6-Pulse. b,12-Pulse.

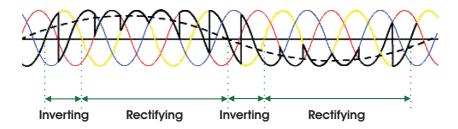

Once a thyristor has been fired, it conducts until the potential applied across it is reversed. This implies that high frequency switching of the devices is not possible, and hence only output frequencies lower than that of the input frequency may be reproduced. Figure 2.3 shows the three input phase voltages along with the output phase voltage in solid black, and the output current as the dashed black sine curve. This is for the case of a resistive load, with maximum output voltage at approximately  $2/11^{ths}$  supply frequency. More commonly, inductive loads are supplied. When this is the case, the current lags the voltage as shown

in figure 2.4.

Figure 2.3: Cycloconverter Single Output Phase Voltage - Resistive Load

Figure 2.4: Cycloconverter Single Output Phase Voltage - Resistive & Inductive Load

Whilst clearly a direct power converter, the cycloconverter has the significant disadvantage that its switching frequency is tied to that of the voltage supply, and can therefore only supply loads requiring slow changes in average current level, such as low frequency AC drives as can be found in traction applications [18] and large rolling mills [19].

### 2.2.2 The Matrix Converter

The matrix converter can be considered as a force commutated cycloconverter, implying a direct AC to AC converter capable of high switching frequencies, and therefore output voltage frequencies greater than that of the cycloconverter. The three phase version uses nine bidirectional switches, allowing connection of each output phase to each input phase of the converter. This implies bidirectional power flow, allowing regeneration to the supply if the application is suitable. Precise control of the phase commutations is essential in order to avoid short circuits on the input side of the converter.

Complex switching strategies are employed within the matrix converter control, requiring

the use of a DSP. This however allows sinusoidal input currents to be drawn, when a balanced sinusoidal load is being driven. Power factor correction is inherently possible by advancing or delaying the input current waveform with respect to the input voltage waveforms.

The direct conversion nature of the matrix converter means that no DC link capacitor is used. This is advantageous for aerospace actuators, however, the lack of energy storage within the converter implies filtering of the supply is necessary in order to meet its harmonic requirements. The input filter uses a small amount of energy storage within low value capacitors in order to remove the majority of the switching harmonics induced in the supply currents due to the PWM switching of the matrix converter.

A more in depth description of the topology, control, and commutation problem is provided in section 2.3.

### 2.3 The Conventional Matrix Converter

The concept of the matrix converter was first seen in the work of L.Gyugyi and B.Pelly, who described 'Static Power Frequency Changers' in their publication of 1976 [20]. At this time the matrix converter was referred to as a Force Commutated Cycloconverter, this being a cycloconverter in which bidirectional static power devices were employed and controlled in such a way as to enable the converter to be used as an unrestricted frequency changer capable of regenerative power recovery. Much research has been carried out since this time in optimising the control of the matrix converter devices in order to produce a safe, reliable and efficient implementation of the topology, suitable for applications in the real world.

The following sections discuss the fundamentals of the matrix converter, including its advantages and disadvantages when compared with alternative drives. Many solutions to the practical implementation problems of the matrix converter have been proposed over the years, and a review of those is given, including descriptions of the mathematical models used to solve the modulation problem.

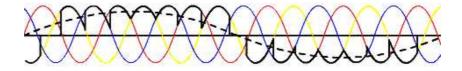

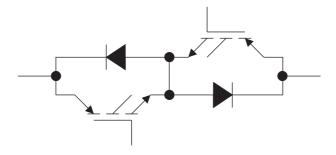

### 2.3.1 Circuit Structure

The Matrix converter offers an all silicon solution for AC-AC power conversion. A 3-phase to 3-phase matrix converter consists of an array of nine bi-directional switches, constructed from unidirectional power devices, and arranged such that any of the output lines of the converter can be connected to any of the input lines. A simplified block diagram of the circuit layout is given in figure 2.5. One commonly used form of bidirectional switch is the common emitter configuration, as shown in figure 2.6. The advantage of the common emitter configuration is that only one isolated floating power supply is required per bidirectional switch cell.

Figure 2.5: Conventional AC Matrix Converter Topology

The required output voltages are generated by the precise, high frequency modulation of the converter switches, based on the supply voltage state. When compared with conventional AC/DC drives as used with switched reluctance motors, or AC/DC/AC drives used with sinusoidal AC machines, the matrix converter topology has several advantages. The first, and major of these is the removal of the DC link and associated bulky electrolytic capacitors, which have a limited lifetime, and are intolerant to high temperatures. This results in a high power density converter being possible. Bidirectional power flow is also

Figure 2.6: Common Emitter Bidirectional Switch Cell used in Conventional AC Matrix Converters

an inherent feature of the matrix converter, and with appropriate control of the switching components, both output voltage and input current are sinusoidal (for a balanced sinusoidal load), with the only harmonics generated being at or above the device switching frequency. Unity displacement factor in the supply is also inherently possible with the use of the appropriate modulation technique.

Research carried out since the 1970's has overcome many of the problems of practical implementation of the matrix converter, and interest from industry is growing [21], with specific matrix converter IGBT packages being developed [22] [23] [24]. As semiconductor prices continue to fall, matrix converters may in the future become attractive alternatives to the back-to-back inverter commonly used in applications where sinusoidal input currents and true bidirectional power flow are required [25]. One of the problems with the matrix converter, where standard supply voltage and standard machines are to be used is the voltage transfer ratio, as is discussed in section 2.3.2.2. This will not however cause a problem when the electrical machine can be designed for use with a matrix converter, as part of an integrated motor drive.

### 2.3.2 Mathematical Model and Modulation Strategies

The problem of modulating the switches in a matrix converter is a complex one. This section presents the mathematical model of matrix converter operation, and introduces the

modulation problem. The material in this section is based on the mathematical development presented in [26]. Several different matrix converter modulation strategies have been proposed, and this section discusses the two most common. The remaining solutions are mostly similar, and are not discussed here.

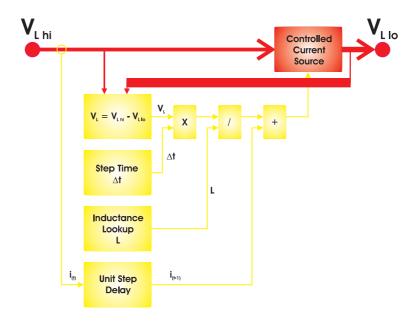

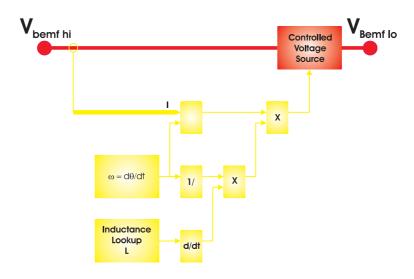

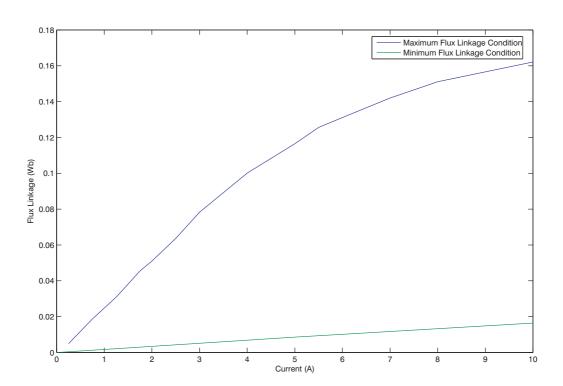

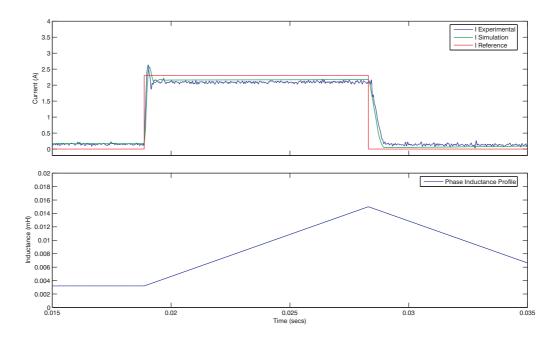

The following study is based on a three phase input, three phase output matrix converter, as shown in figure 2.5. The principle will however apply to a converter with any number of input and output phases. The designation of input and output connections in the matrix converter is arbitrary, as the converter switching circuit is symmetrical. However all sensible modes of operation will see one side of the matrix converter having a voltage stiff characteristic, and the other side having a current stiff characteristic. In this discussion, and as with any motor drive application, the input side is voltage stiff (as ensured by lineside phase to phase filter capacitors), and the output is current stiff, due to the inductive nature of the motor load.